#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 10MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                        |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 36                                                                       |

| Program Memory Size        | 14KB (8K x 14)                                                           |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 368 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                |

| Data Converters            | A/D 14x10b                                                               |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Through Hole                                                             |

| Package / Case             | 40-DIP (0.600", 15.24mm)                                                 |

| Supplier Device Package    | 40-PDIP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf777-i-p |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 2.0 MEMORY ORGANIZATION

There are two memory blocks in each of these PIC<sup>®</sup> MCUs. The program memory and data memory have separate buses so that concurrent access can occur and is detailed in this section. The program memory can be read internally by user code (see Section 3.0 "Reading Program Memory").

Additional information on device memory may be found in the *"PIC<sup>®</sup> Mid-Range MCU Family Reference Manual"* (DS33023).

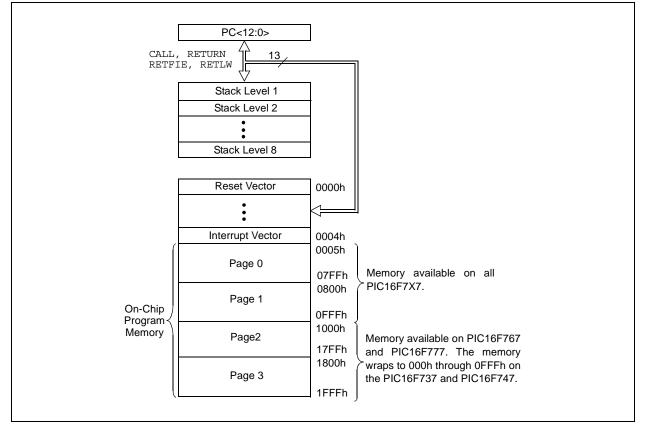

## 2.1 Program Memory Organization

The PIC16F7X7 devices have a 13-bit program counter capable of addressing an 8K word x 14-bit program memory space. The PIC16F767/777 devices have 8K words of Flash program memory and the PIC16F737/747 devices have 4K words. The program memory maps for PIC16F7X7 devices are shown in Figure 2-1. Accessing a location above the physically implemented address will cause a wraparound.

The Reset vector is at 0000h and the interrupt vector is at 0004h.

## 2.2 Data Memory Organization

The data memory is partitioned into multiple banks which contain the General Purpose Registers and the Special Function Registers. Bits RP1 (Status<6>) and RP0 (Status<5>) are the bank select bits:

| RP1:RP0 | Bank |

|---------|------|

| 0 0     | 0    |

| 01      | 1    |

| 10      | 2    |

| 11      | 3    |

Each bank extends up to 7Fh (128 bytes). The lower locations of each bank are reserved for the Special Function Registers. Above the Special Function Registers are General Purpose Registers, implemented as static RAM. All implemented banks contain Special Function Registers. Some frequently used Special Function Registers from one bank may be mirrored in another bank for code reduction and quicker access.

### 2.2.1 GENERAL PURPOSE REGISTER FILE

The register file (shown in Figure 2-2 and Figure 2-3) can be accessed either directly, or indirectly, through the File Select Register (FSR).

### FIGURE 2-1: PROGRAM MEMORY MAPS AND STACKS FOR PIC16F7X7 DEVICES

© 2003-2013 Microchip Technology Inc.

#### 4.7.4 EXITING SLEEP WITH AN INTERRUPT

Any interrupt, such as WDT or INTO, will cause the part to leave the Sleep mode.

The SCS bits are unaffected by a SLEEP command and are the same before and after entering and leaving Sleep. The clock source used after an exit from Sleep is determined by the SCS bits.

#### 4.7.4.1 Sequence of Events

#### If SCS<1:0> = 00:

- 1. The device is held in Sleep until the CPU start-up time-out is complete.

- If the primary system clock is configured as an 2. external oscillator (HS, XT, LP), then the OST will be active waiting for 1024 clocks of the primary system clock. While waiting for the OST, the device will be held in Sleep unless Two-Speed Start-up is enabled. The OST and CPU start-up timers run in parallel. Refer to Section 15.17.3 "Two-Speed Clock Start-up Mode" for details on Two-Speed Start-up.

- 3. After both the CPU start-up timer and the Oscillator Start-up Timer have timed out, the device will exit Sleep and begin instruction execution with the primary clock defined by the FOSC bits.

If SCS < 1:0 > = 01 or 10:

- The device is held in Sleep until the CPU start-up 1. time-out is complete.

- 2. After the CPU start-up timer has timed out, the device will exit Sleep and begin instruction execution with the selected oscillator mode.

- Note: If a user changes SCS<1:0> just before entering Sleep mode, the system clock used when exiting Sleep mode could be different than the system clock used when entering Sleep mode. As an example, if SCS<1:0> = 01, T1OSC is the system clock and the following instructions are executed: BCF

SLEEP

OSCCON, SCS0

then a clock change event is executed. If the primary oscillator is XT, LP or HS, the core will continue to run off T1OSC and execute the SLEEP command.

When Sleep is exited, the part will resume operation with the primary oscillator after the OST has expired.

## 7.6 Timer1 Oscillator

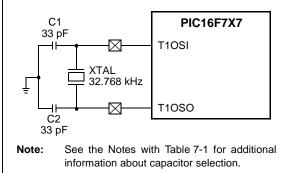

A crystal oscillator circuit is built between pins T1OSI (input) and T1OSO (amplifier output). It is enabled by setting control bit, T1OSCEN (T1CON<3>). The oscillator is a low-power oscillator, rated up to 32.768 kHz. It will continue to run during all power-managed modes. It is primarily intended for a 32 kHz crystal. The circuit for a typical LP oscillator is shown in Figure 7-3. Table 7-1 shows the capacitor selection for the Timer1 oscillator.

The user must provide a software time delay to ensure proper oscillator start-up.

## FIGURE 7-3: EXTERNAL COMPONENTS FOR THE TIMER1 LP OSCILLATOR

## TABLE 7-1:CAPACITOR SELECTION FOR<br/>THE TIMER1 OSCILLATOR

| Osc Type | Freq   | C1    | C2    |  |  |

|----------|--------|-------|-------|--|--|

| LP       | 32 kHz | 33 pF | 33 pF |  |  |

- **Note 1:** Microchip suggests this value as a starting point in validating the oscillator circuit.

- **2:** Higher capacitance increases the stability of the oscillator but also increases the start-up time.

- 3: Since each resonator/crystal has its own characteristics, the user should consult the resonator/crystal manufacturer for appropriate values of external components.

- **4:** Capacitor values are for design guidance only.

## 7.7 Timer1 Oscillator Layout Considerations

The Timer1 oscillator circuit draws very little power during operation. Due to the low-power nature of the oscillator, it may also be sensitive to rapidly changing signals in close proximity.

The oscillator circuit, shown in Figure 7-3, should be located as close as possible to the microcontroller. There should be no circuits passing within the oscillator circuit boundaries other than VSS or VDD.

If a high-speed circuit must be located near the oscillator, a grounded guard ring around the oscillator circuit, as shown in Figure 7-4, may be helpful when used on a single sided PCB or in addition to a ground plane.

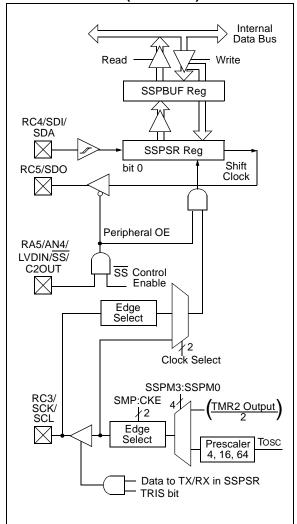

## 7.8 Resetting Timer1 Using a CCP Trigger Output

If the CCP1 module is configured in Compare mode to generate a "special event trigger" signal (CCP1M3:CCP1M0 = 1011), the signal will reset Timer1 and start an A/D conversion (if the A/D module is enabled).

| Note: | The special event triggers from the CCP1 |      |     |     |           |      |      |  |  |

|-------|------------------------------------------|------|-----|-----|-----------|------|------|--|--|

|       | module                                   | will | not | set | interrupt | flag | bit, |  |  |

|       | TMR1IF (PIR1<0>).                        |      |     |     |           |      |      |  |  |

Timer1 must be configured for either Timer or Synchronized Counter mode to take advantage of this feature. If Timer1 is running in Asynchronous Counter mode, this Reset operation may not work.

In the event that a write to Timer1 coincides with a special event trigger from CCP1, the write will take precedence.

In this mode of operation, the CCPR1H:CCPR1L register pair effectively becomes the period register for Timer1.

NOTES:

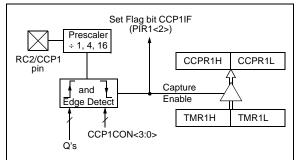

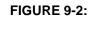

## 9.4 Capture Mode

In Capture mode, CCPR1H:CCPR1L captures the 16-bit value of the TMR1 register when an event occurs on pin RC2/CCP1. An event is defined as one of the following and is configured by CCPxCON<3:0>:

- Every falling edge

- Every rising edge

- Every 4th rising edge

- Every 16th rising edge

An event is selected by control bits, CCP1M3:CCP1M0 (CCP1CON<3:0>). When a capture is made, the interrupt request flag bit, CCP1IF (PIR1<2>), is set. The interrupt flag must be cleared in software. If another capture occurs before the value in register CCPR1 is read, the old captured value is overwritten by the new captured value.

#### 9.4.1 CCP PIN CONFIGURATION

In Capture mode, the RC2/CCP1 pin should be configured as an input by setting the TRISC<2> bit.

| Note: | If the RC2/CCP1 pin is configured as an |  |  |  |  |

|-------|-----------------------------------------|--|--|--|--|

|       | output, a write to the port can cause a |  |  |  |  |

|       | capture condition.                      |  |  |  |  |

#### FIGURE 9-1: CAPTURE MODE OPERATION BLOCK DIAGRAM

## 9.4.2 TIMER1 MODE SELECTION

Timer1 must be running in Timer mode or Synchronized Counter mode for the CCP module to use the capture feature. In Asynchronous Counter mode, the capture operation may not work.

### 9.4.3 SOFTWARE INTERRUPT

When the Capture mode is changed, a false capture interrupt may be generated. The user should keep bit, CCP1IE (PIE1<2>), clear to avoid false interrupts and should clear the flag bit, CCP1IF, following any such change in operating mode.

### 9.4.4 CCP PRESCALER

There are four prescaler settings specified by bits, CCP1M3:CCP1M0. Whenever the CCP module is turned off, or the CCP module is not in Capture mode, the prescaler counter is cleared. Any Reset will clear the prescaler counter.

Switching from one capture prescaler to another may generate an interrupt. Also, the prescaler counter will not be cleared, therefore, the first capture may be from a non-zero prescaler. Example 9-1 shows the recommended method for switching between capture prescalers. This example also clears the prescaler counter and will not generate the "false" interrupt.

#### EXAMPLE 9-1: CHANGING BETWEEN CAPTURE PRESCALERS

| CLRF  | CCP1CON     | ;Turn CCP module off    |

|-------|-------------|-------------------------|

| MOVLW | NEW_CAPT_PS | ;Load the W reg with    |

|       |             | ;the new prescaler      |

|       |             | ;move value and CCP ON  |

| MOVWF | CCP1CON     | ;Load CCP1CON with this |

|       |             | ;value                  |

|       |             |                         |

## 9.5 Compare Mode

In Compare mode, the 16-bit CCPR1 register value is constantly compared against the TMR1 register pair value. When a match occurs, the RC2/CCP1 pin is:

- Driven high

- Driven low

- Remains unchanged

The action on the pin is based on the value of control bits, CCP1M3:CCP1M0 (CCP1CON<3:0>). At the same time, interrupt flag bit CCP1IF is set.

#### COMPARE MODE OPERATION BLOCK DIAGRAM

Special Event Trigger will:

- clear TMR1H and TMR1L registers

- NOT set interrupt flag bit, TMR1IF (PIR1<0>)

- (for CCP2 only) set the GO/DONE bit (ADCON0<2>)

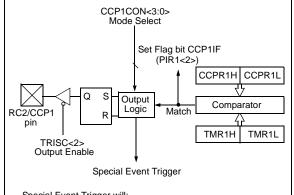

## 10.0 MASTER SYNCHRONOUS SERIAL PORT (MSSP) MODULE

### 10.1 Master SSP (MSSP) Module Overview

The Master Synchronous Serial Port (MSSP) module is a serial interface, useful for communicating with other peripheral or microcontroller devices. These peripheral devices may be serial EEPROMs, shift registers, display drivers, A/D converters, etc. The MSSP module can operate in one of two modes:

- Serial Peripheral Interface (SPI)

- Inter-Integrated Circuit (I<sup>2</sup>C<sup>™</sup>)

- Full Master mode

- Slave mode (with general address call)

The I<sup>2</sup>C interface supports the following modes in hardware:

- Master mode

- Multi-Master mode

- Slave mode

## 10.2 Control Registers

The MSSP module has three associated registers. These include a status register (SSPSTAT) and two control registers (SSPCON and SSPCON2). The use of these registers and their individual configuration bits differ significantly, depending on whether the MSSP module is operated in SPI or  $I^2C$  mode.

Additional details are provided under the individual sections.

## 10.3 SPI Mode

The SPI mode allows 8 bits of data to be synchronously transmitted and received simultaneously. All four modes of SPI are supported. To accomplish communication, typically three pins are used:

- Serial Data Out (SDO) RC5/SDO

- Serial Data In (SDI) RC4/SDI/SDA

- Serial Clock (SCK) RC3/SCK/SCL

Additionally, a fourth pin may be used when in a Slave mode of operation:

Slave Select (SS) – RA5/AN4/LVDIN/SS/C2OUT

Figure 10-1 shows the block diagram of the MSSP module when operating in SPI mode.

#### FIGURE 10-1:

#### MSSP BLOCK DIAGRAM (SPI MODE)

### 10.4.10 I<sup>2</sup>C MASTER MODE TRANSMISSION

Transmission of a data byte, a 7-bit address or the other half of a 10-bit address, is accomplished by simply writing a value to the SSPBUF register. This action will set the Buffer Full flag bit, BF and allow the Baud Rate Generator to begin counting and start the next transmission. Each bit of address/data will be shifted out onto the SDA pin after the falling edge of SCL is asserted (see data hold time specification parameter #106). SCL is held low for one Baud Rate Generator rollover count (TBRG). Data should be valid before SCL is released high (see data setup time specification parameter #107). When the SCL pin is released high, it is held that way for TBRG. The data on the SDA pin must remain stable for that duration and some hold time after the next falling edge of SCL. After the eighth bit is shifted out (the falling edge of the eighth clock), the BF flag is cleared and the master releases SDA. This allows the slave device being addressed to respond with an ACK bit, during the ninth bit time, if an address match occurred or if data was received properly. The status of ACK is written into the ACKDT bit on the falling edge of the ninth clock. If the master receives an Acknowledge, the Acknowledge Status bit, ACKSTAT, is cleared. If not, the bit is set. After the ninth clock, the SSPIF bit is set and the master clock (Baud Rate Generator) is suspended until the next data byte is loaded into the SSPBUF, leaving SCL low and SDA unchanged (Figure 10-21).

After the write to the SSPBUF, each bit of address will be shifted out on the falling edge of SCL until all seven address bits and the R/W bit are completed. On the falling edge of the eighth clock, the master will deassert the SDA pin, allowing the slave to respond with an Acknowledge. On the falling edge of the ninth clock, the master will sample the SDA pin to see if the address was recognized by a slave. The status of the ACK bit is loaded into the ACKSTAT status bit (SSPCON2<6>). Following the falling edge of the ninth clock transmission of the address, the SSPIF is set, The BF flag Is cleared and the Baud Rate Generator is turned off until another write to the SSPBUF takes place, holding SCL low and allowing SDA to float.

### 10.4.10.1 BF Status Flag

In Transmit mode, the BF bit (SSPSTAT<0>) is set when the CPU writes to SSPBUF and is cleared when all 8 bits are shifted out.

### 10.4.10.2 WCOL Status Flag

If the user writes the SSPBUF when a transmit is already in progress (i.e., SSPSR is still shifting out a data byte), the WCOL is set and the contents of the buffer are unchanged (the write doesn't occur).

WCOL must be cleared in software.

### 10.4.10.3 ACKSTAT Status Flag

In Transmit mode, the ACKSTAT bit (SSPCON2<6>) is cleared when the slave has sent an Acknowledge  $(\overline{ACK} = 0)$  and is set when the slave does not Acknowledge  $(\overline{ACK} = 1)$ . A slave sends an Acknowledge when it has recognized its address (including a general call) or when the slave has properly received its data.

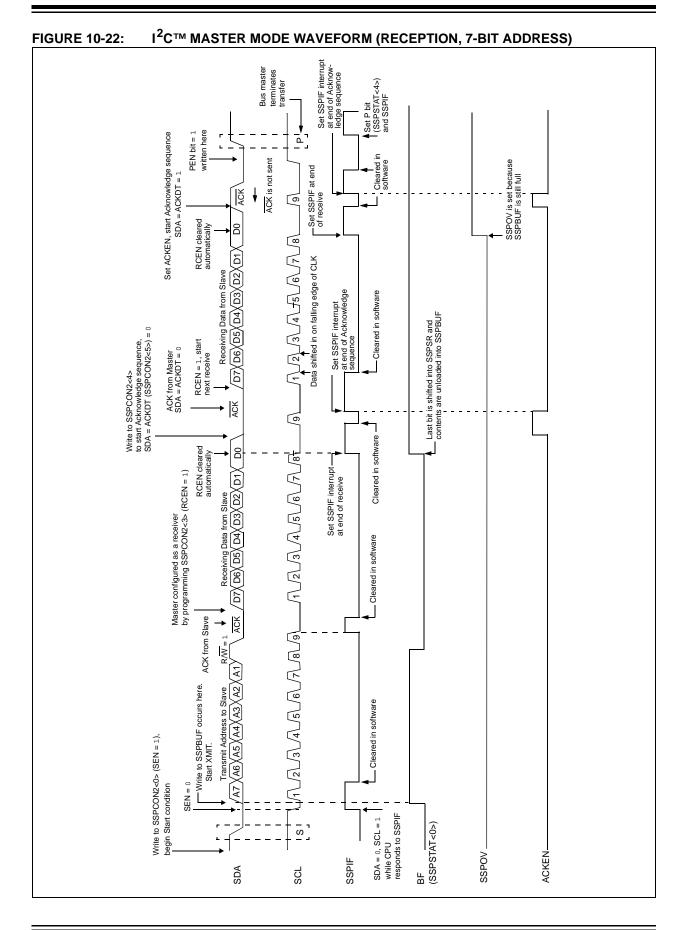

## 10.4.11 I<sup>2</sup>C MASTER MODE RECEPTION

Master mode reception is enabled by programming the Receive Enable bit, RCEN (SSPCON2<3>).

Note: The MSSP module must be in an Idle state before the RCEN bit is set or the RCEN bit will be disregarded.

The Baud Rate Generator begins counting and on each rollover, the state of the SCL pin changes (high-to-low/ low-to-high) and data is shifted into the SSPSR. After the falling edge of the eighth clock, the receive enable flag is automatically cleared, the contents of the SSPSR are loaded into the SSPBUF, the BF flag bit is set, the SSPIF flag bit is set and the Baud Rate Generator is suspended from counting, holding SCL low. The MSSP is now in Idle state, awaiting the next command. When the buffer is read by the CPU, the BF flag bit is automatically cleared. The user can then send an Acknowledge bit at the end of reception by setting the Acknowledge Sequence Enable bit, ACKEN (SSPCON2<4>).

### 10.4.11.1 BF Status Flag

In receive operation, the BF bit is set when an address or data byte is loaded into SSPBUF from SSPSR. It is cleared when the SSPBUF register is read.

### 10.4.11.2 SSPOV Status Flag

In receive operation, the SSPOV bit is set when 8 bits are received into the SSPSR and the BF flag bit is already set from a previous reception.

### 10.4.11.3 WCOL Status Flag

If the user writes the SSPBUF when a receive is already in progress (i.e., SSPSR is still shifting in a data byte), the WCOL bit is set and the contents of the buffer are unchanged (the write doesn't occur).

### 11.4 AUSART Synchronous Slave Mode

Synchronous Slave mode differs from the Master mode in the fact that the shift clock is supplied externally at the RC6/TX/CK pin (instead of being supplied internally in Master mode). This allows the device to transfer or receive data while in Sleep mode. Slave mode is entered by clearing bit, CSRC (TXSTA<7>).

#### 11.4.1 AUSART SYNCHRONOUS SLAVE TRANSMIT

The operation of the Synchronous Master and Slave modes is identical, except in the case of Sleep mode.

If two words are written to the TXREG and then the SLEEP instruction is executed, the following will occur:

- a) The first word will immediately transfer to the TSR register and transmit.

- b) The second word will remain in the TXREG register.

- c) Flag bit TXIF will not be set.

- When the first word has been shifted out of TSR, the TXREG register will transfer the second word to the TSR and flag bit TXIF will now be set.

- e) If enable bit TXIE is set, the interrupt will wake the chip from Sleep and if the global interrupt is enabled, the program will branch to the interrupt vector (0004h).

When setting up a Synchronous Slave Transmission, follow these steps:

- Enable the synchronous slave serial port by setting bits SYNC and SPEN and clearing bit CSRC.

- 2. Clear bits CREN and SREN.

- 3. If interrupts are desired, then set enable bit TXIE.

- 4. If 9-bit transmission is desired, then set bit TX9.

- 5. Enable the transmission by setting enable bit TXEN.

- 6. If 9-bit transmission is selected, the ninth bit should be loaded in bit TX9D.

- 7. Start transmission by loading data to the TXREG register.

- 8. If using interrupts, ensure that GIE and PEIE (bits 7 and 6) of the INTCON register are set.

| Address                | Name                                 | Bit 7                           | Bit 6 | Bit 5  | Bit 4  | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value<br>POR, |      | Valu<br>all o<br>Res | ther |

|------------------------|--------------------------------------|---------------------------------|-------|--------|--------|-------|--------|--------|--------|---------------|------|----------------------|------|

| 0Bh, 8Bh,<br>10Bh,18Bh | INTCON                               | GIE                             | PEIE  | TMR0IE | INT0IE | RBIE  | TMR0IF | INTOIF | RBIF   | 0000          | 000x | 0000                 | 000u |

| 0Ch                    | PIR1                                 | PSPIF <sup>(1)</sup>            | ADIF  | RCIF   | TXIF   | SSPIF | CCP1IF | TMR2IF | TMR1IF | 0000          | 0000 | 0000                 | 0000 |

| 18h                    | RCSTA                                | SPEN                            | RX9   | SREN   | CREN   | ADDEN | FERR   | OERR   | RX9D   | 0000          | 000x | 0000                 | 000x |

| 19h                    | TXREG                                | G AUSART Transmit Data Register |       |        |        |       |        |        |        | 0000          | 0000 | 0000                 | 0000 |

| 8Ch                    | PIE1                                 | PSPIE <sup>(1)</sup>            | ADIE  | RCIE   | TXIE   | SSPIE | CCP1IE | TMR2IE | TMR1IE | 0000          | 0000 | 0000                 | 0000 |

| 98h                    | TXSTA                                | CSRC                            | TX9   | TXEN   | SYNC   | —     | BRGH   | TRMT   | TX9D   | 0000          | -010 | 0000                 | -010 |

| 99h                    | h SPBRG Baud Rate Generator Register |                                 |       |        |        |       | 0000   | 0000   | 0000   | 0000          |      |                      |      |

### TABLE 11-12: REGISTERS ASSOCIATED WITH SYNCHRONOUS SLAVE TRANSMISSION

**Legend:** x = unknown, - = unimplemented, read as '0'. Shaded cells are not used for synchronous slave transmission.

Note 1: Bits PSPIE and PSPIF are reserved on 28-pin devices; always maintain these bits clear.

#### 11.4.2 AUSART SYNCHRONOUS SLAVE RECEPTION

The operation of the Synchronous Master and Slave modes is identical, except in the case of Sleep mode. Bit SREN is a "don't care" in Slave mode.

If receive is enabled by setting bit CREN prior to the SLEEP instruction, then a word may be received during Sleep. On completely receiving the word, the RSR register will transfer the data to the RCREG register and if enable bit RCIE bit is set, the interrupt generated will wake the chip from Sleep. If the global interrupt is enabled, the program will branch to the interrupt vector (0004h).

When setting up a Synchronous Slave Reception, follow these steps:

- 1. Enable the synchronous master serial port by setting bits SYNC and SPEN and clearing bit CSRC.

- 2. If interrupts are desired, set enable bit RCIE.

- 3. If 9-bit reception is desired, set bit RX9.

- 4. To enable reception, set enable bit CREN.

- 5. Flag bit RCIF will be set when reception is complete and an interrupt will be generated if enable bit RCIE was set.

- 6. Read the RCSTA register to get the ninth bit (if enabled) and determine if any error occurred during reception.

- 7. Read the 8-bit received data by reading the RCREG register.

- 8. If any error occurred, clear the error by clearing bit CREN.

- 9. If using interrupts, ensure that GIE and PEIE (bits 7 and 6) of the INTCON register are set.

#### TABLE 11-13: REGISTERS ASSOCIATED WITH SYNCHRONOUS SLAVE RECEPTION

| Address                                | Name   | Bit 7                | Bit 6   | Bit 5     | Bit 4  | Bit 3 | Bit 2     | Bit 1     | Bit 0  | Value on:<br>POR, BOR | Value on<br>all other<br>Resets |

|----------------------------------------|--------|----------------------|---------|-----------|--------|-------|-----------|-----------|--------|-----------------------|---------------------------------|

| 0Bh, 8Bh,<br>10Bh,18Bh                 | INTCON | GIE                  | PEIE    | TMR0IE    | INT0IE | RBIE  | TMR0IF    | INTOIF    | RBIF   | 0000 000x             | 0000 000u                       |

| 0Ch                                    | PIR1   | PSPIF <sup>(1)</sup> | ADIF    | RCIF      | TXIF   | SSPIF | CCP1IF    | TMR2IF    | TMR1IF | 0000 0000             | 0000 0000                       |

| 18h                                    | RCSTA  | SPEN                 | RX9     | SREN      | CREN   | ADDEN | FERR      | OERR      | RX9D   | 0000 000x             | 0000 000x                       |

| 1Ah                                    | RCREG  | AUSART               | Receive | Data Regi | ster   |       |           |           |        | 0000 0000             | 0000 0000                       |

| 8Ch                                    | PIE1   | PSPIE <sup>(1)</sup> | ADIE    | RCIE      | TXIE   | SSPIE | CCP1IE    | TMR2IE    | TMR1IE | 0000 0000             | 0000 0000                       |

| 98h                                    | TXSTA  | CSRC                 | TX9     | TXEN      | SYNC   | —     | BRGH      | TRMT      | TX9D   | 0000 -010             | 0000 -010                       |

| 99h SPBRG Baud Rate Generator Register |        |                      |         |           |        |       | 0000 0000 | 0000 0000 |        |                       |                                 |

Legend: x = unknown, — = unimplemented, read as '0'. Shaded cells are not used for synchronous slave reception.

Note 1: Bits PSPIE and PSPIF are reserved on 28-pin devices, always maintain these bits clear.

### 15.10.1 REFERENCE VOLTAGE SET POINT

The internal reference voltage of the LVD module may be used by other internal circuitry (the Programmable Brown-out Reset). If these circuits are disabled (lower current consumption), the reference voltage circuit requires a time to become stable before a low-voltage condition can be reliably detected. This time is invariant of system clock speed. This start-up time is specified in electrical specification parameter #36. The low-voltage interrupt flag will not be enabled until a stable reference voltage is reached. Refer to the waveform in Figure 15-6.

#### 15.10.2 CURRENT CONSUMPTION

When the module is enabled, the LVD comparator and voltage divider are enabled and will consume static current. The voltage divider can be tapped from multiple places in the resistor array. Total current consumption, when enabled, is specified in electrical specification parameter #D022B.

## 15.11 Operation During Sleep

When enabled, the LVD circuitry continues to operate during Sleep. If the device voltage crosses the trip point, the LVDIF bit will be set and the device will wakeup from Sleep. Device execution will continue from the interrupt vector address if interrupts have been globally enabled.

## 15.12 Effects of a Reset

A device Reset forces all registers to their Reset state. This forces the LVD module to be turned off.

Note: If the LVD is enabled and the BOR module is not enabled, the band gap will require a start-up time of no more than 50 μs before the band gap reference is stable. Before enabling the LVD interrupt, the user should ensure that the band gap reference voltage is stable by monitoring the IRVST bit in the LVDCON register. The LVD could cause erroneous interrupts before the band gap is stable.

#### 15.13 Time-out Sequence

On power-up, the time-out sequence is as follows: the PWRT delay starts (if enabled) when a POR occurs; then, OST starts counting 1024 oscillator cycles when PWRT ends (LP, XT, HS); when the OST ends, the device comes out of Reset.

If  $\overline{\text{MCLR}}$  is kept low long enough, all delays will expire. Bringing  $\overline{\text{MCLR}}$  high will begin execution immediately. This is useful for testing purposes or to synchronize more than one PIC16F7X7 device operating in parallel.

Table 15-3 shows the Reset conditions for the Status, PCON and PC registers, while Table 15-4 shows the Reset conditions for all the registers.

### 15.14 Power Control/Status Register (PCON)

The Power Control/Status register, PCON, has two bits to indicate the type of Reset that last occurred.

Bit 0 is Brown-out Reset status bit, BOR. Bit BOR is unknown on a Power-on Reset. It must then be set by the user and checked on subsequent Resets to see if bit BOR cleared, indicating a Brown-out Reset occurred. When the Brown-out Reset is disabled, the state of the BOR bit is unpredictable.

Bit 1 is Power-on Reset Status bit, POR. It is cleared on a Power-on Reset and unaffected otherwise. The user must set this bit following a Power-on Reset.

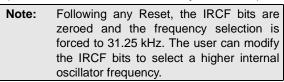

#### 15.17.3 TWO-SPEED CLOCK START-UP MODE

Two-Speed Start-up minimizes the latency between oscillator start-up and code execution that may be selected with the IESO (Internal/External Switchover) bit in Configuration Word Register 2. This mode is achieved by initially using the INTRC for code execution until the primary oscillator is stable.

If this mode is enabled and any of the following conditions exist, the system will begin execution with the INTRC oscillator. This results in almost immediate code execution with a minimum of delay.

- POR and after the Power-up Timer has expired (if <u>PWRTEN</u> = 0)

- or following a wake-up from Sleep

- or a Reset, when running from T1OSC or INTRC (after a Reset, SCS<1:0> are always set to '00').

If the primary oscillator is configured to be anything other than XT, LP or HS, then Two-Speed Start-up is disabled because the primary oscillator will not require any time to become stable after POR or an exit from Sleep.

If the IRCF bits of the OSCCON register are configured to a non-zero value prior to entering Sleep mode, the secondary system clock frequency will come from the output of the INTOSC. The IOFS bit in the OSCCON register will be clear until the INTOSC is stable. This will allow the user to determine when the internal oscillator can be used for time critical applications. Checking the state of the OSTS bit will confirm whether the primary clock configuration is engaged. If not, the OSTS bit will remain clear.

When the device is auto-configured in INTRC mode following a POR or wake-up from Sleep, the rules for entering other oscillator modes still apply, meaning the SCS<1:0> bits in OSCCON can be modified before the OST time-out has occurred. This would allow the application to wake-up from Sleep, perform a few instructions using the INTRC as the clock source and go back to Sleep without waiting for the primary oscillator to become stable.

Note: Executing a SLEEP instruction will abort the oscillator start-up time and will cause the OSTS bit to remain clear.

15.17.3.1 Two-Speed Start-up Sequence

- 1. Wake-up from Sleep, Reset or POR.

- OSCON bits configured to run from INTRC (31.25 kHz).

- Instructions begin execution by INTRC (31.25 kHz).

- 4. OST enabled to count 1024 clock cycles.

- 5. OST timed out, wait for falling edge of INTRC.

- 6. OSTS is set.

- 7. System clock held low for eight falling edges of new clock (LP, XT or HS).

- 8. System clock is switched to primary source (LP, XT or HS).

The software may read the OSTS bit to determine when the switchover takes place so that any software timing edges can be adjusted.

#### FIGURE 15-13: TWO-SPEED START-UP

## 18.2 DC Characteristics: Power-Down and Supply Current PIC16F737/747/767/777 (Industrial, Extended) PIC16LF737/747/767/777 (Industrial) (Continued)

| PIC16LF737/747/767/777<br>(Industrial) |                                       | Standard Operating Conditions (unless otherwise stated)   Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial   Standard Operating Conditions (unless otherwise stated)   Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial $-40^{\circ}C \le TA \le +85^{\circ}C$ for extended |     |       |            |            |                                       |  |  |

|----------------------------------------|---------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------|------------|------------|---------------------------------------|--|--|

| PIC16F7<br>(Indu                       |                                       |                                                                                                                                                                                                                                                                                                                                   |     |       |            |            |                                       |  |  |

| Param<br>No.                           | Device                                | Тур                                                                                                                                                                                                                                                                                                                               | Max | Units | Conditions |            |                                       |  |  |

|                                        | Supply Current (IDD) <sup>(2,3)</sup> |                                                                                                                                                                                                                                                                                                                                   |     |       |            |            |                                       |  |  |

|                                        | PIC16LF7X7                            | .950                                                                                                                                                                                                                                                                                                                              | 1.3 | mA    | -40°C      |            |                                       |  |  |

|                                        |                                       | .930                                                                                                                                                                                                                                                                                                                              | 1.2 | mA    | +25°C      | VDD = 3.0V |                                       |  |  |

|                                        |                                       | .930                                                                                                                                                                                                                                                                                                                              | 1.2 | mA    | +85°C      | VDD = 5.0V | Fosc = 8 MHz<br>( <b>RC_RUN</b> mode, |  |  |

|                                        | All devices                           | 1.8                                                                                                                                                                                                                                                                                                                               | 3.0 | mA    | -40°C      |            |                                       |  |  |

|                                        |                                       | 1.7                                                                                                                                                                                                                                                                                                                               | 2.8 | mA    | +25°C      |            | Internal RC Oscillator)               |  |  |

|                                        |                                       | 1.7                                                                                                                                                                                                                                                                                                                               | 2.8 | mA    | +85°C      | VDD = 3.0V |                                       |  |  |

|                                        | Extended devices                      | 2.0                                                                                                                                                                                                                                                                                                                               | 4.0 | mA    | +125°C     |            |                                       |  |  |

|                                        | PIC16LF7X7                            | 9                                                                                                                                                                                                                                                                                                                                 | 13  | μA    | -10°C      |            |                                       |  |  |

|                                        |                                       | 9                                                                                                                                                                                                                                                                                                                                 | 14  | μA    | +25°C      | VDD = 2.0V |                                       |  |  |

|                                        |                                       | 11                                                                                                                                                                                                                                                                                                                                | 16  | μΑ    | +70°C      |            |                                       |  |  |

|                                        | PIC16LF7X7                            | 12                                                                                                                                                                                                                                                                                                                                | 34  | μΑ    | -10°C      |            | Fosc = 32 kHz                         |  |  |

|                                        |                                       | 12                                                                                                                                                                                                                                                                                                                                | 31  | μA    | +25°C      | VDD = 3.0V | (SEC_RUN mode,                        |  |  |

|                                        |                                       | 14                                                                                                                                                                                                                                                                                                                                | 28  | μA    | +70°C      |            | Timer1 as Clock)                      |  |  |

|                                        | All devices                           | 20                                                                                                                                                                                                                                                                                                                                | 72  | μA    | -10°C      |            |                                       |  |  |

|                                        |                                       | 20                                                                                                                                                                                                                                                                                                                                | 65  | μA    | +25°C      | VDD = 5.0V |                                       |  |  |

|                                        |                                       | 25                                                                                                                                                                                                                                                                                                                                | 59  | μA    | +70°C      |            |                                       |  |  |

Legend: Shading of rows is to assist in readability of the table.

**Note 1:** The power-down current in Sleep mode does not depend on the oscillator type. Power-down current is measured with the part in Sleep mode, with all I/O pins in high-impedance state and tied to VDD or VSS and all features that add delta current disabled (such as WDT, Timer1 Oscillator, BOR, etc.).

2: The supply current is mainly a function of operating voltage, frequency and mode. Other factors, such as I/O pin loading and switching rate, oscillator type and circuit, internal code execution pattern and temperature, also have an impact on the current consumption.

The test conditions for all IDD measurements in active operation mode are:

OSC1 = external square wave, from rail-to-rail; all I/O pins tri-stated, pulled to VDD;

- MCLR = VDD; WDT enabled/disabled as specified.

- **3:** For RC oscillator configurations, current through REXT is not included. The current through the resistor can be estimated by the formula Ir = VDD/2REXT (mA) with REXT in kΩ.

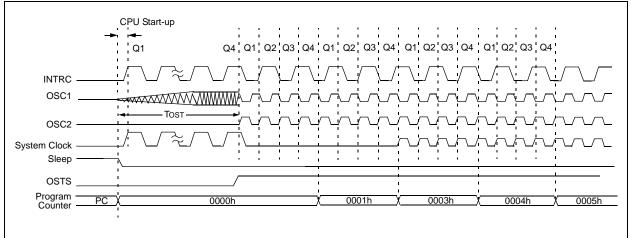

| Param<br>No. | Symbol | Characte                           | Min        | Тур†     | Max      | Units | Conditions |                                                                                                                                                                                                                              |

|--------------|--------|------------------------------------|------------|----------|----------|-------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 130          | TAD    | A/D Clock Period                   | PIC16F7X7  | 1.6      | _        | _     | μS         | Tosc based, VREF $\geq$ 3.0V                                                                                                                                                                                                 |

|              |        |                                    | PIC16LF7X7 | 3.0      | —        | _     | μS         | Tosc based, VREF $\geq 2.0V$                                                                                                                                                                                                 |

|              |        |                                    | PIC16F7X7  | 2.0      | 4.0      | 6.0   | μS         | A/D RC mode                                                                                                                                                                                                                  |

|              |        |                                    | PIC16LF7X7 | 3.0      | 6.0      | 9.0   | μS         | A/D RC mode                                                                                                                                                                                                                  |

| 131          | TCNV   | Conversion Time (not i<br>(Note 1) |            | —        | 12       | TAD   |            |                                                                                                                                                                                                                              |

| 132          | TACQ   | Acquisition Time                   |            | (Note 2) | 40       | _     | μS         |                                                                                                                                                                                                                              |

|              |        |                                    |            | 10*      | _        |       | μs         | The minimum time is the<br>amplifier settling time. This may<br>be used if the "new" input<br>voltage has not changed by<br>more than 1 LSb (i.e., 5.0 mV @<br>5.12V) from the last sampled<br>voltage (as stated on CHOLD). |

| 134          | TGO    | Q4 to A/D Clock Start              |            | _        | Tosc/2 § | _     | _          | If the A/D clock source is<br>selected as RC, a time of TCY is<br>added before the A/D clock<br>starts. This allows the SLEEP<br>instruction to be executed.                                                                 |

#### TABLE 18-16: A/D CONVERSION REQUIREMENTS

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

§ This specification ensured by design.

**Note 1:** ADRES register may be read on the following TCY cycle.

2: See Section 12.1 "A/D Acquisition Requirements" for minimum conditions.

NOTES:

| Device Differences |   |

|--------------------|---|

| Device Overview    | 5 |

| Features           | 5 |

| Direct Addressing  |   |

| -                  |   |

## Е

| Electrical Characteristics | 205 |

|----------------------------|-----|

| Errata                     | 4   |

| External Clock Input       |     |

## F

| Fail-Safe Clock Monitor | 169, | 189 |

|-------------------------|------|-----|

| FSR Register            |      | 30  |

| 1                                               |      |

|-------------------------------------------------|------|

| I/O Ports                                       | 49   |

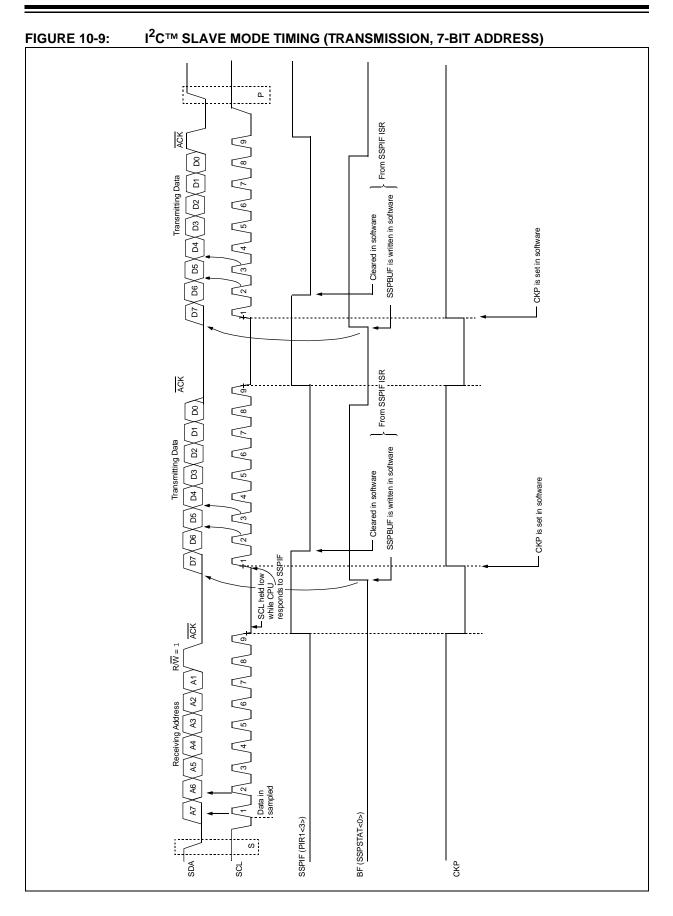

| l <sup>2</sup> Mode                             | 10   |

| Operation                                       | 106  |

| I <sup>2</sup> Slave Mode                       | 100  |

| Clock Stretching, 10-bit Receive                |      |

| Mode (SEN = 1)                                  | 112  |

| Clock Stretching, 10-bit Transmit Mode          |      |

| Clock Stretching, 7-bit Receive Mode (SEN = 1)  |      |

| Clock Stretching, 7-bit Transmit Mode (SEN = 1) |      |

| I <sup>2</sup> C Master Mode                    |      |

| Clock Arbitration                               |      |

| Operation                                       | -    |

| Reception                                       |      |

|                                                 |      |

| Repeated Start Condition Timing                 |      |

| Start Condition Timing<br>Transmission          |      |

|                                                 |      |

| I <sup>2</sup> C Mode                           |      |

| ACK Pulse                                       |      |

| Acknowledge Sequence Timing                     |      |

| Baud Rate Generator                             | 119  |

| Bus Collision                                   | 400  |

| Repeated Start Condition                        |      |

| Start Condition                                 | -    |

| Stop Condition                                  | 131  |

| Clock Synchronization and the CKP Bit           | 113  |

| Effect of a Reset                               |      |

| General Call Address Support                    | 116  |

| Multi-Master Communication, Bus Collision       |      |

| and Arbitration                                 |      |

| Multi-Master Mode                               | 127  |

| Read/Write Bit Information (R/W Bit)            |      |

| Registers                                       |      |

| Serial Clock (RC3/SCK/SCL)                      |      |

| Sleep Operation                                 |      |

| Stop Condition Timing                           |      |

| I <sup>2</sup> C Slave Mode                     |      |

| Addressing                                      |      |

| Clock Stretching                                |      |

| Reception                                       |      |

| Transmission                                    |      |

| ID Locations                                    | -, - |

| In-Circuit Debugger                             |      |

| In-Circuit Serial Programming                   | 169  |

| In-Circuit Serial Programming (ICSP)            | 192  |

| INDF Register                                   |      |

| Indirect Addressing                             | 30   |

| FSR Register                                    | 15   |

|                                                 |      |

| Instruction Set                                 |          |

|-------------------------------------------------|----------|

| Firmware Instructions 19                        |          |

| General Format 19                               |          |

| Opcode Field Descriptions 19                    |          |

| Read-Modify-Write Operations 19                 | 93       |

| ADDLW 19                                        | 95       |

| ADDWF 19                                        | 95       |

| ANDLW 19                                        | 95       |

| ANDWF 19                                        | 95       |

| BCF 19                                          | 95       |

| BSF19                                           | 95       |

| BTFSC 19                                        | 95       |

| BTFSS 19                                        | 95       |

| CALL                                            | 96       |

| CLRF                                            | 96       |

| CLRW 19                                         | 96       |

| CLRWDT 19                                       | 96       |

| COMF                                            | 96       |

| DECF                                            | 96       |

| DECFSZ 19                                       |          |

| GOTO                                            |          |

| INCF                                            |          |

| INCFSZ                                          |          |

| IORLW                                           |          |

| IORWF                                           |          |

| MOVF                                            |          |

| MOVLW                                           |          |

| MOVWF                                           |          |

| NOP                                             |          |

| RETFIE                                          |          |

| RETLW                                           |          |

| RETURN                                          |          |

| RLF                                             |          |

| RRF                                             |          |

| SLEEP                                           |          |

| SLEEP                                           |          |

|                                                 |          |

| SUBWF                                           |          |

| SWAPF                                           |          |

| XORLW                                           |          |

| XORWF                                           |          |

| Summary Table                                   | 94       |

| INT Interrupt (RB0/INT). See Interrupt Sources. |          |

| INTCON Register                                 |          |

| GIE Bit                                         |          |

| INTOIE Bit                                      | -0       |

| INTOIF Bit                                      |          |

| PEIE Bit                                        |          |

| RBIF Bit                                        |          |

| TMR0IE Bit 2                                    | 23       |

| Inter-Integrated Circuit. See I <sup>2</sup> C. |          |

| Internal Oscillator Block 3                     |          |

| INTRC Modes 3                                   |          |

| Internet Address 27                             |          |

| Interrupt Sources 169, 18                       |          |

| A/D Conversion Complete 15                      | 55       |

| Interrupt-on-Change (RB7:RB4)5                  | 56       |

| RB0/INT Pin, External 18                        |          |

|                                                 |          |

| TMR0 Overflow                                   |          |

| TMR0 Overflow                                   | 35       |

| TMR0 Overflow                                   | 35<br>48 |

| TMR0 Overflow                                   | 35<br>48 |