Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Product Status             | Active                                                                   |

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 32MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                        |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 16                                                                       |

| Program Memory Size        | 3.5KB (2K x 14)                                                          |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 256 x 8                                                                  |

| RAM Size                   | 256 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                              |

| Data Converters            | A/D 12x10b                                                               |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                       |

| Mounting Type              | Through Hole                                                             |

| Package / Case             | 18-DIP (0.300", 7.62mm)                                                  |

| Supplier Device Package    | 18-PDIP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f1826-e-p |

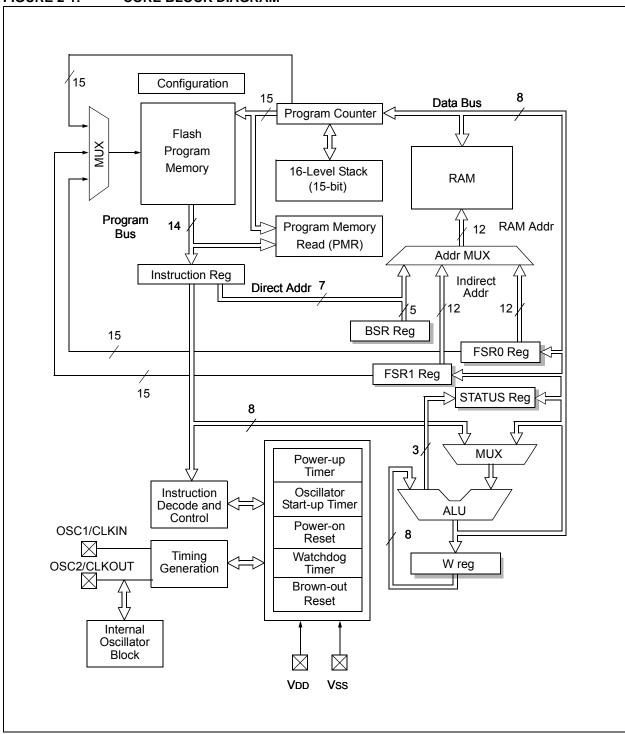

FIGURE 2-1: CORE BLOCK DIAGRAM

#### 3.0 MEMORY ORGANIZATION

There are three types of memory in PIC16(L)F1826/27: Data Memory, Program Memory and Data EEPROM Memory<sup>(1)</sup>.

- · Program Memory

- · Data Memory

- Core Registers

- Special Function Registers

- General Purpose RAM

- Common RAM

- Device Memory Maps

- Special Function Registers Summary

- Data EEPROM memory<sup>(1)</sup>

Note 1: The Data EEPROM Memory and the method to access Flash memory through the EECON registers is described in Section 11.0 "Data EEPROM and Flash Program Memory Control".

The following features are associated with access and control of program memory and data memory:

- · PCL and PCLATH

- Stack

- · Indirect Addressing

#### 3.1 Program Memory Organization

The enhanced mid-range core has a 15-bit program counter capable of addressing a 32K x 14 program memory space. Table 3-1 shows the memory sizes implemented for the PIC16(L)F1826/27 family. Accessing a location above these boundaries will cause a wrap-around within the implemented memory space. The Reset vector is at 0000h and the interrupt vector is at 0004h (see Figures 3-1 and 3-2).

TABLE 3-1: DEVICE SIZES AND ADDRESSES

| Device        | Program Memory Space (Words) | Last Program Memory Address |

|---------------|------------------------------|-----------------------------|

| PIC16(L)F1826 | 2,048                        | 07FFh                       |

| PIC16(L)F1827 | 4,096                        | 0FFFh                       |

**SPECIAL FUNCTION REGISTER SUMMARY TABLE 3-6:**

| Address | Name                | Bit 7                    | Bit 6            | Bit 5            | Bit 4          | Bit 3          | Bit 2   | Bit 1   | Bit 0                 | Value on<br>POR, BOR | Value on all<br>other<br>Resets |

|---------|---------------------|--------------------------|------------------|------------------|----------------|----------------|---------|---------|-----------------------|----------------------|---------------------------------|

| Bank 0  |                     |                          |                  |                  |                |                |         |         |                       |                      |                                 |

| 00Ch    | PORTA               | RA7                      | RA6              | RA5              | RA4            | RA3            | RA2     | RA1     | RA0                   | xxxx xxxx            | xxxx xxxx                       |

| 00Dh    | PORTB               | RB7                      | RB6              | RB5              | RB4            | RB3            | RB2     | RB1     | RB0                   | xxxx xxxx            | xxxx xxxx                       |

| 00Eh    | _                   | Unimplement              | ed               |                  |                |                |         |         |                       | _                    | _                               |

| 00Fh    | _                   | Unimplement              | ed               |                  |                |                |         |         |                       | _                    | _                               |

| 010h    | _                   | Unimplement              | ed               |                  |                |                |         |         |                       | _                    | _                               |

| 011h    | PIR1                | TMR1GIF                  | ADIF             | RCIF             | TXIF           | SSP1IF         | CCP1IF  | TMR2IF  | TMR1IF                | 0000 0000            | 0000 0000                       |

| 012h    | PIR2                | OSFIF                    | C2IF             | C1IF             | EEIF           | BCL1IF         | _       | _       | CCP2IF <sup>(1)</sup> | 0000 00              | 0000 00                         |

| 013h    | PIR3 <sup>(1)</sup> | _                        | ı                | CCP4IF           | CCP3IF         | TMR6IF         | _       | TMR4IF  | _                     | 00 0-0-              | 00 0-0-                         |

| 014h    | PIR4 <sup>(1)</sup> | _                        | ı                | ı                | _              | _              | _       | BCL2IF  | SSP2IF                | 00                   | 00                              |

| 015h    | TMR0                | Timer0 Modu              | le Register      |                  |                |                |         |         |                       | xxxx xxxx            | uuuu uuuu                       |

| 016h    | TMR1L               | Holding Regis            | ster for the Lea | ast Significant  | Byte of the 16 | 6-bit TMR1 Re  | egister |         |                       | xxxx xxxx            | uuuu uuuu                       |

| 017h    | TMR1H               | Holding Regis            | ster for the Mo  | st Significant I | Byte of the 16 | -bit TMR1 Re   | gister  |         |                       | xxxx xxxx            | uuuu uuuu                       |

| 018h    | T1CON               | TMR1CS1                  | TMR1CS0          | T1CKPS1          | T1CKPS0        | T10SCEN        | T1SYNC  | _       | TMR10N                | 0000 00-0            | uuuu uu-u                       |

| 019h    | T1GCON              | TMR1GE                   | T1GPOL           | T1GTM            | T1GSPM         | T1GGO/<br>DONE | T1GVAL  | T1GSS1  | T1GSS0                | 0000 0x00            | uuuu uxuu                       |

| 01Ah    | TMR2                | Timer2 Modu              | le Register      |                  |                |                |         |         |                       | 0000 0000            | 0000 0000                       |

| 01Bh    | PR2                 | Timer2 Period            | d Register       |                  |                |                |         |         |                       | 1111 1111            | 1111 1111                       |

| 01Ch    | T2CON               | _                        | T2OUTPS3         | T2OUTPS2         | T2OUTPS1       | T2OUTPS0       | TMR2ON  | T2CKPS1 | T2CKPS0               | -000 0000            | -000 0000                       |

| 01Dh    | _                   | Unimplement              | ed               |                  |                |                |         |         |                       | _                    | _                               |

| 01Eh    | CPSCON0             | CPSON                    | _                | _                | _              | CPSRNG1        | CPSRNG0 | CPSOUT  | T0XCS                 | 0 0000               | 0 0000                          |

| 01Fh    | CPSCON1             | _                        | _                | _                | _              | CPSCH3         | CPSCH2  | CPSCH1  | CPSCH0                | 0000                 | 0000                            |

| Bank 1  |                     |                          |                  |                  |                |                |         |         |                       |                      |                                 |

| 08Ch    | TRISA               | TRISA7                   | TRISA6           | TRISA5           | TRISA4         | TRISA3         | TRISA2  | TRISA1  | TRISA0                | 1111 1111            | 1111 1111                       |

| 08Dh    | TRISB               | TRISB7                   | TRISB6           | TRISB5           | TRISB4         | TRISB3         | TRISB2  | TRISB1  | TRISB0                | 1111 1111            | 1111 1111                       |

| 08Eh    | _                   | Unimplement              | ed               |                  |                |                |         |         |                       | _                    | _                               |

| 08Fh    | _                   | Unimplement              | ed               |                  |                |                |         |         |                       | _                    | _                               |

| 090h    | _                   | Unimplement              | ed               |                  |                |                |         |         |                       | _                    | _                               |

| 091h    | PIE1                | TMR1GIE                  | ADIE             | RCIE             | TXIE           | SSP1IE         | CCP1IE  | TMR2IE  | TMR1IE                | 0000 0000            | 0000 0000                       |

| 092h    | PIE2                | OSFIE                    | C2IE             | C1IE             | EEIE           | BCL1IE         | _       | _       | CCP2IE <sup>(1)</sup> | 0000 00              | 0000 00                         |

| 093h    | PIE3 <sup>(1)</sup> | _                        | _                | CCP4IE           | CCP3IE         | TMR6IE         | _       | TMR4IE  | _                     | 00 0-0-              | 00 0-0-                         |

| 094h    | PIE4 <sup>(1)</sup> | _                        | _                | _                | _              | _              | _       | BCL2IE  | SSP2IE                | 00                   | 00                              |

| 095h    | OPTION_REG          | WPUEN                    | INTEDG           | TMR0CS           | TMR0SE         | PSA            | PS2     | PS1     | PS0                   | 1111 1111            | 1111 1111                       |

| 096h    | PCON                | STKOVF                   | STKUNF           | _                | _              | RMCLR          | RI      | POR     | BOR                   | 00 11qq              | qq qquu                         |

| 097h    | WDTCON              | _                        | _                | WDTPS4           | WDTPS3         | WDTPS2         | WDTPS1  | WDTPS0  | SWDTEN                |                      | 1                               |

| 098h    | OSCTUNE             | _                        | _                | TUN5             | TUN4           | TUN3           | TUN2    | TUN1    | TUN0                  | 00 0000              | 00 0000                         |

| 099h    | OSCCON              | SPLLEN                   | IRCF3            | IRCF2            | IRCF1          | IRCF0          | _       | SCS1    | SCS0                  | 0011 1-00            | 0011 1-00                       |

| 09Ah    | OSCSTAT             | T10SCR                   | PLLR             | OSTS             | HFIOFR         | HFIOFL         | MFIOFR  | LFIOFR  | HFIOFS                | 10q0 0q00            | qqqq qq0q                       |

| 09Bh    | ADRESL              | A/D Result Register Low  |                  |                  |                |                |         |         |                       | xxxx xxxx            | uuuu uuuu                       |

| 09Ch    | ADRESH              | A/D Result Register High |                  |                  |                |                |         |         |                       | xxxx xxxx            | uuuu uuuu                       |

| 09Dh    | ADCON0              | _                        | CHS4             | CHS3             | CHS2           | CHS1           | CHS0    | GO/DONE | ADON                  | -000 0000            | -000 0000                       |

| 09Eh    | ADCON1              | ADFM                     | ADCS2            | ADCS1            | ADCS0          | _              | ADNREF  | ADPREF1 | ADPREF0               | 0000 -000            | 0000 -000                       |

| 09Fh    | _                   | Unimplement              |                  |                  |                |                |         |         |                       | _                    | _                               |

| Legend: |                     | = unknown 11 = unchanged |                  |                  |                |                |         |         |                       |                      |                                 |

Legend: x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, r = reserved. Shaded locations are unimplemented, read as '0'.

Note 1: PIC16(L)F1827 only.

#### 8.6.3 PIE2 REGISTER

The PIE2 register contains the interrupt enable bits, as shown in Register 8-3.

**Note:** Bit PEIE of the INTCON register must be set to enable any peripheral interrupt.

#### REGISTER 8-3: PIE2: PERIPHERAL INTERRUPT ENABLE REGISTER 2

| R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | U-0 | U-0 | R/W-0/0               |

|---------|---------|---------|---------|---------|-----|-----|-----------------------|

| OSFIE   | C2IE    | C1IE    | EEIE    | BCL1IE  | _   | _   | CCP2IE <sup>(1)</sup> |

| bit 7   |         |         |         |         |     |     | bit 0                 |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7   | OSFIE: Oscillator Fail Interrupt Enable bit                                                                                    |

|---------|--------------------------------------------------------------------------------------------------------------------------------|

|         | <ul><li>1 = Enables the Oscillator Fail interrupt</li><li>0 = Disables the Oscillator Fail interrupt</li></ul>                 |

| bit 6   | C2IE: Comparator C2 Interrupt Enable bit                                                                                       |

|         | <ul><li>1 = Enables the Comparator C2 interrupt</li><li>0 = Disables the Comparator C2 interrupt</li></ul>                     |

| bit 5   | C1IE: Comparator C1 Interrupt Enable bit                                                                                       |

|         | 1 = Enables the Comparator C1 interrupt                                                                                        |

|         | 0 = Disables the Comparator C1 interrupt                                                                                       |

| bit 4   | <b>EEIE:</b> EEPROM Write Completion Interrupt Enable bit                                                                      |

|         | <ul><li>1 = Enables the EEPROM Write Completion interrupt</li><li>0 = Disables the EEPROM Write Completion interrupt</li></ul> |

| bit 3   | BCL1IE: MSSP1 Bus Collision Interrupt Enable bit                                                                               |

|         | <ul><li>1 = Enables the MSSP1 Bus Collision Interrupt</li><li>0 = Disables the MSSP1 Bus Collision Interrupt</li></ul>         |

| bit 2-1 | Unimplemented: Read as '0'                                                                                                     |

| bit 0   | CCP2IE: CCP2 Interrupt Enable bit                                                                                              |

|         | 1 = Enables the CCP2 interrupt                                                                                                 |

|         | 0 = Disables the CCP2 interrupt                                                                                                |

**Note 1:** PIC16(L)F1827 only.

#### 12.1 Alternate Pin Function

The Alternate Pin Function Control (APFCON0 and APFCON1) registers are used to steer specific peripheral input and output functions between different pins. The APFCON0 and APFCON1 registers are shown in Register 12-1 and Register 12-2. For this device family, the following functions can be moved between different pins.

- RX/DT

- SDO1

- SS1 (Slave Select 1)

- P2B

- CCP2/P2A

- P1D

- P1C

- CCP1/P1A

- TX/CK

These bits have no effect on the values of any TRIS register. PORT and TRIS overrides will be routed to the correct pin. The unselected pin will be unaffected.

#### 12.3 PORTB and TRISB Registers

PORTB is an 8-bit wide, bidirectional port. The corresponding data direction register is TRISB (Register 12-9). Setting a TRISB bit (= 1) will make the corresponding PORTB pin an input (i.e., put the corresponding output driver in a High-Impedance mode). Clearing a TRISB bit (= 0) will make the corresponding PORTB pin an output (i.e., enable the output driver and put the contents of the output latch on the selected pin). Example 12-1 shows how to initialize an I/O port.

Reading the PORTB register (Register 12-8) reads the status of the pins, whereas writing to it will write to the PORT latch. All write operations are read-modify-write operations. Therefore, a write to a port implies that the port pins are read, this value is modified and then written to the PORT data latch.

The TRISB register (Register 12-9) controls the PORTB pin output drivers, even when they are being used as analog inputs. The user should ensure the bits in the TRISB register are maintained set when using them as analog inputs. I/O pins configured as analog input always read '0'.

#### 12.3.1 INTERRUPT-ON-CHANGE

All of the PORTB pins are individually configurable as an interrupt-on-change pin. Control bits IOCB<7:0> enable or disable the interrupt function for each pin. The interrupt-on-change feature is disabled on a Power-on Reset. Reference Section 13.0 "Interrupt-On-Change" for more information.

#### 12.3.2 WEAK PULL-UPS

Each of the PORTB pins has an individually configurable internal weak pull-up. Control bits WPUB<7:0> enable or disable each pull-up (see Register 12-11). Each weak pull-up is automatically turned off when the port pin is configured as an output. All pull-ups are disabled on a Power-on Reset by the WPUEN bit of the OPTION register.

#### 12.3.3 ANSELB REGISTER

The ANSELB register (Register 12-12) is used to configure the Input mode of an I/O pin to analog. Setting the appropriate ANSELB bit high will cause all digital reads on the pin to be read as '0' and allow analog functions on the pin to operate correctly.

The state of the ANSELB bits has no affect on digital output functions. A pin with TRIS clear and ANSELB set will still operate as a digital output, but the Input mode will be analog. This can cause unexpected behavior when executing read-modify-write instructions on the affected port.

The TRISB register (Register 12-9) controls the PORTB pin output drivers, even when they are being used as analog inputs. The user should ensure the bits in the TRISB register are maintained set when using them as analog inputs. I/O pins configured as analog input always read '0'.

Note:

The ANSELB register must be initialized to configure an analog channel as a digital input. Pins configured as analog inputs will read '0'.

#### 16.1 ADC Configuration

When configuring and using the ADC the following functions must be considered:

- · Port configuration

- · Channel selection

- · ADC voltage reference selection

- · ADC conversion clock source

- · Interrupt control

- · Result formatting

#### 16.1.1 PORT CONFIGURATION

The ADC can be used to convert both analog and digital signals. When converting analog signals, the I/O pin should be configured for analog by setting the associated TRIS and ANSEL bits. Refer to **Section 12.0 "I/O Ports"** for more information.

**Note:** Analog voltages on any pin that is defined as a digital input may cause the input buffer to conduct excess current.

#### 16.1.2 CHANNEL SELECTION

There are up to 15 channel selections available:

- AN<11:0> pins

- · Temperature Indicator

- DAC Output

- · FVR (Fixed Voltage Reference) Output

Refer to Section 14.0 "Fixed Voltage Reference (FVR)" and Section 15.0 "Temperature Indicator Module" for more information on these channel selections.

The CHS bits of the ADCON0 register determine which channel is connected to the sample and hold circuit.

When changing channels, a delay is required before starting the next conversion. Refer to **Section 16.2** "**ADC Operation**" for more information.

#### 16.1.3 ADC VOLTAGE REFERENCE

The ADPREF bits of the ADCON1 register provides control of the positive voltage reference. The positive voltage reference can be:

- VREF+ pin

- VDD

- FVR 2.048V

- FVR 4.096V (Not available on LF devices)

The ADNREF bits of the ADCON1 register provides control of the negative voltage reference. The negative voltage reference can be:

- VREF- pin

- Vss

See Section 14.0 "Fixed Voltage Reference (FVR)" for more details on the fixed voltage reference.

#### 16.1.4 CONVERSION CLOCK

The source of the conversion clock is software selectable via the ADCS bits of the ADCON1 register. There are seven possible clock options:

- Fosc/2

- Fosc/4

- Fosc/8

- Fosc/16

- Fosc/32

- Fosc/64

- · FRC (dedicated internal oscillator)

The time to complete one bit conversion is defined as TAD. One full 10-bit conversion requires 11.5 TAD periods as shown in Figure 16-2.

For correct conversion, the appropriate TAD specification must be met. Refer to the A/D conversion requirements in **Section 30.0** "**Electrical Specifications**" for more information. Table 16-1 gives examples of appropriate ADC clock selections.

Note: Unless using the FRC, any changes in the system clock frequency will change the ADC clock frequency, which may adversely affect the ADC result.

#### 16.2.6 A/D CONVERSION PROCEDURE

This is an example procedure for using the ADC to perform an Analog-to-Digital conversion:

- 1. Configure Port:

- Disable pin output driver (Refer to the TRIS register)

- Configure pin as analog (Refer to the ANSEL register)

- 2. Configure the ADC module:

- · Select ADC conversion clock

- · Configure voltage reference

- · Select ADC input channel

- · Turn on ADC module

- 3. Configure ADC interrupt (optional):

- · Clear ADC interrupt flag

- · Enable ADC interrupt

- · Enable peripheral interrupt

- Enable global interrupt<sup>(1)</sup>

- 4. Wait the required acquisition time<sup>(2)</sup>.

- 5. Start conversion by setting the GO/DONE bit.

- Wait for ADC conversion to complete by one of the following:

- Polling the GO/DONE bit

- Waiting for the ADC interrupt (interrupts enabled)

- 7. Read ADC Result.

- 8. Clear the ADC interrupt flag (required if interrupt is enabled).

- **Note 1:** The global interrupt can be disabled if the user is attempting to wake-up from Sleep and resume in-line code execution.

- 2: Refer to Section 16.4 "A/D Acquisition Requirements".

#### **EXAMPLE 16-1: A/D CONVERSION**

```

; This code block configures the ADC

; for polling, Vdd and Vss references, Frc

; clock and ANO input.

;Conversion start & polling for completion

; are included.

BANKSEL ADCON1

B'11110000' ;Right justify, Frc

MOVLW

;clock

MOVWF

ADCON1

;Vdd and Vss Vref

BANKSEL TRISA

BSF

TRISA,0

;Set RAO to input

BANKSEL ANSEL

BSF

ANSEL,0 ;Set RAO to analog

BANKSEL

ADCON0

B'00000001' ;Select channel AN0

MOVLW

MOVWE

;Turn ADC On

ADCON0

SampleTime ;Acquisiton delay

CALL

ADCON0, ADGO ; Start conversion

BSF

BTFSC

ADCON0, ADGO ; Is conversion done?

GOTO

$-1

;No, test again

ADRESH

BANKSEL

ADRESH,W ;Read upper 2 bits

MOVF

MOVWF

RESULTHI

;store in GPR space

BANKSEL

ADRESL

ADRESL,W

MOVF

;Read lower 8 bits

MOVWF

RESULTLO

;Store in GPR space

```

# 17.0 DIGITAL-TO-ANALOG CONVERTER (DAC) MODULE

The Digital-to-Analog Converter supplies a variable voltage reference, ratiometric with the input source, with 32 selectable output levels.

The input of the DAC can be connected to:

- · External VREF pins

- · VDD supply voltage

- FVR (Fixed Voltage Reference)

The output of the DAC can be configured to supply a reference voltage to the following:

- · Comparator positive input

- · ADC input channel

- DACOUT pin

- · Capacitive Sensing module (CSM)

The Digital-to-Analog Converter (DAC) can be enabled by setting the DACEN bit of the DACCON0 register.

#### 17.1 Output Voltage Selection

The DAC has 32 voltage level ranges. The 32 levels are set with the DACR<4:0> bits of the DACCON1 register.

The DAC output voltage is determined by the equations in Equation 17-1.

#### **EQUATION 17-1: DAC OUTPUT VOLTAGE**

#### IF DACEN = 1

$$VOUT = \left( (VSOURCE + - VSOURCE -) \times \frac{DACR[4:0]}{2^5} \right) + VSOURCE - VSOUR$$

#### IF DACEN = 0 and DACLPS = 1 and DACR[4:0] = 11111

VOUT = VSOURCE +

#### IF DACEN = 0 and DACLPS = 0 and DACR[4:0] = 00000

VOUT = VSOURCE -

VSOURCE+ = VDD, VREF, or FVR BUFFER 2

VSOURCE-=VSS

#### 17.2 Ratiometric Output Level

The DAC output value is derived using a resistor ladder with each end of the ladder tied to a positive and negative voltage reference input source. If the voltage of either input source fluctuates, a similar fluctuation will result in the DAC output value.

The value of the individual resistors within the ladder can be found in **Section 29.0** "**Electrical Specifications**".

#### 17.3 DAC Voltage Reference Output

The DAC can be output to the DACOUT pin by setting the DACOE bit of the DACCON0 register to '1'. Selecting the DAC reference voltage for output on the DACOUT pin automatically overrides the digital output buffer and digital input threshold detector functions of that pin. Reading the DACOUT pin when it has been configured for DAC reference voltage output will always return a '0'.

Due to the limited current drive capability, a buffer must be used on the DAC voltage reference output for external connections to DACOUT. Figure 17-2 shows an example buffering technique.

TABLE 21-5: SUMMARY OF REGISTERS ASSOCIATED WITH TIMER1

| Name    | Bit 7       | Bit 6          | Bit 5      | Bit 4         | Bit 3          | Bit 2     | Bit 1  | Bit 0  | Register on Page |

|---------|-------------|----------------|------------|---------------|----------------|-----------|--------|--------|------------------|

| ANSELB  | ANSB7       | ANSB6          | ANSB5      | ANSB4         | ANSB3          | ANSB2     | ANSB1  | _      | 128              |

| CCP1CON | PxM1        | PxM0           | DCxB1      | DCxB0         | CCPxM3         | CCPxM2    | CCPxM1 | CCPxM0 | 226              |

| INTCON  | GIE         | PEIE           | TMR0IE     | INTE          | IOCIE          | TMR0IF    | INTF   | IOCIF  | 86               |

| PIE1    | TMR1GIE     | ADIE           | RCIE       | TXIE          | SSP1IE         | CCP1IE    | TMR2IE | TMR1IE | 87               |

| PIR1    | TMR1GIF     | ADIF           | RCIF       | TXIF          | SSP1IF         | CCP1IF    | TMR2IF | TMR1IF | 91               |

| PORTB   | RB7         | RB6            | RB5        | RB4           | RB3            | RB2       | RB1    | RB0    | 127              |

| TMR1H   | Holding Reg | gister for the | Most Signi | ficant Byte o | of the 16-bit  | TMR1 Regi | ster   |        | 177*             |

| TMR1L   | Holding Reg | gister for the | Least Sign | ificant Byte  | of the 16-bit  | TMR1 Reg  | ister  |        | 177*             |

| TRISB   | TRISB7      | TRISB6         | TRISB5     | TRISB4        | TRISB3         | TRISB2    | TRISB1 | TRISB0 | 127              |

| T1CON   | TMR1CS1     | TMR1CS0        | T1CKPS1    | T1CKPS0       | T10SCEN        | T1SYNC    | _      | TMR10N | 185              |

| T1GCON  | TMR1GE      | T1GPOL         | T1GTM      | T1GSPM        | T1GGO/<br>DONE | T1GVAL    | T1GSS1 | T1GSS0 | 186              |

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used by the Timer1 module.

<sup>\*</sup> Page provides register information.

#### 24.5 CCP Control Registers

#### REGISTER 24-1: CCPxCON: CCPx CONTROL REGISTER

| R/W-00      | R/W-0/0 |

|-------------|---------|---------|---------|---------|---------|---------|---------|

| PxM<1:0>(1) |         | DCxE    | 3<1:0>  |         | CCPxI   | M<3:0>  |         |

| bit 7       |         |         |         |         |         |         | bit 0   |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unknown -n/n = Value at POR and BOR/Value at all other Reset

'1' = Bit is set '0' = Bit is cleared

bit 7-6 PxM<1:0>: Enhanced PWM Output Configuration bits<sup>(1)</sup>

Capture mode:

Unused

Compare mode:

Unused

If CCPxM<3:2> = 00, 01, 10:

xx = PxA assigned as Capture/Compare input; PxB, PxC, PxD assigned as port pins

If CCPxM<3:2> = 11:

00 = Single output; PxA modulated; PxB, PxC, PxD assigned as port pins

01 = Full-Bridge output forward; PxD modulated; PxA active; PxB, PxC inactive

10 = Half-Bridge output; PxA, PxB modulated with dead-band control; PxC, PxD assigned as port pins

11 = Full-Bridge output reverse; PxB modulated; PxC active; PxA, PxD inactive

bit 5-4 DCxB<1:0>: PWM Duty Cycle Least Significant bits

Capture mode:

Unused

Compare mode:

Unused

PWM mode:

These bits are the two LSbs of the PWM duty cycle. The eight MSbs are found in CCPRxL.

bit 3-0 CCPxM<3:0>: ECCPx Mode Select bits

0000 =Capture/Compare/PWM off (resets ECCPx module)

0001 =Reserved

0010 =Compare mode: toggle output on match

0011 =Reserved

0100 =Capture mode: every falling edge

0101 =Capture mode: every rising edge

0110 =Capture mode: every 4th rising edge

0111 =Capture mode: every 16th rising edge

1000 =Compare mode: initialize ECCPx pin low; set output on compare match (set CCPxIF)

1001 =Compare mode: initialize ECCPx pin high; clear output on compare match (set CCPxIF)

1010 =Compare mode: generate software interrupt only; ECCPx pin reverts to I/O state

1011 =Compare mode: Special Event Trigger (ECCPx resets Timer, sets CCPxIF bit, starts A/D conversion if A/D module is enabled)<sup>(1)</sup>

CCP Modules only:

11xx =PWM mode

**ECCP Modules only:**

1100 =PWM mode: PxA, PxC active-high; PxB, PxD active-high

1101 =PWM mode: PxA, PxC active-high; PxB, PxD active-low

1110 =PWM mode: PxA, PxC active-low; PxB, PxD active-high

1111 =PWM mode: PxA, PxC active-low; PxB, PxD active-low

Note 1: These bits are not implemented on CCP<4:3>.

#### REGISTER 24-4: PWMxCON: ENHANCED PWM CONTROL REGISTER

| R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0   | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|---------|---------|---------|---------|-----------|---------|---------|---------|

| PxRSEN  |         |         |         | PxDC<6:0> |         |         |         |

| bit 7   |         |         |         |           |         | _       | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7 PxRSEN: PWM Restart Enable bit

1 = Upon auto-shutdown, the CCPxASE bit clears automatically once the shutdown event goes away; the PWM restarts automatically

0 = Upon auto-shutdown, CCPxASE must be cleared in software to restart the PWM

bit 6-0 PxDC<6:0>: PWM Delay Count bits

PxDCx =Number of Fosc/4 (4 \* Tosc) cycles between the scheduled time when a PWM signal **should** transition active and the **actual** time it transitions active

Note 1: Bit resets to '0' with Two-Speed Start-up and LP, XT or HS selected as the Oscillator mode or Fail-Safe mode is enabled.

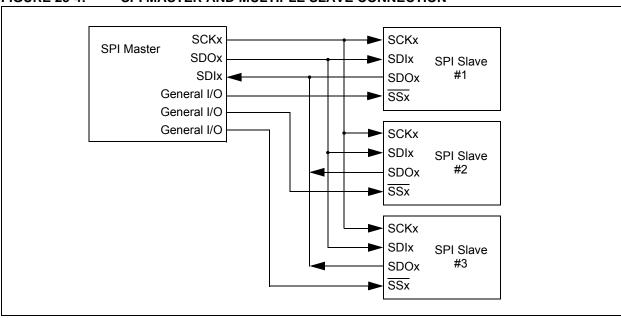

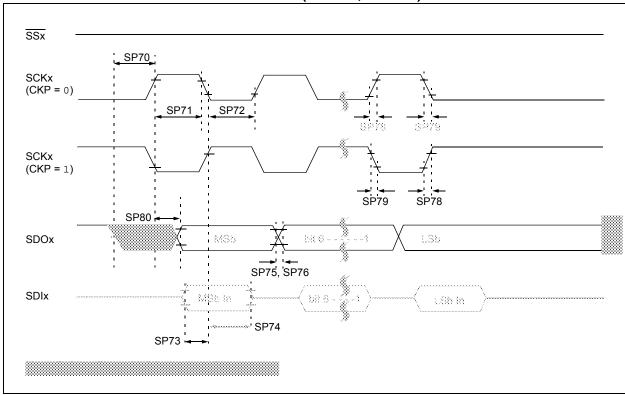

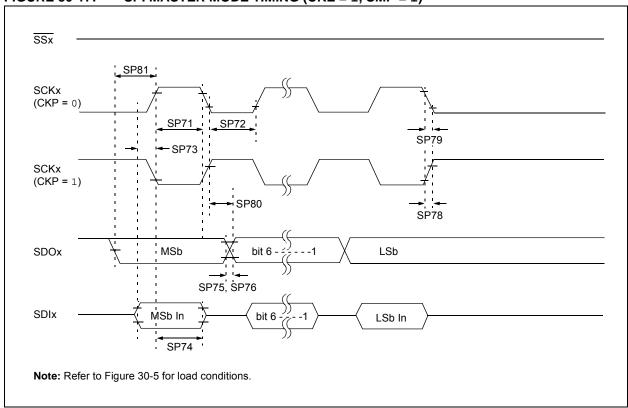

FIGURE 25-4: SPI MASTER AND MULTIPLE SLAVE CONNECTION

#### 25.2.1 SPI MODE REGISTERS

The MSSPx module has five registers for SPI mode operation. These are:

- MSSPx STATUS register (SSPxSTAT)

- MSSPx Control Register 1 (SSPxCON1)

- MSSPx Control Register 3 (SSPxCON3)

- MSSPx Data Buffer register (SSPxBUF)

- · MSSPx Address register (SSPxADD)

- MSSPx Shift register (SSPxSR) (Not directly accessible)

SSPxCON1 and SSPxSTAT are the control and STATUS registers in SPI mode operation. The SSPxCON1 register is readable and writable. The lower 6 bits of the SSPxSTAT are read-only. The upper two bits of the SSPxSTAT are read/write.

In one SPI master mode, SSPxADD can be loaded with a value used in the Baud Rate Generator. More information on the Baud Rate Generator is available in **Section 25.7 "Baud Rate Generator"**.

SSPxSR is the shift register used for shifting data in and out. SSPxBUF provides indirect access to the SSPxSR register. SSPxBUF is the buffer register to which data bytes are written, and from which data bytes are read.

In receive operations, SSPxSR and SSPxBUF together create a buffered receiver. When SSPxSR receives a complete byte, it is transferred to SSPxBUF and the SSPxIF interrupt is set.

During transmission, the SSPxBUF is not buffered. A write to SSPxBUF will write to both SSPxBUF and SSPxSR.

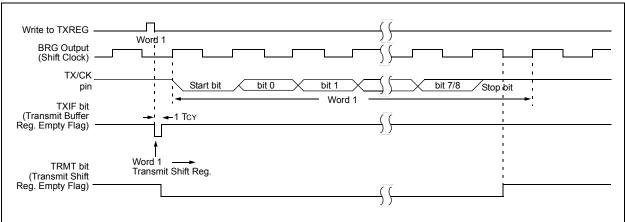

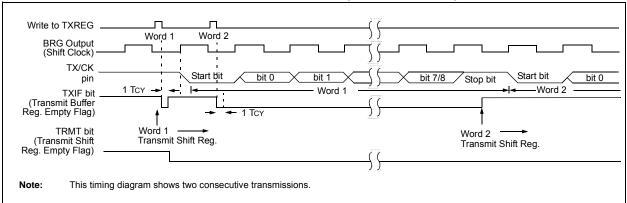

#### 26.1.1.5 TSR Status

The TRMT bit of the TXSTA register indicates the status of the TSR register. This is a read-only bit. The TRMT bit is set when the TSR register is empty and is cleared when a character is transferred to the TSR register from the TXREG. The TRMT bit remains clear until all bits have been shifted out of the TSR register. No interrupt logic is tied to this bit, so the user has to poll this bit to determine the TSR status.

**Note:** The TSR register is not mapped in data memory, so it is not available to the user.

#### 26.1.1.6 Transmitting 9-Bit Characters

The EUSART supports 9-bit character transmissions. When the TX9 bit of the TXSTA register is set, the EUSART will shift 9 bits out for each character transmitted. The TX9D bit of the TXSTA register is the ninth, and Most Significant, data bit. When transmitting 9-bit data, the TX9D data bit must be written before writing the 8 Least Significant bits into the TXREG. All nine bits of data will be transferred to the TSR shift register immediately after the TXREG is written.

A special 9-bit Address mode is available for use with multiple receivers. See **Section 26.1.2.7** "Address **Detection**" for more information on the address mode.

#### 26.1.1.7 Asynchronous Transmission Set-up:

- Initialize the SPBRGH, SPBRGL register pair and the BRGH and BRG16 bits to achieve the desired baud rate (see Section 26.3 "EUSART Baud Rate Generator (BRG)").

- Enable the asynchronous serial port by clearing the SYNC bit and setting the SPEN bit.

- If 9-bit transmission is desired, set the TX9 control bit. A set ninth data bit will indicate that the 8

Least Significant data bits are an address when the receiver is set for address detection.

- Set SCKP bit if inverted transmit is desired.

- Enable the transmission by setting the TXEN control bit. This will cause the TXIF interrupt bit to be set.

- If interrupts are desired, set the TXIE interrupt enable bit of the PIE1 register. An interrupt will occur immediately provided that the GIE and PEIE bits of the INTCON register are also set.

- 7. If 9-bit transmission is selected, the ninth bit should be loaded into the TX9D data bit.

- Load 8-bit data into the TXREG register. This will start the transmission.

#### FIGURE 26-4: ASYNCHRONOUS TRANSMISSION (BACK-TO-BACK)

**TABLE 26-1:** SUMMARY OF REGISTERS ASSOCIATED WITH ASYNCHRONOUS TRANSMISSION

| Name    | Bit 7                         | Bit 6   | Bit 5  | Bit 4                 | Bit 3                  | Bit 2  | Bit 1  | Bit 0   | Register on<br>Page |

|---------|-------------------------------|---------|--------|-----------------------|------------------------|--------|--------|---------|---------------------|

| APFCON0 | RXDTSEL                       | SDO1SEL | SS1SEL | P2BSEL <sup>(1)</sup> | CCP2SEL <sup>(1)</sup> | P1DSEL | P1CSEL | CCP1SEL | 119                 |

| APFCON1 | _                             | _       | ı      | _                     | _                      | ı      | _      | TXCKSEL | 119                 |

| BAUDCON | ABDOVF                        | RCIDL   | 1      | SCKP                  | BRG16                  | ı      | WUE    | ABDEN   | 296                 |

| INTCON  | GIE                           | PEIE    | TMR0IE | INTE                  | IOCIE                  | TMR0IF | INTF   | IOCIF   | 86                  |

| PIE1    | TMR1GIE                       | ADIE    | RCIE   | TXIE                  | SSPIE                  | CCP1IE | TMR2IE | TMR1IE  | 87                  |

| PIR1    | TMR1GIF                       | ADIF    | RCIF   | TXIF                  | SSPIF                  | CCP1IF | TMR2IF | TMR1IF  | 91                  |

| RCSTA   | SPEN                          | RX9     | SREN   | CREN                  | ADDEN                  | FERR   | OERR   | RX9D    | 295                 |

| SPBRGL  |                               |         |        | BRG•                  | <7:0>                  |        |        |         | 297*                |

| SPBRGH  |                               |         |        | BRG<                  | :15:8>                 |        |        |         | 297*                |

| TRISB   | TRISB7                        | TRISB6  | TRISB5 | TRISB4                | TRISB3                 | TRISB2 | TRISB1 | TRISB0  | 127                 |

| TXREG   | EUSART Transmit Data Register |         |        |                       |                        |        |        |         | 287*                |

| TXSTA   | CSRC                          | TX9     | TXEN   | SYNC                  | SENDB                  | BRGH   | TRMT   | TX9D    | 294                 |

— = unimplemented location, read as '0'. Shaded cells are not used for Asynchronous Transmission. Page provides register information. PIC16(L)F1827 only. Legend:

Note 1:

FIGURE 30-16: SPI MASTER MODE TIMING (CKE = 0, SMP = 0)

FIGURE 30-17: SPI MASTER MODE TIMING (CKE = 1, SMP = 1)

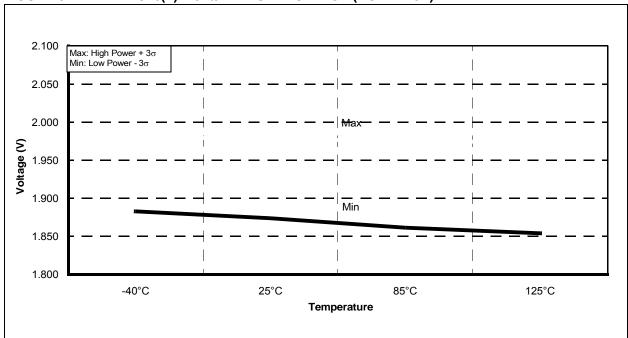

FIGURE 31-7: PIC16(L)F1826/27 RESET VOLTAGE (BOR = 1.9V)

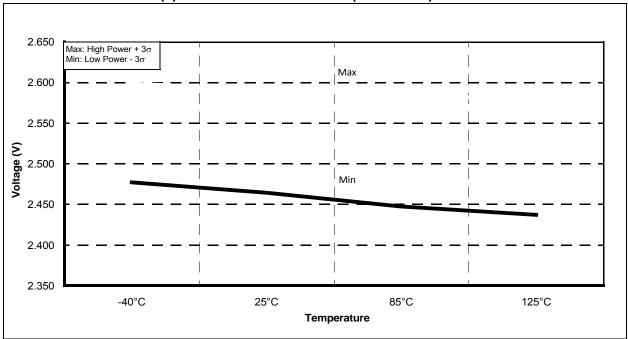

FIGURE 31-8: PIC16(L)F1826/27 RESET VOLTAGE (BOR = 1.9V)

## 32.2 MPLAB C Compilers for Various Device Families

The MPLAB C Compiler code development systems are complete ANSI C compilers for Microchip's PIC18, PIC24 and PIC32 families of microcontrollers and the dsPIC30 and dsPIC33 families of digital signal controllers. These compilers provide powerful integration capabilities, superior code optimization and ease of use.

For easy source level debugging, the compilers provide symbol information that is optimized to the MPLAB IDE debugger.

## 32.3 HI-TECH C for Various Device Families

The HI-TECH C Compiler code development systems are complete ANSI C compilers for Microchip's PIC family of microcontrollers and the dsPIC family of digital signal controllers. These compilers provide powerful integration capabilities, omniscient code generation and ease of use.

For easy source level debugging, the compilers provide symbol information that is optimized to the MPLAB IDE debugger.

The compilers include a macro assembler, linker, preprocessor, and one-step driver, and can run on multiple platforms.

#### 32.4 MPASM Assembler

The MPASM Assembler is a full-featured, universal macro assembler for PIC10/12/16/18 MCUs.

The MPASM Assembler generates relocatable object files for the MPLINK Object Linker, Intel® standard HEX files, MAP files to detail memory usage and symbol reference, absolute LST files that contain source lines and generated machine code and COFF files for debugging.

The MPASM Assembler features include:

- · Integration into MPLAB IDE projects

- User-defined macros to streamline assembly code

- Conditional assembly for multi-purpose source files

- Directives that allow complete control over the assembly process

#### 32.5 MPLINK Object Linker/ MPLIB Object Librarian

The MPLINK Object Linker combines relocatable objects created by the MPASM Assembler and the MPLAB C18 C Compiler. It can link relocatable objects from precompiled libraries, using directives from a linker script.

The MPLIB Object Librarian manages the creation and modification of library files of precompiled code. When a routine from a library is called from a source file, only the modules that contain that routine will be linked in with the application. This allows large libraries to be used efficiently in many different applications.

The object linker/library features include:

- Efficient linking of single libraries instead of many smaller files

- Enhanced code maintainability by grouping related modules together

- Flexible creation of libraries with easy module listing, replacement, deletion and extraction

# 32.6 MPLAB Assembler, Linker and Librarian for Various Device Families

MPLAB Assembler produces relocatable machine code from symbolic assembly language for PIC24, PIC32 and dsPIC devices. MPLAB C Compiler uses the assembler to produce its object file. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. Notable features of the assembler include:

- Support for the entire device instruction set

- · Support for fixed-point and floating-point data

- · Command line interface

- · Rich directive set

- · Flexible macro language

- MPLAB IDE compatibility

## APPENDIX A: DATA SHEET REVISION HISTORY

#### **Revision A**

Original release (06/2009)

#### **Revision B (08/09)**

Revised Tables 5-3, 6-2, 12-2, 12-3; Updated Electrical Specifications; Added UQFN Package; Added SOIC and QFN Land Patterns; Updated Product ID section.

#### Revision C (06/10)

Updated Electrical Specification and included Enhanced Core Golden Chapters.

#### **Revision D (04/11)**

Added Char Data to release Final data sheet.

# APPENDIX B: MIGRATING FROM OTHER PIC® DEVICES

This section provides comparisons when migrating from other similar  $PIC^{\textcircled{@}}$  devices to the PIC16(L)F1826/27 family of devices.

# B.1 PIC16F648A to PIC16(L)F1827 TABLE B-1: FEATURE COMPARISON

| Feature                               | PIC16F648A         | PIC16(L)F1827               |

|---------------------------------------|--------------------|-----------------------------|

| Max. Operating<br>Speed               | 20 MHz             | 32 MHz                      |

| Max. Program<br>Memory (Words)        | 4K                 | 4K                          |

| Max. SRAM (Bytes)                     | 256                | 384                         |

| Max. EEPROM (Bytes)                   | 256                | 256                         |

| A/D Resolution                        | 10-bit             | 10-bit                      |

| Timers (8/16-bit)                     | 2/1                | 4/1                         |

| Brown-out Reset                       | Y                  | Y                           |

| Internal Pull-ups                     | RB<7:0>            | RB<7:0>, RA5                |

| Interrupt-on-Change                   | RB<7:4>            | RB<7:0>, Edge<br>Selectable |

| Comparator                            | 2                  | 2                           |

| AUSART/EUSART                         | 1/0                | 0/2                         |

| Extended WDT                          | N                  | Y                           |

| Software Control<br>Option of WDT/BOR | N                  | Y                           |

| INTOSC<br>Frequencies                 | 48 kHz or<br>4 MHz | 31 kHz -<br>32 MHz          |

| Clock Switching                       | Y                  | Y                           |

| Capacitive Sensing                    | N                  | Y                           |

| CCP/ECCP                              | 2/0                | 2/2                         |

| Enhanced PIC16<br>CPU                 | N                  | Y                           |

| MSSPx/SSPx                            | 0                  | 2/0                         |

| Reference Clock                       | N                  | Y                           |

| Data Signal<br>Modulator              | N                  | Y                           |

| SR Latch                              | N                  | Y                           |

| Voltage Reference                     | N                  | Y                           |

| DAC                                   | Υ                  | Y                           |