Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 32MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 16                                                                        |

| Program Memory Size        | 3.5KB (2K x 14)                                                           |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 256 x 8                                                                   |

| RAM Size                   | 256 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                               |

| Data Converters            | A/D 12x10b                                                                |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 18-SOIC (0.295", 7.50mm Width)                                            |

| Supplier Device Package    | 18-SOIC                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f1826-e-so |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| TADLL   | J-0. JI              |                                    |                                      | I KEGISTI |          |          |        | וש        |           |                      |                                 |

|---------|----------------------|------------------------------------|--------------------------------------|-----------|----------|----------|--------|-----------|-----------|----------------------|---------------------------------|

| Address | Name                 | Bit 7                              | Bit 6                                | Bit 5     | Bit 4    | Bit 3    | Bit 2  | Bit 1     | Bit 0     | Value on<br>POR, BOR | Value on all<br>other<br>Resets |

| Bank 8  | Bank 8               |                                    |                                      |           |          |          |        |           |           |                      |                                 |

| 40Ch    | _                    | Unimplement                        | ed                                   |           |          |          |        |           |           | _                    | _                               |

| 40Dh    | _                    | Unimplement                        | ed                                   |           |          |          |        |           |           | _                    | _                               |

| 40Eh    | _                    | Unimplement                        | ed                                   |           |          |          |        |           |           | _                    | _                               |

| 40Fh    | _                    | Unimplement                        | ed                                   |           |          |          |        |           |           | _                    | _                               |

| 410h    | _                    | Unimplement                        | ed                                   |           |          |          |        |           |           | _                    | _                               |

| 411h    | _                    | Unimplement                        | ed                                   |           |          |          |        |           |           | _                    | _                               |

| 412h    | _                    | Unimplement                        | ed                                   |           |          |          |        |           |           | —                    | _                               |

| 413h    | _                    | Unimplement                        | ed                                   |           |          |          |        |           |           | —                    | _                               |

| 414h    | _                    | Unimplement                        | ed                                   |           |          |          |        |           |           | —                    | _                               |

| 415h    | TMR4 <sup>(1)</sup>  | Timer4 Modu                        | le Register                          |           |          |          |        |           |           | 0000 0000            | 0000 0000                       |

| 416h    | PR4 <sup>(1)</sup>   | Timer4 Perio                       | d Register                           |           |          |          |        |           |           | 1111 1111            | 1111 1111                       |

| 417h    | T4CON <sup>(1)</sup> | —                                  | T4OUTPS3                             | T4OUTPS2  | T4OUTPS1 | T4OUTPS0 | TMR4ON | T4CKPS1   | T4CKPS0   | -000 0000            | -000 0000                       |

| 418h    | _                    | Unimplement                        | ed                                   |           |          |          |        |           |           | —                    | _                               |

| 419h    | _                    | Unimplement                        | ed                                   |           |          |          |        |           |           | _                    | _                               |

| 41Ah    | _                    | Unimplement                        | ed                                   |           |          |          |        |           |           | —                    | _                               |

| 41Bh    | _                    | Unimplement                        | Unimplemented —                      |           |          |          |        |           | _         |                      |                                 |

| 41Ch    | TMR6 <sup>(1)</sup>  | Timer6 Modu                        | Timer6 Module Register 0000 0000 000 |           |          |          |        |           | 0000 0000 |                      |                                 |

| 41Dh    | PR6 <sup>(1)</sup>   | Timer6 Period Register 1111 111 11 |                                      |           |          |          |        | 1111 1111 |           |                      |                                 |

| 41Eh    | T6CON <sup>(1)</sup> | —                                  | T6OUTPS3                             | T6OUTPS2  | T6OUTPS1 | T6OUTPS0 | TMR6ON | T6CKPS1   | T6CKPS0   | -000 0000            | -000 0000                       |

| 41Fh    | _                    | Unimplement                        | ed                                   |           |          |          |        |           |           | _                    | _                               |

#### SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED) **TABLE 3-6:**

x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, r = reserved. Shaded locations are unimplemented, read as '0'. Legend:

Note 1: PIC16(L)F1827 only.

#### REGISTER 4-1: CONFIGURATION WORD 1

|                |                                                                                                                                                                                                                                                                                   | R/P-1                                                                            | R/P-1                                             | R/P-1                                                                           | R/P-1           | R/P-1         | R/P-1/1 |  |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|---------------------------------------------------|---------------------------------------------------------------------------------|-----------------|---------------|---------|--|

|                |                                                                                                                                                                                                                                                                                   | FCMEN                                                                            | IESO                                              | CLKOUTEN                                                                        | BORE            | N<1:0>        | CPD     |  |

|                |                                                                                                                                                                                                                                                                                   | bit 13                                                                           |                                                   | 1 1                                                                             |                 |               | bit 8   |  |

|                |                                                                                                                                                                                                                                                                                   |                                                                                  |                                                   |                                                                                 |                 |               |         |  |

| R/P-1          | R/P-1                                                                                                                                                                                                                                                                             | R/P-1                                                                            | R/P-1                                             | R/P-1                                                                           | R/P-1           | R/P-1         | R/P-1   |  |

| CP             | MCLRE                                                                                                                                                                                                                                                                             | PWRTE                                                                            | WDT                                               | E<1:0>                                                                          |                 | FOSC<2:0>     |         |  |

| bit 7          |                                                                                                                                                                                                                                                                                   |                                                                                  |                                                   |                                                                                 |                 |               | bit C   |  |

|                |                                                                                                                                                                                                                                                                                   |                                                                                  |                                                   |                                                                                 |                 |               |         |  |

| Legend:        |                                                                                                                                                                                                                                                                                   |                                                                                  |                                                   |                                                                                 |                 |               |         |  |

| R = Readab     | ole bit                                                                                                                                                                                                                                                                           | P = Programn                                                                     | nable bit                                         | U = Unimplem                                                                    | ented bit, read | d as '1'      |         |  |

| '0' = Bit is c | leared                                                                                                                                                                                                                                                                            | '1' = Bit is set                                                                 |                                                   | -n = Value whe                                                                  | en blank or aft | er Bulk Erase |         |  |

| bit 13         | 1 = Fail-Safe<br>0 = Fail-Safe                                                                                                                                                                                                                                                    | -Safe Clock Mo<br>Clock Monitor i<br>Clock Monitor i                             | s enabled<br>s disabled                           | bit                                                                             |                 |               |         |  |

| bit 12         | 1 = Internal/E                                                                                                                                                                                                                                                                    | al External Swite<br>External Switche<br>External Switche                        | ver mode is e                                     |                                                                                 |                 |               |         |  |

| bit 11         | If FOSC confi<br>This bit is<br>All other FOS                                                                                                                                                                                                                                     | <u>SC modes</u> :<br>OUT function is                                             | e set to LP, X<br>OUT function i<br>disabled. I/O | <u>T. HS modes</u> :<br>s disabled. Oscil<br>function on the (<br>he CLKOUT pin |                 | on the CLKOUT | pin.    |  |

| bit 10-9       | 11 = BOR en<br>10 = BOR en                                                                                                                                                                                                                                                        | abled during op<br>ntrolled by SBC                                               | eration and d                                     | its<br>lisabled in Sleep<br>e BORCON regi                                       |                 |               |         |  |

| bit 8          | 1 = Data mer                                                                                                                                                                                                                                                                      | ode Protection<br>nory code prote<br>nory code prote                             | ction is disab                                    |                                                                                 |                 |               |         |  |

| bit 7          |                                                                                                                                                                                                                                                                                   | otection bit<br>memory code p<br>memory code p                                   |                                                   |                                                                                 |                 |               |         |  |

| bit 6          |                                                                                                                                                                                                                                                                                   |                                                                                  |                                                   |                                                                                 |                 |               |         |  |

| bit 5          | 1 = PWRT di                                                                                                                                                                                                                                                                       | <b>PWRTE:</b> Power-up Timer Enable bit<br>1 = PWRT disabled<br>0 = PWRT enabled |                                                   |                                                                                 |                 |               |         |  |

| bit 4-3        | <ul> <li>0 = PWRT enabled</li> <li>WDTE&lt;1:0&gt;: Watchdog Timer Enable bit</li> <li>11 = WDT enabled</li> <li>10 = WDT enabled while running and disabled in Sleep</li> <li>01 = WDT controlled by the SWDTEN bit in the WDTCON register</li> <li>00 = WDT disabled</li> </ul> |                                                                                  |                                                   |                                                                                 |                 |               |         |  |

| EXAM                 | PLE 11-4:                                             | ERASING ONI                                                                    | E ROW OF PROGRAM MEMORY -                                                                                                                                                                                                                                                                                                                       |

|----------------------|-------------------------------------------------------|--------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                      |                                                       | routine assumes                                                                | -                                                                                                                                                                                                                                                                                                                                               |

| ; 1. A               | valid addr                                            | ess within the                                                                 | erase block is loaded in ADDRH:ADDRL                                                                                                                                                                                                                                                                                                            |

| ; 2. AI              | ODRH and AD                                           | DRL are located                                                                | in shared data memory 0x70 - 0x7F (common RAM)                                                                                                                                                                                                                                                                                                  |

|                      | BCF<br>BANKSEL<br>MOVF<br>MOVWF<br>MOVF<br>BSF        | INTCON,GIE<br>EEADRL<br>ADDRL,W<br>EEADRL<br>ADDRH,W<br>EEADRH<br>EECON1,EEPGD | <ul> <li>; Disable ints so required sequences will execute properly</li> <li>; Load lower 8 bits of erase address boundary</li> <li>; Load upper 6 bits of erase address boundary</li> <li>; Point to program memory</li> </ul>                                                                                                                 |

|                      | BCF                                                   | EECON1, EEFGD                                                                  | ; Not configuration space                                                                                                                                                                                                                                                                                                                       |

|                      | BSF                                                   | EECON1, FREE                                                                   | ; Specify an erase operation                                                                                                                                                                                                                                                                                                                    |

|                      | BSF                                                   | EECON1, WREN                                                                   | ; Enable writes                                                                                                                                                                                                                                                                                                                                 |

| Required<br>Sequence | MOVLW<br>MOVWF<br>MOVLW<br>MOVWF<br>BSF<br>NOP<br>NOP | 55h<br>EECON2<br>0AAh<br>EECON2<br>EECON1,WR                                   | <pre>; Start of required sequence to initiate erase<br/>; Write 55h<br/>;<br/>; Write AAh<br/>; Set WR bit to begin erase<br/>; Any instructions here are ignored as processor<br/>; halts to begin erase sequence<br/>; Processor will stop here and wait for erase complete.<br/>; after erase processor continues with 3rd instruction</pre> |

|                      | BCF<br>BSF                                            | EECON1,WREN<br>INTCON,GIE                                                      | ; Disable writes<br>; Enable interrupts                                                                                                                                                                                                                                                                                                         |

#### 13.6 Interrupt-On-Change Registers

#### REGISTER 13-1: IOCBP: INTERRUPT-ON-CHANGE POSITIVE EDGE REGISTER

| '1' = Bit is set                        |         | '0' = Bit is clea | ared    |                                    |               |                  |             |  |

|-----------------------------------------|---------|-------------------|---------|------------------------------------|---------------|------------------|-------------|--|

| u = Bit is unchanged x = Bit is unknown |         |                   | nown    | -n/n = Value a                     | at POR and BO | R/Value at all o | ther Resets |  |

| R = Readable                            | bit     | W = Writable      | bit     | U = Unimplemented bit, read as '0' |               |                  |             |  |

| Legend:                                 |         |                   |         |                                    |               |                  |             |  |

|                                         |         |                   |         |                                    |               |                  |             |  |

| bit 7                                   | •       | •                 |         | •                                  |               |                  | bit 0       |  |

| IOCBP7                                  | IOCBP6  | IOCBP5            | IOCBP4  | IOCBP3                             | IOCBP2        | IOCBP1           | IOCBP0      |  |

| R/W-0/0                                 | R/W-0/0 | R/W-0/0           | R/W-0/0 | R/W-0/0                            | R/W-0/0       | R/W-0/0          | R/W-0/0     |  |

bit 7-0

**IOCBP<7:0>:** Interrupt-on-Change Positive Edge Enable bits

- 1 = Interrupt-on-change enabled on the pin for a positive going edge. Associated Status bit and interrupt flag will be set upon detecting an edge.

- 0 = Interrupt-on-change disabled for the associated pin.

#### REGISTER 13-2: IOCBN: INTERRUPT-ON-CHANGE NEGATIVE EDGE REGISTER

| R/W-0/0 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| IOCBN7  | IOCBN6  | IOCBN5  | IOCBN4  | IOCBN3  | IOCBN2  | IOCBN1  | IOCBN0  |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0

IOCBN<7:0>: Interrupt-on-Change Negative Edge Enable bits

- 1 = Interrupt-on-change enabled on the pin for a negative going edge. Associated Status bit and interrupt flag will be set upon detecting an edge.

- 0 = Interrupt-on-change disabled for the associated pin.

#### REGISTER 13-3: IOCBF: INTERRUPT-ON-CHANGE FLAG REGISTER

| R/W/HS-0/0 |

|------------|------------|------------|------------|------------|------------|------------|------------|

| IOCBF7     | IOCBF6     | IOCBF5     | IOCBF4     | IOCBF3     | IOCBF2     | IOCBF1     | IOCBF0     |

| bit 7      |            |            |            |            |            |            | bit 0      |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | HS - Bit is set in hardware                           |

bit 7-0

IOCBF<7:0>: Interrupt-on-Change Flag bits

- 1 = An enabled change was detected on the associated pin.

Set when IOCBPx = 1 and a rising edge was detected on RBx, or when IOCBNx = 1 and a falling edge was detected on RBx.

- 0 = No change was detected, or the user cleared the detected change.

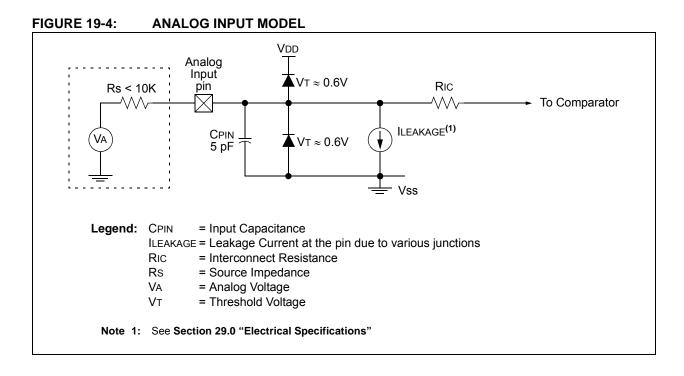

#### 16.2.6 A/D CONVERSION PROCEDURE

This is an example procedure for using the ADC to perform an Analog-to-Digital conversion:

- 1. Configure Port:

- Disable pin output driver (Refer to the TRIS register)

- Configure pin as analog (Refer to the ANSEL register)

- 2. Configure the ADC module:

- Select ADC conversion clock

- · Configure voltage reference

- · Select ADC input channel

- Turn on ADC module

- 3. Configure ADC interrupt (optional):

- Clear ADC interrupt flag

- · Enable ADC interrupt

- Enable peripheral interrupt

- Enable global interrupt<sup>(1)</sup>

- 4. Wait the required acquisition time<sup>(2)</sup>.

- 5. Start conversion by setting the GO/DONE bit.

- 6. Wait for ADC conversion to complete by one of the following:

- Polling the GO/DONE bit

- Waiting for the ADC interrupt (interrupts enabled)

- 7. Read ADC Result.

- 8. Clear the ADC interrupt flag (required if interrupt is enabled).

**Note 1:** The global interrupt can be disabled if the user is attempting to wake-up from Sleep and resume in-line code execution.

2: Refer to Section 16.4 "A/D Acquisition Requirements".

#### EXAMPLE 16-1: A/D CONVERSION

;This code block configures the ADC ; for polling, Vdd and Vss references, Frc ;clock and ANO input. ;Conversion start & polling for completion ; are included. BANKSEL ADCON1 ; B'11110000' ;Right justify, Frc MOVLW ;clock MOVWF ADCON1 ;Vdd and Vss Vref BANKSEL TRISA ; BSF TRISA,0 ;Set RA0 to input BANKSEL ANSEL ; BSF ANSEL,0 ;Set RA0 to analog BANKSEL ADCON0 B'00000001' ;Select channel AN0 MOVLW MOVWE ;Turn ADC On ADCON0 SampleTime ; Acquisiton delay CALL ADCON0, ADGO ; Start conversion BSF BTFSC ADCON0, ADGO ; Is conversion done? GOTO \$-1 ;No, test again ADRESH ; BANKSEL ADRESH,W ;Read upper 2 bits MOVF MOVWF RESULTHI ;store in GPR space BANKSEL ADRESL ; ADRESL,W MOVF ;Read lower 8 bits MOVWE RESULTIO ;Store in GPR space

#### REGISTER 16-5: ADRESH: ADC RESULT REGISTER HIGH (ADRESH) ADFM = 1

| R/W-x/u                                 | R/W-x/u | R/W-x/u           | R/W-x/u | R/W-x/u                                               | R/W-x/u | R/W-x/u | R/W-x/u |  |

|-----------------------------------------|---------|-------------------|---------|-------------------------------------------------------|---------|---------|---------|--|

| —                                       | —       | —                 | _       | —                                                     | _       | ADRE    | S<9:8>  |  |

| bit 7                                   | •       |                   |         |                                                       |         |         | bit 0   |  |

|                                         |         |                   |         |                                                       |         |         |         |  |

| Legend:                                 |         |                   |         |                                                       |         |         |         |  |

| R = Readable                            | bit     | W = Writable      | bit     | U = Unimplemented bit, read as '0'                    |         |         |         |  |

| u = Bit is unchanged x = Bit is unknown |         |                   |         | -n/n = Value at POR and BOR/Value at all other Resets |         |         |         |  |

| '1' = Bit is set                        |         | '0' = Bit is clea | ared    |                                                       |         |         |         |  |

bit 7-2 Reserved: Do not use.

bit 1-0 ADRES<9:8>: ADC Result Register bits Upper 2 bits of 10-bit conversion result

## REGISTER 16-6: ADRESL: ADC RESULT REGISTER LOW (ADRESL) ADFM = 1

| R/W-x/u |

|---------|---------|---------|---------|---------|---------|---------|---------|

|         |         |         | ADRES   | 6<7:0>  |         |         |         |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 ADRES<7:0>: ADC Result Register bits Lower 8 bits of 10-bit conversion result

## 17.0 DIGITAL-TO-ANALOG CONVERTER (DAC) MODULE

The Digital-to-Analog Converter supplies a variable voltage reference, ratiometric with the input source, with 32 selectable output levels.

The input of the DAC can be connected to:

- External VREF pins

- VDD supply voltage

- FVR (Fixed Voltage Reference)

The output of the DAC can be configured to supply a reference voltage to the following:

- Comparator positive input

- ADC input channel

- DACOUT pin

- Capacitive Sensing module (CSM)

The Digital-to-Analog Converter (DAC) can be enabled by setting the DACEN bit of the DACCON0 register.

## EQUATION 17-1: DAC OUTPUT VOLTAGE

## <u>**IF DACEN = 1**</u> $VOUT = \left( (VSOURCE - VSOURCE -) \times \frac{DACR[4:0]}{2^5} \right) + VSOURCE - VSOURCE -$

IF DACEN = 0 and DACLPS = 1 and DACR[4:0] = 11111

VOUT = VSOURCE +

#### IF DACEN = 0 and DACLPS = 0 and DACR[4:0] = 00000

VOUT = VSOURCE -

VSOURCE+ = VDD, VREF, or FVR BUFFER 2

VSOURCE - = VSS

## 17.2 Ratiometric Output Level

The DAC output value is derived using a resistor ladder with each end of the ladder tied to a positive and negative voltage reference input source. If the voltage of either input source fluctuates, a similar fluctuation will result in the DAC output value.

The value of the individual resistors within the ladder can be found in **Section 29.0** "**Electrical Specifications**".

## 17.1 Output Voltage Selection

The DAC has 32 voltage level ranges. The 32 levels are set with the DACR<4:0> bits of the DACCON1 register.

The DAC output voltage is determined by the equations in Equation 17-1.

## 17.3 DAC Voltage Reference Output

The DAC can be output to the DACOUT pin by setting the DACOE bit of the DACCON0 register to '1'. Selecting the DAC reference voltage for output on the DACOUT pin automatically overrides the digital output buffer and digital input threshold detector functions of that pin. Reading the DACOUT pin when it has been configured for DAC reference voltage output will always return a '0'.

Due to the limited current drive capability, a buffer must be used on the DAC voltage reference output for external connections to DACOUT. Figure 17-2 shows an example buffering technique.

| SRCLK | Divider | Fosc = 32 MHz | Fosc = 20 MHz | Fosc = 16 MHz | Fosc = 4 MHz | Fosc = 1 MHz |

|-------|---------|---------------|---------------|---------------|--------------|--------------|

| 111   | 512     | 62.5 kHz      | 39.0 kHz      | 31.3 kHz      | 7.81 kHz     | 1.95 kHz     |

| 110   | 256     | 125 kHz       | 78.1 kHz      | 62.5 kHz      | 15.6 kHz     | 3.90 kHz     |

| 101   | 128     | 250 kHz       | 156 kHz       | 125 kHz       | 31.25 kHz    | 7.81 kHz     |

| 100   | 64      | 500 kHz       | 313 kHz       | 250 kHz       | 62.5 kHz     | 15.6 kHz     |

| 011   | 32      | 1 MHz         | 625 kHz       | 500 kHz       | 125 kHz      | 31.3 kHz     |

| 010   | 16      | 2 MHz         | 1.25 MHz      | 1 MHz         | 250 kHz      | 62.5 kHz     |

| 001   | 8       | 4 MHz         | 2.5 MHz       | 2 MHz         | 500 kHz      | 125 kHz      |

| 000   | 4       | 8 MHz         | 5 MHz         | 4 MHz         | 1 MHz        | 250 kHz      |

#### TABLE 18-1: SRCLK FREQUENCY TABLE

#### REGISTER 18-1: SRCON0: SR LATCH CONTROL 0 REGISTER

| R/W-0/0 | R/W-0/0 | R/W-0/0    | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/S-0/0 | R/S-0/0 |

|---------|---------|------------|---------|---------|---------|---------|---------|

| SRLEN   |         | SRCLK<2:0> |         | SRQEN   | SRNQEN  | SRPS    | SRPR    |

| bit 7   |         |            |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | S = Bit is set only                                   |

| bit 7      | SRLEN: SR Latch Enable bit<br>1 = SR Latch is enabled<br>0 = SR Latch is disabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| bit 6-4    | <b>SRCLK&lt;2:0&gt;:</b> SR Latch Clock Divider bits<br>000 = Generates a 1 Fosc wide pulse every 4th Fosc cycle clock<br>001 = Generates a 1 Fosc wide pulse every 8th Fosc cycle clock<br>010 = Generates a 1 Fosc wide pulse every 16th Fosc cycle clock<br>011 = Generates a 1 Fosc wide pulse every 32nd Fosc cycle clock<br>100 = Generates a 1 Fosc wide pulse every 64th Fosc cycle clock<br>101 = Generates a 1 Fosc wide pulse every 128th Fosc cycle clock<br>110 = Generates a 1 Fosc wide pulse every 256th Fosc cycle clock<br>111 = Generates a 1 Fosc wide pulse every 512th Fosc cycle clock |  |  |  |  |  |  |

| bit 3      | SRQEN: SR Latch Q Output Enable bit<br><u>If SRLEN = 1</u> :<br>1 = Q is present on the SRQ pin<br>0 = External Q output is disabled<br><u>If SRLEN = 0</u> :<br>SR Latch is disabled                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |

| bit 2      | SRNQEN: SR Latch Q Output Enable bit<br><u>If SRLEN = 1</u> :<br>1 = Q is present on the SRnQ pin<br>0 = External Q output is disabled<br><u>If SRLEN = 0</u> :<br>SR Latch is disabled                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |

| bit 1      | <ul> <li>SRPS: Pulse Set Input of the SR Latch bit<sup>(1)</sup></li> <li>1 = Pulse set input for 1 Q-clock period</li> <li>0 = No effect on set input.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |

| bit 0      | <ul> <li>SRPR: Pulse Reset Input of the SR Latch bit<sup>(1)</sup></li> <li>1 = Pulse reset input for 1 Q-clock period</li> <li>0 = No effect on reset input.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |

| Note 1: Se | t only, always reads back '0'.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |

| R/W-0/0         | R-0/0                                                                                                                      | R/W-0/0                                                     | R/W-0/0        | U-0           | R/W-1/1          | R/W-0/0         | R/W-0/0          |  |  |

|-----------------|----------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|----------------|---------------|------------------|-----------------|------------------|--|--|

| CxON            | CxOUT                                                                                                                      | CxOE                                                        | CxPOL          |               | CxSP             | CxHYS           | CxSYNC           |  |  |

| bit 7           | ·                                                                                                                          |                                                             |                | ·             |                  |                 | bit 0            |  |  |

| Legend:         |                                                                                                                            |                                                             |                |               |                  |                 |                  |  |  |

| R = Readable    | e bit                                                                                                                      | W = Writable                                                | bit            | U = Unimple   | mented bit, read | d as '0'        |                  |  |  |

| u = Bit is unc  | hanged                                                                                                                     | x = Bit is unkr                                             | nown           | -n/n = Value  | at POR and BC    | R/Value at all  | other Resets     |  |  |

| '1' = Bit is se | t                                                                                                                          | '0' = Bit is clea                                           | ared           |               |                  |                 |                  |  |  |

| bit 7           | CxON: Com                                                                                                                  | parator Enable                                              | bit            |               |                  |                 |                  |  |  |

|                 | 1 = Compara                                                                                                                | ator is enabled a ator is disabled                          |                | no active pov | ver              |                 |                  |  |  |

| bit 6           | CxOUT: Cor                                                                                                                 | nparator Output                                             | bit            |               |                  |                 |                  |  |  |

|                 |                                                                                                                            | (inverted polar                                             | <u>ity):</u>   |               |                  |                 |                  |  |  |

|                 | 1 = CxVP <<br>0 = CxVP >                                                                                                   | -                                                           |                |               |                  |                 |                  |  |  |

|                 |                                                                                                                            | <u>) (non-inverted p</u>                                    | oolaritv):     |               |                  |                 |                  |  |  |

|                 | 1 = CxVP >                                                                                                                 | CxVN                                                        |                |               |                  |                 |                  |  |  |

|                 | 0 = CxVP <                                                                                                                 | CxVN                                                        |                |               |                  |                 |                  |  |  |

| bit 5           |                                                                                                                            | parator Output I                                            |                |               |                  |                 |                  |  |  |

|                 | drive the                                                                                                                  | is present on the<br>e pin. Not affecte<br>is internal only |                | Requires that | the associated T | RIS bit be clea | ired to actually |  |  |

| bit 4           |                                                                                                                            | nparator Output                                             | Polarity Selec | ct bit        |                  |                 |                  |  |  |

|                 | 1 = Compara                                                                                                                | ator output is inv<br>ator output is no                     | verted         |               |                  |                 |                  |  |  |

| bit 3           |                                                                                                                            | nted: Read as '                                             |                |               |                  |                 |                  |  |  |

| bit 2           | CxSP: Com                                                                                                                  | parator Speed/P                                             | ower Select b  | it            |                  |                 |                  |  |  |

|                 |                                                                                                                            | ator operates in ator operates in                           |                |               |                  |                 |                  |  |  |

| bit 1           | CxHYS: Cor                                                                                                                 | CxHYS: Comparator Hysteresis Enable bit                     |                |               |                  |                 |                  |  |  |

|                 | •                                                                                                                          | ator hysteresis                                             |                |               |                  |                 |                  |  |  |

|                 | •                                                                                                                          | ator hysteresis                                             |                |               |                  |                 |                  |  |  |

| bit 0           |                                                                                                                            | omparator Outp                                              | •              |               |                  | <u> </u>        |                  |  |  |

|                 |                                                                                                                            |                                                             |                |               | ronous to chang  | ges on Timer1   | clock source     |  |  |

|                 | Output updated on the falling edge of Timer1 clock source.<br>0 = Comparator output to Timer1 and I/O pin is asynchronous. |                                                             |                |               |                  |                 |                  |  |  |

### REGISTER 19-1: CMxCON0: COMPARATOR Cx CONTROL REGISTER 0

| Name                | Bit 7                                                        | Bit 6           | Bit 5         | Bit 4                  | Bit 3    | Bit 2  | Bit 1   | Bit 0   | Register<br>on Page |

|---------------------|--------------------------------------------------------------|-----------------|---------------|------------------------|----------|--------|---------|---------|---------------------|

| INTCON              | GIE                                                          | PEIE            | TMR0IE        | INTE                   | IOCIE    | TMR0IF | INTF    | IOCIF   | 91                  |

| PIE1                | TMR1GIE                                                      | ADIE            | RCIE          | TXIE                   | SSP1IE   | CCP1IE | TMR2IE  | TMR1IE  | 92                  |

| PIR1                | TMR1GIF                                                      | ADIF            | RCIF          | TXIF                   | SSP1IF   | CCP1IF | TMR2IF  | TMR1IF  | 96                  |

| PIE3 <sup>(1)</sup> | —                                                            | _               | CCP4IE        | CCP3IE                 | TMR6IE   |        | TMR4IE  | _       | 94                  |

| PIR3 <sup>(1)</sup> | —                                                            | _               | CCP4IF        | CCP3IF                 | TMR6IF   | _      | TMR4IF  | —       | 98                  |

| PR2                 | Timer2 Module Period Register                                |                 |               |                        |          |        |         |         |                     |

| PR4                 | Timer4 Mod                                                   | ule Period Re   | gister        |                        |          |        |         |         | 189*                |

| PR6                 | Timer6 Mod                                                   | ule Period Re   | gister        |                        |          |        |         |         | 189*                |

| T2CON               | —                                                            | T2OUTPS3        | T2OUTPS2      | T2OUTPS1               | T2OUTPS0 | TMR2ON | T2CKPS1 | T2CKPS0 | 191                 |

| T4CON               | —                                                            | T4OUTPS3        | T4OUTPS2      | T4OUTPS1               | T4OUTPS0 | TMR4ON | T4CKPS1 | T4CKPS0 | 191                 |

| T6CON               | —                                                            | T6OUTPS3        | T6OUTPS2      | T6OUTPS1               | T6OUTPS0 | TMR6ON | T6CKPS1 | T6CKPS0 | 191                 |

| TMR2                | Holding Register for the 8-bit TMR2 Time Base                |                 |               |                        |          |        |         |         | 189*                |

| TMR4                | Holding Register for the 8-bit TMR4 Time Base <sup>(1)</sup> |                 |               |                        |          |        |         | 189*    |                     |

| TMR6                | Holding Reg                                                  | ister for the 8 | -bit TMR6 Tin | ne Base <sup>(1)</sup> |          |        |         |         | 189*                |

#### TABLE 22-1: SUMMARY OF REGISTERS ASSOCIATED WITH TIMER2/4/6

Legend: — = unimplemented read as '0'. Shaded cells are not used for Timer2 module.

\* Page provides register information.

Note 1: PIC16(L)F1827 only.

| R/W-0/       | /0 R/W-0/0           | R/W-1/1                                                                                        | R/W-0/0         | R-0/0          | U-0                | U-0            | R/W-0/0      |  |

|--------------|----------------------|------------------------------------------------------------------------------------------------|-----------------|----------------|--------------------|----------------|--------------|--|

| MDEN         | N MDOE               | MDSLR                                                                                          | MDOPOL          | MDOUT          | —                  |                | MDBIT        |  |

| bit 7        |                      |                                                                                                |                 |                |                    |                | bit 0        |  |

| <u> </u>     |                      |                                                                                                |                 |                |                    |                |              |  |

| Legend:      |                      |                                                                                                |                 |                |                    |                |              |  |

| R = Read     |                      | W = Writable                                                                                   |                 | •              | mented bit, read   |                |              |  |

|              | unchanged            | x = Bit is unk                                                                                 |                 | -n/n = Value   | at POR and BOF     | R/Value at all | other Resets |  |

| '1' = Bit is | set                  | '0' = Bit is cle                                                                               | ared            |                |                    |                |              |  |

|              |                      |                                                                                                |                 |                |                    |                |              |  |

| bit 7        |                      | ulator Module E                                                                                |                 |                |                    |                |              |  |

|              |                      | or module is er                                                                                |                 | 0 1 0          | als                |                |              |  |

|              |                      | or module is di                                                                                |                 |                |                    |                |              |  |

| bit 6        |                      | ulator Module F                                                                                | •               | ble bit        |                    |                |              |  |

|              |                      | or pin output er<br>or pin output di                                                           |                 |                |                    |                |              |  |

| bit 5        |                      | OUT Pin Slew                                                                                   |                 | ait            |                    |                |              |  |

| DIL 5        |                      | pin slew rate li                                                                               | 0               |                |                    |                |              |  |

|              |                      | pin slew rate li                                                                               |                 |                |                    |                |              |  |

| bit 4        |                      | Iodulator Outpu                                                                                | •               |                |                    |                |              |  |

|              |                      | or output signa                                                                                |                 |                |                    |                |              |  |

|              |                      | or output signa                                                                                |                 | b              |                    |                |              |  |

| bit 3        | MDOUT: Mo            | dulator Output                                                                                 | bit             |                |                    |                |              |  |

|              | Displays the         | current output                                                                                 | value of the me | odulator modu  | le. <sup>(1)</sup> |                |              |  |

| bit 2-1      | Unimpleme            | nted: Read as                                                                                  | 0'              |                |                    |                |              |  |

| bit 0        | MDBIT: Allo          | <b>MDBIT:</b> Allows software to manually set modulation source input to module <sup>(2)</sup> |                 |                |                    |                |              |  |

|              |                      | or uses High C                                                                                 |                 |                | ·                  |                |              |  |

|              | 0 = Modulat          | or uses Low Ca                                                                                 | arrier source   |                |                    |                |              |  |

| Note 1:      | The modulated o      | utput frequency                                                                                | can be greate   | r and asynchro | onous from the c   | lock that upd  | ates this    |  |

|              | register bit, the bi |                                                                                                |                 |                |                    |                |              |  |

#### **REGISTER 23-1: MDCON: MODULATION CONTROL REGISTER**

2: MDBIT must be selected as the modulation source in the MDSRC register for this operation.

| R/W-x/u                 | R/W-x/u                   | R/W-x/u                              | U-0          | R/W-x/u            | R/W-x/u                       | R/W-x/u         | R/W-x/u          |

|-------------------------|---------------------------|--------------------------------------|--------------|--------------------|-------------------------------|-----------------|------------------|

| MDCLODIS                | MDCLPOL                   | MDCLSYNC                             |              |                    | MDCL                          | _<3:0>          |                  |

| bit 7                   |                           |                                      |              |                    |                               |                 | bit 0            |

| Lonondi                 |                           |                                      |              |                    |                               |                 |                  |

| Legend:<br>R = Readable | hit                       | W = Writable bi                      | +            | II = I Inimpler    | nented bit, read              | l as 'N'        |                  |

| u = Bit is unch         |                           | x = Bit is unkno                     |              | •                  | at POR and BO                 |                 | ther Resets      |

| '1' = Bit is set        | angeu                     | '0' = Bit is clear                   |              |                    |                               |                 |                  |

| I – DILIS SEL           |                           |                                      | eu           |                    |                               |                 |                  |

| bit 7                   | MDCLODIS:                 | Modulator Low C                      | Carrier Out  | out Disable bit    |                               |                 |                  |

|                         |                           | ignal driving the                    |              |                    | ted by MDCL<3                 | 3:0> of the MD  | CARL register)   |

|                         | is disable                |                                      |              |                    | -                             |                 |                  |

|                         | 0 = Output s<br>is enable | ignal driving the p<br>ed            | peripheral o | output pin (selec  | ted by MDCL<3                 | 3:0> of the MD0 | CARL register)   |

| bit 6                   | MDCLPOL:                  | Modulator Low C                      | arrier Pola  | rity Select bit    |                               |                 |                  |

|                         |                           | l low carrier signa                  |              |                    |                               |                 |                  |

|                         |                           | l low carrier signa                  |              |                    |                               |                 |                  |

| bit 5                   |                           | : Modulator Low                      | -            |                    |                               |                 | ····             |

|                         | 1 = Modulato              | or waits for a fallin<br>rier        | ng eage on   | the low time carr  | rier signal before            | e allowing a sw | itch to the high |

|                         |                           | or Output is not s                   | ynchronize   | d to the low time  | e carrier signal <sup>(</sup> | 1)              |                  |

| bit 4                   | Unimplemer                | ted: Read as '0'                     |              |                    |                               |                 |                  |

| bit 3-0                 | MDCL<3:0>                 | Modulator Data H                     | High Carrie  | r Selection bits ( | [1]                           |                 |                  |

|                         | 1111 = Res                | erved. No chanr                      | nel connect  | ed.                |                               |                 |                  |

|                         | •                         |                                      |              |                    |                               |                 |                  |

|                         | •                         |                                      |              |                    |                               |                 |                  |

|                         | 1000 = Res                | erved. No chanr                      | nel connect  | ed.                |                               |                 |                  |

|                         |                           | P4 output (PWM                       |              |                    |                               |                 |                  |

|                         |                           | P3 output (PWM                       |              |                    |                               |                 |                  |

|                         |                           | P2 output (PWM (<br>P1 output (PWM ( |              |                    |                               |                 |                  |

|                         |                           | erence Clock mo                      |              |                    |                               |                 |                  |

|                         | 0010 = MD0                | CIN2 port pin                        | -            |                    |                               |                 |                  |

|                         | 0001 = MD0                |                                      |              |                    |                               |                 |                  |

|                         | 0000 = Vss                |                                      |              |                    |                               |                 |                  |

#### REGISTER 23-4: MDCARL: MODULATION LOW CARRIER CONTROL REGISTER

Note 1: Narrowed carrier pulse widths or spurs may occur in the signal stream if the carrier is not synchronized.

| Name   | Bit 7    | Bit 6   | Bit 5    | Bit 4  | Bit 3 | Bit 2 | Bit 1   | Bit 0 | Register<br>on Page |

|--------|----------|---------|----------|--------|-------|-------|---------|-------|---------------------|

| MDCARH | MDCHODIS | MDCHPOL | MDCHSYNC | _      |       | MDCH  | <3:0>   |       | 200                 |

| MDCARL | MDCLODIS | MDCLPOL | MDCLSYNC | _      |       | MDCL  | <3:0>   |       | 201                 |

| MDCON  | MDEN     | MDOE    | MDSLR    | MDOPOL | MDOUT | _     | _       | MDBIT | 198                 |

| MDSRC  | MDMSODIS |         | —        | —      |       | MDMS  | \$<3:0> |       | 199                 |

Legend: — = unimplemented, read as '0'. Shaded cells are not used in the Data Signal Modulator mode.

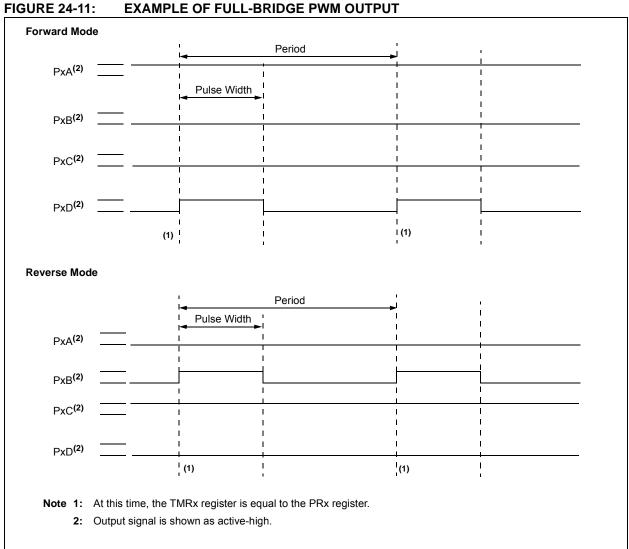

FIGURE 24-11:

| U-0            | U-0                                                                    | U-0              | R/W-0/0          | R/W-0/0          | R/W-0/0           | R/W-0/0          | R/W-1/1      |

|----------------|------------------------------------------------------------------------|------------------|------------------|------------------|-------------------|------------------|--------------|

| _              | —                                                                      | —                | STRxSYNC         | STRxD            | STRxC             | STRxB            | STRxA        |

| bit 7          |                                                                        |                  |                  |                  |                   |                  | bit 0        |

|                |                                                                        |                  |                  |                  |                   |                  |              |

| Legend:        |                                                                        |                  |                  |                  |                   |                  |              |

| R = Readab     | ole bit                                                                | W = Writable     | bit              | U = Unimpler     | mented bit, read  | d as '0'         |              |

| u = Bit is un  | changed                                                                | x = Bit is unk   | nown             | -n/n = Value a   | at POR and BO     | R/Value at all o | other Resets |

| '1' = Bit is s | et                                                                     | '0' = Bit is cle | ared             |                  |                   |                  |              |

|                |                                                                        |                  |                  |                  |                   |                  |              |

| bit 7-5        | Unimplemer                                                             | nted: Read as    | '0'              |                  |                   |                  |              |

| bit 4          |                                                                        | Steering Sync    |                  |                  |                   |                  |              |

|                |                                                                        |                  | occurs on next   |                  |                   |                  |              |

|                | 0 = Output st                                                          | teering update   | occurs at the b  | eginning of the  | e instruction cyc | le boundary      |              |

| bit 3          |                                                                        | ering Enable bi  |                  |                  |                   |                  |              |

|                | •                                                                      |                  | vaveform with p  | olarity control  | from CCPxM<1      | 1:0>             |              |

|                | 0 = PxD pin i                                                          | s assigned to p  | port pin         |                  |                   |                  |              |

| bit 2          |                                                                        | ering Enable bi  |                  |                  |                   |                  |              |

|                |                                                                        |                  | vaveform with p  | polarity control | from CCPxM<1      | 1:0>             |              |

|                | •                                                                      | s assigned to p  | •                |                  |                   |                  |              |

| bit 1          | STRxB: Stee                                                            | ering Enable bi  | t B              |                  |                   |                  |              |

|                | 1 = PxB pin has the PWM waveform with polarity control from CCPxM<1:0> |                  |                  |                  |                   |                  |              |

|                | 0 = PxB pin i                                                          | s assigned to p  | oort pin         |                  |                   |                  |              |

| bit 0          | STRxA: Steering Enable bit A                                           |                  |                  |                  |                   |                  |              |

|                | 1 = PxA pin ł                                                          | nas the PWM v    | vaveform with p  | olarity control  | from CCPxM<1      | 1:0>             |              |

|                | 0 = PxA pin i                                                          | s assigned to p  | oort pin         |                  |                   |                  |              |

| Note 1: 1      | The PWM Steerin                                                        | a modo is avai   | ilabla only whor |                  | N register bits ( | ~~DvM~3·2~ -     | - 11 ond     |

## **REGISTER 24-5: PSTRxCON: PWM STEERING CONTROL REGISTER<sup>(1)</sup>**

Note 1: The PWM Steering mode is available only when the CCPxCON register bits CCPxM<3:2> = 11 and PxM<1:0> = 00.

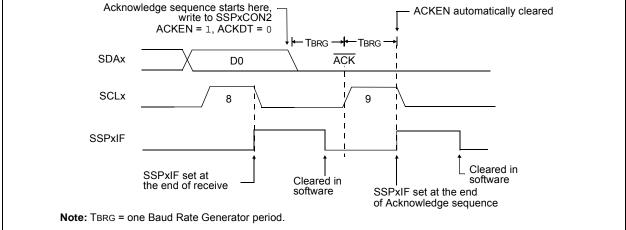

#### 25.6.8 ACKNOWLEDGE SEQUENCE TIMING

An Acknowledge sequence is enabled by setting the Acknowledge Sequence Enable bit, ACKEN bit of the SSPxCON2 register. When this bit is set, the SCLx pin is pulled low and the contents of the Acknowledge data bit are presented on the SDAx pin. If the user wishes to generate an Acknowledge, then the ACKDT bit should be cleared. If not, the user should set the ACKDT bit before starting an Acknowledge sequence. The Baud Rate Generator then counts for one rollover period (TBRG) and the SCLx pin is deasserted (pulled high). When the SCLx pin is sampled high (clock arbitration), the Baud Rate Generator counts for TBRG. The SCLx pin is then pulled low. Following this, the ACKEN bit is automatically cleared, the Baud Rate Generator is turned off and the MSSPx module then goes into Idle mode (Figure 25-29).

#### 25.6.8.1 WCOL Status Flag

If the user writes the SSPxBUF when an Acknowledge sequence is in progress, then WCOL is set and the contents of the buffer are unchanged (the write does not occur).

#### 25.6.9 STOP CONDITION TIMING