Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Product Status             | Active                                                                   |

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 32MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                        |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 16                                                                       |

| Program Memory Size        | 3.5KB (2K x 14)                                                          |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 256 x 8                                                                  |

| RAM Size                   | 256 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                              |

| Data Converters            | A/D 12x10b                                                               |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Through Hole                                                             |

| Package / Case             | 18-DIP (0.300", 7.62mm)                                                  |

| Supplier Device Package    | 18-PDIP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f1826-i-p |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 2.0 ENHANCED MID-RANGE CPU

This family of devices contain an enhanced mid-range 8-bit CPU core. The CPU has 49 instructions. Interrupt capability includes automatic context saving. The hardware stack is 16 levels deep and has Overflow and Underflow Reset capability. Direct, Indirect, and Relative addressing modes are available. Two File Select Registers (FSRs) provide the ability to read program and data memory.

- Automatic Interrupt Context Saving

- 16-level Stack with Overflow and Underflow

- File Select Registers

- Instruction Set

#### 2.1 Automatic Interrupt Context Saving

During interrupts, certain registers are automatically saved in shadow registers and restored when returning from the interrupt. This saves stack space and user code. See **Section 8.5 "Automatic Context Saving"**, for more information.

#### 2.2 16-level Stack with Overflow and Underflow

These devices have an external stack memory 15 bits wide and 16 words deep. A Stack Overflow or Underflow will set the appropriate bit (STKOVF or STKUNF) in the PCON register, and if enabled will cause a software Reset. See section **Section 3.4 "Stack"** for more details.

#### 2.3 File Select Registers

There are two 16-bit File Select Registers (FSR). FSRs can access all file registers and program memory, which allows one Data Pointer for all memory. When an FSR points to program memory, there is one additional instruction cycle in instructions using INDF to allow the data to be fetched. General purpose memory can now also be addressed linearly, providing the ability to access contiguous data larger than 80 bytes. There are also new instructions to support the FSRs. See **Section 3.4 "Stack**"for more details.

#### 2.4 Instruction Set

There are 49 instructions for the enhanced mid-range CPU to support the features of the CPU. See **Section 29.0** "Instruction Set Summary" for more details.

#### 8.6.3 PIE2 REGISTER

The PIE2 register contains the interrupt enable bits, as shown in Register 8-3.

**Note:** Bit PEIE of the INTCON register must be set to enable any peripheral interrupt.

| REGISTER 8-3: | PIE2: PERIPHERAL INTERRUPT ENABLE REGISTER 2 |

|---------------|----------------------------------------------|

|               |                                              |

| R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | U-0 | U-0 | R/W-0/0               |

|---------|---------|---------|---------|---------|-----|-----|-----------------------|

| OSFIE   | C2IE    | C1IE    | EEIE    | BCL1IE  | —   | _   | CCP2IE <sup>(1)</sup> |

| bit 7   |         |         |         |         |     |     | bit 0                 |

| Legend:          |                                                                                                                                   |                                                             |                                                       |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|-------------------------------------------------------|--|--|--|

| R = Readable bit |                                                                                                                                   | W = Writable bit                                            | U = Unimplemented bit, read as '0'                    |  |  |  |

| u = Bit is uncha | anged                                                                                                                             | x = Bit is unknown                                          | -n/n = Value at POR and BOR/Value at all other Resets |  |  |  |

| '1' = Bit is set |                                                                                                                                   | '0' = Bit is cleared                                        |                                                       |  |  |  |

| bit 7            |                                                                                                                                   | lator Fail Interrupt Enable                                 |                                                       |  |  |  |

|                  |                                                                                                                                   | the Oscillator Fail interrup<br>the Oscillator Fail interru |                                                       |  |  |  |

| bit 6            | C2IE: Compa                                                                                                                       | rator C2 Interrupt Enable                                   | e bit                                                 |  |  |  |

|                  | <ul> <li>1 = Enables the Comparator C2 interrupt</li> <li>0 = Disables the Comparator C2 interrupt</li> </ul>                     |                                                             |                                                       |  |  |  |

| bit 5            | C1IE: Compa                                                                                                                       | rator C1 Interrupt Enable                                   | bit                                                   |  |  |  |

|                  | <ul> <li>1 = Enables the Comparator C1 interrupt</li> <li>0 = Disables the Comparator C1 interrupt</li> </ul>                     |                                                             |                                                       |  |  |  |

| bit 4            | EEIE: EEPRO                                                                                                                       | OM Write Completion Inte                                    | errupt Enable bit                                     |  |  |  |

|                  | <ul> <li>1 = Enables the EEPROM Write Completion interrupt</li> <li>0 = Disables the EEPROM Write Completion interrupt</li> </ul> |                                                             |                                                       |  |  |  |

| bit 3            | BCL1IE: MSS                                                                                                                       | SP1 Bus Collision Interrup                                  | pt Enable bit                                         |  |  |  |

|                  | <ul> <li>1 = Enables the MSSP1 Bus Collision Interrupt</li> <li>0 = Disables the MSSP1 Bus Collision Interrupt</li> </ul>         |                                                             |                                                       |  |  |  |

| bit 2-1          | Unimplemented: Read as '0'                                                                                                        |                                                             |                                                       |  |  |  |

| bit 0            | CCP2IE: CCF                                                                                                                       | P2 Interrupt Enable bit                                     |                                                       |  |  |  |

|                  |                                                                                                                                   | the CCP2 interrupt the CCP2 interrupt                       |                                                       |  |  |  |

Note 1: PIC16(L)F1827 only.

#### 8.6.4 PIE3 REGISTER

The PIE3 register contains the interrupt enable bits, as shown in Register 8-4.

| Note: | Bit PEIE of the INTCON register must be |

|-------|-----------------------------------------|

|       | set to enable any peripheral interrupt. |

| U-0   | U-0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | U-0 | R/W-0/0 | U-0   |

|-------|-----|---------|---------|---------|-----|---------|-------|

| —     | —   | CCP4IE  | CCP3IE  | TMR6IE  | —   | TMR4IE  | —     |

| bit 7 |     |         |         |         |     |         | bit 0 |

| Legend:          |                                                                                                                       |                            |                                                       |  |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------|----------------------------|-------------------------------------------------------|--|--|--|--|

| R = Readable     | e bit                                                                                                                 | W = Writable bit           | U = Unimplemented bit, read as '0'                    |  |  |  |  |

| u = Bit is unc   | hanged                                                                                                                | x = Bit is unknown         | -n/n = Value at POR and BOR/Value at all other Resets |  |  |  |  |

| '1' = Bit is set |                                                                                                                       | '0' = Bit is cleared       |                                                       |  |  |  |  |

| bit 7-6          | Unimplemer                                                                                                            | nted: Read as '0'          |                                                       |  |  |  |  |

| bit 5            | CCP4IE: CC                                                                                                            | P4 Interrupt Enable bit    |                                                       |  |  |  |  |

|                  |                                                                                                                       | the CCP4 interrupt         |                                                       |  |  |  |  |

|                  | 0 = Disables the CCP4 interrupt                                                                                       |                            |                                                       |  |  |  |  |

| bit 4            | CCP3IE: CCP3 Interrupt Enable bit                                                                                     |                            |                                                       |  |  |  |  |

|                  |                                                                                                                       | the CCP3 interrupt         |                                                       |  |  |  |  |

|                  | 0 = Disables                                                                                                          | the CCP3 interrupt         |                                                       |  |  |  |  |

| bit 3            | TMR6IE: TMR6 to PR6 Match Interrupt Enable bit                                                                        |                            |                                                       |  |  |  |  |

|                  |                                                                                                                       | the TMR6 to PR6 Match      |                                                       |  |  |  |  |

|                  | 0 = Disables                                                                                                          | the TMR6 to PR6 Match      | interrupt                                             |  |  |  |  |

| bit 2            | Unimplemer                                                                                                            | Unimplemented: Read as '0' |                                                       |  |  |  |  |

| bit 1            | TMR4IE: TM                                                                                                            | R4 to PR4 Match Interrup   | t Enable bit                                          |  |  |  |  |

|                  | <ul> <li>1 = Enables the TMR4 to PR4 Match interrupt</li> <li>0 = Disables the TMR4 to PR4 Match interrupt</li> </ul> |                            |                                                       |  |  |  |  |

bit 0 Unimplemented: Read as '0'

**Note 1:** This register is only available on PIC16(L)F1827.

#### 8.6.7 PIR2 REGISTER

The PIR2 register contains the interrupt flag bits, as shown in Register 8-7.

Note: Interrupt flag bits are set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the Global Enable bit, GIE, of the INTCON register. User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

#### REGISTER 8-7: PIR2: PERIPHERAL INTERRUPT REQUEST REGISTER 2

| <b>B</b> # 4 / 6 / 6 | <b>B</b> 4 4 4 6 4 5     | B 8 4 / 6 / 5             | B 4 4 4 6 15         | B 4 4 4 4      |                  |                | <b>B</b> 444 6 / 5    |  |  |

|----------------------|--------------------------|---------------------------|----------------------|----------------|------------------|----------------|-----------------------|--|--|

| R/W-0/0              | R/W-0/0                  | R/W-0/0                   | R/W-0/0              | R/W-0/0        | U-0              | U-0            | R/W-0/0               |  |  |

| OSFIF                | C2IF                     | C1IF                      | EEIF                 | BCL1IF         | —                | <u> </u>       | CCP2IF <sup>(1)</sup> |  |  |

| bit 7                |                          |                           |                      |                |                  |                | bit C                 |  |  |

|                      |                          |                           |                      |                |                  |                |                       |  |  |

| Legend:              |                          |                           |                      |                |                  |                |                       |  |  |

| R = Readable         | bit                      | W = Writable              | bit                  | U = Unimpler   | mented bit, read | as '0'         |                       |  |  |

| u = Bit is unch      | anged                    | x = Bit is unkr           | nown                 | -n/n = Value a | at POR and BO    | R/Value at all | other Resets          |  |  |

| '1' = Bit is set     |                          | '0' = Bit is cle          | ared                 |                |                  |                |                       |  |  |

|                      |                          |                           |                      |                |                  |                |                       |  |  |

| bit 7                | <b>OSFIF:</b> Oscil      | llator Fail Interru       | upt Flag bit         |                |                  |                |                       |  |  |

|                      | 1 = Interrupt            | 1 0                       |                      |                |                  |                |                       |  |  |

|                      | 0 = Interrupt            | is not pending            |                      |                |                  |                |                       |  |  |

| bit 6                | C2IF: Compa              | arator C2 Interru         | upt Flag bit         |                |                  |                |                       |  |  |

|                      |                          | 1 = Interrupt is pending  |                      |                |                  |                |                       |  |  |

|                      | -                        | is not pending            |                      |                |                  |                |                       |  |  |

| bit 5                |                          | arator C1 Interru         | upt Flag bit         |                |                  |                |                       |  |  |

|                      | 1 = Interrupt            | is penaing is not pending |                      |                |                  |                |                       |  |  |

| bit 4                |                          | OM Write Com              | letion Interru       | nt Flag bit    |                  |                |                       |  |  |

| 511 4                | 1 = Interrupt            |                           |                      | pt i lag bit   |                  |                |                       |  |  |

|                      |                          | is not pending            |                      |                |                  |                |                       |  |  |

| bit 3                | BCL1IF: MS               | SP1 Bus Collisi           | on Interrupt F       | lag bit        |                  |                |                       |  |  |

|                      | 1 = Interrupt is pending |                           |                      |                |                  |                |                       |  |  |

|                      | 0 = Interrupt            | is not pending            |                      |                |                  |                |                       |  |  |

| bit 2-1              | Unimplemer               | nted: Read as '           | 0'                   |                |                  |                |                       |  |  |

| bit 0                | CCP2IF: CC               | P2 Interrupt Fla          | g bit <sup>(1)</sup> |                |                  |                |                       |  |  |

|                      | 1 = Interrupt            |                           |                      |                |                  |                |                       |  |  |

|                      | 0 = Interrupt            | is not pending            |                      |                |                  |                |                       |  |  |

Note 1: PIC16(L)F1827 only.

#### 8.6.9 PIR4 REGISTER<sup>(1)</sup>

The PIR4 register contains the interrupt flag bits, as shown in Register 8-9.

- **Note 1:** The PIR4 register is available only on the PIC16(L)F1827 device.

- 2: Interrupt flag bits are set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the Global Enable bit, GIE, of the INTCON register. User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

#### **REGISTER 8-9: PIR4: PERIPHERAL INTERRUPT REQUEST REGISTER 4<sup>(1)</sup>**

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | R/W/HS-0/0 | R/W/HS-0/0 |

|-------|-----|-----|-----|-----|-----|------------|------------|

| —     | —   | —   | —   | —   | —   | BCL2IF     | SSP2IF     |

| bit 7 |     |     |     |     |     |            | bit 0      |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | HS = Bit is set by hardware                           |

| bit 7-2 | Unimplemented: Read as '0'                                                                                                                                                                                                                                 |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 1   | BCL2IF: MSSP2 Bus Collision Interrupt Flag bit                                                                                                                                                                                                             |

|         | <ul><li>1 = A Bus Collision was detected (must be cleared in software)</li><li>0 = No Bus collision was detected</li></ul>                                                                                                                                 |

| bit 0   | <ul> <li>SSP2IF: Master Synchronous Serial Port 2 (MSSP2) Interrupt Flag bit</li> <li>1 = The Transmission/Reception/Bus Condition is complete (must be cleared in software)</li> <li>0 = Waiting to Transmit/Receive/Bus Condition in progress</li> </ul> |

**Note 1:** This register is only available on PIC16(L)F1827.

#### TABLE 8-1: SUMMARY OF REGISTERS ASSOCIATED WITH INTERRUPTS

| Name                | Bit 7   | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0                 | Register<br>on Page |

|---------------------|---------|--------|--------|--------|--------|--------|--------|-----------------------|---------------------|

| INTCON              | GIE     | PEIE   | TMR0IE | INTE   | IOCIE  | TMR0IF | INTF   | IOCIF                 | 86                  |

| OPTION_REG          | WPUEN   | INTEDG | TMR0CS | TMR0SE | PSA    | PS2    | PS1    | PS0                   | 177                 |

| PIE1                | TMR1GIE | ADIE   | RCIE   | TXIE   | SSP1IE | CCP1IE | TMR2IE | TMR1IE                | 87                  |

| PIE2                | OSFIE   | C2IE   | C1IE   | EEIE   | BCL1IE | —      | _      | CCP2IE <sup>(1)</sup> | 88                  |

| PIE3 <sup>(1)</sup> | _       | -      | CCP4IE | CCP3IE | TMR6IE | _      | TMR4IE | _                     | 89                  |

| PIE4 <sup>(1)</sup> | _       | -      | _      | _      | -      | _      | BCL2IE | SSP2IE                | 90                  |

| PIR1                | TMR1GIF | ADIF   | RCIF   | TXIF   | SSP1IF | CCP1IF | TMR2IF | TMR1IF                | 91                  |

| PIR2                | OSFIF   | C2IF   | C1IF   | EEIF   | BCL1IF | —      | _      | CCP2IF <sup>(1)</sup> | 92                  |

| PIR3 <sup>(1)</sup> | _       | _      | CCP4IF | CCP3IF | TMR6IF | _      | TMR4IF | _                     | 93                  |

| PIR4 <sup>(1)</sup> | _       | _      | _      | _      | _      | _      | BCL2IF | SSP2IF                | 94                  |

Legend: — = unimplemented locations read as '0'. Shaded cells are not used by Interrupts.

Note 1: PIC16(L)F1827 only.

#### 11.3 Flash Program Memory Overview

It is important to understand the Flash program memory structure for erase and programming operations. Flash Program memory is arranged in rows. A row consists of a fixed number of 14-bit program memory words. A row is the minimum block size that can be erased by user software.

Flash program memory may only be written or erased if the destination address is in a segment of memory that is not write-protected, as defined in bits WRT<1:0> of Configuration Word 2.

After a row has been erased, the user can reprogram all or a portion of this row. Data to be written into the program memory row is written to 14-bit wide data write latches. These write latches are not directly accessible to the user, but may be loaded via sequential writes to the EEDATH:EEDATL register pair.

| Note: | If the user wants to modify only a portion |

|-------|--------------------------------------------|

|       | of a previously programmed row, then the   |

|       | contents of the entire row must be read    |

|       | and saved in RAM prior to the erase.       |

The number of data write latches may not be equivalent to the number of row locations. During programming, user software may need to fill the set of write latches and initiate a programming operation multiple times in order to fully reprogram an erased row. For example, a device with a row size of 32 words and eight write latches will need to load the write latches with data and initiate a programming operation four times.

The size of a program memory row and the number of program memory write latches may vary by device. See Table 11-1 for details.

### TABLE 11-1:FLASH MEMORY<br/>ORGANIZATION BY DEVICE

| Device           | Erase Block<br>(Row) Size/<br>Boundary | Number of<br>Write Latches/<br>Boundary |  |

|------------------|----------------------------------------|-----------------------------------------|--|

| PIC16(L)F1826/27 | 32 words,                              | 32 words,                               |  |

|                  | EEADRL<4:0>                            | EEADRL<4:0>                             |  |

|                  | = 00000                                | = 00000                                 |  |

### 11.3.1 READING THE FLASH PROGRAM MEMORY

To read a program memory location, the user must:

- 1. Write the Least and Most Significant address bits to the EEADRH:EEADRL register pair.

- 2. Clear the CFGS bit of the EECON1 register.

- 3. Set the EEPGD control bit of the EECON1 register.

- 4. Then, set control bit RD of the EECON1 register.

Once the read control bit is set, the program memory Flash controller will use the second instruction cycle to read the data. This causes the second instruction immediately following the "BSF EECON1, RD" instruction to be ignored. The data is available in the very next cycle, in the EEDATH:EEDATL register pair; therefore, it can be read as two bytes in the following instructions.

EEDATH:EEDATL register pair will hold this value until another read or until it is written to by the user.

- Note 1: The two instructions following a program memory read are required to be NOPS. This prevents the user from executing a two-cycle instruction on the next instruction after the RD bit is set.

- 2: Flash program memory can be read regardless of the setting of the CP bit.

#### 12.2.3 PORTA FUNCTIONS AND OUTPUT PRIORITIES

Each PORTA pin is multiplexed with other functions. The pins, their combined functions and their output priorities are shown in Table 12-2.

When multiple outputs are enabled, the actual pin control goes to the peripheral with the highest priority.

Analog input functions, such as ADC, comparator and CapSense inputs, are not shown in the priority lists. These inputs are active when the I/O pin is set for Analog mode using the ANSELx registers. Digital output functions may control the pin when it is in Analog mode with the priority shown in Table 12-2.

| Pin Name | Function Priority <sup>(1)</sup>                                                                                     |

|----------|----------------------------------------------------------------------------------------------------------------------|

| RA0      | SDO2 (PIC16(L)F1827 only)<br>RA0                                                                                     |

| RA1      | SS2 (PIC16(L)F1827 only)<br>RA1                                                                                      |

| RA2      | DACOUT (DAC)<br>RA2                                                                                                  |

| RA3      | SRQ (SR latch)<br>CCP3 (PIC16(L)F1827 only)<br>C1OUT (Comparator)<br>RA3                                             |

| RA4      | SRNQ (SR latch)<br>CCP4 (PIC16(L)F1827 only)<br>T0CKI<br>C2OUT (Comparator)<br>RA4                                   |

| RA5      | Input only pin                                                                                                       |

| RA6      | OSC2 (enabled by Configura-<br>tion Word)<br>CLKOUT<br>CLKR<br>SDO1<br>P1D<br>P2B (PIC16(L)F1827 only)<br>RA6        |

| RA7      | OSC1/CLKIN (enabled by<br>Configuration Word)<br>P1C<br>CCP2 (PIC16(L)F1827 only)<br>P2A (PIC16(L)F1827 only)<br>RA7 |

TABLE 12-2: PORTA OUTPUT PRIORITY

**Note 1:** Priority listed from highest to lowest.

Each PORTA pin is multiplexed with other functions. The pins, their combined functions and their output priorities are briefly described here. For additional information, refer to the appropriate section in this data sheet.

When multiple outputs are enabled, the actual pin control goes to the peripheral with the lowest number in the following lists.

#### 13.6 Interrupt-On-Change Registers

#### REGISTER 13-1: IOCBP: INTERRUPT-ON-CHANGE POSITIVE EDGE REGISTER

| '1' = Bit is set                        |         | '0' = Bit is clea | ared           |                                    |                  |             |         |

|-----------------------------------------|---------|-------------------|----------------|------------------------------------|------------------|-------------|---------|

| u = Bit is unchanged x = Bit is unknown |         | nown              | -n/n = Value a | at POR and BO                      | R/Value at all o | ther Resets |         |

| R = Readable bit W = Writable bit       |         |                   | bit            | U = Unimplemented bit, read as '0' |                  |             |         |

| Legend:                                 |         |                   |                |                                    |                  |             |         |

|                                         |         |                   |                |                                    |                  |             |         |

| bit 7                                   | •       | •                 |                | •                                  |                  |             | bit 0   |

| IOCBP7                                  | IOCBP6  | IOCBP5            | IOCBP4         | IOCBP3                             | IOCBP2           | IOCBP1      | IOCBP0  |

| R/W-0/0                                 | R/W-0/0 | R/W-0/0           | R/W-0/0        | R/W-0/0                            | R/W-0/0          | R/W-0/0     | R/W-0/0 |

bit 7-0

**IOCBP<7:0>:** Interrupt-on-Change Positive Edge Enable bits

- 1 = Interrupt-on-change enabled on the pin for a positive going edge. Associated Status bit and interrupt flag will be set upon detecting an edge.

- 0 = Interrupt-on-change disabled for the associated pin.

#### REGISTER 13-2: IOCBN: INTERRUPT-ON-CHANGE NEGATIVE EDGE REGISTER

| R/W-0/0 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| IOCBN7  | IOCBN6  | IOCBN5  | IOCBN4  | IOCBN3  | IOCBN2  | IOCBN1  | IOCBN0  |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0

IOCBN<7:0>: Interrupt-on-Change Negative Edge Enable bits

- 1 = Interrupt-on-change enabled on the pin for a negative going edge. Associated Status bit and interrupt flag will be set upon detecting an edge.

- 0 = Interrupt-on-change disabled for the associated pin.

#### REGISTER 13-3: IOCBF: INTERRUPT-ON-CHANGE FLAG REGISTER

| R/W/HS-0/0 |

|------------|------------|------------|------------|------------|------------|------------|------------|

| IOCBF7     | IOCBF6     | IOCBF5     | IOCBF4     | IOCBF3     | IOCBF2     | IOCBF1     | IOCBF0     |

| bit 7      |            |            |            |            |            |            | bit 0      |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | HS - Bit is set in hardware                           |

bit 7-0

IOCBF<7:0>: Interrupt-on-Change Flag bits

- 1 = An enabled change was detected on the associated pin.

Set when IOCBPx = 1 and a rising edge was detected on RBx, or when IOCBNx = 1 and a falling edge was detected on RBx.

- 0 = No change was detected, or the user cleared the detected change.

#### 22.4 Timer2 Control Register

| U-0                  | R/W-0/0            | R/W-0/0                                        | R/W-0/0        | R/W-0/0        | R/W-0/0          | R/W-0/0          | R/W-0/0      |  |

|----------------------|--------------------|------------------------------------------------|----------------|----------------|------------------|------------------|--------------|--|

|                      |                    | TxOUTF                                         | PS<3:0>        |                | TMRxON           | TxCKP            | S<1:0>       |  |

| pit 7                | ·                  |                                                |                |                |                  |                  | bit          |  |

|                      |                    |                                                |                |                |                  |                  |              |  |

| Legend:              | la hit             |                                                |                |                | nonted bit rece  |                  |              |  |

| R = Readab           |                    | W = Writable                                   |                |                | nented bit, read |                  | - 44 D 4-    |  |

| u = Bit is unchanged |                    | x = Bit is unkn                                |                | -n/n = value a | at POR and BO    | R/value at all o | other Resets |  |

| 1' = Bit is s        | et                 | '0' = Bit is clea                              | ared           |                |                  |                  |              |  |

| oit 7                | Unimplem           | ented: Read as '                               | כי             |                |                  |                  |              |  |

| oit 6-3              | TxOUTPS            | <3:0>: Timerx Ou                               | tput Postscale | er Select bits |                  |                  |              |  |

|                      | 0000 = 1:1         | Postscaler                                     |                |                |                  |                  |              |  |

| 00<br>00<br>01       |                    | 2 Postscaler                                   |                |                |                  |                  |              |  |

|                      |                    | 0010 = 1:3 Postscaler                          |                |                |                  |                  |              |  |

|                      |                    | 0011 = 1:4 Postscaler                          |                |                |                  |                  |              |  |

|                      |                    | 0100 = 1:5 Postscaler<br>0101 = 1:6 Postscaler |                |                |                  |                  |              |  |

|                      |                    | : 1.7 Postscaler                               |                |                |                  |                  |              |  |

|                      |                    | Postscaler                                     |                |                |                  |                  |              |  |

|                      | 1000 <b>= 1</b> :9 | Postscaler                                     |                |                |                  |                  |              |  |

|                      |                    | 0 Postscaler                                   |                |                |                  |                  |              |  |

|                      |                    | 1 Postscaler                                   |                |                |                  |                  |              |  |

|                      |                    | 2 Postscaler<br>3 Postscaler                   |                |                |                  |                  |              |  |

|                      |                    | 4 Postscaler                                   |                |                |                  |                  |              |  |

|                      |                    | 5 Postscaler                                   |                |                |                  |                  |              |  |

|                      | 1111 <b>= 1:1</b>  | 6 Postscaler                                   |                |                |                  |                  |              |  |

| oit 2                | TMRxON:            | Timerx On bit                                  |                |                |                  |                  |              |  |

|                      | 1 = Timer          | 1 = Timerx is on                               |                |                |                  |                  |              |  |

|                      | 0 = Timer          | k is off                                       |                |                |                  |                  |              |  |

| oit 1-0              | TxCKPS<            | 1:0>: Timer2-type                              | Clock Presca   | le Select bits |                  |                  |              |  |

|                      | 00 <b>= Presc</b>  |                                                |                |                |                  |                  |              |  |

|                      | 01 = Presc         |                                                |                |                |                  |                  |              |  |

|                      | 10 <b>= Presc</b>  |                                                |                |                |                  |                  |              |  |

|                      | 11 = Presc         | aler is 64                                     |                |                |                  |                  |              |  |

#### 24.0 CAPTURE/COMPARE/PWM MODULES

The Capture/Compare/PWM module is a peripheral which allows the user to time and control different events, and to generate Pulse-Width Modulation (PWM) signals. In Capture mode, the peripheral allows the timing of the duration of an event. The Compare mode allows the user to trigger an external event when a predetermined amount of time has expired. The PWM mode can generate Pulse-Width Modulated signals of varying frequency and duty cycle.

This family of devices contains two Enhanced Capture/Compare/PWM modules (ECCP1 and ECCP2) and two standard Capture/Compare/PWM modules (CCP3 and CCP4).

The Capture and Compare functions are identical for all four CCP modules (ECCP1, ECCP2, CCP3 and CCP4). The only differences between CCP modules are in the Pulse-Width Modulation (PWM) function. The standard PWM function is identical in modules, CCP3 and CCP4. In CCP modules ECCP1 and ECCP2, the Enhanced PWM function has slight variations from one another. Full-Bridge ECCP modules have four available I/O pins while Half-Bridge ECCP modules only have two available I/O pins. See Table 24-1 for more information.

- Note 1: In devices with more than one CCP module, it is very important to pay close attention to the register names used. A number placed after the module acronym is used to distinguish between separate modules. For example, the CCP1CON and CCP2CON control the same operational aspects of two completely different CCP modules.

- 2: Throughout this section, generic references to a CCP module in any of its operating modes may be interpreted as being equally applicable to ECCP1, ECCP2, CCP3 and CCP4. Register names, module signals, I/O pins, and bit names may use the generic designator 'x' to indicate the use of a numeral to distinguish a particular module, when required.

#### TABLE 24-1:PWM RESOURCES

| Device Name   | ECCP1                       | ECCP2                       | CCP3          | CCP4          |

|---------------|-----------------------------|-----------------------------|---------------|---------------|

| PIC16(L)F1826 | Enhanced PWM<br>Full-Bridge | Not Available               | Not Available | Not Available |

| PIC16(L)F1827 | Enhanced PWM<br>Full-Bridge | Enhanced PWM<br>Half-Bridge | Standard PWM  | Standard PWM  |

#### 24.3.7 OPERATION IN SLEEP MODE

In Sleep mode, the TMRx register will not increment and the state of the module will not change. If the CCPx pin is driving a value, it will continue to drive that value. When the device wakes up, TMRx will continue from its previous state.

#### 24.3.8 CHANGES IN SYSTEM CLOCK FREQUENCY

The PWM frequency is derived from the system clock frequency. Any changes in the system clock frequency will result in changes to the PWM frequency. See Section 5.0 "Oscillator Module (With Fail-Safe Clock Monitor)" for additional details.

#### 24.3.9 EFFECTS OF RESET

Any Reset will force all ports to Input mode and the CCP registers to their Reset states.

#### 24.3.10 ALTERNATE PIN LOCATIONS

This module incorporates I/O pins that can be moved to other locations with the use of the alternate pin function registers, APFCON0 and APFCON1. To determine which pins can be moved and what their default locations are upon a reset, see **Section 12.1 "Alternate Pin Function"** for more information.

| Name     | Bit 7                                                        | Bit 6               | Bit 5    | Bit 4                 | Bit 3                  | Bit 2   | Bit 1   | Bit 0   | Register<br>on Page |

|----------|--------------------------------------------------------------|---------------------|----------|-----------------------|------------------------|---------|---------|---------|---------------------|

| APFCON0  | RXDTSEL                                                      | SDO1SEL             | SS1SEL   | P2BSEL <sup>(2)</sup> | CCP2SEL <sup>(2)</sup> | P1DSEL  | P1CSEL  | CCP1SEL | 119                 |

| CCPxCON  | PxM1 <sup>(1)</sup>                                          | PxM0 <sup>(1)</sup> | DCxB1    | DCxB0                 | CCPxM3                 | CCPxM2  | CCPxM1  | CCPxM0  | 226                 |

| CCPxAS   | CCPxASE                                                      | CCPxAS2             | CCPxAS1  | CCPxAS0               | PSSxAC1                | PSSxAC0 | PSSxBD1 | PSSxBD0 | 228                 |

| CCPTMRS  | C4TSEL1                                                      | C4TSEL0             | C3TSEL1  | C3TSEL0               | C2TSEL1                | C2TSEL0 | C1TSEL1 | C1TSEL0 | 227                 |

| INTCON   | GIE                                                          | PEIE                | TMR0IE   | INTE                  | IOCIE                  | TMR0IF  | INTF    | IOCIF   | 86                  |

| PR2      | Timer2 Period Register                                       |                     |          |                       |                        |         |         |         | 189*                |

| PR4      | Timer4 Module Period Register                                |                     |          |                       |                        |         |         |         | 189*                |

| PR6      | Timer6 Module Period Register                                |                     |          |                       |                        |         |         |         | 189*                |

| PSTRxCON | _                                                            | —                   | _        | STRxSYNC              | STRxD                  | STRxC   | STRxB   | STRxA   | 230                 |

| PWMxCON  | PxRSEN                                                       | PxDC6               | PxDC5    | PxDC4                 | PxDC3                  | PxDC2   | PxDC1   | PxDC0   | 229                 |

| T2CON    | —                                                            | T2OUTPS3            | T2OUTPS2 | T2OUTPS1              | T2OUTPS0               | TMR2ON  | T2CKPS1 | T2CKPS0 | 191                 |

| T4CON    | —                                                            | T4OUTPS3            | T4OUTPS2 | T4OUTPS1              | T4OUTPS0               | TMR4ON  | T4CKPS1 | T4CKPS0 | 191                 |

| T6CON    | —                                                            | T6OUTPS3            | T6OUTPS2 | T6OUTPS1              | T6OUTPS0               | TMR6ON  | T6CKPS1 | T6CKPS0 | 191                 |

| TMR2     | Holding Register for the 8-bit TMR2 Time Base                |                     |          |                       |                        |         |         |         | 189*                |

| TMR4     | Holding Register for the 8-bit TMR4 Time Base <sup>(1)</sup> |                     |          |                       |                        |         |         | 189*    |                     |

| TMR6     | Holding Register for the 8-bit TMR6 Time Base <sup>(1)</sup> |                     |          |                       |                        |         |         |         | 189*                |

| TRISB    | TRISB7                                                       | TRISB6              | TRISB5   | TRISB4                | TRISB3                 | TRISB2  | TRISB1  | TRISB0  | 127                 |

#### TABLE 24-8: SUMMARY OF REGISTERS ASSOCIATED WITH STANDARD PWM

**Legend:** — = Unimplemented locations, read as '0'. Shaded cells are not used by the PWM.

\* Page provides register information.

Note 1: Applies to ECCP modules only.

2: PIC16(L)F1827 only.

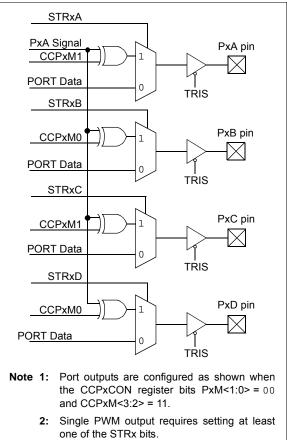

#### 24.4.6 PWM STEERING MODE

In Single Output mode, PWM steering allows any of the PWM pins to be the modulated signal. Additionally, the same PWM signal can be simultaneously available on multiple pins.

Once the Single Output mode is selected (CCPxM<3:2> = 11 and PxM<1:0> = 00 of the CCPxCON register), the user firmware can bring out the same PWM signal to one, two, three or four output pins by setting the appropriate STRx<D:A> bits of the PSTRxCON register, as shown in Register 24-5.

**Note:** The associated TRIS bits must be set to output ('0') to enable the pin output driver in order to see the PWM signal on the pin.

While the PWM Steering mode is active, CCPxM<1:0> bits of the CCPxCON register select the PWM output polarity for the Px<D:A> pins.

The PWM auto-shutdown operation also applies to PWM Steering mode as described in **Section 24.4.3 "Enhanced PWM Auto-shutdown mode"**. An auto-shutdown event will only affect pins that have PWM outputs enabled.

FIGURE 24-18: SIMPLIFIED STEERING BLOCK DIAGRAM

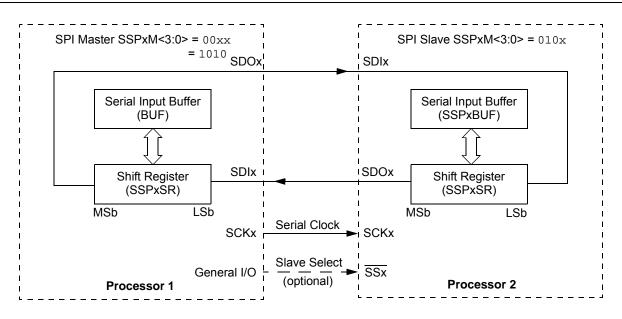

#### 25.2.2 SPI MODE OPERATION

When initializing the SPI, several options need to be specified. This is done by programming the appropriate control bits (SSPxCON1<5:0> and SSPxSTAT<7:6>). These control bits allow the following to be specified:

- · Master mode (SCKx is the clock output)

- · Slave mode (SCKx is the clock input)

- Clock Polarity (Idle state of SCKx)

- Data Input Sample Phase (middle or end of data output time)

- Clock Edge (output data on rising/falling edge of SCKx)

- Clock Rate (Master mode only)

- · Slave Select mode (Slave mode only)

To enable the serial port, SSPx Enable bit, SSPxEN of the SSPxCON1 register, must be set. To reset or reconfigure SPI mode, clear the SSPxEN bit, re-initialize the SSPxCONx registers and then set the SSPxEN bit. This configures the SDIx, SDOx, SCKx and SSx pins as serial port pins. For the pins to behave as the serial port function, some must have their data direction bits (in the TRIS register) appropriately programmed as follows:

- · SDIx must have corresponding TRIS bit set

- · SDOx must have corresponding TRIS bit cleared

- SCKx (Master mode) must have corresponding TRIS bit cleared

- SCKx (Slave mode) must have corresponding

TRIS bit set

- SSx must have corresponding TRIS bit set

Any serial port function that is not desired may be overridden by programming the corresponding data direction (TRIS) register to the opposite value.

The MSSPx consists of a transmit/receive shift register (SSPxSR) and a buffer register (SSPxBUF). The SSPxSR shifts the data in and out of the device, MSb first. The SSPxBUF holds the data that was written to the SSPxSR until the received data is ready. Once the 8 bits of data have been received, that byte is moved to the SSPxBUF register. Then, the Buffer Full Detect bit, BF of the SSPxSTAT register, and the interrupt flag bit, SSPxIF, are set. This double-buffering of the received data (SSPxBUF) allows the next byte to start reception before reading the data that was just received. Any write to the **SSPxBUF** reaister durina transmission/reception of data will be ignored and the write collision detect bit WCOL of the SSPxCON1 register, will be set. User software must clear the WCOL bit to allow the following write(s) to the SSPxBUF register to complete successfully.

When the application software is expecting to receive valid data, the SSPxBUF should be read before the next byte of data to transfer is written to the SSPxBUF. The Buffer Full bit, BF of the SSPxSTAT register, indicates when SSPxBUF has been loaded with the received data (transmission is complete). When the SSPxBUF is read, the BF bit is cleared. This data may be irrelevant if the SPI is only a transmitter. Generally, the MSSPx interrupt is used to determine when the transmission/reception has completed. If the interrupt method is not going to be used, then software polling can be done to ensure that a write collision does not occur.

#### FIGURE 25-5: SPI MASTER/SLAVE CONNECTION

#### 25.6.6 I<sup>2</sup>C MASTER MODE TRANSMISSION

Transmission of a data byte, a 7-bit address or the other half of a 10-bit address is accomplished by simply writing a value to the SSPxBUF register. This action will set the Buffer Full flag bit, BF and allow the Baud Rate Generator to begin counting and start the next transmission. Each bit of address/data will be shifted out onto the SDAx pin after the falling edge of SCLx is asserted. SCLx is held low for one Baud Rate Generator rollover count (TBRG). Data should be valid before SCLx is released high. When the SCLx pin is released high, it is held that way for TBRG. The data on the SDAx pin must remain stable for that duration and some hold time after the next falling edge of SCLx. After the eighth bit is shifted out (the falling edge of the eighth clock), the BF flag is cleared and the master releases SDAx. This allows the slave device being addressed to respond with an ACK bit during the ninth bit time if an address match occurred, or if data was received properly. The status of  $\overline{ACK}$  is written into the ACKSTAT bit on the rising edge of the ninth clock. If the master receives an Acknowledge, the Acknowledge Status bit, ACKSTAT, is cleared. If not, the bit is set. After the ninth clock, the SSPxIF bit is set and the master clock (Baud Rate Generator) is suspended until the next data byte is loaded into the SSPxBUF, leaving SCLx low and SDAx unchanged (Figure 25-27).

After the write to the SSPxBUF, each bit of the address will be shifted out on the falling edge of SCLx until all seven address bits and the R/W bit are completed. On the falling edge of the eighth clock, the master will release the SDAx pin, allowing the slave to respond with an Acknowledge. On the falling edge of the ninth clock, the master will sample the SDAx pin to see if the address was recognized by a slave. The status of the ACK bit is loaded into the ACKSTAT Status bit of the SSPxCON2 register. Following the falling edge of the ninth clock transmission of the address, the SSPxIF is set, the BF flag is cleared and the Baud Rate Generator is turned off until another write to the SSPxBUF takes place, holding SCLx low and allowing SDAx to float.

#### 25.6.6.1 BF Status Flag

In Transmit mode, the BF bit of the SSPxSTAT register is set when the CPU writes to SSPxBUF and is cleared when all 8 bits are shifted out.

#### 25.6.6.2 WCOL Status Flag

If the user writes the SSPxBUF when a transmit is already in progress (i.e., SSPxSR is still shifting out a data byte), the WCOL is set and the contents of the buffer are unchanged (the write does not occur).

WCOL must be cleared by software before the next transmission.

#### 25.6.6.3 ACKSTAT Status Flag

In Transmit mode, the ACKSTAT bit of the SSPxCON2 register is cleared when the slave has sent an Acknowledge (ACK = 0) and is set when the slave does not Acknowledge (ACK = 1). A slave sends an Acknowledge when it has recognized its address (including a general call), or when the slave has properly received its data.

25.6.6.4 Typical transmit sequence:

- 1. The user generates a Start condition by setting the SEN bit of the SSPxCON2 register.

- 2. SSPxIF is set by hardware on completion of the Start.

- 3. SSPxIF is cleared by software.

- 4. The MSSPx module will wait the required start time before any other operation takes place.

- 5. The user loads the SSPxBUF with the slave address to transmit.

- Address is shifted out the SDAx pin until all 8 bits are transmitted. Transmission begins as soon as SSPxBUF is written to.

- The MSSPx module shifts in the ACK bit from the slave device and writes its value into the ACKSTAT bit of the SSPxCON2 register.

- The MSSPx module generates an interrupt at the end of the ninth clock cycle by setting the SSPxIF bit.

- 9. The user loads the SSPxBUF with eight bits of data.

- 10. Data is shifted out the SDAx pin until all 8 bits are transmitted.

- 11. The MSSPx module shifts in the ACK bit from the slave device and writes its value into the ACKSTAT bit of the SSPxCON2 register.

- 12. Steps 8-11 are repeated for all transmitted data bytes.

- 13. The user generates a Stop or Restart condition by setting the PEN or RSEN bits of the SSPxCON2 register. Interrupt is generated once the Stop/Restart condition is complete.

#### REGISTER 25-2: SSPxCON1: SSPx CONTROL REGISTER 1

| R/C/HS-0/0              | R/C/HS-0/0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | R/W-0/0                                                                                                                                                                    | R/W-0/0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | R/W-0/0                                                                                                 | R/W-0/0                                    | R/W-0/0                                            | R/W-0/0                                     |

|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|--------------------------------------------|----------------------------------------------------|---------------------------------------------|

| WCOL                    | SSPxOV                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | SSPxEN                                                                                                                                                                     | CKP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                         | SSPx                                       | M<3:0>                                             |                                             |

| bit 7                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                         |                                            |                                                    | bit                                         |