Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 32MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 16                                                                        |

| Program Memory Size        | 3.5KB (2K x 14)                                                           |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 256 x 8                                                                   |

| RAM Size                   | 256 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                               |

| Data Converters            | A/D 12x10b                                                                |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 18-SOIC (0.295", 7.50mm Width)                                            |

| Supplier Device Package    | 18-SOIC                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f1826-i-so |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **TABLE 1-2:** PIC16(L)F1826/27 PINOUT DESCRIPTION (CONTINUED)

| Name                                                                                                      | Function | Input<br>Type     | Output<br>Type | Description                                                                                        |

|-----------------------------------------------------------------------------------------------------------|----------|-------------------|----------------|----------------------------------------------------------------------------------------------------|

| RA6/OSC2/CLKOUT/CLKR/                                                                                     | RA6      | TTL               | CMOS           | General purpose I/O.                                                                               |

| P1D <sup>(1)</sup> /P2B <sup>(1,2)</sup> /SDO1 <sup>(1)</sup>                                             | OSC2     | —                 | XTAL           | Crystal/Resonator (LP, XT, HS modes).                                                              |

|                                                                                                           | CLKOUT   | _                 | CMOS           | Fosc/4 output.                                                                                     |

|                                                                                                           | CLKR     | —                 | CMOS           | Clock Reference Output.                                                                            |

|                                                                                                           | P1D      | —                 | CMOS           | PWM output.                                                                                        |

|                                                                                                           | P2B      | —                 | CMOS           | PWM output.                                                                                        |

|                                                                                                           | SDO1     | —                 | CMOS           | SPI data output 1.                                                                                 |

| RA7/OSC1/CLKIN/P1C <sup>(1)</sup> /                                                                       | RA7      | TTL               | CMOS           | General purpose I/O.                                                                               |

| CCP2 <sup>(1,2)</sup> /P2A <sup>(1,2)</sup>                                                               | OSC1     | XTAL              | _              | Crystal/Resonator (LP, XT, HS modes).                                                              |

|                                                                                                           | CLKIN    | CMOS              | —              | External clock input (EC mode).                                                                    |

|                                                                                                           | P1C      | —                 | CMOS           | PWM output.                                                                                        |

|                                                                                                           | CCP2     | ST                | CMOS           | Capture/Compare/PWM2.                                                                              |

|                                                                                                           | P2A      | —                 | CMOS           | PWM output.                                                                                        |

| RB0/T1G/CCP1 <sup>(1)</sup> /P1A <sup>(1)</sup> /INT/<br>SRI/FLT0                                         | RB0      | TTL               | CMOS           | General purpose I/O. Individually controlled interrupt-on-change.<br>Individually enabled pull-up. |

|                                                                                                           | T1G      | ST                | _              | Timer1 Gate input.                                                                                 |

|                                                                                                           | CCP1     | ST                | CMOS           | Capture/Compare/PWM1.                                                                              |

|                                                                                                           | P1A      | _                 | CMOS           | PWM output.                                                                                        |

|                                                                                                           | INT      | ST                | —              | External interrupt.                                                                                |

|                                                                                                           | SRI      | ST                |                | SR latch input.                                                                                    |

|                                                                                                           | FLT0     | ST                |                | ECCP Auto-Shutdown Fault input.                                                                    |

| RB1/AN11/CPS11/RX <sup>(1,3)</sup> /<br>DT <sup>(1,3)</sup> /SDA1/SDI1                                    | RB1      | TTL               | CMOS           | General purpose I/O. Individually controlled interrupt-on-change.<br>Individually enabled pull-up. |

|                                                                                                           | AN11     | AN                |                | A/D Channel 11 input.                                                                              |

|                                                                                                           | CPS11    | AN                |                | Capacitive sensing input 11.                                                                       |

|                                                                                                           | RX       | ST                |                | USART asynchronous input.                                                                          |

|                                                                                                           | DT       | ST                | CMOS           | USART synchronous data.                                                                            |

|                                                                                                           | SDA1     | I <sup>2</sup> C™ | OD             | I <sup>2</sup> C™ data input/output 1.                                                             |

|                                                                                                           | SDI1     | CMOS              |                | SPI data input 1.                                                                                  |

| RB2/AN10/CPS10/MDMIN/<br>TX <sup>(1,3)</sup> /CK <sup>(1,3)</sup> /RX <sup>(1)</sup> /DT <sup>(1)</sup> / | RB2      | TTL               | CMOS           | General purpose I/O. Individually controlled interrupt-on-change.<br>Individually enabled pull-up. |

| SDA2 <sup>(2)</sup> /SDI2 <sup>(2)</sup> /SDO1 <sup>(1,3)</sup>                                           | AN10     | AN                |                | A/D Channel 10 input.                                                                              |

|                                                                                                           | CPS10    | AN                |                | Capacitive sensing input 10.                                                                       |

|                                                                                                           | MDMIN    | _                 | CMOS           | Modulator source input.                                                                            |

|                                                                                                           | ТΧ       | _                 | CMOS           | USART asynchronous transmit.                                                                       |

|                                                                                                           | СК       | ST                | CMOS           | USART synchronous clock.                                                                           |

|                                                                                                           | RX       | ST                | —              | USART asynchronous input.                                                                          |

|                                                                                                           | DT       | ST                | CMOS           | USART synchronous data.                                                                            |

|                                                                                                           | SDA2     | I <sup>2</sup> C™ | OD             | I <sup>2</sup> C™ data input/output 2.                                                             |

|                                                                                                           |          |                   |                |                                                                                                    |

|                                                                                                           | SDI2     | ST                | _              | SPI data input 2.                                                                                  |

Legend: AN = Analog input or output CMOS = CMOS compatible input or output

OD = Open Drain

TTL = TTL compatible input ST = Schmitt Trigger input with CMOS levels  $I^2C^{TM}$  = Schmitt Trigger input with  $I^2C$ HV = High Voltage XTAL = Crystal

levels

Note 1: Pin functions can be moved using the APFCON0 or APFCON1 register.

2: Functions are only available on the PIC16(L)F1827.

3: Default function location.

# 3.0 MEMORY ORGANIZATION

There are three types of memory in PIC16(L)F1826/27: Data Memory, Program Memory and Data EEPROM Memory<sup>(1)</sup>.

- Program Memory

- Data Memory

- Core Registers

- Special Function Registers

- General Purpose RAM

- Common RAM

- Device Memory Maps

- Special Function Registers Summary

- Data EEPROM memory<sup>(1)</sup>

Note 1: The Data EEPROM Memory and the method to access Flash memory through the EECON registers is described in Section 11.0 "Data EEPROM and Flash Program Memory Control". The following features are associated with access and control of program memory and data memory:

- PCL and PCLATH

- Stack

- Indirect Addressing

# 3.1 Program Memory Organization

The enhanced mid-range core has a 15-bit program counter capable of addressing a  $32K \times 14$  program memory space. Table 3-1 shows the memory sizes implemented for the PIC16(L)F1826/27 family. Accessing a location above these boundaries will cause a wrap-around within the implemented memory space. The Reset vector is at 0000h and the interrupt vector is at 0004h (see Figures 3-1 and 3-2).

# TABLE 3-1:DEVICE SIZES AND ADDRESSES

| Device        | Program Memory Space (Words) | Last Program Memory Address |

|---------------|------------------------------|-----------------------------|

| PIC16(L)F1826 | 2,048                        | 07FFh                       |

| PIC16(L)F1827 | 4,096                        | 0FFFh                       |

#### 8.6.3 PIE2 REGISTER

The PIE2 register contains the interrupt enable bits, as shown in Register 8-3.

**Note:** Bit PEIE of the INTCON register must be set to enable any peripheral interrupt.

| REGISTER 8-3: | PIE2: PERIPHERAL INTERRUPT ENABLE REGISTER 2 |

|---------------|----------------------------------------------|

|               |                                              |

| R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | U-0 | U-0 | R/W-0/0               |

|---------|---------|---------|---------|---------|-----|-----|-----------------------|

| OSFIE   | C2IE    | C1IE    | EEIE    | BCL1IE  | —   | _   | CCP2IE <sup>(1)</sup> |

| bit 7   |         |         |         |         |     |     | bit 0                 |

| Legend:                                                                                                                           |             |                                       |                                                       |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------|-------------|---------------------------------------|-------------------------------------------------------|--|--|

| R = Readable                                                                                                                      | bit         | W = Writable bit                      | U = Unimplemented bit, read as '0'                    |  |  |

| u = Bit is unchanged x = Bit is                                                                                                   |             | x = Bit is unknown                    | -n/n = Value at POR and BOR/Value at all other Resets |  |  |

| '1' = Bit is set                                                                                                                  |             | '0' = Bit is cleared                  |                                                       |  |  |

| bit 7                                                                                                                             |             | lator Fail Interrupt Enable           |                                                       |  |  |

| <ul> <li>1 = Enables the Oscillator Fail interrupt</li> <li>0 = Disables the Oscillator Fail interrupt</li> </ul>                 |             |                                       |                                                       |  |  |

| bit 6                                                                                                                             | C2IE: Compa | rator C2 Interrupt Enable             | e bit                                                 |  |  |

| <ul> <li>1 = Enables the Comparator C2 interrupt</li> <li>0 = Disables the Comparator C2 interrupt</li> </ul>                     |             |                                       |                                                       |  |  |

| bit 5 C1IE: Comparator C1 Interrupt Enable bit                                                                                    |             |                                       |                                                       |  |  |

| <ul> <li>1 = Enables the Comparator C1 interrupt</li> <li>0 = Disables the Comparator C1 interrupt</li> </ul>                     |             |                                       |                                                       |  |  |

| bit 4                                                                                                                             | EEIE: EEPRO | OM Write Completion Inte              | errupt Enable bit                                     |  |  |

| <ul> <li>1 = Enables the EEPROM Write Completion interrupt</li> <li>0 = Disables the EEPROM Write Completion interrupt</li> </ul> |             |                                       |                                                       |  |  |

| bit 3                                                                                                                             | BCL1IE: MSS | SP1 Bus Collision Interrup            | pt Enable bit                                         |  |  |

| <ul> <li>1 = Enables the MSSP1 Bus Collision Interrupt</li> <li>0 = Disables the MSSP1 Bus Collision Interrupt</li> </ul>         |             |                                       |                                                       |  |  |

| bit 2-1                                                                                                                           | Unimplemen  | ted: Read as '0'                      |                                                       |  |  |

| bit 0                                                                                                                             | CCP2IE: CCF | P2 Interrupt Enable bit               |                                                       |  |  |

|                                                                                                                                   |             | the CCP2 interrupt the CCP2 interrupt |                                                       |  |  |

Note 1: PIC16(L)F1827 only.

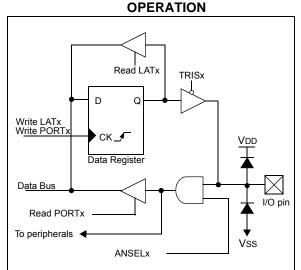

# 12.0 I/O PORTS

Depending on the device selected and peripherals enabled, there are two ports available. In general, when a peripheral is enabled, that pin may not be used as a general purpose I/O pin.

Each port has three registers for its operation. These registers are:

- TRISx registers (data direction register)

- PORTx registers (reads the levels on the pins of the device)

- LATx registers (output latch)

Some ports may have one or more of the following additional registers. These registers are:

- ANSELx (analog select)

- WPUx (weak pull-up)

# TABLE 12-1:PORT AVAILABILITY PER<br/>DEVICE

| Device        | PORTA | РОКТВ | PORTC |

|---------------|-------|-------|-------|

| PIC16(L)F1826 | •     | ٠     |       |

| PIC16(L)F1827 | •     | •     | •     |

The Data Latch (LATx registers) is useful for read-modify-write operations on the value that the I/O pins are driving.

A write operation to the LATx register has the same effect as a write to the corresponding PORTx register. A read of the LATx register reads of the values held in the I/O PORT latches, while a read of the PORTx register reads the actual I/O pin value.

Ports with analog functions also have an ANSELx register which can disable the digital input and save power. A simplified model of a generic I/O port, without the interfaces to other peripherals, is shown in Figure 12-1.

# FIGURE 12-1: GENERIC I/O PORT

#### EXAMPLE 12-1: INITIALIZING PORTA

- ; initializing the PORTA register. The

- ; other ports are initialized in the same

- ; manner.

| BANKSEL | PORTA       | ;                      |

|---------|-------------|------------------------|

| CLRF    | PORTA       | ;Init PORTA            |

| BANKSEL | LATA        | ;Data Latch            |

| CLRF    | LATA        | ;                      |

| BANKSEL | ANSELA      | ;                      |

| CLRF    | ANSELA      | ;digital I/O           |

| BANKSEL | TRISA       | ;                      |

| MOVLW   | B'00111000' | ;Set RA<5:3> as inputs |

| MOVWF   | TRISA       | ;and set RA<2:0> as    |

|         |             | ;outputs               |

|         |             |                        |

| R/W-1/1                        | R/W-1/1 | R/W-1/1      | R/W-1/1 | R/W-1/1      | R/W-1/1          | R/W-1/1 | R/W-1/1 |

|--------------------------------|---------|--------------|---------|--------------|------------------|---------|---------|

| WPUB7                          | WPUB6   | WPUB5        | WPUB4   | WPUB3        | WPUB2            | WPUB1   | WPUB0   |

| bit 7                          |         |              |         |              |                  |         | bit 0   |

|                                |         |              |         |              |                  |         |         |

|                                |         |              |         |              |                  |         |         |

| Legend:                        |         |              |         |              |                  |         |         |

| <b>Legend:</b><br>R = Readable | bit     | W = Writable | bit     | U = Unimplen | nented bit, read | as '0'  |         |

#### REGISTER 12-11: WPUB: WEAK PULL-UP PORTB REGISTER

bit 7-0 WPUB<7:0>: Weak Pull-up Register bits

1 = Pull-up enabled

'1' = Bit is set

0 = Pull-up disabled

Note 1: Global WPUEN bit of the OPTION register must be cleared for individual pull-ups to be enabled.

2: The weak pull-up device is automatically disabled if the pin is in configured as an output.

#### REGISTER 12-12: ANSELB: PORTB ANALOG SELECT REGISTER

'0' = Bit is cleared

| R/W-1/1 | U-0   |

|---------|---------|---------|---------|---------|---------|---------|-------|

| ANSB7   | ANSB6   | ANSB5   | ANSB4   | ANSB3   | ANSB2   | ANSB1   | —     |

| bit 7   |         |         |         |         |         |         | bit 0 |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-1 **ANSB<7:1>**: Analog Select between Analog or Digital Function on Pins RB<7:1>, respectively 0 = Digital I/O. Pin is assigned to port or digital special function.

1 = Analog input. Pin is assigned as analog input<sup>(1)</sup>. Digital input buffer disabled.

#### bit 0 Unimplemented: Read as '0'

**Note 1:** When setting a pin to an analog input, the corresponding TRIS bit must be set to Input mode in order to allow external control of the voltage on the pin.

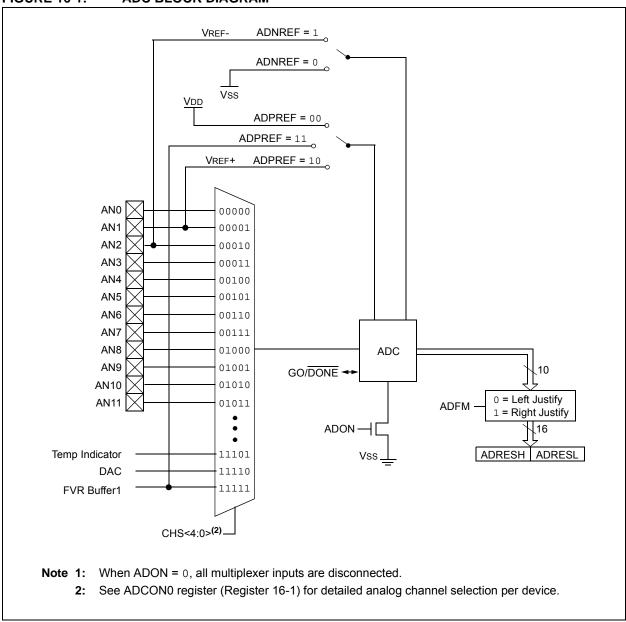

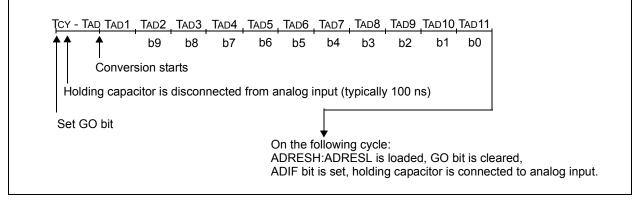

# 16.0 ANALOG-TO-DIGITAL CONVERTER (ADC) MODULE

The Analog-to-Digital Converter (ADC) allows conversion of an analog input signal to a 10-bit binary representation of that signal. This device uses analog inputs, which are multiplexed into a single sample and hold circuit. The output of the sample and hold is connected to the input of the converter. The converter generates a 10-bit binary result via successive approximation and stores the conversion result into the ADC result registers (ADRESH:ADRESL register pair). Figure 16-1 shows the block diagram of the ADC.

The ADC voltage reference is software selectable to be either internally generated or externally supplied.

# FIGURE 16-1: ADC BLOCK DIAGRAM

The ADC can generate an interrupt upon completion of a conversion. This interrupt can be used to wake-up the device from Sleep.

#### TABLE 16-1: ADC CLOCK PERIOD (TAD) Vs. DEVICE OPERATING FREQUENCIES

| ADC Clock Period (TAD) |           | Device Frequency (Fosc)     |                             |                             |                             |                             |                               |

|------------------------|-----------|-----------------------------|-----------------------------|-----------------------------|-----------------------------|-----------------------------|-------------------------------|

| ADC<br>Clock Source    | ADCS<2:0> | 32 MHz                      | 20 MHz                      | 16 MHz                      | 8 MHz                       | 4 MHz                       | 1 MHz                         |

| Fosc/2                 | 000       | 62.5ns <sup>(2)</sup>       | 100 ns <sup>(2)</sup>       | 125 ns <sup>(2)</sup>       | 250 ns <sup>(2)</sup>       | 500 ns <sup>(2)</sup>       | 2.0 μs                        |

| Fosc/4                 | 100       | 125 ns <sup>(2)</sup>       | 200 ns <sup>(2)</sup>       | 250 ns <sup>(2)</sup>       | 500 ns <sup>(2)</sup>       | 1.0 μs                      | 4.0 μs                        |

| Fosc/8                 | 001       | 0.5 μs <sup>(2)</sup>       | 400 ns <sup>(2)</sup>       | 0.5 μs <sup>(2)</sup>       | 1.0 μs                      | 2.0 μs                      | 8.0 μs <sup>(3)</sup>         |

| Fosc/16                | 101       | 800 ns                      | 800 ns                      | 1.0 μs                      | 2.0 μs                      | 4.0 μs                      | 16.0 μs <b><sup>(3)</sup></b> |

| Fosc/32                | 010       | 1.0 μs                      | 1.6 μs                      | 2.0 μs                      | 4.0 μs                      | 8.0 μs <sup>(3)</sup>       | 32.0 μs <sup>(3)</sup>        |

| Fosc/64                | 110       | 2.0 μs                      | 3.2 μs                      | 4.0 μs                      | 8.0 μs <sup>(3)</sup>       | 16.0 μs <sup>(3)</sup>      | 64.0 μs <sup>(3)</sup>        |

| FRC                    | x11       | 1.0-6.0 μs <sup>(1,4)</sup>   |

Legend: Shaded cells are outside of recommended range.

**Note 1:** The FRC source has a typical TAD time of 1.6  $\mu$ s for VDD.

2: These values violate the minimum required TAD time.

3: For faster conversion times, the selection of another clock source is recommended.

4: The ADC clock period (TAD) and total ADC conversion time can be minimized when the ADC clock is derived from the system clock FOSC. However, the FRC clock source must be used when conversions are to be performed with the device in Sleep mode.

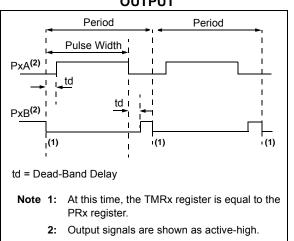

#### 24.4.5 PROGRAMMABLE DEAD-BAND DELAY MODE

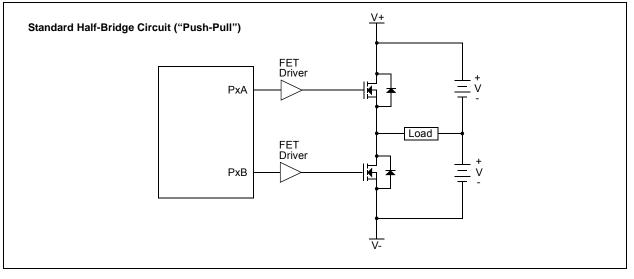

In Half-Bridge applications where all power switches are modulated at the PWM frequency, the power switches normally require more time to turn off than to turn on. If both the upper and lower power switches are switched at the same time (one turned on, and the other turned off), both switches may be on for a short period of time until one switch completely turns off. During this brief interval, a very high current (*shoot-through current*) will flow through both power switches, shorting the bridge supply. To avoid this potentially destructive shoot-through current from flowing during switching, turning on either of the power switches is normally delayed to allow the other switch to completely turn off.

In Half-Bridge mode, a digitally programmable dead-band delay is available to avoid shoot-through current from destroying the bridge power switches. The delay occurs at the signal transition from the non-active state to the active state. See Figure 24-16 for illustration. The lower seven bits of the associated PWMxCON register (Register 24-4) sets the delay period in terms of microcontroller instruction cycles (TcY or 4 Tosc).

#### FIGURE 24-16: EXAMPLE OF HALF-BRIDGE PWM OUTPUT

#### FIGURE 24-17: EXAMPLE OF HALF-BRIDGE APPLICATIONS

### 24.4.6.1 Steering Synchronization

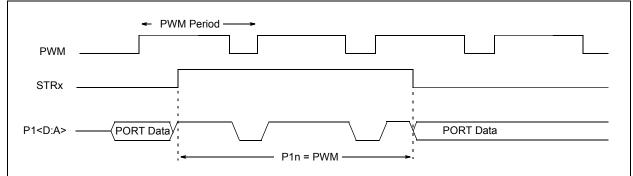

The STRxSYNC bit of the PSTRxCON register gives the user two selections of when the steering event will happen. When the STRxSYNC bit is '0', the steering event will happen at the end of the instruction that writes to the PSTRxCON register. In this case, the output signal at the Px<D:A> pins may be an incomplete PWM waveform. This operation is useful when the user firmware needs to immediately remove a PWM signal from the pin.

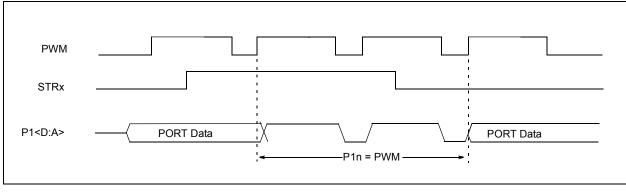

When the STRxSYNC bit is '1', the effective steering update will happen at the beginning of the next PWM period. In this case, steering on/off the PWM output will always produce a complete PWM waveform.

Figures 24-19 and 24-20 illustrate the timing diagrams of the PWM steering depending on the STRxSYNC setting.

#### 24.4.7 START-UP CONSIDERATIONS

When any PWM mode is used, the application hardware must use the proper external pull-up and/or pull-down resistors on the PWM output pins.

The CCPxM<1:0> bits of the CCPxCON register allow the user to choose whether the PWM output signals are active-high or active-low for each pair of PWM output pins (PxA/PxC and PxB/PxD). The PWM output polarities must be selected before the PWM pin output drivers are enabled. Changing the polarity configuration while the PWM pin output drivers are enable is not recommended since it may result in damage to the application circuits.

The PxA, PxB, PxC and PxD output latches may not be in the proper states when the PWM module is initialized. Enabling the PWM pin output drivers at the same time as the Enhanced PWM modes may cause damage to the application circuit. The Enhanced PWM modes must be enabled in the proper Output mode and complete a full PWM cycle before enabling the PWM pin output drivers. The completion of a full PWM cycle is indicated by the TMRxIF bit of the PIRx register being set as the second PWM period begins.

Note: When the microcontroller is released from Reset, all of the I/O pins are in the high-impedance state. The external circuits must keep the power switch devices in the Off state until the microcontroller drives the I/O pins with the proper signal levels or activates the PWM output(s).

# 24.4.8 ALTERNATE PIN LOCATIONS

This module incorporates I/O pins that can be moved to other locations with the use of the alternate pin function registers, APFCON0 and APFCON1. To determine which pins can be moved and what their default locations are upon a reset, see **Section 12.1 "Alternate Pin Function"** for more information.

#### FIGURE 24-19: EXAMPLE OF STEERING EVENT AT END OF INSTRUCTION (STRxSYNC = 0)

# FIGURE 24-20: EXAMPLE OF STEERING EVENT AT BEGINNING OF INSTRUCTION (STRxSYNC = 1)

The  $\mathsf{I}^2\mathsf{C}$  interface supports the following modes and features:

- Master mode

- Slave mode

- Byte NACKing (Slave mode)

- Limited Multi-master support

- 7-bit and 10-bit addressing

- Start and Stop interrupts

- Interrupt masking

- Clock stretching

- · Bus collision detection

- · General call address matching

- Address masking

- Address Hold and Data Hold modes

- Selectable SDAx hold times

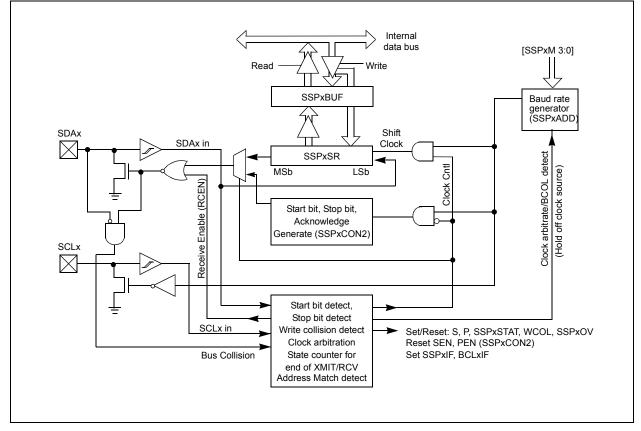

Figure 25-2 is a block diagram of the  $I^2C$  interface module in Master mode. Figure 25-3 is a diagram of the  $I^2C$  interface module in Slave mode.

The PIC16F1827 has two MSSP modules, MSSP1 and MSSP2, each module operating independently from the other.

- Note 1: In devices with more than one MSSP module, it is very important to pay close attention to SSPxCONx register names. SSP1CON1 and SSP1CON2 registers control different operational aspects of the same module, while SSP1CON1 and SSP2CON1 control the same features for two different modules.

- 2: Throughout this section, generic references to an MSSP module in any of its operating modes may be interpreted as being equally applicable to MSSP1 or MSSP2. Register names, module I/O signals, and bit names may use the generic designator 'x' to indicate the use of a numeral to distinguish a particular module when required.

# FIGURE 25-2: MSSPX BLOCK DIAGRAM (I<sup>2</sup>C<sup>™</sup> MASTER MODE)

# 25.6.7 I<sup>2</sup>C MASTER MODE RECEPTION

Master mode reception is enabled by programming the Receive Enable bit, RCEN bit of the SSPxCON2 register.

| Note: | The MSSPx module must be in an Idle     |

|-------|-----------------------------------------|

|       | state before the RCEN bit is set or the |

|       | RCEN bit will be disregarded.           |

The Baud Rate Generator begins counting and on each rollover, the state of the SCLx pin changes (high-to-low/low-to-high) and data is shifted into the SSPxSR. After the falling edge of the eighth clock, the receive enable flag is automatically cleared, the contents of the SSPxSR are loaded into the SSPxBUF, the BF flag bit is set, the SSPxIF flag bit is set and the Baud Rate Generator is suspended from counting, holding SCLx low. The MSSPx is now in Idle state awaiting the next command. When the buffer is read by the CPU, the BF flag bit is automatically cleared. The user can then send an Acknowledge bit at the end of reception by setting the Acknowledge Sequence Enable, ACKEN bit of the SSPxCON2 register.

#### 25.6.7.1 BF Status Flag

In receive operation, the BF bit is set when an address or data byte is loaded into SSPxBUF from SSPxSR. It is cleared when the SSPxBUF register is read.

#### 25.6.7.2 SSPxOV Status Flag

In receive operation, the SSPxOV bit is set when 8 bits are received into the SSPxSR and the BF flag bit is already set from a previous reception.

#### 25.6.7.3 WCOL Status Flag

If the user writes the SSPxBUF when a receive is already in progress (i.e., SSPxSR is still shifting in a data byte), the WCOL bit is set and the contents of the buffer are unchanged (the write does not occur). 25.6.7.4 Typical Receive Sequence:

- 1. The user generates a Start condition by setting the SEN bit of the SSPxCON2 register.

- 2. SSPxIF is set by hardware on completion of the Start.

- 3. SSPxIF is cleared by software.

- 4. User writes SSPxBUF with the slave address to transmit and the R/W bit set.

- 5. Address is shifted out the SDAx pin until all 8 bits are transmitted. Transmission begins as soon as SSPxBUF is written to.

- The MSSPx module shifts in the ACK bit from the slave device and writes its value into the ACKSTAT bit of the SSPxCON2 register.

- The MSSPx module generates an interrupt at the end of the ninth clock cycle by setting the SSPxIF bit.

- 8. User sets the RCEN bit of the SSPxCON2 register and the Master clocks in a byte from the slave.

- 9. After the 8th falling edge of SCLx, SSPxIF and BF are set.

- 10. Master clears SSPxIF and reads the received byte from SSPxUF, clears BF.

- Master sets ACK value sent to slave in ACKDT bit of the SSPxCON2 register and initiates the ACK by setting the ACKEN bit.

- 12. Masters ACK is clocked out to the Slave and SSPxIF is set.

- 13. User clears SSPxIF.

- 14. Steps 8-13 are repeated for each received byte from the slave.

- 15. Master sends a not ACK or Stop to end communication.

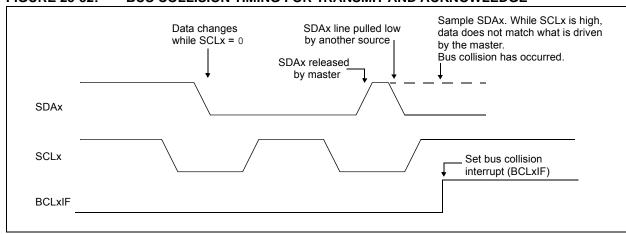

#### FIGURE 25-32: BUS COLLISION TIMING FOR TRANSMIT AND ACKNOWLEDGE

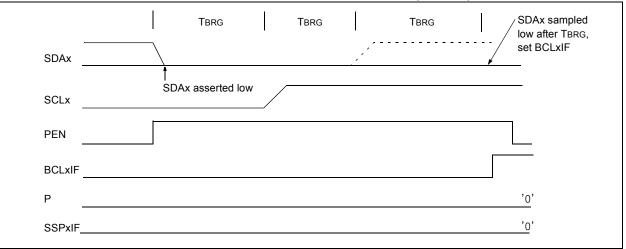

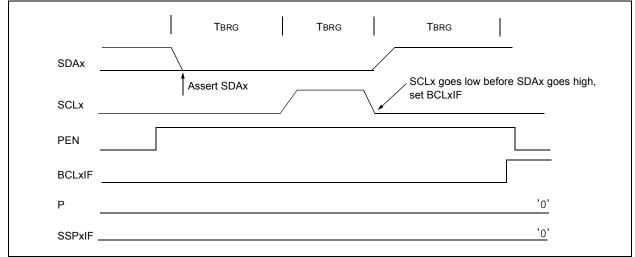

#### 25.6.13.3 Bus Collision During a Stop Condition

Bus collision occurs during a Stop condition if:

- a) After the SDAx pin has been deasserted and allowed to float high, SDAx is sampled low after the BRG has timed out.

- b) After the SCLx pin is deasserted, SCLx is sampled low before SDAx goes high.

The Stop condition begins with SDAx asserted low. When SDAx is sampled low, the SCLx pin is allowed to float. When the pin is sampled high (clock arbitration), the Baud Rate Generator is loaded with SSPxADD and counts down to 0. After the BRG times out, SDAx is sampled. If SDAx is sampled low, a bus collision has occurred. This is due to another master attempting to drive a data '0' (Figure 25-37). If the SCLx pin is sampled low before SDAx is allowed to float high, a bus collision occurs. This is another case of another master attempting to drive a data '0' (Figure 25-38).

#### FIGURE 25-38: BUS COLLISION DURING A STOP CONDITION (CASE 1)

#### FIGURE 25-39: BUS COLLISION DURING A STOP CONDITION (CASE 2)

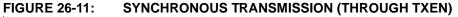

# 26.4 EUSART Synchronous Mode

Synchronous serial communications are typically used in systems with a single master and one or more slaves. The master device contains the necessary circuitry for baud rate generation and supplies the clock for all devices in the system. Slave devices can take advantage of the master clock by eliminating the internal clock generation circuitry.

There are two signal lines in Synchronous mode: a bidirectional data line and a clock line. Slaves use the external clock supplied by the master to shift the serial data into and out of their respective receive and transmit shift registers. Since the data line is bidirectional, synchronous operation is half-duplex only. Half-duplex refers to the fact that master and slave devices can receive and transmit data but not both simultaneously. The EUSART can operate as either a master or slave device.

Start and Stop bits are not used in synchronous transmissions.

#### 26.4.1 SYNCHRONOUS MASTER MODE

The following bits are used to configure the EUSART for Synchronous Master operation:

- SYNC = 1

- CSRC = 1

- SREN = 0 (for transmit); SREN = 1 (for receive)

- CREN = 0 (for transmit); CREN = 1 (for receive)

- SPEN = 1

Setting the SYNC bit of the TXSTA register configures the device for synchronous operation. Setting the CSRC bit of the TXSTA register configures the device as a master. Clearing the SREN and CREN bits of the RCSTA register ensures that the device is in the Transmit mode, otherwise the device will be configured to receive. Setting the SPEN bit of the RCSTA register enables the EUSART.

#### 26.4.1.1 Master Clock

Synchronous data transfers use a separate clock line, which is synchronous with the data. A device configured as a master transmits the clock on the TX/CK line. The TX/CK pin output driver is automatically enabled when the EUSART is configured for synchronous transmit or receive operation. Serial data bits change on the leading edge to ensure they are valid at the trailing edge of each clock. One clock cycle is generated for each data bit. Only as many clock cycles are generated as there are data bits.

#### 26.4.1.2 Clock Polarity

A clock polarity option is provided for Microwire compatibility. Clock polarity is selected with the SCKP bit of the BAUDCON register. Setting the SCKP bit sets the clock Idle state as high. When the SCKP bit is set, the data changes on the falling edge of each clock. Clearing the SCKP bit sets the Idle state as low. When the SCKP bit is cleared, the data changes on the rising edge of each clock.

#### 26.4.1.3 Synchronous Master Transmission

Data is transferred out of the device on the RX/DT pin. The RX/DT and TX/CK pin output drivers are automatically enabled when the EUSART is configured for synchronous master transmit operation.

A transmission is initiated by writing a character to the TXREG register. If the TSR still contains all or part of a previous character the new character data is held in the TXREG until the last bit of the previous character has been transmitted. If this is the first character, or the previous character has been completely flushed from the TSR, the data in the TXREG is immediately transferred to the TSR. The transmission of the character commences immediately following the transfer of the data to the TSR from the TXREG.

Each data bit changes on the leading edge of the master clock and remains valid until the subsequent leading clock edge.

| Note: | The TSR register is not mapped in data      |

|-------|---------------------------------------------|

|       | memory, so it is not available to the user. |

- 26.4.1.4 Synchronous Master Transmission Set-up:

- Initialize the SPBRGH, SPBRGL register pair and the BRGH and BRG16 bits to achieve the desired baud rate (see Section 26.3 "EUSART Baud Rate Generator (BRG)").

- 2. Enable the synchronous master serial port by setting bits SYNC, SPEN and CSRC.

- 3. Disable Receive mode by clearing bits SREN and CREN.

- 4. Enable Transmit mode by setting the TXEN bit.

- 5. If 9-bit transmission is desired, set the TX9 bit.

- 6. If interrupts are desired, set the TXIE bit of the PIE1 register and the GIE and PEIE bits of the INTCON register.

- 7. If 9-bit transmission is selected, the ninth bit should be loaded in the TX9D bit.

- 8. Start transmission by loading data to the TXREG register.

# 26.5 EUSART Operation During Sleep

The EUSART will remain active during Sleep only in the Synchronous Slave mode. All other modes require the system clock and therefore cannot generate the necessary signals to run the Transmit or Receive Shift registers during Sleep.

Synchronous Slave mode uses an externally generated clock to run the Transmit and Receive Shift registers.

#### 26.5.1 SYNCHRONOUS RECEIVE DURING SLEEP

To receive during Sleep, all the following conditions must be met before entering Sleep mode:

- RCSTA and TXSTA Control registers must be configured for Synchronous Slave Reception (see Section 26.4.2.4 "Synchronous Slave Reception Set-up:").

- If interrupts are desired, set the RCIE bit of the PIE1 register and the GIE and PEIE bits of the INTCON register.

- The RCIF interrupt flag must be cleared by reading RCREG to unload any pending characters in the receive buffer.

Upon entering Sleep mode, the device will be ready to accept data and clocks on the RX/DT and TX/CK pins, respectively. When the data word has been completely clocked in by the external device, the RCIF interrupt flag bit of the PIR1 register will be set. Thereby, waking the processor from Sleep.

Upon waking from Sleep, the instruction following the SLEEP instruction will be executed. If the GIE global interrupt enable bit of the INTCON register is also set, then the Interrupt Service Routine at address 004h will be called.

#### 26.5.2 SYNCHRONOUS TRANSMIT DURING SLEEP

To transmit during Sleep, all the following conditions must be met before entering Sleep mode:

- RCSTA and TXSTA Control registers must be configured for Synchronous Slave Transmission (see Section 26.4.2.2 "Synchronous Slave Transmission Set-up:").

- The TXIF interrupt flag must be cleared by writing the output data to the TXREG, thereby filling the TSR and transmit buffer.

- If interrupts are desired, set the TXIE bit of the PIE1 register and the PEIE bit of the INTCON register.

- Interrupt enable bits TXIE of the PIE1 register and PEIE of the INTCON register must set.

Upon entering Sleep mode, the device will be ready to accept clocks on TX/CK pin and transmit data on the RX/DT pin. When the data word in the TSR has been completely clocked out by the external device, the pending byte in the TXREG will transfer to the TSR and the TXIF flag will be set. Thereby, waking the processor from Sleep. At this point, the TXREG is available to accept another character for transmission, which will clear the TXIF flag.

Upon waking from Sleep, the instruction following the SLEEP instruction will be executed. If the Global Interrupt Enable (GIE) bit is also set then the Interrupt Service Routine at address 0004h will be called.

#### 26.5.3 ALTERNATE PIN LOCATIONS

This module incorporates I/O pins that can be moved to other locations with the use of the alternate pin function registers, APFCON0 and APFCON1. To determine which pins can be moved and what their default locations are upon a reset, see **Section 12.1 "Alternate Pin Function"** for more information.

# PIC16(L)F1826/27

# FIGURE 29-1: GENERAL FORMAT FOR INSTRUCTIONS

| Byte-oriented file register operations                                                |

|---------------------------------------------------------------------------------------|

| OPCODE d f (FILE #)                                                                   |

| d = 0 for destination W<br>d = 1 for destination f<br>f = 7-bit file register address |

| Bit-oriented file register operations<br>13 10 9 7 6 0                                |

| OPCODE b (BIT #) f (FILE #)                                                           |

| b = 3-bit bit address<br>f = 7-bit file register address                              |

| Literal and control operations                                                        |

| General                                                                               |

| 13 8 7 0<br>OPCODE k (literal)                                                        |

|                                                                                       |

| k = 8-bit immediate value                                                             |

| CALL and GOTO instructions only                                                       |

| 13 11 10 0                                                                            |

| OPCODE k (literal)                                                                    |

| k = 11-bit immediate value                                                            |

| MOVLP instruction only                                                                |

| 13 7 6 0                                                                              |

| OPCODE k (literal)                                                                    |

| k = 7-bit immediate value                                                             |

| MOVLB instruction only                                                                |

| 13 5 4 0                                                                              |

| OPCODE k (literal)                                                                    |

| k = 5-bit immediate value                                                             |

| BRA instruction only                                                                  |

| 13 9 8 0<br>OPCODE k (literal)                                                        |

|                                                                                       |

| k = 9-bit immediate value                                                             |

| FSR Offset instructions                                                               |

| 13 7 6 5 0<br>OPCODE n k (literal)                                                    |

|                                                                                       |

| n = appropriate FSR<br>k = 6-bit immediate value                                      |

| FSR Increment instructions                                                            |

| 13 3 2 1 0<br>OPCODE n m (mode)                                                       |

| n = appropriate FSR<br>m = 2-bit mode value                                           |

| OPCODE only                                                                           |

| 13 0<br>OPCODE                                                                        |

| UFCODE                                                                                |

| RRF              | Rotate Right f through Carry                                                                                                                                                                                       |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] RRF f,d                                                                                                                                                                                           |

| Operands:        | $\begin{array}{l} 0\leq f\leq 127\\ d\in [0,1] \end{array}$                                                                                                                                                        |

| Operation:       | See description below                                                                                                                                                                                              |

| Status Affected: | С                                                                                                                                                                                                                  |

| Description:     | The contents of register 'f' are rotated<br>one bit to the right through the Carry<br>flag. If 'd' is '0', the result is placed in<br>the W register. If 'd' is '1', the result is<br>placed back in register 'f'. |

|                  | C Register f                                                                                                                                                                                                       |

| SUBLW            | Subtract V                                                                                                                              | V from literal  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------|-----------------|

| Syntax:          | [label] SI                                                                                                                              | JBLW k          |

| Operands:        | $0 \leq k \leq 255$                                                                                                                     |                 |

| Operation:       | $k - (W) \to (W$                                                                                                                        | V)              |

| Status Affected: | C, DC, Z                                                                                                                                |                 |

| Description:     | The W register is subtracted (2's com-<br>plement method) from the eight-bit<br>literal 'k'. The result is placed in the W<br>register. |                 |

|                  | <b>C</b> = 0                                                                                                                            | W > k           |

|                  | <b>C =</b> 1                                                                                                                            | $W \le k$       |

|                  | DC = 0                                                                                                                                  | W<3:0> > k<3:0> |

DC = 1

$W<3:0> \le k<3:0>$

$W<3:0> \le f<3:0>$

| SLEEP            | Enter Sleep mode                                                                                                                                                                                                                     |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] SLEEP                                                                                                                                                                                                                        |

| Operands:        | None                                                                                                                                                                                                                                 |

| Operation:       | $\begin{array}{l} \text{O0h} \rightarrow \text{WDT}, \\ 0 \rightarrow \text{WDT prescaler}, \\ 1 \rightarrow \overline{\text{TO}}, \\ 0 \rightarrow \overline{\text{PD}} \end{array}$                                                |

| Status Affected: | TO, PD                                                                                                                                                                                                                               |

| Description:     | The power-down Status bit, $\overline{\text{PD}}$ is cleared. Time-out Status bit, $\overline{\text{TO}}$ is set. Watchdog Timer and its prescaler are cleared.<br>The processor is put into Sleep mode with the oscillator stopped. |

| SUBWF            | Subtract W                                                                                                                                                                                 | / from f        |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

| Syntax:          | [label] SL                                                                                                                                                                                 | JBWF f,d        |

| Operands:        | $\begin{array}{l} 0\leq f\leq 127\\ d\in [0,1] \end{array}$                                                                                                                                |                 |

| Operation:       | (f) - $(W)$ → $(d)$                                                                                                                                                                        | lestination)    |

| Status Affected: | C, DC, Z                                                                                                                                                                                   |                 |

| Description:     | Subtract (2's complement method) W<br>register from register 'f'. If 'd' is '0', the<br>result is stored in the W<br>register. If 'd' is '1', the result is stored<br>back in register 'f. |                 |

|                  | <b>C =</b> 0                                                                                                                                                                               | W > f           |

|                  | C = 1                                                                                                                                                                                      | $W \leq f$      |

|                  | DC = 0                                                                                                                                                                                     | W<3:0> > f<3:0> |

| SUBWFB           | Subtract W from f with Borrow                                                                                                                                                                       |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | SUBWFB f {,d}                                                                                                                                                                                       |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                                                   |

| Operation:       | $(f) - (W) - (\overline{B}) \rightarrow dest$                                                                                                                                                       |

| Status Affected: | C, DC, Z                                                                                                                                                                                            |

| Description:     | Subtract W and the BORROW flag<br>(CARRY) from register 'f' (2's comple-<br>ment method). If 'd' is '0', the result is<br>stored in W. If 'd' is '1', the result is<br>stored back in register 'f'. |

DC = 1

# 33.0 PACKAGING INFORMATION

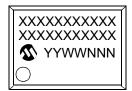

# 33.1 Package Marking Information

#### 18-Lead PDIP

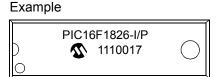

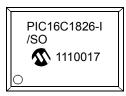

#### 18-Lead SOIC (.300")

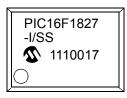

#### 20-Lead SSOP

#### 28-Lead QFN/UQFN

# Example

# Example

#### Example

| Legend | : XXX<br>Y<br>YY<br>WW<br>NNN<br>@3<br>* | Customer-specific information<br>Year code (last digit of calendar year)<br>Year code (last 2 digits of calendar year)<br>Week code (week of January 1 is week '01')<br>Alphanumeric traceability code<br>Pb-free JEDEC designator for Matte Tin (Sn)<br>This package is Pb-free. The Pb-free JEDEC designator ((e3))<br>can be found on the outer packaging for this package. |

|--------|------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Note:  | be carried                               | nt the full Microchip part number cannot be marked on one line, it will<br>d over to the next line, thus limiting the number of available<br>s for customer-specific information.                                                                                                                                                                                              |

\* Standard PICmicro<sup>®</sup> device marking consists of Microchip part number, year code, week code and traceability code. For PICmicro device marking beyond this, certain price adders apply. Please check with your Microchip Sales Office. For QTP devices, any special marking adders are included in QTP price.

# **Worldwide Sales and Service**

#### AMERICAS

Corporate Office 2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200 Fax: 480-792-7277 Technical Support: http://www.microchip.com/ support Web Address: www.microchip.com

Atlanta Duluth, GA Tel: 678-957-9614 Fax: 678-957-1455

Boston Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

Chicago Itasca, IL Tel: 630-285-0071 Fax: 630-285-0075

**Cleveland** Independence, OH Tel: 216-447-0464 Fax: 216-447-0643

**Dallas** Addison, TX Tel: 972-818-7423 Fax: 972-818-2924

Detroit Farmington Hills, MI Tel: 248-538-2250 Fax: 248-538-2260

Indianapolis Noblesville, IN Tel: 317-773-8323 Fax: 317-773-5453

Los Angeles Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608

Santa Clara Santa Clara, CA Tel: 408-961-6444 Fax: 408-961-6445

Toronto Mississauga, Ontario, Canada Tel: 905-673-0699 Fax: 905-673-6509

#### ASIA/PACIFIC

Asia Pacific Office Suites 3707-14, 37th Floor Tower 6, The Gateway Harbour City, Kowloon Hong Kong Tel: 852-2401-1200 Fax: 852-2401-3431 Australia - Sygney

Tel: 61-2-9868-6733 Fax: 61-2-9868-6755

**China - Beijing** Tel: 86-10-8528-2100 Fax: 86-10-8528-2104

**China - Chengdu** Tel: 86-28-8665-5511 Fax: 86-28-8665-7889

**China - Chongqing** Tel: 86-23-8980-9588 Fax: 86-23-8980-9500

**China - Hong Kong SAR** Tel: 852-2401-1200 Fax: 852-2401-3431

**China - Nanjing** Tel: 86-25-8473-2460

Fax: 86-25-8473-2470 China - Qingdao Tel: 86-532-8502-7355 Fax: 86-532-8502-7205

**China - Shanghai** Tel: 86-21-5407-5533 Fax: 86-21-5407-5066

China - Shenyang Tel: 86-24-2334-2829 Fax: 86-24-2334-2393

**China - Shenzhen** Tel: 86-755-8203-2660 Fax: 86-755-8203-1760

**China - Wuhan** Tel: 86-27-5980-5300 Fax: 86-27-5980-5118

**China - Xian** Tel: 86-29-8833-7252 Fax: 86-29-8833-7256

**China - Xiamen** Tel: 86-592-2388138 Fax: 86-592-2388130

**China - Zhuhai** Tel: 86-756-3210040 Fax: 86-756-3210049

# ASIA/PACIFIC

India - Bangalore Tel: 91-80-3090-4444 Fax: 91-80-3090-4123

India - New Delhi Tel: 91-11-4160-8631 Fax: 91-11-4160-8632

India - Pune Tel: 91-20-2566-1512 Fax: 91-20-2566-1513

**Japan - Yokohama** Tel: 81-45-471- 6166 Fax: 81-45-471-6122

**Korea - Daegu** Tel: 82-53-744-4301 Fax: 82-53-744-4302

Korea - Seoul Tel: 82-2-554-7200 Fax: 82-2-558-5932 or 82-2-558-5934

Malaysia - Kuala Lumpur Tel: 60-3-6201-9857 Fax: 60-3-6201-9859

**Malaysia - Penang** Tel: 60-4-227-8870 Fax: 60-4-227-4068

Philippines - Manila Tel: 63-2-634-9065 Fax: 63-2-634-9069

Singapore Tel: 65-6334-8870 Fax: 65-6334-8850

**Taiwan - Hsin Chu** Tel: 886-3-6578-300 Fax: 886-3-6578-370

**Taiwan - Kaohsiung** Tel: 886-7-213-7830 Fax: 886-7-330-9305

Taiwan - Taipei Tel: 886-2-2500-6610 Fax: 886-2-2508-0102

**Thailand - Bangkok** Tel: 66-2-694-1351 Fax: 66-2-694-1350

#### EUROPE

Austria - Wels Tel: 43-7242-2244-39 Fax: 43-7242-2244-393 Denmark - Copenhagen Tel: 45-4450-2828 Fax: 45-4485-2829

France - Paris Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79

**Germany - Munich** Tel: 49-89-627-144-0 Fax: 49-89-627-144-44

Italy - Milan Tel: 39-0331-742611 Fax: 39-0331-466781

Netherlands - Drunen Tel: 31-416-690399 Fax: 31-416-690340

**Spain - Madrid** Tel: 34-91-708-08-90 Fax: 34-91-708-08-91

**UK - Wokingham** Tel: 44-118-921-5869 Fax: 44-118-921-5820

02/18/11