Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 16                                                                         |

| Program Memory Size        | 3.5KB (2K x 14)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 256 x 8                                                                    |

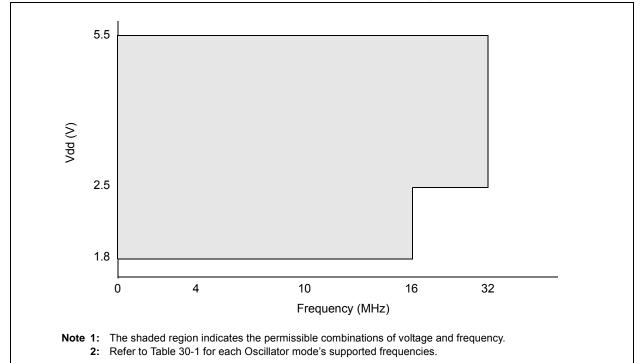

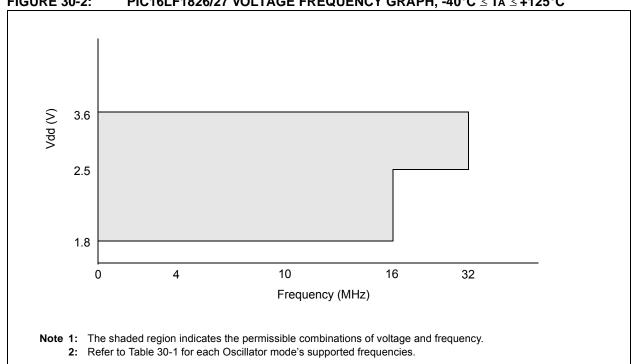

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                                |

| Data Converters            | A/D 12x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

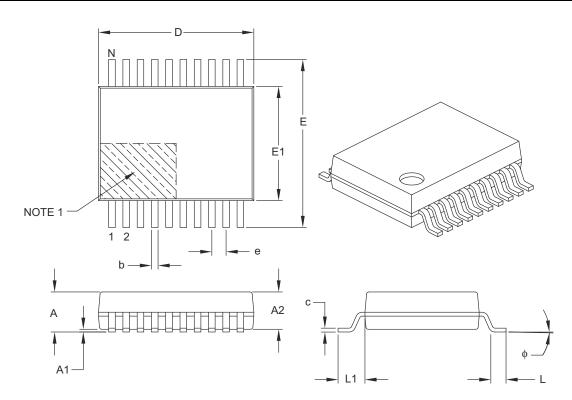

| Package / Case             | 28-UFQFN Exposed Pad                                                       |

| Supplier Device Package    | 28-UQFN (4x4)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f1826t-i-mv |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### TABLE 3-3: PIC16(L)F1826/27 MEMORY MAP

|      | BANK 0                        | 010( | BANK 1                         |      | BANK 2                         |      | BANK 3                         |      | BANK 4                              |      | BANK 5                        |      | BANK 6                        |      | BANK 7                        |

|------|-------------------------------|------|--------------------------------|------|--------------------------------|------|--------------------------------|------|-------------------------------------|------|-------------------------------|------|-------------------------------|------|-------------------------------|

| 000h |                               | 080h |                                | 100h |                                | 180h |                                | 200h |                                     | 280h |                               | 300h |                               | 380h |                               |

|      | Core Registers<br>(Table 3-2) |      | Core Registers<br>(Table 3-2)  |      | Core Registers<br>(Table 3-2)  |      | Core Registers<br>(Table 3-2)  |      | Core Registers<br>(Table 3-2)       |      | Core Registers<br>(Table 3-2) |      | Core Registers<br>(Table 3-2) |      | Core Registers<br>(Table 3-2) |

| 00Bh |                               | 08Bh |                                | 10Bh |                                | 18Bh |                                | 20Bh |                                     | 28Bh |                               | 30Bh |                               | 38Bh |                               |

| 00Ch | PORTA                         | 08Ch | TRISA                          | 10Ch | LATA                           | 18Ch | ANSELA                         | 20Ch | WPUA                                | 28Ch | _                             | 30Ch | _                             | 38Ch | _                             |

| 00Dh | PORTB                         | 08Dh | TRISB                          | 10Dh | LATB                           | 18Dh | ANSELB                         | 20Dh | WPUB                                | 28Dh | —                             | 30Dh | —                             | 38Dh | —                             |

| 00Eh | —                             | 08Eh | —                              | 10Eh | —                              | 18Eh | —                              | 20Eh | —                                   | 28Eh | —                             | 30Eh | —                             | 38Eh | —                             |

| 00Fh | _                             | 08Fh | —                              | 10Fh | _                              | 18Fh | _                              | 20Fh | _                                   | 28Fh | _                             | 30Fh | —                             | 38Fh | _                             |

| 010h | _                             | 090h | —                              | 110h | —                              | 190h | —                              | 210h | —                                   | 290h | —                             | 310h | —                             | 390h | —                             |

| 011h | PIR1                          | 091h | PIE1                           | 111h | CM1CON0                        | 191h | EEADRL                         | 211h | SSP1BUF                             | 291h | CCPR1L                        | 311h | CCPR3L <sup>(1)</sup>         | 391h | _                             |

| 012h | PIR2                          | 092h | PIE2                           | 112h | CM1CON1                        | 192h | EEADRH                         | 212h | SSP1ADD                             | 292h | CCPR1H                        | 312h | CCPR3H <sup>(1)</sup>         | 392h | —                             |

| 013h | PIR3 <sup>(1)</sup>           | 093h | PIE3 <sup>(1)</sup>            | 113h | CM2CON0                        | 193h | EEDATL                         | 213h | SSP1MASK                            | 293h | CCP1CON                       | 313h | CCP3CON <sup>(1)</sup>        | 393h | —                             |

| 014h | PIR4 <sup>(1)</sup>           | 094h | PIE4 <sup>(1)</sup>            | 114h | CM2CON1                        | 194h | EEDATH                         | 214h | SSP1STAT                            | 294h | PWM1CON                       | 314h | —                             | 394h | IOCBP                         |

| 015h | TMR0                          | 095h | OPTION                         | 115h | CMOUT                          | 195h | EECON1                         | 215h | SSP1CON                             | 295h | CCP1AS                        | 315h | —                             | 395h | IOCBN                         |

| 016h | TMR1L                         | 096h | PCON                           | 116h | BORCON                         | 196h | EECON2                         | 216h | SSP1CON2                            | 296h | PSTR1CON                      | 316h | —                             | 396h | IOCBF                         |

| 017h | TMR1H                         | 097h | WDTCON                         | 117h | FVRCON                         | 197h | —                              | 217h | SSP1CON3                            | 297h | —                             | 317h | —                             | 397h | —                             |

| 018h | T1CON                         | 098h | OSCTUNE                        | 118h | DACCON0                        | 198h | _                              | 218h |                                     | 298h | CCPR2L <sup>(1)</sup>         | 318h | CCPR4L <sup>(1)</sup>         | 398h | —                             |

| 019h | T1GCON                        | 099h | OSCCON                         | 119h | DACCON1                        | 199h | RCREG                          | 219h | SSP2BUF <sup>(1)</sup>              | 299h | CCPR2H <sup>(1)</sup>         | 319h | CCPR4H <sup>(1)</sup>         | 399h | —                             |

| 01Ah | TMR2                          | 09Ah | OSCSTAT                        | 11Ah | SRCON0                         | 19Ah | TXREG                          | 21Ah | SSP2ADD <sup>(1)</sup>              | 29Ah | CCP2CON <sup>(1)</sup>        | 31Ah | CCP4CON <sup>(1)</sup>        | 39Ah | CLKRCON                       |

| 01Bh | PR2                           | 09Bh | ADRESL                         | 11Bh | SRCON1                         | 19Bh | SPBRGL                         | 21Bh | SSP2MASK <sup>(1)</sup>             | 29Bh | PWM2CON <sup>(1)</sup>        | 31Bh | —                             | 39Bh | _                             |

| 01Ch | T2CON                         | 09Ch | ADRESH                         | 11Ch | —                              | 19Ch | SPBRGH                         | 21Ch | SSP2STAT <sup>(1)</sup>             | 29Ch | CCP2AS <sup>(1)</sup>         | 31Ch | —                             | 39Ch | MDCON                         |

| 01Dh | —                             | 09Dh | ADCON0                         | 11Dh | APFCON0                        | 19Dh | RCSTA                          | 21Dh | SSP2CON <sup>(1)</sup>              | 29Dh | PSTR2CON <sup>(1)</sup>       | 31Dh | —                             | 39Dh | MDSRC                         |

| 01Eh | CPSCON0                       | 09Eh | ADCON1                         | 11Eh | APFCON1                        | 19Eh | TXSTA                          | 21Eh | SSP2CON2 <sup>(1)</sup>             | 29Eh | CCPTMRS <sup>(1)</sup>        | 31Eh | —                             | 39Eh | MDCARL                        |

| 01Fh | CPSCON1                       | 09Fh | —                              | 11Fh | _                              | 19Fh | BAUDCON                        | 21Fh | SSP2CON3 <sup>(1)</sup>             | 29Fh | _                             | 31Fh | —                             | 39Fh | MDCARH                        |

| 020h |                               | 0A0h |                                | 120h |                                | 1A0h |                                | 220h | General<br>Purpose                  | 2A0h |                               | 320h |                               | 3A0h |                               |

|      | General                       |      | General<br>Purpose<br>Register |      | General<br>Purpose<br>Register |      | General<br>Purpose<br>Register |      | Register<br>48 Bytes <sup>(1)</sup> |      | Unimplemented<br>Read as '0'  |      | Unimplemented<br>Read as '0'  |      | Unimplemented<br>Read as '0'  |

|      | Purpose                       |      | 80 Bytes                       |      | 80 Bytes                       |      | 80 Bytes <sup>(1)</sup>        |      | Unimplemented                       |      |                               |      |                               |      |                               |

| 06Fh | Register                      | 0EFh |                                | 16Fh |                                | 1EFh |                                | 26Fh | Read as '0'                         | 2EFh |                               | 36Fh |                               | 3EFh |                               |

| 070h | 96 Bytes                      | 0F0h |                                | 170h |                                | 1F0h |                                | 270h |                                     | 2F0h |                               | 370h |                               | 3F0h |                               |

|      |                               |      | Accesses<br>70h – 7Fh               |      | Accesses<br>70h – 7Fh         |      | Accesses<br>70h – 7Fh         |      | Accesses<br>70h – 7Fh         |

| 07Fh |                               | 0FFh |                                | 17Fh |                                | 1FFh |                                | 27Fh |                                     | 2FFh |                               | 37Fh |                               | 3FFh |                               |

Legend: = Unimplemented data memory locations, read as '0'

Note 1: Available only on PIC16(L)F1827.

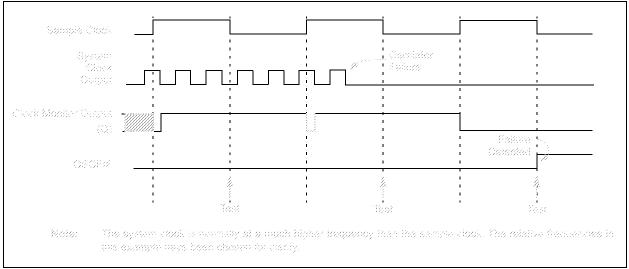

## 6.0 REFERENCE CLOCK MODULE

The reference clock module provides the ability to send a divided clock to the clock output pin of the device (CLKR) and provide a secondary internal clock source to the modulator module. This module is available in all oscillator configurations and allows the user to select a greater range of clock submultiples to drive external devices in the application. The reference clock module includes the following features:

- System clock is the source

- Available in all oscillator configurations

- · Programmable clock divider

- Output enable to a port pin

- · Selectable duty cycle

- Slew rate control

The reference clock module is controlled by the CLKRCON register (Register 6-1) and is enabled when setting the CLKREN bit. To output the divided clock signal to the CLKR port pin, the CLKROE bit must be set. The CLKRDIV<2:0> bits enable the selection of 8 different clock divider options. The CLKRDC<1:0> bits can be used to modify the duty cycle of the output clock<sup>(1)</sup>. The CLKRSLR bit controls slew rate limiting.

Note 1: If the base clock rate is selected without a divider, the output clock will always have a duty cycle equal to that of the source clock, unless a 0% duty cycle is selected. If the clock divider is set to base clock/2, then 25% and 75% duty cycle accuracy will be dependent upon the source clock.

For information on using the reference clock output with the modulator module, see **Section 23.0 "Data Signal Modulator"**.

### 6.1 Slew Rate

The slew rate limitation on the output port pin can be disabled. The slew rate limitation can be removed by clearing the CLKRSLR bit in the CLKRCON register.

### 6.2 Effects of a Reset

Upon any device Reset, the reference clock module is disabled. The user's firmware is responsible for initializing the module before enabling the output. The registers are reset to their default values.

### 6.3 Conflicts with the CLKR Pin

There are two cases when the reference clock output signal cannot be output to the CLKR pin, if:

- LP, XT or HS Oscillator mode is selected.

- CLKOUT function is enabled.

Even if either of these cases are true, the module can still be enabled and the reference clock signal may be used in conjunction with the modulator module.

### 6.3.1 OSCILLATOR MODES

If LP, XT or HS oscillator modes are selected, the OSC2/CLKR pin must be used as an oscillator input pin and the CLKR output cannot be enabled. See **Section 5.2 "Clock Source Types**" for more information on different oscillator modes.

### 6.3.2 CLKOUT FUNCTION

The CLKOUT function has a higher priority than the reference clock module. <u>Therefore</u>, if the CLKOUT function is enabled by the CLKOUTEN bit in Configuration Word 1, FOSC/4 will always be output on the port pin. Reference **Section 4.0** "**Device Configuration**" for more information.

### 6.4 Operation During Sleep

As the reference clock module relies on the system clock as its source, and the system clock is disabled in Sleep, the module does not function in Sleep, even if an external clock source or the Timer1 clock source is configured as the system clock. The module outputs will remain in their current state until the device exits Sleep.

### 8.6.3 PIE2 REGISTER

The PIE2 register contains the interrupt enable bits, as shown in Register 8-3.

**Note:** Bit PEIE of the INTCON register must be set to enable any peripheral interrupt.

| REGISTER 8-3: | PIE2: PERIPHERAL INTERRUPT ENABLE REGISTER 2 |

|---------------|----------------------------------------------|

|               |                                              |

| R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | U-0 | U-0 | R/W-0/0               |

|---------|---------|---------|---------|---------|-----|-----|-----------------------|

| OSFIE   | C2IE    | C1IE    | EEIE    | BCL1IE  | —   | _   | CCP2IE <sup>(1)</sup> |

| bit 7   |         |         |         |         |     |     | bit 0                 |

| Legend:                                        |                                                                                                                           |                                                             |                                                       |  |  |  |  |

|------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|-------------------------------------------------------|--|--|--|--|

| R = Readable bit                               |                                                                                                                           | W = Writable bit                                            | U = Unimplemented bit, read as '0'                    |  |  |  |  |

| u = Bit is uncha                               | anged                                                                                                                     | x = Bit is unknown                                          | -n/n = Value at POR and BOR/Value at all other Resets |  |  |  |  |

| '1' = Bit is set                               |                                                                                                                           | '0' = Bit is cleared                                        |                                                       |  |  |  |  |

| bit 7                                          |                                                                                                                           | lator Fail Interrupt Enable                                 |                                                       |  |  |  |  |

|                                                |                                                                                                                           | the Oscillator Fail interrup<br>the Oscillator Fail interru |                                                       |  |  |  |  |

| bit 6                                          | C2IE: Compa                                                                                                               | rator C2 Interrupt Enable                                   | e bit                                                 |  |  |  |  |

|                                                | <ul> <li>1 = Enables the Comparator C2 interrupt</li> <li>0 = Disables the Comparator C2 interrupt</li> </ul>             |                                                             |                                                       |  |  |  |  |

| bit 5 C1IE: Comparator C1 Interrupt Enable bit |                                                                                                                           |                                                             |                                                       |  |  |  |  |

|                                                | <ul> <li>1 = Enables the Comparator C1 interrupt</li> <li>0 = Disables the Comparator C1 interrupt</li> </ul>             |                                                             |                                                       |  |  |  |  |

| bit 4                                          | EEIE: EEPRO                                                                                                               | OM Write Completion Inte                                    | errupt Enable bit                                     |  |  |  |  |

|                                                |                                                                                                                           | the EEPROM Write Com<br>the EEPROM Write Com                | · · ·                                                 |  |  |  |  |

| bit 3                                          | BCL1IE: MSS                                                                                                               | SP1 Bus Collision Interrup                                  | pt Enable bit                                         |  |  |  |  |

|                                                | <ul> <li>1 = Enables the MSSP1 Bus Collision Interrupt</li> <li>0 = Disables the MSSP1 Bus Collision Interrupt</li> </ul> |                                                             |                                                       |  |  |  |  |

| bit 2-1                                        | Unimplemented: Read as '0'                                                                                                |                                                             |                                                       |  |  |  |  |

| bit 0                                          | CCP2IE: CCF                                                                                                               | P2 Interrupt Enable bit                                     |                                                       |  |  |  |  |

|                                                |                                                                                                                           | the CCP2 interrupt the CCP2 interrupt                       |                                                       |  |  |  |  |

Note 1: PIC16(L)F1827 only.

### 8.6.6 PIR1 REGISTER

The PIR1 register contains the interrupt flag bits, as shown in Register 8-6.

| Note: | Interrupt flag bits are set when an interrupt   |

|-------|-------------------------------------------------|

|       | condition occurs, regardless of the state of    |

|       | its corresponding enable bit or the Global      |

|       | Enable bit, GIE, of the INTCON register.        |

|       | User software should ensure the                 |

|       | appropriate interrupt flag bits are clear prior |

|       | to enabling an interrupt.                       |

### REGISTER 8-6: PIR1: PERIPHERAL INTERRUPT REQUEST REGISTER 1

| R/W-0/0 | R/W-0/0 | R-0/0 | R-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|---------|---------|-------|-------|---------|---------|---------|---------|

| TMR1GIF | ADIF    | RCIF  | TXIF  | SSP1IF  | CCP1IF  | TMR2IF  | TMR1IF  |

| bit 7   |         |       |       |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7 | TMR1GIF: Timer1 Gate Interrupt Flag bit                      |

|-------|--------------------------------------------------------------|

|       | 1 = Interrupt is pending                                     |

|       | 0 = Interrupt is not pending                                 |

| bit 6 | ADIF: A/D Converter Interrupt Flag bit                       |

|       | 1 = Interrupt is pending                                     |

|       | 0 = Interrupt is not pending                                 |

| bit 5 | RCIF: USART Receive Interrupt Flag bit                       |

|       | 1 = Interrupt is pending                                     |

|       | 0 = Interrupt is not pending                                 |

| bit 4 | TXIF: USART Transmit Interrupt Flag bit                      |

|       | 1 = Interrupt is pending                                     |

|       | 0 = Interrupt is not pending                                 |

| bit 3 | SSP1IF: Synchronous Serial Port 1 (MSSP1) Interrupt Flag bit |

|       | 1 = Interrupt is pending                                     |

|       | 0 = Interrupt is not pending                                 |

| bit 2 | CCP1IF: CCP1 Interrupt Flag bit                              |

|       | 1 = Interrupt is pending                                     |

|       | 0 = Interrupt is not pending                                 |

| bit 1 | TMR2IF: Timer2 to PR2 Interrupt Flag bit                     |

|       | 1 = Interrupt is pending                                     |

|       | 0 = Interrupt is not pending                                 |

| bit 0 | TMR1IF: Timer1 Overflow Interrupt Flag bit                   |

|       | 1 = Interrupt is pending                                     |

|       | 0 = Interrupt is not pending                                 |

|       |                                                              |

### 8.6.9 PIR4 REGISTER<sup>(1)</sup>

The PIR4 register contains the interrupt flag bits, as shown in Register 8-9.

- **Note 1:** The PIR4 register is available only on the PIC16(L)F1827 device.

- 2: Interrupt flag bits are set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the Global Enable bit, GIE, of the INTCON register. User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

### **REGISTER 8-9: PIR4: PERIPHERAL INTERRUPT REQUEST REGISTER 4<sup>(1)</sup>**

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | R/W/HS-0/0 | R/W/HS-0/0 |

|-------|-----|-----|-----|-----|-----|------------|------------|

| —     | —   | —   | —   | —   | —   | BCL2IF     | SSP2IF     |

| bit 7 |     |     |     |     |     |            | bit 0      |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | HS = Bit is set by hardware                           |

| bit 7-2 | Unimplemented: Read as '0'                                                                                                                                                                                                                                 |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 1   | BCL2IF: MSSP2 Bus Collision Interrupt Flag bit                                                                                                                                                                                                             |

|         | <ul><li>1 = A Bus Collision was detected (must be cleared in software)</li><li>0 = No Bus collision was detected</li></ul>                                                                                                                                 |

| bit 0   | <ul> <li>SSP2IF: Master Synchronous Serial Port 2 (MSSP2) Interrupt Flag bit</li> <li>1 = The Transmission/Reception/Bus Condition is complete (must be cleared in software)</li> <li>0 = Waiting to Transmit/Receive/Bus Condition in progress</li> </ul> |

**Note 1:** This register is only available on PIC16(L)F1827.

### TABLE 8-1: SUMMARY OF REGISTERS ASSOCIATED WITH INTERRUPTS

| Name                | Bit 7   | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0                 | Register<br>on Page |

|---------------------|---------|--------|--------|--------|--------|--------|--------|-----------------------|---------------------|

| INTCON              | GIE     | PEIE   | TMR0IE | INTE   | IOCIE  | TMR0IF | INTF   | IOCIF                 | 86                  |

| OPTION_REG          | WPUEN   | INTEDG | TMR0CS | TMR0SE | PSA    | PS2    | PS1    | PS0                   | 177                 |

| PIE1                | TMR1GIE | ADIE   | RCIE   | TXIE   | SSP1IE | CCP1IE | TMR2IE | TMR1IE                | 87                  |

| PIE2                | OSFIE   | C2IE   | C1IE   | EEIE   | BCL1IE | —      | _      | CCP2IE <sup>(1)</sup> | 88                  |

| PIE3 <sup>(1)</sup> | _       | -      | CCP4IE | CCP3IE | TMR6IE | _      | TMR4IE | _                     | 89                  |

| PIE4 <sup>(1)</sup> | _       | -      | _      | _      | -      | _      | BCL2IE | SSP2IE                | 90                  |

| PIR1                | TMR1GIF | ADIF   | RCIF   | TXIF   | SSP1IF | CCP1IF | TMR2IF | TMR1IF                | 91                  |

| PIR2                | OSFIF   | C2IF   | C1IF   | EEIF   | BCL1IF | —      | _      | CCP2IF <sup>(1)</sup> | 92                  |

| PIR3 <sup>(1)</sup> | _       | _      | CCP4IF | CCP3IF | TMR6IF | _      | TMR4IF | _                     | 93                  |

| PIR4 <sup>(1)</sup> | _       | _      | _      | _      | _      | _      | BCL2IF | SSP2IF                | 94                  |

Legend: — = unimplemented locations read as '0'. Shaded cells are not used by Interrupts.

Note 1: PIC16(L)F1827 only.

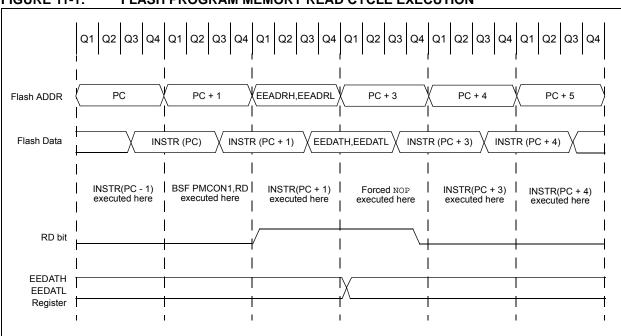

### FIGURE 11-1: FLASH PROGRAM MEMORY READ CYCLE EXECUTION

### 11.3.2 ERASING FLASH PROGRAM MEMORY

While executing code, program memory can only be erased by rows. To erase a row:

- 1. Load the EEADRH:EEADRL register pair with the address of new row to be erased.

- 2. Clear the CFGS bit of the EECON1 register.

- 3. Set the EEPGD, FREE, and WREN bits of the EECON1 register.

- 4. Write 55h, then AAh, to EECON2 (Flash programming unlock sequence).

- 5. Set control bit WR of the EECON1 register to begin the erase operation.

- 6. Poll the FREE bit in the EECON1 register to determine when the row erase has completed.

### See Example 11-4.

After the "BSF EECON1, WR" instruction, the processor requires two cycles to set up the erase operation. The user must place two NOP instructions after the WR bit is set. The processor will halt internal operations for the typical 2 ms erase time. This is not Sleep mode as the clocks and peripherals will continue to run. After the erase cycle, the processor will resume operation with the third instruction after the EECON1 write instruction.

## 11.3.3 WRITING TO FLASH PROGRAM MEMORY

Program memory is programmed using the following steps:

- 1. Load the starting address of the word(s) to be programmed.

- 2. Load the write latches with data.

- 3. Initiate a programming operation.

- 4. Repeat steps 1 through 3 until all data is written.

Before writing to program memory, the word(s) to be written must be erased or previously unwritten. Program memory can only be erased one row at a time. No automatic erase occurs upon the initiation of the write.

Program memory can be written one or more words at a time. The maximum number of words written at one time is equal to the number of write latches. See Figure 11-2 (block writes to program memory with 32 write latches) for more details. The write latches are aligned to the address boundary defined by EEADRL as shown in Table 11-1. Write operations do not cross these boundaries. At the completion of a program memory write operation, the write latches are reset to contain 0x3FFF. The following steps should be completed to load the write latches and program a block of program memory. These steps are divided into two parts. First, all write latches are loaded with data except for the last program memory location. Then, the last write latch is loaded and the programming sequence is initiated. A special unlock sequence is required to load a write latch with data or initiate a Flash programming operation. This unlock sequence should not be interrupted.

- 1. Set the EEPGD and WREN bits of the EECON1 register.

- 2. Clear the CFGS bit of the EECON1 register.

- Set the LWLO bit of the EECON1 register. When the LWLO bit of the EECON1 register is '1', the write sequence will only load the write latches and will not initiate the write to Flash program memory.

- 4. Load the EEADRH:EEADRL register pair with the address of the location to be written.

- 5. Load the EEDATH:EEDATL register pair with the program memory data to be written.

- 6. Write 55h, then AAh, to EECON2, then set the WR bit of the EECON1 register (Flash programming unlock sequence). The write latch is now loaded.

- 7. Increment the EEADRH:EEADRL register pair to point to the next location.

- 8. Repeat steps 5 through 7 until all but the last write latch has been loaded.

- Clear the LWLO bit of the EECON1 register. When the LWLO bit of the EECON1 register is '0', the write sequence will initiate the write to Flash program memory.

- 10. Load the EEDATH:EEDATL register pair with the program memory data to be written.

- 11. Write 55h, then AAh, to EECON2, then set the WR bit of the EECON1 register (Flash programming unlock sequence). The entire latch block is now written to Flash program memory.

It is not necessary to load the entire write latch block with user program data. However, the entire write latch block will be written to program memory.

An example of the complete write sequence for eight words is shown in Example 11-5. The initial address is loaded into the EEADRH:EEADRL register pair; the eight words of data are loaded using indirect addressing.

| R/W-0/0          | R/W-0/0               | R/W-0/0                       | R/W/HC-0/0                           | R/W-x/q           | R/W-0/0         | R/S/HC-0/0               | R/S/HC-0/0      |

|------------------|-----------------------|-------------------------------|--------------------------------------|-------------------|-----------------|--------------------------|-----------------|

| EEPGD            | CFGS                  | LWLO                          | FREE                                 | WRERR             | WREN            | WR                       | RD              |

| bit 7            |                       |                               |                                      |                   |                 |                          | bit (           |

|                  |                       |                               |                                      |                   |                 |                          |                 |

| Legend:          | <b>b</b> :4           |                               | <b>b</b> :4                          |                   | nanted bit was  | d aa (0)                 |                 |

| R = Readable     |                       | W = Writable                  |                                      | •                 | nented bit, rea |                          | than Decete     |

| S = Bit can or   | 5                     | x = Bit is unk                |                                      |                   |                 | R/Value at all o         | iner Resets     |

| '1' = Bit is set |                       | '0' = Bit is cl€              | eared                                | HC = Bit is cl    | eared by hardv  | vare                     |                 |

| bit 7            | EEPGD: Flas           | sh Program/Da                 | ta EEPROM M                          | emory Select      | bit             |                          |                 |

|                  | 1 = Accesse           | s program spa                 | ce Flash memo                        | -                 |                 |                          |                 |

|                  |                       | s data EEPRC                  | -                                    |                   |                 |                          |                 |

| bit 6            |                       | -                             | EEPROM or C                          | -                 |                 |                          |                 |

|                  |                       |                               | n, User ID and I<br>Im or data EEP   |                   |                 |                          |                 |

| bit 5            |                       | Write Latches                 |                                      |                   |                 |                          |                 |

| bit 0            |                       |                               | <u>space)</u> OR <u>CFC</u>          | SS = 0 and $FF$   | PGD = 1 (proc   | oram Flash) <sup>.</sup> |                 |

|                  |                       | -                             |                                      |                   |                 | program memoi            | v latches are   |

|                  | upda                  | ated.                         |                                      |                   |                 | C                        | -               |

|                  |                       |                               |                                      |                   |                 | into program m           | emory latche    |

|                  | and                   | initiates a write             | e of all the data                    | stored in the     | program memo    | bry latches.             |                 |

|                  | <u> If CFGS = 0 a</u> | and EEPGD =                   | 0: (Accessing c                      | lata EEPROM       | 1)              |                          |                 |

|                  |                       |                               | WR command i                         |                   |                 | EPROM.                   |                 |

| bit 4            | FREE: Progr           | am Flash Eras                 | e Enable bit                         |                   |                 |                          |                 |

|                  |                       | -                             | <u>space)</u> OR <u>CFC</u>          |                   |                 | -                        |                 |

|                  |                       |                               | operation on the                     | he next WR co     | ommand (clear   | ed by hardware           | after comple    |

|                  |                       | of erase).<br>forms a write o | peration on the                      | next WR com       | mand            |                          |                 |

|                  | 0 - 1 Ch              |                               | peration on the                      |                   | inana.          |                          |                 |

|                  |                       |                               | 0: (Accessing c                      |                   |                 |                          |                 |

|                  | -                     |                               |                                      | will initiate bot | h a erase cycle | e and a write cyc        | de.             |

| bit 3            |                       | PROM Error F                  | •                                    |                   |                 |                          |                 |

|                  |                       |                               | improper prog<br>et attempt (write   |                   |                 | empt or termination      | tion (bit is se |

|                  |                       |                               | operation comp                       |                   |                 |                          |                 |

| bit 2            |                       | ram/Erase Ena                 | • •                                  | j                 |                 |                          |                 |

|                  | -                     | rogram/erase o                |                                      |                   |                 |                          |                 |

|                  |                       |                               | rasing of progra                     | am Flash and      | data EEPROM     | l                        |                 |

| bit 1            | WR: Write Co          | ontrol bit                    |                                      |                   |                 |                          |                 |

|                  |                       |                               | sh or data EEPI                      |                   |                 |                          |                 |

|                  |                       |                               | ned and the bit<br>e set (not cleare |                   |                 | operation is co          | mplete.         |

|                  |                       | •                             | on to the Flash                      |                   |                 | e and inactive.          |                 |

| bit 0            | RD: Read Co           | -                             |                                      |                   |                 |                          |                 |

|                  |                       |                               | lash or data E                       | EPROM read        | d. Read takes   | one cycle. RD            | is cleared in   |

|                  |                       |                               |                                      |                   |                 | , <b>.</b>               |                 |

|                  | nardware              | e. The RD bit o               | an only be set                       | (not cleared) i   | n software.     |                          |                 |

### REGISTER 11-5: EECON1: EEPROM CONTROL 1 REGISTER

NOTES:

| R/W-0/0          | R/W-0/0                    | R/W-0/0            | R/W-0/0      | R/W-0/0        | R/W-0/0          | R/W-0/0        | R/W-0/0      |

|------------------|----------------------------|--------------------|--------------|----------------|------------------|----------------|--------------|

| C4TSI            | EL<1:0>                    | C3TSE              | L<1:0>       | C2TSE          | EL<1:0>          | C1TSE          | EL<1:0>      |

| bit 7            |                            |                    |              |                |                  |                | bit 0        |

|                  |                            |                    |              |                |                  |                |              |

| Legend:          |                            |                    |              |                |                  |                |              |

| R = Readable     | e bit                      | W = Writable       | bit          | U = Unimplen   | nented bit, read | d as '0'       |              |

| u = Bit is uncl  | nanged                     | x = Bit is unkr    | nown         | -n/n = Value a | at POR and BO    | R/Value at all | other Resets |

| '1' = Bit is set |                            | '0' = Bit is clea  | ared         |                |                  |                |              |

|                  |                            |                    |              |                |                  |                |              |

| bit 7-6          | C4TSEL<1:0                 | >: CCP4 Timer      | Selection    |                |                  |                |              |

|                  |                            | based off Time     |              |                |                  |                |              |

|                  |                            | based off Time     |              |                |                  |                |              |

|                  | 10 =CCP4 is<br>11 =Reserve | based off Time     | r 6 in PWM M | ode            |                  |                |              |

| bit 5-4          |                            | o<br>>: CCP3 Timer | Soloction    |                |                  |                |              |

| DIL 3-4          |                            | based off Time     |              | odo            |                  |                |              |

|                  |                            | based off Time     |              |                |                  |                |              |

|                  |                            | based off Time     |              |                |                  |                |              |

|                  | 11 =Reserve                | d                  |              |                |                  |                |              |

| bit 3-2          | C2TSEL<1:0                 | >: CCP2 Timer      | Selection    |                |                  |                |              |

|                  | 00 00. 2.0                 | based off Time     |              | 0.0            |                  |                |              |

|                  |                            | based off Time     |              |                |                  |                |              |

|                  | 10 =CCP2 is<br>11 =Reserve | based off Time     | r 6 in PWM M | ode            |                  |                |              |

| bit 1-0          |                            | o<br>>: CCP1 Timer | Soloction    |                |                  |                |              |

| DIL 1-0          |                            | based off Time     |              | odo            |                  |                |              |

|                  |                            | based off Time     |              |                |                  |                |              |

|                  |                            | based off Time     |              |                |                  |                |              |

|                  | 11 =Reserve                |                    |              |                |                  |                |              |

### REGISTER 24-2: CCPTMRS: PWM TIMER SELECTION CONTROL REGISTER

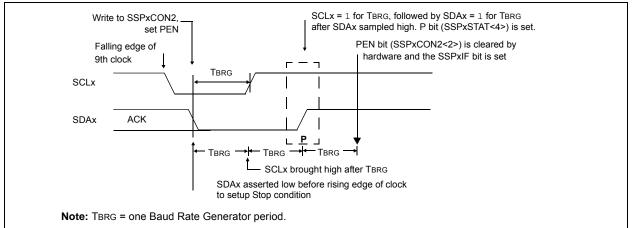

### FIGURE 25-31: STOP CONDITION RECEIVE OR TRANSMIT MODE

### 25.6.10 SLEEP OPERATION

While in Sleep mode, the I<sup>2</sup>C slave module can receive addresses or data and when an address match or complete byte transfer occurs, wake the processor from Sleep (if the MSSPx interrupt is enabled).

### 25.6.11 EFFECTS OF A RESET

A Reset disables the MSSPx module and terminates the current transfer.

### 25.6.12 MULTI-MASTER MODE

In Multi-Master mode, the interrupt generation on the detection of the Start and Stop conditions allows the determination of when the bus is free. The Stop (P) and Start (S) bits are cleared from a Reset or when the MSSPx module is disabled. Control of the I<sup>2</sup>C bus may be taken when the P bit of the SSPxSTAT register is set, or the bus is Idle, with both the S and P bits clear. When the bus is busy, enabling the SSPx interrupt will generate the interrupt when the Stop condition occurs.

In multi-master operation, the SDAx line must be monitored for arbitration to see if the signal level is the expected output level. This check is performed by hardware with the result placed in the BCLxIF bit.

The states where arbitration can be lost are:

- Address Transfer

- · Data Transfer

- A Start Condition

- A Repeated Start Condition

- An Acknowledge Condition

### 25.6.13 MULTI -MASTER COMMUNICATION, BUS COLLISION AND BUS ARBITRATION

Multi-Master mode support is achieved by bus arbitration. When the master outputs address/data bits onto the SDAx pin, arbitration takes place when the master outputs a '1' on SDAx, by letting SDAx float high and another master asserts a '0'. When the SCLx pin floats high, data should be stable. If the expected data on SDAx is a '1' and the data sampled on the SDAx pin is '0', then a bus collision has taken place. The master will set the Bus Collision Interrupt Flag, BCLxIF and reset the I<sup>2</sup>C port to its Idle state (Figure 25-31).

If a transmit was in progress when the bus collision occurred, the transmission is halted, the BF flag is cleared, the SDAx and SCLx lines are deasserted and the SSPxBUF can be written to. When the user services the bus collision Interrupt Service Routine and if the  $l^2C$  bus is free, the user can resume communication by asserting a Start condition.

If a Start, Repeated Start, Stop or Acknowledge condition was in progress when the bus collision occurred, the condition is aborted, the SDAx and SCLx lines are deasserted and the respective control bits in the SSPxCON2 register are cleared. When the user services the bus collision Interrupt Service Routine and if the I<sup>2</sup>C bus is free, the user can resume communication by asserting a Start condition.

The master will continue to monitor the SDAx and SCLx pins. If a Stop condition occurs, the SSPxIF bit will be set.

A write to the SSPxBUF will start the transmission of data at the first data bit, regardless of where the transmitter left off when the bus collision occurred.

In Multi-Master mode, the interrupt generation on the detection of Start and Stop conditions allows the determination of when the bus is free. Control of the  $I^2C$  bus can be taken when the P bit is set in the SSPxSTAT register, or the bus is Idle and the S and P bits are cleared.

| Name    | Bit 7   | Bit 6   | Bit 5  | Bit 4                 | Bit 3                  | Bit 2  | Bit 1  | Bit 0   | Register<br>on Page |

|---------|---------|---------|--------|-----------------------|------------------------|--------|--------|---------|---------------------|

| APFCON0 | RXDTSEL | SDO1SEL | SS1SEL | P2BSEL <sup>(1)</sup> | CCP2SEL <sup>(1)</sup> | P1DSEL | P1CSEL | CCP1SEL | 119                 |

| APFCON1 | —       | _       | —      | —                     | _                      | _      | _      | TXCKSEL | 119                 |

| BAUDCON | ABDOVF  | RCIDL   |        | SCKP                  | BRG16                  | _      | WUE    | ABDEN   | 296                 |

| INTCON  | GIE     | PEIE    | TMR0IE | INTE                  | IOCIE                  | TMR0IF | INTF   | IOCIF   | 86                  |

| PIE1    | TMR1GIE | ADIE    | RCIE   | TXIE                  | SSPIE                  | CCP1IE | TMR2IE | TMR1IE  | 87                  |

| PIR1    | TMR1GIF | ADIF    | RCIF   | TXIF                  | SSPIF                  | CCP1IF | TMR2IF | TMR1IF  | 91                  |

| RCREG   |         |         | EU     | SART Recei            | ve Data Regis          | ter    |        |         | 290*                |

| RCSTA   | SPEN    | RX9     | SREN   | CREN                  | ADDEN                  | FERR   | OERR   | RX9D    | 295                 |

| SPBRGL  |         |         |        | BRG                   | <7:0>                  |        |        |         | 297*                |

| SPBRGH  |         |         |        | BRG∢                  | <15:8>                 |        |        |         | 297*                |

| TRISB   | TRISB7  | TRISB6  | TRISB5 | TRISB4                | TRISB3                 | TRISB2 | TRISB1 | TRISB0  | 127                 |

| TXSTA   | CSRC    | TX9     | TXEN   | SYNC                  | SENDB                  | BRGH   | TRMT   | TX9D    | 294                 |

### TABLE 26-2: SUMMARY OF REGISTERS ASSOCIATED WITH ASYNCHRONOUS RECEPTION

Legend: — = unimplemented location, read as '0'. Shaded cells are not used for Asynchronous Reception.

\* Page provides register information.

Note 1: PIC16(L)F1827 only.

| R/W-0/0          | R/W-0/0                           | R/W-0/0                            | R/W-0/0            | R/W-0/0         | R-0/0            | R-0/0            | R-0/0       |

|------------------|-----------------------------------|------------------------------------|--------------------|-----------------|------------------|------------------|-------------|

| SPEN             | RX9                               | SREN                               | CREN               | ADDEN           | FERR             | OERR             | RX9D        |

| bit 7            |                                   |                                    | ·                  |                 | ·                |                  | bit 0       |

|                  |                                   |                                    |                    |                 |                  |                  |             |

| Legend:          |                                   |                                    |                    |                 |                  |                  |             |

| R = Readable     | e bit                             | W = Writable                       | bit                | U = Unimpler    | mented bit, read | l as '0'         |             |

| u = Bit is unch  | nanged                            | x = Bit is unki                    | nown               | -n/n = Value a  | at POR and BO    | R/Value at all o | ther Resets |

| '1' = Bit is set |                                   | '0' = Bit is cle                   | ared               |                 |                  |                  |             |

|                  |                                   |                                    |                    |                 |                  |                  |             |

| bit 7            |                                   | Port Enable bi                     |                    |                 | ••••••           |                  |             |

|                  |                                   | rt enabled (cor<br>rt disabled (he |                    | I and I X/CK p  | ins as serial po | rt pins)         |             |

| bit 6            |                                   | ceive Enable t                     |                    |                 |                  |                  |             |

| 2                | 1 = Selects 9                     |                                    |                    |                 |                  |                  |             |

|                  | 0 = Selects 8                     |                                    |                    |                 |                  |                  |             |

| bit 5            | SREN: Single                      | e Receive Enal                     | ole bit            |                 |                  |                  |             |

|                  | Asynchronou                       | <u>s mode</u> :                    |                    |                 |                  |                  |             |

|                  | Don't care                        | mada Maata                         |                    |                 |                  |                  |             |

|                  | -                                 | mode – Maste<br>single receive     | <u>r</u> .         |                 |                  |                  |             |

|                  |                                   | single receive                     |                    |                 |                  |                  |             |

|                  |                                   | ared after rece                    | ption is compl     | ete.            |                  |                  |             |

|                  | •                                 | mode – Slave                       |                    |                 |                  |                  |             |

|                  | Don't care                        |                                    |                    |                 |                  |                  |             |

| bit 4            |                                   | nuous Receive                      | Enable bit         |                 |                  |                  |             |

|                  | <u>Asynchronou</u><br>1 = Enables |                                    |                    |                 |                  |                  |             |

|                  | 0 = Disables                      |                                    |                    |                 |                  |                  |             |

|                  | <u>Synchronous</u>                |                                    |                    |                 |                  |                  |             |

|                  |                                   | continuous rec<br>continuous rec   |                    | ole bit CREN is | cleared (CREN    | l overrides SR   | EN)         |

| bit 3            | ADDEN: Add                        | ress Detect Er                     | able bit           |                 |                  |                  |             |

|                  | Asynchronou                       | <u>s mode 9-bit (</u> F            | RX9 = 1):          |                 |                  |                  |             |

|                  |                                   |                                    |                    | •               | d the receive bu |                  |             |

|                  |                                   | address detec<br>s mode 8-bit (F   |                    | are received a  | nd ninth bit can | be used as pa    | rity bit    |

|                  | Don't care                        |                                    | <u>(//9 – 0)</u> . |                 |                  |                  |             |

| bit 2            | FERR: Frami                       | na Error bit                       |                    |                 |                  |                  |             |

|                  |                                   | error (can be ι                    | pdated by rea      | Iding RCREG I   | register and rec | eive next valid  | byte)       |

| bit 1            | OERR: Overr                       | •                                  |                    |                 |                  |                  |             |

|                  |                                   | error (can be c                    | leared by clea     | ring bit CREN   | )                |                  |             |

|                  | 0 = No overn                      |                                    | 2                  | -               |                  |                  |             |

| bit 0            |                                   | bit of Received                    |                    |                 |                  |                  |             |

|                  | This can be a                     | ddress/data bi                     | t or a parity bi   | and must be o   | calculated by us | er firmware.     |             |

## REGISTER 26-2: RCSTA: RECEIVE STATUS AND CONTROL REGISTER<sup>(1)</sup>

|        |                |            |                             |                   | SYNC       | <b>C</b> = 0, BRGH          | l = 0, BRG     | <b>616 =</b> 0    |                             |                |            |                             |

|--------|----------------|------------|-----------------------------|-------------------|------------|-----------------------------|----------------|-------------------|-----------------------------|----------------|------------|-----------------------------|

| BAUD   | Fosc           | = 32.00    | 0 MHz                       | Fosc = 20.000 MHz |            |                             | Foso           | Fosc = 18.432 MHz |                             |                | = 11.059   | 92 MHz                      |

| RATE   | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate    | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error        | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) |

| 300    | _              | _          | _                           | _                 |            | _                           | _              | _                 | _                           | _              | _          | _                           |

| 1200   | —              |            | —                           | 1221              | 1.73       | 255                         | 1200           | 0.00              | 239                         | 1200           | 0.00       | 143                         |

| 2400   | 2404           | 0.16       | 207                         | 2404              | 0.16       | 129                         | 2400           | 0.00              | 119                         | 2400           | 0.00       | 71                          |

| 9600   | 9615           | 0.16       | 51                          | 9470              | -1.36      | 32                          | 9600           | 0.00              | 29                          | 9600           | 0.00       | 17                          |

| 10417  | 10417          | 0.00       | 47                          | 10417             | 0.00       | 29                          | 10286          | -1.26             | 27                          | 10165          | -2.42      | 16                          |

| 19.2k  | 19.23k         | 0.16       | 25                          | 19.53k            | 1.73       | 15                          | 19.20k         | 0.00              | 14                          | 19.20k         | 0.00       | 8                           |

| 57.6k  | 55.55k         | -3.55      | 3                           | —                 | —          | _                           | 57.60k         | 0.00              | 7                           | 57.60k         | 0.00       | 2                           |

| 115.2k | —              | —          | _                           | —                 | —          | —                           | —              | —                 | —                           | —              | —          | —                           |

### TABLE 26-5: BAUD RATES FOR ASYNCHRONOUS MODES

|        |                |            |                             |                  | SYNC       | <b>C =</b> 0, BRGH          | l = 0, BRG        | <b>616 =</b> 0 |                             |                |                  |                             |  |

|--------|----------------|------------|-----------------------------|------------------|------------|-----------------------------|-------------------|----------------|-----------------------------|----------------|------------------|-----------------------------|--|

| BAUD   | Fos            | c = 8.000  | ) MHz                       | Fosc = 4.000 MHz |            |                             | Fosc = 3.6864 MHz |                |                             | Fos            | Fosc = 1.000 MHz |                             |  |

| RATE   | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate   | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate    | %<br>Error     | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error       | SPBRG<br>value<br>(decimal) |  |

| 300    |                | _          | _                           | 300              | 0.16       | 207                         | 300               | 0.00           | 191                         | 300            | 0.16             | 51                          |  |

| 1200   | 1202           | 0.16       | 103                         | 1202             | 0.16       | 51                          | 1200              | 0.00           | 47                          | 1202           | 0.16             | 12                          |  |

| 2400   | 2404           | 0.16       | 51                          | 2404             | 0.16       | 25                          | 2400              | 0.00           | 23                          | _              | _                | _                           |  |

| 9600   | 9615           | 0.16       | 12                          | _                | _          | _                           | 9600              | 0.00           | 5                           | _              | _                | _                           |  |

| 10417  | 10417          | 0.00       | 11                          | 10417            | 0.00       | 5                           | _                 | _              | _                           | _              | _                | _                           |  |

| 19.2k  | —              | _          | _                           | _                | _          | _                           | 19.20k            | 0.00           | 2                           | _              | _                | _                           |  |

| 57.6k  | —              | _          | —                           | —                | _          | —                           | 57.60k            | 0.00           | 0                           | _              | _                | —                           |  |

| 115.2k | —              | _          | _                           | —                | _          | _                           | _                 | _              | _                           | _              | _                | —                           |  |

|        |                |         |                             |                   | SYNC       | <b>C</b> = 0, BRGH          | l = 1, BRC     | <b>G16 =</b> 0 |                             |                |            |                             |

|--------|----------------|---------|-----------------------------|-------------------|------------|-----------------------------|----------------|----------------|-----------------------------|----------------|------------|-----------------------------|

| BAUD   | Foso           | = 32.00 | 0 MHz                       | Fosc = 20.000 MHz |            |                             | Fosc           | : = 18.43      | 2 MHz                       | Fosc           | = 11.059   | 92 MHz                      |

| RATE   | Actual<br>Rate |         | SPBRG<br>value<br>(decimal) | Actual<br>Rate    | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error     | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) |

| 300    | —              | —       | —                           |                   |            | _                           |                | _              | —                           |                | —          | _                           |

| 1200   | _              | _       | —                           | _                 |            | —                           | _              | _              | —                           | —              | _          | —                           |

| 2400   |                | _       | _                           | _                 | _          | _                           | _              | _              | _                           | _              | _          | _                           |

| 9600   | 9615           | 0.16    | 207                         | 9615              | 0.16       | 129                         | 9600           | 0.00           | 119                         | 9600           | 0.00       | 71                          |

| 10417  | 10417          | 0.00    | 191                         | 10417             | 0.00       | 119                         | 10378          | -0.37          | 110                         | 10473          | 0.53       | 65                          |

| 19.2k  | 19.23k         | 0.16    | 103                         | 19.23k            | 0.16       | 64                          | 19.20k         | 0.00           | 59                          | 19.20k         | 0.00       | 35                          |

| 57.6k  | 57.14k         | -0.79   | 34                          | 56.82k            | -1.36      | 21                          | 57.60k         | 0.00           | 19                          | 57.60k         | 0.00       | 11                          |

| 115.2k | 117.64k        | 2.12    | 16                          | 113.64k           | -1.36      | 10                          | 115.2k         | 0.00           | 9                           | 115.2k         | 0.00       | 5                           |

|        |                |            |                             | SYNC = 0          | , BRGH     | = 1, BRG16                  | = 1 or SY         | 'NC = 1,   | BRG16 = 1                   |                |            |                             |

|--------|----------------|------------|-----------------------------|-------------------|------------|-----------------------------|-------------------|------------|-----------------------------|----------------|------------|-----------------------------|

| BAUD   | Foso           | : = 32.00  | 0 MHz                       | Fosc = 20.000 MHz |            |                             | Fosc = 18.432 MHz |            |                             | Fosc           | = 11.059   | 92 MHz                      |

| RATE   | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate    | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate    | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) |

| 300    | 300.0          | 0.00       | 26666                       | 300.0             | 0.00       | 16665                       | 300.0             | 0.00       | 15359                       | 300.0          | 0.00       | 9215                        |

| 1200   | 1200           | 0.00       | 6666                        | 1200              | -0.01      | 4166                        | 1200              | 0.00       | 3839                        | 1200           | 0.00       | 2303                        |

| 2400   | 2400           | 0.01       | 3332                        | 2400              | 0.02       | 2082                        | 2400              | 0.00       | 1919                        | 2400           | 0.00       | 1151                        |

| 9600   | 9604           | 0.04       | 832                         | 9597              | -0.03      | 520                         | 9600              | 0.00       | 479                         | 9600           | 0.00       | 287                         |

| 10417  | 10417          | 0.00       | 767                         | 10417             | 0.00       | 479                         | 10425             | 0.08       | 441                         | 10433          | 0.16       | 264                         |

| 19.2k  | 19.18k         | -0.08      | 416                         | 19.23k            | 0.16       | 259                         | 19.20k            | 0.00       | 239                         | 19.20k         | 0.00       | 143                         |

| 57.6k  | 57.55k         | -0.08      | 138                         | 57.47k            | -0.22      | 86                          | 57.60k            | 0.00       | 79                          | 57.60k         | 0.00       | 47                          |

| 115.2k | 115.9k         | 0.64       | 68                          | 116.3k            | 0.94       | 42                          | 115.2k            | 0.00       | 39                          | 115.2k         | 0.00       | 23                          |

### TABLE 26-5: BAUD RATES FOR ASYNCHRONOUS MODES (CONTINUED)

|        |                |            |                             | SYNC = 0       | , BRGH     | = 1, BRG16                  | = 1 or SΥ         | ′NC = 1,   | BRG16 = 1                   |                  |            |                             |

|--------|----------------|------------|-----------------------------|----------------|------------|-----------------------------|-------------------|------------|-----------------------------|------------------|------------|-----------------------------|

| BAUD   | Fos            | c = 8.000  | ) MHz                       | Fos            | c = 4.000  | ) MHz                       | Fosc = 3.6864 MHz |            |                             | Fosc = 1.000 MHz |            |                             |

| RATE   | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate    | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate   | %<br>Error | SPBRG<br>value<br>(decimal) |

| 300    | 300.0          | 0.00       | 6666                        | 300.0          | 0.01       | 3332                        | 300.0             | 0.00       | 3071                        | 300.1            | 0.04       | 832                         |

| 1200   | 1200           | -0.02      | 1666                        | 1200           | 0.04       | 832                         | 1200              | 0.00       | 767                         | 1202             | 0.16       | 207                         |

| 2400   | 2401           | 0.04       | 832                         | 2398           | 0.08       | 416                         | 2400              | 0.00       | 383                         | 2404             | 0.16       | 103                         |

| 9600   | 9615           | 0.16       | 207                         | 9615           | 0.16       | 103                         | 9600              | 0.00       | 95                          | 9615             | 0.16       | 25                          |

| 10417  | 10417          | 0          | 191                         | 10417          | 0.00       | 95                          | 10473             | 0.53       | 87                          | 10417            | 0.00       | 23                          |

| 19.2k  | 19.23k         | 0.16       | 103                         | 19.23k         | 0.16       | 51                          | 19.20k            | 0.00       | 47                          | 19.23k           | 0.16       | 12                          |

| 57.6k  | 57.14k         | -0.79      | 34                          | 58.82k         | 2.12       | 16                          | 57.60k            | 0.00       | 15                          | —                | _          | _                           |

| 115.2k | 117.6k         | 2.12       | 16                          | 111.1k         | -3.55      | 8                           | 115.2k            | 0.00       | 7                           | —                | —          | —                           |

## 26.4.2.3 EUSART Synchronous Slave Reception

The operation of the Synchronous Master and Slave modes is identical (Section 26.4.1.5 "Synchronous Master Reception"), with the following exceptions:

- Sleep

- CREN bit is always set, therefore the receiver is

never Idle

- SREN bit, which is a "don't care" in Slave mode

A character may be received while in Sleep mode by setting the CREN bit prior to entering Sleep. Once the word is received, the RSR register will transfer the data to the RCREG register. If the RCIE enable bit is set, the interrupt generated will wake the device from Sleep and execute the next instruction. If the GIE bit is also set, the program will branch to the interrupt vector.

- 26.4.2.4 Synchronous Slave Reception Set-up:

- 1. Set the SYNC and SPEN bits and clear the CSRC bit.