Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Product Status             | Active                                                                   |

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 32MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                        |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 16                                                                       |

| Program Memory Size        | 7KB (4K x 14)                                                            |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 256 x 8                                                                  |

| RAM Size                   | 384 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                              |

| Data Converters            | A/D 12x10b                                                               |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                       |

| Mounting Type              | Through Hole                                                             |

| Package / Case             | 18-DIP (0.300", 7.62mm)                                                  |

| Supplier Device Package    | 18-PDIP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f1827-e-p |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# TABLE 3-3: PIC16(L)F1826/27 MEMORY MAP

|      | BANK 0                        | 010( | BANK 1                         |      | BANK 2                         |      | BANK 3                         |      | BANK 4                              |      | BANK 5                        |      | BANK 6                        |      | BANK 7                        |

|------|-------------------------------|------|--------------------------------|------|--------------------------------|------|--------------------------------|------|-------------------------------------|------|-------------------------------|------|-------------------------------|------|-------------------------------|

| 000h |                               | 080h |                                | 100h |                                | 180h |                                | 200h |                                     | 280h |                               | 300h |                               | 380h |                               |

|      | Core Registers<br>(Table 3-2) |      | Core Registers<br>(Table 3-2)  |      | Core Registers<br>(Table 3-2)  |      | Core Registers<br>(Table 3-2)  |      | Core Registers<br>(Table 3-2)       |      | Core Registers<br>(Table 3-2) |      | Core Registers<br>(Table 3-2) |      | Core Registers<br>(Table 3-2) |

| 00Bh |                               | 08Bh |                                | 10Bh |                                | 18Bh |                                | 20Bh |                                     | 28Bh |                               | 30Bh |                               | 38Bh |                               |

| 00Ch | PORTA                         | 08Ch | TRISA                          | 10Ch | LATA                           | 18Ch | ANSELA                         | 20Ch | WPUA                                | 28Ch | _                             | 30Ch | _                             | 38Ch | _                             |

| 00Dh | PORTB                         | 08Dh | TRISB                          | 10Dh | LATB                           | 18Dh | ANSELB                         | 20Dh | WPUB                                | 28Dh | —                             | 30Dh | —                             | 38Dh | _                             |

| 00Eh | —                             | 08Eh | —                              | 10Eh | —                              | 18Eh | —                              | 20Eh | —                                   | 28Eh | —                             | 30Eh | —                             | 38Eh | —                             |

| 00Fh | _                             | 08Fh | _                              | 10Fh | _                              | 18Fh | _                              | 20Fh | _                                   | 28Fh | _                             | 30Fh | —                             | 38Fh | _                             |

| 010h | _                             | 090h | —                              | 110h | —                              | 190h | —                              | 210h | —                                   | 290h | —                             | 310h | —                             | 390h | —                             |

| 011h | PIR1                          | 091h | PIE1                           | 111h | CM1CON0                        | 191h | EEADRL                         | 211h | SSP1BUF                             | 291h | CCPR1L                        | 311h | CCPR3L <sup>(1)</sup>         | 391h | _                             |

| 012h | PIR2                          | 092h | PIE2                           | 112h | CM1CON1                        | 192h | EEADRH                         | 212h | SSP1ADD                             | 292h | CCPR1H                        | 312h | CCPR3H <sup>(1)</sup>         | 392h | —                             |

| 013h | PIR3 <sup>(1)</sup>           | 093h | PIE3 <sup>(1)</sup>            | 113h | CM2CON0                        | 193h | EEDATL                         | 213h | SSP1MASK                            | 293h | CCP1CON                       | 313h | CCP3CON <sup>(1)</sup>        | 393h | —                             |

| 014h | PIR4 <sup>(1)</sup>           | 094h | PIE4 <sup>(1)</sup>            | 114h | CM2CON1                        | 194h | EEDATH                         | 214h | SSP1STAT                            | 294h | PWM1CON                       | 314h | —                             | 394h | IOCBP                         |

| 015h | TMR0                          | 095h | OPTION                         | 115h | CMOUT                          | 195h | EECON1                         | 215h | SSP1CON                             | 295h | CCP1AS                        | 315h | —                             | 395h | IOCBN                         |

| 016h | TMR1L                         | 096h | PCON                           | 116h | BORCON                         | 196h | EECON2                         | 216h | SSP1CON2                            | 296h | PSTR1CON                      | 316h | —                             | 396h | IOCBF                         |

| 017h | TMR1H                         | 097h | WDTCON                         | 117h | FVRCON                         | 197h | —                              | 217h | SSP1CON3                            | 297h | —                             | 317h | —                             | 397h | —                             |

| 018h | T1CON                         | 098h | OSCTUNE                        | 118h | DACCON0                        | 198h | _                              | 218h |                                     | 298h | CCPR2L <sup>(1)</sup>         | 318h | CCPR4L <sup>(1)</sup>         | 398h | —                             |

| 019h | T1GCON                        | 099h | OSCCON                         | 119h | DACCON1                        | 199h | RCREG                          | 219h | SSP2BUF <sup>(1)</sup>              | 299h | CCPR2H <sup>(1)</sup>         | 319h | CCPR4H <sup>(1)</sup>         | 399h | —                             |

| 01Ah | TMR2                          | 09Ah | OSCSTAT                        | 11Ah | SRCON0                         | 19Ah | TXREG                          | 21Ah | SSP2ADD <sup>(1)</sup>              | 29Ah | CCP2CON <sup>(1)</sup>        | 31Ah | CCP4CON <sup>(1)</sup>        | 39Ah | CLKRCON                       |

| 01Bh | PR2                           | 09Bh | ADRESL                         | 11Bh | SRCON1                         | 19Bh | SPBRGL                         | 21Bh | SSP2MASK <sup>(1)</sup>             | 29Bh | PWM2CON <sup>(1)</sup>        | 31Bh | —                             | 39Bh | _                             |

| 01Ch | T2CON                         | 09Ch | ADRESH                         | 11Ch | —                              | 19Ch | SPBRGH                         | 21Ch | SSP2STAT <sup>(1)</sup>             | 29Ch | CCP2AS <sup>(1)</sup>         | 31Ch | —                             | 39Ch | MDCON                         |

| 01Dh | —                             | 09Dh | ADCON0                         | 11Dh | APFCON0                        | 19Dh | RCSTA                          | 21Dh | SSP2CON <sup>(1)</sup>              | 29Dh | PSTR2CON <sup>(1)</sup>       | 31Dh | —                             | 39Dh | MDSRC                         |

| 01Eh | CPSCON0                       | 09Eh | ADCON1                         | 11Eh | APFCON1                        | 19Eh | TXSTA                          | 21Eh | SSP2CON2 <sup>(1)</sup>             | 29Eh | CCPTMRS <sup>(1)</sup>        | 31Eh | —                             | 39Eh | MDCARL                        |

| 01Fh | CPSCON1                       | 09Fh | —                              | 11Fh | _                              | 19Fh | BAUDCON                        | 21Fh | SSP2CON3 <sup>(1)</sup>             | 29Fh | _                             | 31Fh | —                             | 39Fh | MDCARH                        |

| 020h |                               | 0A0h |                                | 120h |                                | 1A0h |                                | 220h | General<br>Purpose                  | 2A0h |                               | 320h |                               | 3A0h |                               |

|      | General                       |      | General<br>Purpose<br>Register |      | General<br>Purpose<br>Register |      | General<br>Purpose<br>Register |      | Register<br>48 Bytes <sup>(1)</sup> |      | Unimplemented<br>Read as '0'  |      | Unimplemented<br>Read as '0'  |      | Unimplemented<br>Read as '0'  |

|      | Purpose                       |      | 80 Bytes                       |      | 80 Bytes                       |      | 80 Bytes <sup>(1)</sup>        |      | Unimplemented                       |      |                               |      |                               |      |                               |

| 06Fh | Register                      | 0EFh |                                | 16Fh |                                | 1EFh |                                | 26Fh | Read as '0'                         | 2EFh |                               | 36Fh |                               | 3EFh |                               |

| 070h | 96 Bytes                      | 0F0h |                                | 170h |                                | 1F0h |                                | 270h |                                     | 2F0h |                               | 370h |                               | 3F0h |                               |

|      |                               |      | Accesses<br>70h – 7Fh               |      | Accesses<br>70h – 7Fh         |      | Accesses<br>70h – 7Fh         |      | Accesses<br>70h – 7Fh         |

| 07Fh |                               | 0FFh |                                | 17Fh |                                | 1FFh |                                | 27Fh |                                     | 2FFh |                               | 37Fh |                               | 3FFh |                               |

Legend: = Unimplemented data memory locations, read as '0'

Note 1: Available only on PIC16(L)F1827.

| Address  | Name            | Bit 7                                              | Bit 6                           | Bit 5          | Bit 4        | Bit 3     | Bit 2  | Bit 1       | Bit 0  | Value on<br>POR, BOR | Value on all<br>other<br>Resets |

|----------|-----------------|----------------------------------------------------|---------------------------------|----------------|--------------|-----------|--------|-------------|--------|----------------------|---------------------------------|

| Bank 3   | 1               |                                                    |                                 |                |              |           |        |             |        |                      |                                 |

| F8Ch     | —               | Unimplement                                        | ed                              |                |              |           |        |             |        | _                    | _                               |

| <br>FE3h |                 |                                                    |                                 |                |              |           |        |             |        |                      |                                 |

| FE4h     | STATUS_<br>SHAD | —                                                  | —                               | _              | _            | —         | Z_SHAD | DC_<br>SHAD | C_SHAD | xxx                  | uuu                             |

| FE5h     | WREG_<br>SHAD   | Working Reg                                        | /orking Register Shadow         |                |              |           |        |             |        | 0000 0000            | uuuu uuuu                       |

| FE6h     | BSR_<br>SHAD    | —                                                  | — — Bank Select Register Shadow |                |              |           |        |             |        | x xxxx               | u uuuu                          |

| FE7h     | PCLATH_<br>SHAD | Program Counter Latch High Register Shadow         |                                 |                |              |           |        |             |        | -xxx xxxx            | uuuu uuuu                       |

| FE8h     | FSR0L_<br>SHAD  | Indirect Data                                      | Memory Addr                     | ess 0 Low Poi  | nter Shadow  |           |        |             |        | XXXX XXXX            | uuuu uuuu                       |

| FE9h     | FSR0H_<br>SHAD  | Indirect Data                                      | Memory Addr                     | ess 0 High Poi | inter Shadow |           |        |             |        | XXXX XXXX            | uuuu uuuu                       |

| FEAh     | FSR1L_<br>SHAD  | Indirect Data                                      | Memory Addr                     | ess 1 Low Poi  | nter Shadow  |           |        |             |        | XXXX XXXX            | uuuu uuuu                       |

| FEBh     | FSR1H_<br>SHAD  | Indirect Data Memory Address 1 High Pointer Shadow |                                 |                |              |           |        |             |        | XXXX XXXX            | uuuu uuuu                       |

| FECh     | _               | Unimplemented                                      |                                 |                |              |           |        |             |        | _                    | —                               |

| FEDh     | STKPTR          | _                                                  | _                               | _              | Current Stac | k pointer |        |             |        | 1 1111               | 1 1111                          |

| FEEh     | TOSL            | Top-of-Stack                                       | Low byte                        |                |              |           |        |             |        | xxxx xxxx            | uuuu uuuu                       |

| FEFh     | TOSH            | -                                                  | Top-of-Stack                    | High byte      |              |           |        |             |        | -xxx xxxx            | -uuu uuuu                       |

TABLE 3-6: SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)

$\label{eq:logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical$

Shaded locations are unimplemented, read as '0'.

Note 1: PIC16(L)F1827 only.

### 4.5 Device ID and Revision ID

The memory location 8006h is where the Device ID and Revision ID are stored. The upper nine bits hold the Device ID. The lower five bits hold the Revision ID. See **Section 11.5 "User ID, Device ID and Configuration Word Access"** for more information on accessing these memory locations.

Development tools, such as device programmers and debuggers, may be used to read the Device ID and Revision ID.

# 10.6 Watchdog Control Register

| U-0                          | U-0              | R/W-0/0                                                                                                                 | R/W-1/1        | R/W-0/0                   | R/W-1/1         | R/W-1/1  | R/W-0/0      |  |  |  |  |

|------------------------------|------------------|-------------------------------------------------------------------------------------------------------------------------|----------------|---------------------------|-----------------|----------|--------------|--|--|--|--|

| _                            | —                |                                                                                                                         |                | WDTPS<4:0>                |                 |          | SWDTEN       |  |  |  |  |

| bit 7                        |                  |                                                                                                                         |                |                           |                 |          | bit (        |  |  |  |  |

| logondi                      |                  |                                                                                                                         |                |                           |                 |          |              |  |  |  |  |

| <b>Legend:</b><br>R = Readat | ole bit          | W = Writable                                                                                                            | bit            | U = Unimpleme             | ented bit. read | 1 as '0' |              |  |  |  |  |

| u = Bit is un                |                  | x = Bit is unkr                                                                                                         |                | -m/n = Value at           |                 |          | other Resets |  |  |  |  |

| '1' = Bit is s               | -                | '0' = Bit is cle                                                                                                        |                |                           |                 |          |              |  |  |  |  |

|                              |                  |                                                                                                                         |                |                           |                 |          |              |  |  |  |  |

| bit 7-6                      | Unimpleme        | ented: Read as '                                                                                                        | 0'             |                           |                 |          |              |  |  |  |  |

| bit 5-1                      | WDTPS<4:         | 0>: Watchdog Ti                                                                                                         | mer Period S   | elect bits <sup>(1)</sup> |                 |          |              |  |  |  |  |

|                              | Bit Value =      | Prescale Rate                                                                                                           |                |                           |                 |          |              |  |  |  |  |

|                              | 00000 = 1        | :32 (Interval 1 m                                                                                                       | s nominal)     |                           |                 |          |              |  |  |  |  |

|                              |                  | :64 (Interval 2 m                                                                                                       | ,              |                           |                 |          |              |  |  |  |  |

|                              |                  | :128 (Interval 4 r                                                                                                      |                |                           |                 |          |              |  |  |  |  |

|                              |                  | = 1:256 (Interval 8 ms nominal)<br>= 1:512 (Interval 16 ms nominal)                                                     |                |                           |                 |          |              |  |  |  |  |

|                              |                  | 1:1024 (Interval 32 ms nominal)                                                                                         |                |                           |                 |          |              |  |  |  |  |

|                              |                  | :2048 (Interval 6                                                                                                       |                |                           |                 |          |              |  |  |  |  |

|                              |                  | :4096 (Interval 1                                                                                                       |                | ,                         |                 |          |              |  |  |  |  |

|                              |                  | :8192 (Interval 2                                                                                                       |                | ,                         |                 |          |              |  |  |  |  |

|                              |                  | :16384 (Interval                                                                                                        |                | nal)                      |                 |          |              |  |  |  |  |

|                              |                  | :32768 (Interval                                                                                                        |                | (Depart value)            |                 |          |              |  |  |  |  |

|                              |                  | :65536 (Interval<br>:131072 (2 <sup>17</sup> ) (Ir                                                                      |                |                           |                 |          |              |  |  |  |  |

|                              | 01100 = <b>1</b> | :262144 (2 <sup>18</sup> ) (Ir                                                                                          | iterval 8s nor | ninal)                    |                 |          |              |  |  |  |  |

|                              | 01110 <b>= 1</b> | :524288 (2 <sup>19</sup> ) (Ir                                                                                          | iterval 16s no | ominal)                   |                 |          |              |  |  |  |  |

|                              | 01111 <b>= 1</b> | :1048576 (2 <sup>20</sup> ) (                                                                                           | Interval 32s r | nominal)                  |                 |          |              |  |  |  |  |

|                              | 10000 <b>= 1</b> | 000 = 1:2097152 (2 <sup>21</sup> ) (Interval 64s nominal)<br>001 = 1:4194304 (2 <sup>22</sup> ) (Interval 128s nominal) |                |                           |                 |          |              |  |  |  |  |

|                              | 10001 = 1        | :4194304 (2 <sup>22</sup> ) (                                                                                           | Interval 128s  | nominal)                  |                 |          |              |  |  |  |  |

|                              | 10010 = 1        | :8388608 (2 <sup>23</sup> ) (                                                                                           | Interval 256s  | nominal)                  |                 |          |              |  |  |  |  |

|                              | 10011 = F        | Reserved. Result                                                                                                        | s in minimum   | interval (1:32)           |                 |          |              |  |  |  |  |

|                              | •                |                                                                                                                         |                |                           |                 |          |              |  |  |  |  |

|                              | •                |                                                                                                                         |                |                           |                 |          |              |  |  |  |  |

|                              | 11111 = F        | Reserved. Result                                                                                                        | s in minimum   | interval (1:32)           |                 |          |              |  |  |  |  |

| bit 0                        | SWDTEN:          | Software Enable/                                                                                                        | Disable for V  | Vatchdog Timer b          | it              |          |              |  |  |  |  |

|                              | If WDTE<1:       |                                                                                                                         |                | C C                       |                 |          |              |  |  |  |  |

|                              | This bit is ig   | nored.                                                                                                                  |                |                           |                 |          |              |  |  |  |  |

|                              | If WDTE<1        |                                                                                                                         |                |                           |                 |          |              |  |  |  |  |

|                              | 1 = WDT is       |                                                                                                                         |                |                           |                 |          |              |  |  |  |  |

|                              | 0 = WDT is       |                                                                                                                         |                |                           |                 |          |              |  |  |  |  |

|                              | If WDTE<1:       | 0 - 1x.                                                                                                                 |                |                           |                 |          |              |  |  |  |  |

# REGISTER 10-1: WDTCON: WATCHDOG TIMER CONTROL REGISTER

Note 1: Times are approximate. WDT time is based on 31 kHz LFINTOSC.

| U-1              | R/W-0/0 | R/W-0/0           | R/W-0/0 | R/W-0/0        | R/W-0/0          | R/W-0/0          | R/W-0/0     |

|------------------|---------|-------------------|---------|----------------|------------------|------------------|-------------|

| —                |         |                   |         | EEADR<14:8     | >                |                  |             |

| bit 7            |         |                   |         |                |                  |                  | bit 0       |

|                  |         |                   |         |                |                  |                  |             |

| Legend:          |         |                   |         |                |                  |                  |             |

| R = Readable b   | oit     | W = Writable      | bit     | U = Unimplen   | nented bit, read | l as '0'         |             |

| u = Bit is uncha | anged   | x = Bit is unkr   | nown    | -n/n = Value a | at POR and BO    | R/Value at all o | ther Resets |

| '1' = Bit is set |         | '0' = Bit is clea | ared    |                |                  |                  |             |

# REGISTER 11-4: EEADRH: EEPROM ADDRESS HIGH BYTE REGISTER

bit 7 Unimplemented: Read as '1'

bit 6-0 EEADR<14:8>: Specifies the Most Significant bits for program memory address or EEPROM address

#### 12.3.4 PORTB FUNCTIONS AND OUTPUT PRIORITIES

Each PORTB pin is multiplexed with other functions. The pins, their combined functions and their output priorities are shown in Table 12-5.

When multiple outputs are enabled, the actual pin control goes to the peripheral with the highest priority.

Analog input and some digital input functions are not included in the list below. These input functions can remain active when the pin is configured as an output. Certain digital input functions, such as the EUSART RX signal, override other port functions and are included in the priority list.

# TABLE 12-5: PORTB OUTPUT PRIORITY

| Pin Name | Function Priority <sup>(1)</sup>                                                                      |

|----------|-------------------------------------------------------------------------------------------------------|

| RB0      | P1A<br>RB0                                                                                            |

| RB1      | SDA1<br>RX/DT<br>RB1                                                                                  |

| RB2      | SDA2 (PIC16(L)F1827 only)<br>TX/CK<br>RX/DT<br>SDO1<br>RB2                                            |

| RB3      | MDOUT<br>CCP1/P1A<br>RB3                                                                              |

| RB4      | SCL1<br>SCK1<br>RB4                                                                                   |

| RB5      | SCL2 (PIC16(L)F1827 only)<br>TX/CK<br>SCK2 (PIC16(L)F1827 only)<br>P1B<br>RB5                         |

| RB6      | ICSPCLK (Programming)<br>T1OSI<br>P1C<br>CCP2 (PIC16(L)F1827 only)<br>P2A (PIC16(L)F1827 only)<br>RB6 |

| RB7      | ICSPDAT (Programming)<br>T1OSO<br>P1D<br>P2B (PIC16(L)F1827 only)<br>RB7                              |

Note 1: Priority listed from highest to lowest.

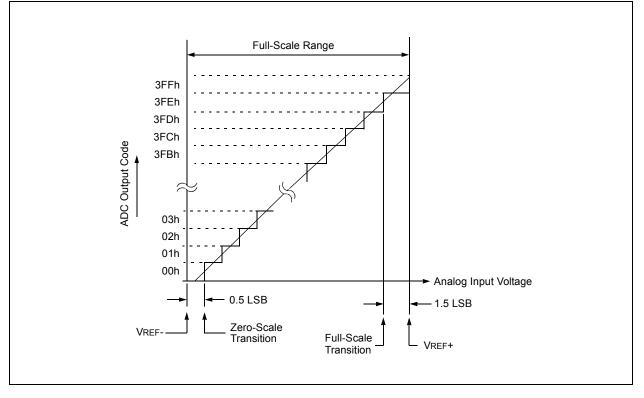

# 16.2 ADC Operation

#### 16.2.1 STARTING A CONVERSION

To enable the ADC module, the ADON bit of the ADCON0 register must be set to a '1'. Setting the GO/ DONE bit of the ADCON0 register to a '1' will start the Analog-to-Digital conversion.

| Note: | The GO/DONE bit should not be set in the |

|-------|------------------------------------------|

|       | same instruction that turns on the ADC.  |

|       | Refer to Section 16.2.6 "A/D Conver-     |

|       | sion Procedure".                         |

### 16.2.2 COMPLETION OF A CONVERSION

When the conversion is complete, the ADC module will:

- Clear the GO/DONE bit

- Set the ADIF Interrupt Flag bit

- Update the ADRESH and ADRESL registers with new conversion result

#### 16.2.3 TERMINATING A CONVERSION

If a conversion must be terminated before completion, the GO/DONE bit can be cleared in software. The ADRESH and ADRESL registers will be updated with the partially complete Analog-to-Digital conversion sample. Incomplete bits will match the last bit converted.

Note: A device Reset forces all registers to their Reset state. Thus, the ADC module is turned off and any pending conversion is terminated.

# 16.2.4 ADC OPERATION DURING SLEEP

The ADC module can operate during Sleep. This requires the ADC clock source to be set to the FRC option. When the FRC clock source is selected, the ADC waits one additional instruction before starting the conversion. This allows the SLEEP instruction to be executed, which can reduce system noise during the conversion. If the ADC interrupt is enabled, the device will wake-up from Sleep when the conversion completes. If the ADC interrupt is disabled, the ADC module is turned off after the conversion completes, although the ADON bit remains set.

When the ADC clock source is something other than FRC, a SLEEP instruction causes the present conversion to be aborted and the ADC module is turned off, although the ADON bit remains set.

# 16.2.5 SPECIAL EVENT TRIGGER

The Special Event Trigger of the CCPx/ECCPx module allows periodic ADC measurements without software intervention. When this trigger occurs, the GO/DONE bit is set by hardware and the Timer1 counter resets to zero.

#### TABLE 16-2: SPECIAL EVENT TRIGGER

| Device        | CCPx/ECCPx |

|---------------|------------|

| PIC16(L)F1826 | ECCP1      |

| PIC16(L)F1827 | CCP4       |

Using the Special Event Trigger does not assure proper ADC timing. It is the user's responsibility to ensure that the ADC timing requirements are met.

Refer to Section 24.0 "Capture/Compare/PWM Modules" for more information.

# 16.4 A/D Acquisition Requirements

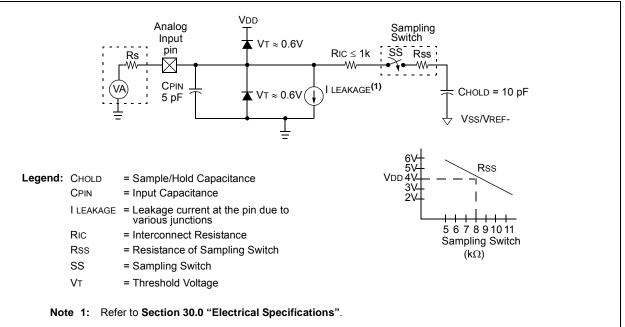

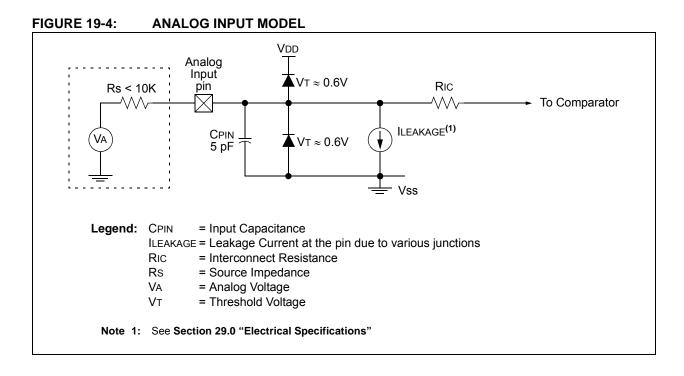

For the ADC to meet its specified accuracy, the charge holding capacitor (CHOLD) must be allowed to fully charge to the input channel voltage level. The Analog Input model is shown in Figure 16-4. The source impedance (Rs) and the internal sampling switch (Rss) impedance directly affect the time required to charge the capacitor CHOLD. The sampling switch (Rss) impedance varies over the device voltage (VDD), refer to Figure 16-4. The maximum recommended impedance for analog sources is 10 k $\Omega$ . As the

source impedance is decreased, the acquisition time may be decreased. After the analog input channel is selected (or changed), an A/D acquisition must be done before the conversion can be started. To calculate the minimum acquisition time, Equation 16-1 may be used. This equation assumes that 1/2 LSb error is used (1,024 steps for the ADC). The 1/2 LSb error is the maximum error allowed for the ADC to meet its specified resolution.

#### EQUATION 16-1: ACQUISITION TIME EXAMPLE

Assumptions: Temperature =

$$50^{\circ}C$$

and external impedance of  $10k\Omega 5.0V$  VDD

$TACQ = Amplifier Settling Time + Hold Capacitor Charging Time + Temperature Coefficient$

$= TAMP + TC + TCOFF$

$= 2\mu s + TC + [(Temperature - 25^{\circ}C)(0.05\mu s/^{\circ}C)]$

*The value for TC can be approximated with the following equations:*

$$V_{APPLIED}\left(1 - \frac{1}{(2^{n+1}) - 1}\right) = V_{CHOLD} \qquad ;[1] V_{CHOLD} charged to within 1/2 lsb$$

$$V_{APPLIED}\left(1 - e^{\frac{-Tc}{RC}}\right) = V_{CHOLD} \qquad ;[2] V_{CHOLD} charge response to V_{APPLIED} \\V_{APPLIED}\left(1 - e^{\frac{-Tc}{RC}}\right) = V_{APPLIED}\left(1 - \frac{1}{(2^{n+1}) - 1}\right) \quad ;combining [1] and [2]$$

*Note:* Where n = number of bits of the ADC.

Solving for TC:

$$Tc = -CHOLD(RIC + RSS + RS) ln(1/511)$$

= -10pF(1k\Omega + 7k\Omega + 10k\Omega) ln(0.001957)

= 1.12\mus

Therefore:

$$TACQ = 2\mu s + 1.12\mu s + [(50^{\circ}C - 25^{\circ}C)(0.05\mu s/^{\circ}C)]$$

= 4.42\mu s

**Note 1:** The reference voltage (VREF) has no effect on the equation, since it cancels itself out.

- 2: The charge holding capacitor (CHOLD) is not discharged after each conversion.

- **3:** The maximum recommended impedance for analog sources is  $10 \text{ k}\Omega$ . This is required to meet the pin leakage specification.

### FIGURE 16-4: ANALOG INPUT MODEL

# 20.2 Option and Timer0 Control Register

### REGISTER 20-1: OPTION\_REG: OPTION REGISTER

| R/W-1/1                                                                            | R/W-1/1  | <b>R/W-</b> 1                                                                       | I/1 I                  | R/W-1/1     | R/W-1/1        | R/W-1/1        | R/W       | /-1/1      | R/W-1/1    |  |

|------------------------------------------------------------------------------------|----------|-------------------------------------------------------------------------------------|------------------------|-------------|----------------|----------------|-----------|------------|------------|--|

| WPUEN                                                                              | INTEDG   | TMR0                                                                                | CS 1                   | MR0SE       | PSA            |                | PS<2      | 2:0>       |            |  |

| bit 7                                                                              |          |                                                                                     |                        |             |                |                |           |            | bit (      |  |

| <u> </u>                                                                           |          |                                                                                     |                        |             |                |                |           |            |            |  |

| Legend:                                                                            |          |                                                                                     |                        |             |                |                |           |            |            |  |

| R = Readable                                                                       |          | W = Wri                                                                             |                        | -           | -              | emented bit, r |           |            |            |  |

| u = Bit is uncl<br>'1' = Bit is set                                                | 0        |                                                                                     | s unknow<br>is cleared |             | -n/n = value   | at POR and     | BOR/value | at all otr | ier Resets |  |

|                                                                                    |          | 0 <b>–</b> Dil                                                                      | is cleared             | 1           |                |                |           |            |            |  |

| bit 7                                                                              | WPUEN: V | Veak Pull-up                                                                        | Enable                 | bit         |                |                |           |            |            |  |

|                                                                                    |          |                                                                                     |                        |             | MCLR, if it is |                |           |            |            |  |

|                                                                                    |          |                                                                                     |                        |             | al WPUx latc   | h values       |           |            |            |  |

| bit 6                                                                              |          | nterrupt Edg                                                                        |                        |             |                |                |           |            |            |  |

|                                                                                    |          | 1 = Interrupt on rising edge of INT pin<br>0 = Interrupt on falling edge of INT pin |                        |             |                |                |           |            |            |  |

| bit 5                                                                              |          |                                                                                     | •                      |             |                |                |           |            |            |  |

| bit 5 <b>TMR0CS:</b> Timer0 Clock Source Select bit<br>1 = Transition on T0CKI pin |          |                                                                                     |                        |             |                |                |           |            |            |  |

| 0 = Internal instruction cycle clock (Fosc/4)                                      |          |                                                                                     |                        |             |                |                |           |            |            |  |

| bit 4                                                                              | TMR0SE:  | Timer0 Sour                                                                         | ce Edge                | Select bit  |                |                |           |            |            |  |

|                                                                                    |          | ent on high-                                                                        |                        |             |                |                |           |            |            |  |

| 1.11.0                                                                             |          | ient on low-to                                                                      |                        | insition on | TOCKI pin      |                |           |            |            |  |

| bit 3                                                                              |          | caler Assign<br>aler is not as                                                      |                        | the Timer   | 0 modulo       |                |           |            |            |  |

|                                                                                    |          | aler is assign                                                                      |                        |             |                |                |           |            |            |  |

| bit 2-0                                                                            | PS<2:0>: | Prescaler Ra                                                                        | ate Select             | t bits      |                |                |           |            |            |  |

|                                                                                    | E        | Bit Value Ti                                                                        | mer0 Rate              | e           |                |                |           |            |            |  |

|                                                                                    | -        | 000                                                                                 | 1:2                    | _           |                |                |           |            |            |  |

|                                                                                    |          | 001                                                                                 | 1:4                    |             |                |                |           |            |            |  |

|                                                                                    |          | 010<br>011                                                                          | 1:8<br>1:16            |             |                |                |           |            |            |  |

|                                                                                    |          | 100                                                                                 | 1:32                   |             |                |                |           |            |            |  |

|                                                                                    |          | 101                                                                                 | 1:64                   |             |                |                |           |            |            |  |

|                                                                                    |          | 110                                                                                 | 1:128                  |             |                |                |           |            |            |  |

|                                                                                    |          | 111                                                                                 | 1 : 256                |             |                |                |           |            |            |  |

| TABLE 20-1                                                                         | : SUMMA  | RY OF RE                                                                            | GISTER                 | S ASSO      | CIATED WI      | TH TIMER0      |           |            |            |  |

| Name                                                                               | Bit 7    | Bit 6                                                                               | Bit 5                  | Bit 4       | Bit 3          | Bit 2          | Bit 1     | Bit 0      | Register   |  |

| Name       | Bit 7                  | Bit 6  | Bit 5  | Bit 4  | Bit 3   | Bit 2   | Bit 1  | Bit 0  | Register<br>on Page |

|------------|------------------------|--------|--------|--------|---------|---------|--------|--------|---------------------|

| CPSCON0    | CPSON                  | —      | —      | —      | CPSRNG1 | CPSRNG0 | CPSOUT | T0XCS  | 318                 |

| INTCON     | GIE                    | PEIE   | TMR0IE | INTE   | IOCIE   | TMR0IF  | INTF   | IOCIF  | 86                  |

| OPTION_REG | WPUEN                  | INTEDG | TMR0CS | TMR0SE | PSA     | PS2     | PS1    | PS0    | 177                 |

| TMR0       | Timer0 Module Register |        |        |        |         |         |        |        | 173*                |

| TRISA      | TRISA7                 | TRISA6 | TRISA5 | TRISA4 | TRISA3  | TRISA2  | TRISA1 | TRISA0 | 122                 |

**Legend:** — = Unimplemented locations, read as '0'. Shaded cells are not used by the Timer0 module.

\* Page provides register information.

### 24.4.6.1 Steering Synchronization

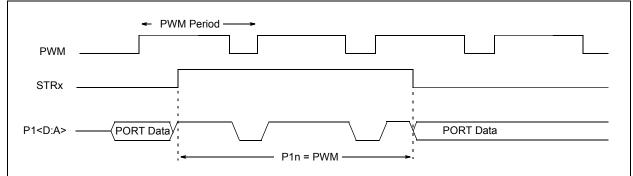

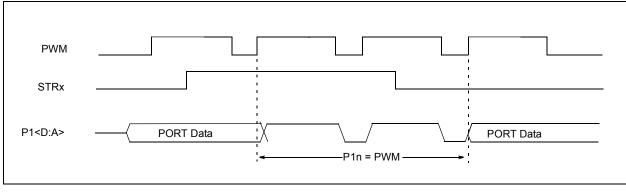

The STRxSYNC bit of the PSTRxCON register gives the user two selections of when the steering event will happen. When the STRxSYNC bit is '0', the steering event will happen at the end of the instruction that writes to the PSTRxCON register. In this case, the output signal at the Px<D:A> pins may be an incomplete PWM waveform. This operation is useful when the user firmware needs to immediately remove a PWM signal from the pin.

When the STRxSYNC bit is '1', the effective steering update will happen at the beginning of the next PWM period. In this case, steering on/off the PWM output will always produce a complete PWM waveform.

Figures 24-19 and 24-20 illustrate the timing diagrams of the PWM steering depending on the STRxSYNC setting.

#### 24.4.7 START-UP CONSIDERATIONS

When any PWM mode is used, the application hardware must use the proper external pull-up and/or pull-down resistors on the PWM output pins.

The CCPxM<1:0> bits of the CCPxCON register allow the user to choose whether the PWM output signals are active-high or active-low for each pair of PWM output pins (PxA/PxC and PxB/PxD). The PWM output polarities must be selected before the PWM pin output drivers are enabled. Changing the polarity configuration while the PWM pin output drivers are enable is not recommended since it may result in damage to the application circuits.

The PxA, PxB, PxC and PxD output latches may not be in the proper states when the PWM module is initialized. Enabling the PWM pin output drivers at the same time as the Enhanced PWM modes may cause damage to the application circuit. The Enhanced PWM modes must be enabled in the proper Output mode and complete a full PWM cycle before enabling the PWM pin output drivers. The completion of a full PWM cycle is indicated by the TMRxIF bit of the PIRx register being set as the second PWM period begins.

Note: When the microcontroller is released from Reset, all of the I/O pins are in the high-impedance state. The external circuits must keep the power switch devices in the Off state until the microcontroller drives the I/O pins with the proper signal levels or activates the PWM output(s).

# 24.4.8 ALTERNATE PIN LOCATIONS

This module incorporates I/O pins that can be moved to other locations with the use of the alternate pin function registers, APFCON0 and APFCON1. To determine which pins can be moved and what their default locations are upon a reset, see **Section 12.1 "Alternate Pin Function"** for more information.

### FIGURE 24-19: EXAMPLE OF STEERING EVENT AT END OF INSTRUCTION (STRxSYNC = 0)

# FIGURE 24-20: EXAMPLE OF STEERING EVENT AT BEGINNING OF INSTRUCTION (STRxSYNC = 1)

#### 25.2.6 SPI OPERATION IN SLEEP MODE

In SPI Master mode, module clocks may be operating at a different speed than when in full power mode; in the case of the Sleep mode, all clocks are halted.

Special care must be taken by the user when the MSSPx clock is much faster than the system clock.

In Slave mode, when MSSPx interrupts are enabled, after the master completes sending data, an MSSPx interrupt will wake the controller from Sleep.

If an exit from Sleep mode is not desired, MSSPx interrupts should be disabled.

In SPI Master mode, when the Sleep mode is selected, all module clocks are halted and the transmission/reception will remain in that state until the device wakes. After the device returns to Run mode, the module will resume transmitting and receiving data.

In SPI Slave mode, the SPI Transmit/Receive Shift register operates asynchronously to the device. This allows the device to be placed in Sleep mode and data to be shifted into the SPI Transmit/Receive Shift register. When all 8 bits have been received, the MSSPx interrupt flag bit will be set and if enabled, will wake the device.

| Name     | Bit 7       | Bit 6           | Bit 5         | Bit 4                 | Bit 3                  | Bit 2  | Bit 1  | Bit 0   | Register<br>on Page |  |

|----------|-------------|-----------------|---------------|-----------------------|------------------------|--------|--------|---------|---------------------|--|

| APFCON0  | RXDTSEL     | SDO1SEL         | SS1SEL        | P2BSEL <sup>(1)</sup> | CCP2SEL <sup>(1)</sup> | P1DSEL | P1CSEL | CCP1SEL | 119                 |  |

| ANSELA   | —           | _               | -             | ANSA4                 | ANSA3                  | ANSA2  | ANSA1  | ANSA0   | 123                 |  |

| ANSELB   | ANSB7       | ANSB6           | ANSB5         | ANSB4                 | ANSB3                  | ANSB2  | ANSB1  | —       | 128                 |  |

| INTCON   | GIE         | PEIE            | TMR0IE        | INTE                  | IOCIE                  | TMR0IF | INTF   | IOCIF   | 86                  |  |

| PIE1     | TMR1GIE     | ADIE            | RCIE          | TXIE                  | SSP1IE                 | CCP1IE | TMR2IE | TMR1IE  | 87                  |  |

| PIR1     | TMR1GIF     | ADIF            | RCIF          | TXIF                  | SSP1IF                 | CCP1IF | TMR2IF | TMR1IF  | 91                  |  |

| SSPxBUF  | Synchronous | s Serial Port F | Receive Buffe | r/Transmit Re         | egister                |        |        |         | 235*                |  |

| SSPxCON1 | WCOL        | SSPxOV          | SSPxEN        | CKP                   | SSPxM3                 | SSPxM2 | SSPxM1 | SSPxM0  | 280                 |  |

| SSPxCON3 | ACKTIM      | PCIE            | SCIE          | BOEN                  | SDAHT                  | SBCDE  | AHEN   | DHEN    | 282                 |  |

| SSPxSTAT | SMP         | CKE             | D/A           | Р                     | S                      | R/W    | UA     | BF      | 279                 |  |

| TRISA    | TRISA7      | TRISA6          | TRISA5        | TRISA4                | TRISA3                 | TRISA2 | TRISA1 | TRISA0  | 122                 |  |

| TRISB    | TRISB7      | TRISB6          | TRISB5        | TRISB4                | TRISB3                 | TRISB2 | TRISB1 | TRISB0  | 127                 |  |

TABLE 25-1: SUMMARY OF REGISTERS ASSOCIATED WITH SPI OPERATION

Legend: — = Unimplemented location, read as '0'. Shaded cells are not used by the MSSPx in SPI mode.

\* Page provides register information.

Note 1: PIC16(L)F1827 only.

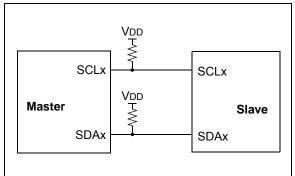

# 25.3 I<sup>2</sup>C MODE OVERVIEW

The Inter-Integrated Circuit Bus (I<sup>2</sup>C) is a multi-master serial data communication bus. Devices communicate in a master/slave environment where the master devices initiate the communication. A Slave device is controlled through addressing.

The I<sup>2</sup>C bus specifies two signal connections:

- · Serial Clock (SCLx)

- Serial Data (SDAx)

Figure 25-11 shows the block diagram of the MSSPx module when operating in  $I^2C$  Mode.

Both the SCLx and SDAx connections are bidirectional open-drain lines, each requiring pull-up resistors for the supply voltage. Pulling the line to ground is considered a logical zero and letting the line float is considered a logical one.

Figure 25-11 shows a typical connection between two processors configured as master and slave devices.

The  $I^2C$  bus can operate with one or more master devices and one or more slave devices.

There are four potential modes of operation for a given device:

- Master Transmit mode

(master is transmitting data to a slave)

- Master Receive mode

(master is receiving data from a slave)

- Slave Transmit mode (slave is transmitting data to a master)

- Slave Receive mode (slave is receiving data from the master)

To begin communication, a master device starts out in Master Transmit mode. The master device sends out a Start bit followed by the address byte of the slave it intends to communicate with. This is followed by a single Read/Write bit, which determines whether the master intends to transmit to or receive data from the slave device.

If the requested slave exists on the bus, it will respond with an Acknowledge bit, otherwise known as an ACK. The master then continues in either Transmit mode or Receive mode and the slave continues in the complement, either in Receive mode or Transmit mode, respectively.

A Start bit is indicated by a high-to-low transition of the SDAx line while the SCLx line is held high. Address and data bytes are sent out, Most Significant bit (MSb) first. The Read/Write bit is sent out as a logical one when the master intends to read data from the slave, and is sent out as a logical zero when it intends to write data to the slave.

#### FIGURE 25-11: I<sup>2</sup>C MASTER/ SLAVE CONNECTION

The Acknowledge bit  $(\overline{ACK})$  is an active-low signal, which holds the SDAx line low to indicate to the transmitter that the slave device has received the transmitted data and is ready to receive more.

The transition of a data bit is always performed while the SCLx line is held low. Transitions that occur while the SCLx line is held high are used to indicate Start and Stop bits.

If the master intends to write to the slave, then it repeatedly sends out a byte of data, with the slave responding after each byte with an  $\overrightarrow{ACK}$  bit. In this example, the master device is in Master Transmit mode and the slave is in Slave Receive mode.

If the master intends to read from the slave, then it repeatedly receives a byte of data from the slave, and responds after each byte with an ACK bit. In this example, the master device is in Master Receive mode and the slave is Slave Transmit mode.

On the last byte of data communicated, the master device may end the transmission by sending a Stop bit. If the master device is in Receive mode, it sends the Stop bit in place of the last ACK bit. A Stop bit is indicated by a low-to-high transition of the SDAx line while the SCLx line is held high.

In some cases, the master may want to maintain control of the bus and re-initiate another transmission. If so, the master device may send another Start bit in place of the Stop bit or last ACK bit when it is in receive mode.

The I<sup>2</sup>C bus specifies three message protocols;

- Single message where a master writes data to a slave.

- Single message where a master reads data from a slave.

- Combined message where a master initiates a minimum of two writes, or two reads, or a combination of writes and reads, to one or more slaves.

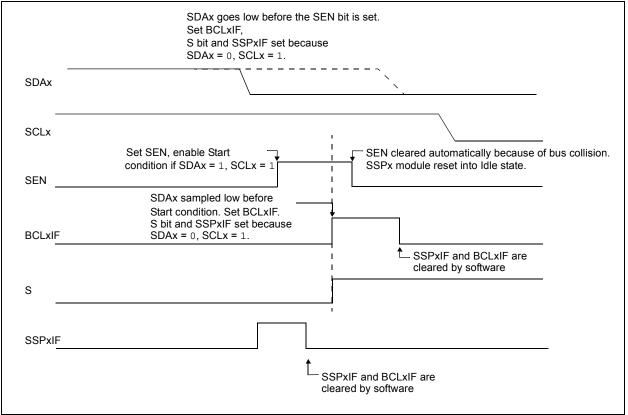

# 25.6.13.1 Bus Collision During a Start Condition

During a Start condition, a bus collision occurs if:

- a) SDAx or SCLx are sampled low at the beginning of the Start condition (Figure 25-32).

- b) SCLx is sampled low before SDAx is asserted low (Figure 25-33).

During a Start condition, both the SDAx and the SCLx pins are monitored.

If the SDAx pin is already low, or the SCLx pin is already low, then all of the following occur:

- · the Start condition is aborted,

- the BCLxIF flag is set and

- the MSSPx module is reset to its Idle state (Figure 25-32).

The Start condition begins with the SDAx and SCLx pins deasserted. When the SDAx pin is sampled high, the Baud Rate Generator is loaded and counts down. If the SCLx pin is sampled low while SDAx is high, a bus collision occurs because it is assumed that another master is attempting to drive a data '1' during the Start condition.

If the SDAx pin is sampled low during this count, the BRG is reset and the SDAx line is asserted early (Figure 25-34). If, however, a '1' is sampled on the SDAx pin, the SDAx pin is asserted low at the end of the BRG count. The Baud Rate Generator is then reloaded and counts down to zero; if the SCLx pin is sampled as '0' during this time, a bus collision does not occur. At the end of the BRG count, the SCLx pin is asserted low.

Note: The reason that bus collision is not a factor during a Start condition is that no two bus masters can assert a Start condition at the exact same time. Therefore, one master will always assert SDAx before the other. This condition does not cause a bus collision because the two masters must be allowed to arbitrate the first address following the Start condition. If the address is the same, arbitration must be allowed to continue into the data portion, Repeated Start or Stop conditions.

#### FIGURE 25-33: BUS COLLISION DURING START CONDITION (SDAX ONLY)

# 26.4 EUSART Synchronous Mode

Synchronous serial communications are typically used in systems with a single master and one or more slaves. The master device contains the necessary circuitry for baud rate generation and supplies the clock for all devices in the system. Slave devices can take advantage of the master clock by eliminating the internal clock generation circuitry.

There are two signal lines in Synchronous mode: a bidirectional data line and a clock line. Slaves use the external clock supplied by the master to shift the serial data into and out of their respective receive and transmit shift registers. Since the data line is bidirectional, synchronous operation is half-duplex only. Half-duplex refers to the fact that master and slave devices can receive and transmit data but not both simultaneously. The EUSART can operate as either a master or slave device.

Start and Stop bits are not used in synchronous transmissions.

#### 26.4.1 SYNCHRONOUS MASTER MODE

The following bits are used to configure the EUSART for Synchronous Master operation:

- SYNC = 1

- CSRC = 1

- SREN = 0 (for transmit); SREN = 1 (for receive)

- CREN = 0 (for transmit); CREN = 1 (for receive)

- SPEN = 1

Setting the SYNC bit of the TXSTA register configures the device for synchronous operation. Setting the CSRC bit of the TXSTA register configures the device as a master. Clearing the SREN and CREN bits of the RCSTA register ensures that the device is in the Transmit mode, otherwise the device will be configured to receive. Setting the SPEN bit of the RCSTA register enables the EUSART.

#### 26.4.1.1 Master Clock

Synchronous data transfers use a separate clock line, which is synchronous with the data. A device configured as a master transmits the clock on the TX/CK line. The TX/CK pin output driver is automatically enabled when the EUSART is configured for synchronous transmit or receive operation. Serial data bits change on the leading edge to ensure they are valid at the trailing edge of each clock. One clock cycle is generated for each data bit. Only as many clock cycles are generated as there are data bits.

#### 26.4.1.2 Clock Polarity

A clock polarity option is provided for Microwire compatibility. Clock polarity is selected with the SCKP bit of the BAUDCON register. Setting the SCKP bit sets the clock Idle state as high. When the SCKP bit is set, the data changes on the falling edge of each clock. Clearing the SCKP bit sets the Idle state as low. When the SCKP bit is cleared, the data changes on the rising edge of each clock.

#### 26.4.1.3 Synchronous Master Transmission

Data is transferred out of the device on the RX/DT pin. The RX/DT and TX/CK pin output drivers are automatically enabled when the EUSART is configured for synchronous master transmit operation.

A transmission is initiated by writing a character to the TXREG register. If the TSR still contains all or part of a previous character the new character data is held in the TXREG until the last bit of the previous character has been transmitted. If this is the first character, or the previous character has been completely flushed from the TSR, the data in the TXREG is immediately transferred to the TSR. The transmission of the character commences immediately following the transfer of the data to the TSR from the TXREG.

Each data bit changes on the leading edge of the master clock and remains valid until the subsequent leading clock edge.

| Note: | The TSR register is not mapped in data      |

|-------|---------------------------------------------|

|       | memory, so it is not available to the user. |

- 26.4.1.4 Synchronous Master Transmission Set-up:

- Initialize the SPBRGH, SPBRGL register pair and the BRGH and BRG16 bits to achieve the desired baud rate (see Section 26.3 "EUSART Baud Rate Generator (BRG)").

- 2. Enable the synchronous master serial port by setting bits SYNC, SPEN and CSRC.

- 3. Disable Receive mode by clearing bits SREN and CREN.

- 4. Enable Transmit mode by setting the TXEN bit.

- 5. If 9-bit transmission is desired, set the TX9 bit.

- 6. If interrupts are desired, set the TXIE bit of the PIE1 register and the GIE and PEIE bits of the INTCON register.

- 7. If 9-bit transmission is selected, the ninth bit should be loaded in the TX9D bit.

- 8. Start transmission by loading data to the TXREG register.

# 26.4.2.3 EUSART Synchronous Slave Reception

The operation of the Synchronous Master and Slave modes is identical (Section 26.4.1.5 "Synchronous Master Reception"), with the following exceptions:

- Sleep

- CREN bit is always set, therefore the receiver is

never Idle

- SREN bit, which is a "don't care" in Slave mode

A character may be received while in Sleep mode by setting the CREN bit prior to entering Sleep. Once the word is received, the RSR register will transfer the data to the RCREG register. If the RCIE enable bit is set, the interrupt generated will wake the device from Sleep and execute the next instruction. If the GIE bit is also set, the program will branch to the interrupt vector.

- 26.4.2.4 Synchronous Slave Reception Set-up:

- 1. Set the SYNC and SPEN bits and clear the CSRC bit.

- 2. Clear the ANSEL bit for both the CK and DT pins (if applicable).

- 3. If interrupts are desired, set the RCIE bit of the PIE1 register and the GIE and PEIE bits of the INTCON register.

- 4. If 9-bit reception is desired, set the RX9 bit.

- 5. Set the CREN bit to enable reception.

- The RCIF bit will be set when reception is complete. An interrupt will be generated if the RCIE bit was set.

- 7. If 9-bit mode is enabled, retrieve the Most Significant bit from the RX9D bit of the RCSTA register.

- 8. Retrieve the 8 Least Significant bits from the receive FIFO by reading the RCREG register.

- 9. If an overrun error occurs, clear the error by either clearing the CREN bit of the RCSTA register or by clearing the SPEN bit which resets the EUSART.

| Name    | Bit 7                        | Bit 6   | Bit 5  | Bit 4                 | Bit 3                  | Bit 2  | Bit 1  | Bit 0   | Register<br>on Page |

|---------|------------------------------|---------|--------|-----------------------|------------------------|--------|--------|---------|---------------------|

| APFCON0 | RXDTSEL                      | SDO1SEL | SS1SEL | P2BSEL <sup>(1)</sup> | CCP2SEL <sup>(1)</sup> | P1DSEL | P1CSEL | CCP1SEL | 119                 |

| APFCON1 | —                            | —       | _      | —                     | —                      |        | _      | TXCKSEL | 119                 |

| BAUDCON | ABDOVF                       | RCIDL   | —      | SCKP                  | BRG16                  | _      | WUE    | ABDEN   | 296                 |

| INTCON  | GIE                          | PEIE    | TMR0IE | INTE                  | IOCIE                  | TMR0IF | INTF   | IOCIF   | 86                  |

| PIE1    | TMR1GIE                      | ADIE    | RCIE   | TXIE                  | SSPIE                  | CCP1IE | TMR2IE | TMR1IE  | 87                  |

| PIR1    | TMR1GIF                      | ADIF    | RCIF   | TXIF                  | SSPIF                  | CCP1IF | TMR2IF | TMR1IF  | 91                  |

| RCREG   | EUSART Receive Data Register |         |        |                       |                        |        | 290*   |         |                     |

| RCSTA   | SPEN                         | RX9     | SREN   | CREN                  | ADDEN                  | FERR   | OERR   | RX9D    | 295                 |

| TRISB   | TRISB7                       | TRISB6  | TRISB5 | TRISB4                | TRISB3                 | TRISB2 | TRISB1 | TRISB0  | 127                 |

| TXSTA   | CSRC                         | TX9     | TXEN   | SYNC                  | SENDB                  | BRGH   | TRMT   | TX9D    | 294                 |

# TABLE 26-10: SUMMARY OF REGISTERS ASSOCIATED WITH SYNCHRONOUS SLAVE RECEPTION

Legend: — = unimplemented location, read as '0'. Shaded cells are not used for Synchronous Slave Reception.

\* Page provides register information.

Note 1: PIC16(L)F1827 only.

# 32.11 PICkit 2 Development Programmer/Debugger and PICkit 2 Debug Express

The PICkit<sup>™</sup> 2 Development Programmer/Debugger is a low-cost development tool with an easy to use interface for programming and debugging Microchip's Flash families of microcontrollers. The full featured Windows® programming interface supports baseline (PIC10F, PIC12F5xx, PIC16F5xx), midrange (PIC12F6xx, PIC16F), PIC18F, PIC24, dsPIC30, dsPIC33, and PIC32 families of 8-bit, 16-bit, and 32-bit microcontrollers, and many Microchip Serial EEPROM products. With Microchip's powerful MPLAB Integrated Development Environment (IDE) the PICkit<sup>™</sup> 2 enables in-circuit debugging on most PIC<sup>®</sup> microcontrollers. In-Circuit-Debugging runs, halts and single steps the program while the PIC microcontroller is embedded in the application. When halted at a breakpoint, the file registers can be examined and modified.

The PICkit 2 Debug Express include the PICkit 2, demo board and microcontroller, hookup cables and CDROM with user's guide, lessons, tutorial, compiler and MPLAB IDE software.

### 32.12 MPLAB PM3 Device Programmer

The MPLAB PM3 Device Programmer is a universal, CE compliant device programmer with programmable voltage verification at VDDMIN and VDDMAX for maximum reliability. It features a large LCD display (128 x 64) for menus and error messages and a modular, detachable socket assembly to support various package types. The ICSP™ cable assembly is included as a standard item. In Stand-Alone mode, the MPLAB PM3 Device Programmer can read, verify and program PIC devices without a PC connection. It can also set code protection in this mode. The MPLAB PM3 connects to the host PC via an RS-232 or USB cable. The MPLAB PM3 has high-speed communications and optimized algorithms for quick programming of large memory devices and incorporates an MMC card for file storage and data applications.

# 32.13 Demonstration/Development Boards, Evaluation Kits, and Starter Kits

A wide variety of demonstration, development and evaluation boards for various PIC MCUs and dsPIC DSCs allows quick application development on fully functional systems. Most boards include prototyping areas for adding custom circuitry and provide application firmware and source code for examination and modification.

The boards support a variety of features, including LEDs, temperature sensors, switches, speakers, RS-232 interfaces, LCD displays, potentiometers and additional EEPROM memory.

The demonstration and development boards can be used in teaching environments, for prototyping custom circuits and for learning about various microcontroller applications.

In addition to the PICDEM<sup>™</sup> and dsPICDEM<sup>™</sup> demonstration/development board series of circuits, Microchip has a line of evaluation kits and demonstration software for analog filter design, KEELOQ<sup>®</sup> security ICs, CAN, IrDA<sup>®</sup>, PowerSmart battery management, SEEVAL<sup>®</sup> evaluation system, Sigma-Delta ADC, flow rate sensing, plus many more.

Also available are starter kits that contain everything needed to experience the specified device. This usually includes a single application and debug capability, all on one board.

Check the Microchip web page (www.microchip.com) for the complete list of demonstration, development and evaluation kits.

# 33.0 PACKAGING INFORMATION

# 33.1 Package Marking Information

#### 18-Lead PDIP

#### 18-Lead SOIC (.300")

#### 20-Lead SSOP

#### 28-Lead QFN/UQFN

# Example

# Example

### Example

| Legend | : XXX<br>Y<br>YY<br>WW<br>NNN<br>@3<br>*                                                                                                                                                                      | Customer-specific information<br>Year code (last digit of calendar year)<br>Year code (last 2 digits of calendar year)<br>Week code (week of January 1 is week '01')<br>Alphanumeric traceability code<br>Pb-free JEDEC designator for Matte Tin (Sn)<br>This package is Pb-free. The Pb-free JEDEC designator ((e3))<br>can be found on the outer packaging for this package. |  |  |  |  |

|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Note:  | In the event the full Microchip part number cannot be marked on one line, it will<br>be carried over to the next line, thus limiting the number of available<br>characters for customer-specific information. |                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

\* Standard PICmicro<sup>®</sup> device marking consists of Microchip part number, year code, week code and traceability code. For PICmicro device marking beyond this, certain price adders apply. Please check with your Microchip Sales Office. For QTP devices, any special marking adders are included in QTP price.