Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 32MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 16                                                                        |

| Program Memory Size        | 7KB (4K x 14)                                                             |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 256 x 8                                                                   |

| RAM Size                   | 384 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                               |

| Data Converters            | A/D 12x10b                                                                |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 18-SOIC (0.295", 7.50mm Width)                                            |

| Supplier Device Package    | 18-SOIC                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f1827-e-so |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com** or fax the **Reader Response Form** in the back of this data sheet to (480) 792-4150. We welcome your feedback.

### **Most Current Data Sheet**

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

### **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

## 1.0 DEVICE OVERVIEW

The PIC16(L)F1826/27 are described within this data sheet. They are available in 18/20/28-pin packages. Figure 1-1 shows a block diagram of the PIC16(L)F1826/27 devices. Table 1-2 shows the pinout descriptions.

Reference Table 1-1 for peripherals available per device.

TABLE 1-1:DEVICE PERIPHERALSUMMARY

| Peripheral               |             | PIC16F/LF1826 | PIC16(L)F1827 |

|--------------------------|-------------|---------------|---------------|

| ADC                      |             | ٠             | •             |

| Capacitive Sensing Mod   | dule        | ٠             | •             |

| Digital-to-Analog Conve  | rter (DAC)  | •             | •             |

| Digital Signal Modulator | (DSM)       | •             | •             |

| EUSART                   |             | ٠             | •             |

| Fixed Voltage Reference  | e (FVR)     | ٠             | •             |

| Reference Clock Module   | e           | ٠             | •             |

| SR Latch                 |             | •             | •             |

| Capture/Compare/PWM      | Modules     |               |               |

|                          | ECCP1       | •             | •             |

|                          | ECCP2       |               | •             |

|                          | CCP3        |               | •             |

|                          | CCP4        |               | •             |

| Comparators              |             |               |               |

|                          | C1          | •             | •             |

|                          | C2          | •             | •             |

| Master Synchronous Se    | erial Ports |               |               |

|                          | MSSP1       | •             | •             |

|                          | MSSP2       |               | •             |

| Timers                   |             |               |               |

|                          | Timer0      | •             | •             |

|                          | Timer1      | •             | •             |

|                          | Timer2      | •             | •             |

|                          | Timer4      |               | •             |

|                          | Timer6      |               |               |

| Name                                                                                                                      | Function | nction Input<br>Type |      | t Description                                                                                     |  |  |

|---------------------------------------------------------------------------------------------------------------------------|----------|----------------------|------|---------------------------------------------------------------------------------------------------|--|--|

| RB3/AN9/CPS9/MDOUT/<br>CCP1 <sup>(1,3)</sup> /P1A <sup>(1,3)</sup>                                                        | RB3      | TTL                  | CMOS | General purpose I/O. Individually controlled interrupt-on-change<br>Individually enabled pull-up. |  |  |

|                                                                                                                           | AN9      | AN                   | _    | A/D Channel 9 input.                                                                              |  |  |

|                                                                                                                           | CPS9     | AN                   | _    | Capacitive sensing input 9.                                                                       |  |  |

|                                                                                                                           | MDOUT    | _                    | CMOS | Modulator output.                                                                                 |  |  |

|                                                                                                                           | CCP1     | ST                   | CMOS | Capture/Compare/PWM1.                                                                             |  |  |

|                                                                                                                           | P1A      | _                    | CMOS | PWM output.                                                                                       |  |  |

| RB4/AN8/CPS8/SCL1/SCK1/<br>MDCIN2                                                                                         | RB4      | TTL                  | CMOS | General purpose I/O. Individually controlled interrupt-on-change<br>Individually enabled pull-up. |  |  |

|                                                                                                                           | AN8      | AN                   | _    | A/D Channel 8 input.                                                                              |  |  |

|                                                                                                                           | CPS8     | AN                   | _    | Capacitive sensing input 8.                                                                       |  |  |

|                                                                                                                           | SCL1     | I <sup>2</sup> C™    | OD   | I <sup>2</sup> C™ clock 1.                                                                        |  |  |

|                                                                                                                           | SCK1     | ST                   | CMOS | SPI clock 1.                                                                                      |  |  |

|                                                                                                                           | MDCIN2   | ST                   | —    | Modulator Carrier Input 2.                                                                        |  |  |

| RB5/AN7/CPS7/P1B/TX <sup>(1)</sup> /CK <sup>(1)</sup> /<br>SCL2 <sup>(2)</sup> /SCK2 <sup>(2)</sup> /SS1 <sup>(1,3)</sup> | RB5      | TTL                  | CMOS | General purpose I/O. Individually controlled interrupt-on-change<br>Individually enabled pull-up. |  |  |

|                                                                                                                           | AN7      | AN                   | —    | A/D Channel 7 input.                                                                              |  |  |

|                                                                                                                           | CPS7     | AN                   | —    | Capacitive sensing input 7.                                                                       |  |  |

|                                                                                                                           | P1B      | _                    | CMOS | PWM output.                                                                                       |  |  |

|                                                                                                                           | TX       | _                    | CMOS | USART asynchronous transmit.                                                                      |  |  |

|                                                                                                                           | СК       | ST                   | CMOS | USART synchronous clock.                                                                          |  |  |

|                                                                                                                           | SCL2     | I <sup>2</sup> C™    | OD   | I <sup>2</sup> C <sup>™</sup> clock 2.                                                            |  |  |

|                                                                                                                           | SCK2     | ST                   | CMOS | SPI clock 2.                                                                                      |  |  |

|                                                                                                                           | SS1      | ST                   | _    | Slave Select input 1.                                                                             |  |  |

| RB6/AN5/CPS5/T1CKI/T1OSI/<br>P1C <sup>(1,3)</sup> /CCP2 <sup>(1,2,3)</sup> /P2A <sup>(1,2,3)</sup> /                      | RB6      | TTL                  | CMOS | General purpose I/O. Individually controlled interrupt-on-change<br>Individually enabled pull-up. |  |  |

| CSPCLK                                                                                                                    | AN5      | AN                   | _    | A/D Channel 5 input.                                                                              |  |  |

|                                                                                                                           | CPS5     | AN                   | _    | Capacitive sensing input 5.                                                                       |  |  |

|                                                                                                                           | T1CKI    | ST                   | —    | Timer1 clock input.                                                                               |  |  |

|                                                                                                                           | T10S0    | XTAL                 | XTAL | Timer1 oscillator connection.                                                                     |  |  |

|                                                                                                                           | P1C      |                      | CMOS | PWM output.                                                                                       |  |  |

|                                                                                                                           | CCP2     | ST                   | CMOS |                                                                                                   |  |  |

|                                                                                                                           | P2A      | _                    | CMOS | PWM output.                                                                                       |  |  |

|                                                                                                                           | ICSPCLK  | ST                   | _    | Serial Programming Clock.                                                                         |  |  |

| RB7/AN6/CPS6/T1OSO/<br>P1D <sup>(1,3)</sup> /P2B <sup>(1,2,3)</sup> /MDCIN1/                                              | RB7      | TTL                  | CMOS | General purpose I/O. Individually controlled interrupt-on-change<br>Individually enabled pull-up. |  |  |

| CSPDAT                                                                                                                    | AN6      | AN                   | —    | A/D Channel 6 input.                                                                              |  |  |

|                                                                                                                           | CPS6     | AN                   | _    | Capacitive sensing input 6.                                                                       |  |  |

|                                                                                                                           | T10S0    | XTAL                 | XTAL | Timer1 oscillator connection.                                                                     |  |  |

|                                                                                                                           | P1D      | _                    | CMOS | PWM output.                                                                                       |  |  |

|                                                                                                                           | P2B      |                      | CMOS | PWM output.                                                                                       |  |  |

|                                                                                                                           | MDCIN1   | ST                   |      | Modulator Carrier Input 1.                                                                        |  |  |

|                                                                                                                           | ICSPDAT  | ST                   | CMOS | ICSP™ Data I/O.                                                                                   |  |  |

#### TARI E 1-2. PIC16/I )F1826/27 PINOLIT DESCRIPTION (CONTINUED)

XTAL = Crystal

TTL = TTL compatible input ST = Schmitt Trigger input with CMOS levels  $I^2C^{TM}$  = Schmitt Trigger input with  $I^2C$ levels

Note 1: Pin functions can be moved using the APFCON0 or APFCON1 register.

2: Functions are only available on the PIC16(L)F1827.

3: Default function location.

HV = High Voltage

### 3.1.1.2 Indirect Read with FSR

The program memory can be accessed as data by setting bit 7 of the FSRxH register and reading the matching INDFx register. The MOVIW instruction will place the lower 8 bits of the addressed word in the W register. Writes to the program memory cannot be performed via the INDF registers. Instructions that access the program memory via the FSR require one extra instruction cycle to complete. Example 3-2 demonstrates accessing the program memory via an FSR.

The HIGH directive will set bit<7> if a label points to a location in program memory.

### EXAMPLE 3-2: ACCESSING PROGRAM MEMORY VIA FSR

| constants |          |        |         |      |  |

|-----------|----------|--------|---------|------|--|

| RETLW     | DATA0    |        | ;Index0 | data |  |

| RETLW     | DATA1    |        | ;Index1 | data |  |

| RETLW     | DATA2    |        |         |      |  |

| RETLW     | data3    |        |         |      |  |

| my_functi | on       |        |         |      |  |

| ;… LOI    | TS OF CO | DE     |         |      |  |

| MOVLW     | LOW cc   | nstant | LS      |      |  |

| MOVWF     | FSR1L    |        |         |      |  |

| MOVLW     | HIGH c   | onstar | nts     |      |  |

| MOVWF     | FSR1H    |        |         |      |  |

| MOVIW     | 0[FSR1]  |        |         |      |  |

| ;THE PROG | RAM MEMO | RY IS  | IN W    |      |  |

|           |          |        |         |      |  |

## 3.2 Data Memory Organization

The data memory is partitioned in 32 memory banks with 128 bytes in a bank. Each bank consists of (Figure 3-3):

- 12 core registers

- · 20 Special Function Registers (SFR)

- Up to 80 bytes of General Purpose RAM (GPR)

- · 16 bytes of common RAM

The active bank is selected by writing the bank number into the Bank Select Register (BSR). Unimplemented memory will read as '0'. All data memory can be accessed either directly (via instructions that use the file registers) or indirectly via the two File Select Registers (FSR). See **Section 3.5** "Indirect Addressing" for more information.

Data Memory uses a 12-bit address. The upper 7-bit of the address define the Bank address and the lower 5-bits select the registers/RAM in that bank.

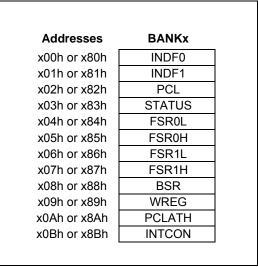

### 3.2.1 CORE REGISTERS

The core registers contain the registers that directly affect the basic operation. The core registers occupy the first 12 addresses of every data memory bank (addresses x00h/x08h through x0Bh/x8Bh). These registers are listed below in Table 3-2. For for detailed information, see Table 3-5.

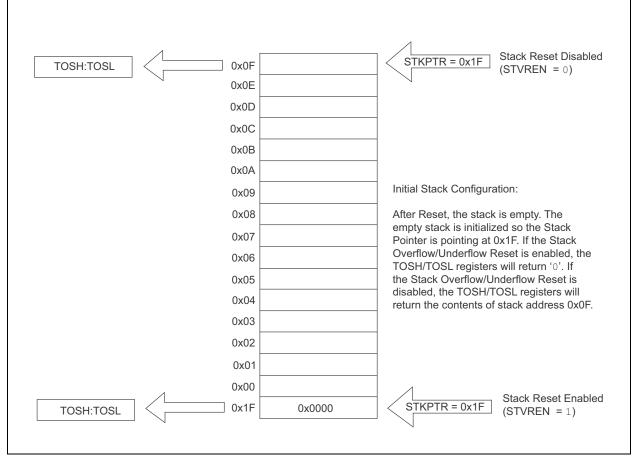

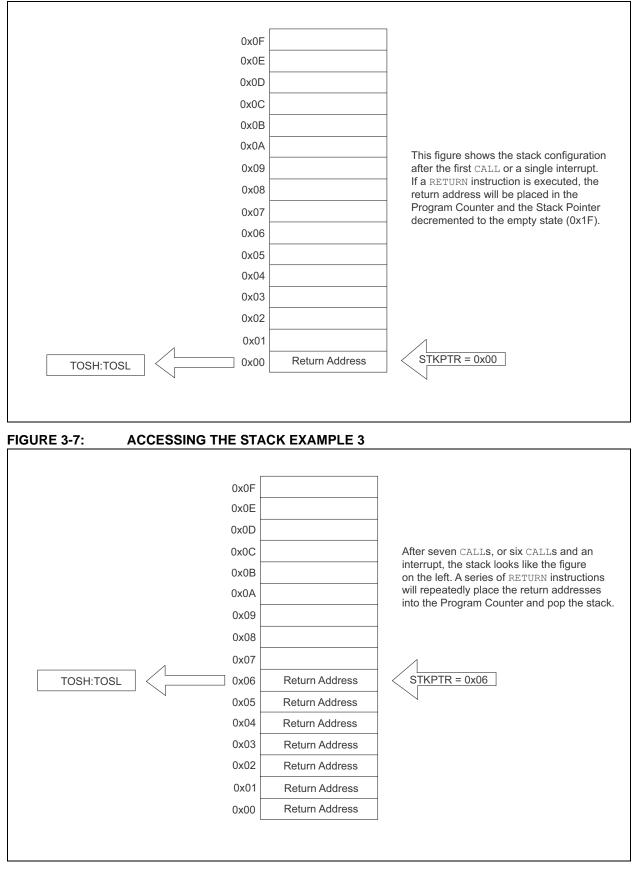

### 3.4 Stack

All devices have a 16-level x 15-bit wide hardware stack (refer to Figures 3-5 through 3-8). The stack space is not part of either program or data space. The PC is PUSHed onto the stack when CALL or CALLW instructions are executed or an interrupt causes a branch. The stack is POPed in the event of a RETURN, RETLW or a RETFIE instruction execution. PCLATH is not affected by a PUSH or POP operation.

The stack operates as a circular buffer if the STVREN bit is programmed to '0' (Configuration Word 2). This means that after the stack has been PUSHed sixteen times, the seventeenth PUSH overwrites the value that was stored from the first PUSH. The eighteenth PUSH overwrites the second PUSH (and so on). The STKOVF and STKUNF flag bits will be set on an Overflow/Underflow, regardless of whether the Reset is enabled.

Note 1: There are no instructions/mnemonics called PUSH or POP. These are actions that occur from the execution of the CALL, CALLW, RETURN, RETLW and RETFIE instructions or the vectoring to an interrupt address.

### 3.4.1 ACCESSING THE STACK

The stack is available through the TOSH, TOSL and STKPTR registers. STKPTR is the current value of the Stack Pointer. TOSH:TOSL register pair points to the TOP of the stack. Both registers are read/writable. TOS is split into TOSH and TOSL due to the 15-bit size of the PC. To access the stack, adjust the value of STKPTR, which will position TOSH:TOSL, then read/write to TOSH:TOSL. STKPTR is 5 bits to allow detection of overflow and underflow.

| Note: | Care should be taken when modifying the |

|-------|-----------------------------------------|

|       | STKPTR while interrupts are enabled.    |

During normal program operation, CALL, CALLW and Interrupts will increment STKPTR while RETLW, RETURN, and RETFIE will decrement STKPTR. At any time STKPTR can be inspected to see how much stack is left. The STKPTR always points at the currently used place on the stack. Therefore, a CALL or CALLW will increment the STKPTR and then write the PC, and a return will unload the PC and then decrement STKPTR.

Reference Figure 3-5 through Figure 3-8 for examples of accessing the stack.

## PIC16(L)F1826/27

FIGURE 3-6: ACCESSING THE STACK EXAMPLE 2

# PIC16(L)F1826/27

| FIGURE 5-7:             | INTERNAL OSCILLATOR SWITCH TIMING                                        |

|-------------------------|--------------------------------------------------------------------------|

| SENETORC/               | UFBNTOSC (FBCSS and WDT (Fbablad)<br>                                    |

| IRCF <3:0>              | $\neq 0$ $X = 0$                                                         |

| System Clock            |                                                                          |

| nfintosc/ i<br>Mfintosc | LENETCISC (ENNET FISCHI es WIDT enabled)                                 |

| HFINTOSC/<br>MEINTOSC   |                                                                          |

| LFINTOSC                |                                                                          |

| IRCF <3:0>              | $\neq 0$ $\chi = 0$                                                      |

| System Clock            |                                                                          |

| LEPEROSC 1<br>LEPEROSC  | EFIRITOSCARFINITOSC<br>LEVELOUSC turns of univer WET or FICER is enabled |

| KUT DIR EKARDKA         | Control Paris, Republic Sono, Second Receiver                            |

| MENTOSC/                |                                                                          |

| \$2CF <330>             | <u>+ C X 19 0</u>                                                        |

| System Grook            |                                                                          |

### 8.6.2 PIE1 REGISTER

The PIE1 register contains the interrupt enable bits, as shown in Register 8-2.

| Note: | Bit PEIE of the INTCON register must be |  |  |  |  |  |  |

|-------|-----------------------------------------|--|--|--|--|--|--|

|       | set to enable any peripheral interrupt. |  |  |  |  |  |  |

### REGISTER 8-2: PIE1: PERIPHERAL INTERRUPT ENABLE REGISTER 1

| R/W-0/0 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| TMR1GIE | ADIE    | RCIE    | TXIE    | SSP1IE  | CCP1IE  | TMR2IE  | TMR1IE  |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                       |  |  |  |  |

|----------------------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|--|--|--|--|

| R = Reada            | ble bit    | W = Writable bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | U = Unimplemented bit, read as '0'                    |  |  |  |  |

| u = Bit is unchanged |            | x = Bit is unknown                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | -n/n = Value at POR and BOR/Value at all other Resets |  |  |  |  |

| '1' = Bit is s       | set        | '0' = Bit is cleared                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                       |  |  |  |  |

| bit 7                | TMR1GIE    | : Timer1 Gate Interrupt Enat                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | le bit                                                |  |  |  |  |

|                      |            | es the Timer1 Gate Acquisitions the Timer1 Gate Acquisitions the Timer1 Gate Acquisitions the Timer1 Gate Acquisitions the transmission of transmission of the transmission of |                                                       |  |  |  |  |

| bit 6                | ADIE: A/D  | Converter (ADC) Interrupt E                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Enable bit                                            |  |  |  |  |

|                      |            | es the ADC interrupt<br>es the ADC interrupt                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                       |  |  |  |  |

| bit 5                | RCIE: US   | ART Receive Interrupt Enabl                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | le bit                                                |  |  |  |  |

|                      |            | es the USART receive interrules the USART receive interrules the USART receive interr                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | •                                                     |  |  |  |  |

| bit 4                | TXIE: USA  | TXIE: USART Transmit Interrupt Enable bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                       |  |  |  |  |

|                      |            | es the USART transmit interr<br>es the USART transmit inter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | •                                                     |  |  |  |  |

| bit 3                | 1 = Enable | Synchronous Serial Port 1 (N<br>es the MSSP1 interrupt<br>es the MSSP1 interrupt                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | ISSP1) Interrupt Enable bit                           |  |  |  |  |

| bit 2                |            | CCP1 Interrupt Enable bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                       |  |  |  |  |

|                      |            | es the CCP1 interrupt<br>es the CCP1 interrupt                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                       |  |  |  |  |

| bit 1                | TMR2IE:    | TMR2 to PR2 Match Interrup                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | t Enable bit                                          |  |  |  |  |

|                      |            | es the Timer2 to PR2 match es the Timer2 to PR2 match                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 1                                                     |  |  |  |  |

| bit 0                | 1 = Enable | Timer1 Overflow Interrupt En<br>es the Timer1 overflow interr<br>es the Timer1 overflow inter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | upt                                                   |  |  |  |  |

### 8.6.3 PIE2 REGISTER

The PIE2 register contains the interrupt enable bits, as shown in Register 8-3.

**Note:** Bit PEIE of the INTCON register must be set to enable any peripheral interrupt.

| REGISTER 8-3: | PIE2: PERIPHERAL INTERRUPT ENABLE REGISTER 2 |

|---------------|----------------------------------------------|

|               |                                              |

| R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | U-0 | U-0 | R/W-0/0               |

|---------|---------|---------|---------|---------|-----|-----|-----------------------|

| OSFIE   | C2IE    | C1IE    | EEIE    | BCL1IE  | —   | _   | CCP2IE <sup>(1)</sup> |

| bit 7   |         |         |         |         |     |     | bit 0                 |

| Legend:                  |                                                                                                                   |                                                     |                                                       |  |  |  |  |

|--------------------------|-------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|-------------------------------------------------------|--|--|--|--|

| R = Readable bit         |                                                                                                                   | W = Writable bit                                    | U = Unimplemented bit, read as '0'                    |  |  |  |  |

| u = Bit is unchanged x = |                                                                                                                   | x = Bit is unknown                                  | -n/n = Value at POR and BOR/Value at all other Resets |  |  |  |  |

| '1' = Bit is set         |                                                                                                                   | '0' = Bit is cleared                                |                                                       |  |  |  |  |

| bit 7                    |                                                                                                                   | lator Fail Interrupt Enable                         |                                                       |  |  |  |  |

|                          | <ul> <li>1 = Enables the Oscillator Fail interrupt</li> <li>0 = Disables the Oscillator Fail interrupt</li> </ul> |                                                     |                                                       |  |  |  |  |

| bit 6                    | C2IE: Compa                                                                                                       | rator C2 Interrupt Enable                           | e bit                                                 |  |  |  |  |

|                          |                                                                                                                   | the Comparator C2 interr<br>the Comparator C2 inter | •                                                     |  |  |  |  |

| bit 5                    | C1IE: Compa                                                                                                       | rator C1 Interrupt Enable                           | bit                                                   |  |  |  |  |

|                          |                                                                                                                   | the Comparator C1 interr<br>the Comparator C1 inter | •                                                     |  |  |  |  |

| bit 4                    | EEIE: EEPRO                                                                                                       | OM Write Completion Inte                            | errupt Enable bit                                     |  |  |  |  |

|                          |                                                                                                                   | the EEPROM Write Com<br>the EEPROM Write Com        | · · ·                                                 |  |  |  |  |

| bit 3                    | BCL1IE: MSS                                                                                                       | SP1 Bus Collision Interrup                          | pt Enable bit                                         |  |  |  |  |

|                          |                                                                                                                   | the MSSP1 Bus Collision<br>the MSSP1 Bus Collisior  |                                                       |  |  |  |  |

| bit 2-1                  | Unimplemen                                                                                                        | ted: Read as '0'                                    |                                                       |  |  |  |  |

| bit 0                    | CCP2IE: CCF                                                                                                       | P2 Interrupt Enable bit                             |                                                       |  |  |  |  |

|                          |                                                                                                                   | the CCP2 interrupt the CCP2 interrupt               |                                                       |  |  |  |  |

Note 1: PIC16(L)F1827 only.

## 11.0 DATA EEPROM AND FLASH PROGRAM MEMORY CONTROL

The Data EEPROM and Flash program memory are readable and writable during normal operation (full VDD range). These memories are not directly mapped in the register file space. Instead, they are indirectly addressed through the Special Function Registers (SFRs). There are six SFRs used to access these memories:

- EECON1

- EECON2

- EEDATL

- EEDATH

- EEADRL

- EEADRH

When interfacing the data memory block, EEDATL holds the 8-bit data for read/write, and EEADRL holds the address of the EEDATL location being accessed. These devices have 256 bytes of data EEPROM with an address range from 0h to 0FFh.

When accessing the program memory block, the EED-ATH:EEDATL register pair forms a 2-byte word that holds the 14-bit data for read/write, and the EEADRL and EEADRH registers form a 2-byte word that holds the 15-bit address of the program memory location being read.

The EEPROM data memory allows byte read and write. An EEPROM byte write automatically erases the location and writes the new data (erase before write).

The write time is controlled by an on-chip timer. The write/erase voltages are generated by an on-chip charge pump rated to operate over the voltage range of the device for byte or word operations.

Depending on the setting of the Flash Program Memory Self Write Enable bits WRT<1:0> of the Configuration Word 2, the device may or may not be able to write certain blocks of the program memory. However, reads from the program memory are always allowed.

When the device is code-protected, the device programmer can no longer access data or program memory. When code-protected, the CPU may continue to read and write the data EEPROM memory and Flash program memory.

### 11.1 EEADRL and EEADRH Registers

The EEADRH:EEADRL register pair can address up to a maximum of 256 bytes of data EEPROM or up to a maximum of 32K words of program memory.

When selecting a program address value, the MSB of the address is written to the EEADRH register and the LSB is written to the EEADRL register. When selecting a EEPROM address value, only the LSB of the address is written to the EEADRL register.

### 11.1.1 EECON1 AND EECON2 REGISTERS

EECON1 is the control register for EE memory accesses.

Control bit EEPGD determines if the access will be a program or data memory access. When clear, any subsequent operations will operate on the EEPROM memory. When set, any subsequent operations will operate on the program memory. On Reset, EEPROM is selected by default.

Control bits RD and WR initiate read and write, respectively. These bits cannot be cleared, only set, in software. They are cleared in hardware at completion of the read or write operation. The inability to clear the WR bit in software prevents the accidental, premature termination of a write operation.

The WREN bit, when set, will allow a write operation to occur. On power-up, the WREN bit is clear. The WRERR bit is set when a write operation is interrupted by a Reset during normal operation. In these situations, following Reset, the user can check the WRERR bit and execute the appropriate error handling routine.

Interrupt flag bit EEIF of the PIR2 register is set when write is complete. It must be cleared in the software.

Reading EECON2 will read all '0's. The EECON2 register is used exclusively in the data EEPROM write sequence. To enable writes, a specific pattern must be written to EECON2.

### 12.2.3 PORTA FUNCTIONS AND OUTPUT PRIORITIES

Each PORTA pin is multiplexed with other functions. The pins, their combined functions and their output priorities are shown in Table 12-2.

When multiple outputs are enabled, the actual pin control goes to the peripheral with the highest priority.

Analog input functions, such as ADC, comparator and CapSense inputs, are not shown in the priority lists. These inputs are active when the I/O pin is set for Analog mode using the ANSELx registers. Digital output functions may control the pin when it is in Analog mode with the priority shown in Table 12-2.

| Pin Name | Function Priority <sup>(1)</sup>                                                                                     |

|----------|----------------------------------------------------------------------------------------------------------------------|

| RA0      | SDO2 (PIC16(L)F1827 only)<br>RA0                                                                                     |

| RA1      | SS2 (PIC16(L)F1827 only)<br>RA1                                                                                      |

| RA2      | DACOUT (DAC)<br>RA2                                                                                                  |

| RA3      | SRQ (SR latch)<br>CCP3 (PIC16(L)F1827 only)<br>C1OUT (Comparator)<br>RA3                                             |

| RA4      | SRNQ (SR latch)<br>CCP4 (PIC16(L)F1827 only)<br>T0CKI<br>C2OUT (Comparator)<br>RA4                                   |

| RA5      | Input only pin                                                                                                       |

| RA6      | OSC2 (enabled by Configura-<br>tion Word)<br>CLKOUT<br>CLKR<br>SDO1<br>P1D<br>P2B (PIC16(L)F1827 only)<br>RA6        |

| RA7      | OSC1/CLKIN (enabled by<br>Configuration Word)<br>P1C<br>CCP2 (PIC16(L)F1827 only)<br>P2A (PIC16(L)F1827 only)<br>RA7 |

TABLE 12-2: PORTA OUTPUT PRIORITY

**Note 1:** Priority listed from highest to lowest.

Each PORTA pin is multiplexed with other functions. The pins, their combined functions and their output priorities are briefly described here. For additional information, refer to the appropriate section in this data sheet.

When multiple outputs are enabled, the actual pin control goes to the peripheral with the lowest number in the following lists.

### **REGISTER 12-3: PORTA: PORTA REGISTER**

| R/W-x/x                                 | R/W-x/x | R-x/x             | R/W-x/x | R/W-x/x                                               | R/W-x/x | R/W-x/x | R/W-x/x |  |

|-----------------------------------------|---------|-------------------|---------|-------------------------------------------------------|---------|---------|---------|--|

| RA7                                     | RA6     | RA5               | RA4     | RA3                                                   | RA2     | RA1     | RA0     |  |

| bit 7                                   |         |                   |         |                                                       |         |         | bit 0   |  |

|                                         |         |                   |         |                                                       |         |         |         |  |

| Legend:                                 |         |                   |         |                                                       |         |         |         |  |

| R = Readable bi                         | it      | W = Writable b    | oit     | U = Unimplemented bit, read as '0'                    |         |         |         |  |

| u = Bit is unchanged x = Bit is unknown |         |                   | own     | -n/n = Value at POR and BOR/Value at all other Resets |         |         |         |  |

| '1' = Bit is set                        |         | '0' = Bit is clea | red     |                                                       |         |         |         |  |

bit 7-0 RA<7:0>: PORTA I/O Value bits<sup>(1)</sup> 1 = Port pin is > VIH 0 = Port pin is < VIL

Note 1: Writes to PORTA are actually written to corresponding LATA register. Reads from PORTA register is return of actual I/O pin values.

### REGISTER 12-4: TRISA: PORTA TRI-STATE REGISTER

| R/W-1/1 | R/W-1/1 | R-1/1  | R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 |

|---------|---------|--------|---------|---------|---------|---------|---------|

| TRISA7  | TRISA6  | TRISA5 | TRISA4  | TRISA3  | TRISA2  | TRISA1  | TRISA0  |

| bit 7   |         |        |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |