Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 32MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 16                                                                        |

| Program Memory Size        | 7KB (4K x 14)                                                             |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 256 x 8                                                                   |

| RAM Size                   | 384 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                               |

| Data Converters            | A/D 12x10b                                                                |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                                            |

| Supplier Device Package    | 20-SSOP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f1827-e-ss |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

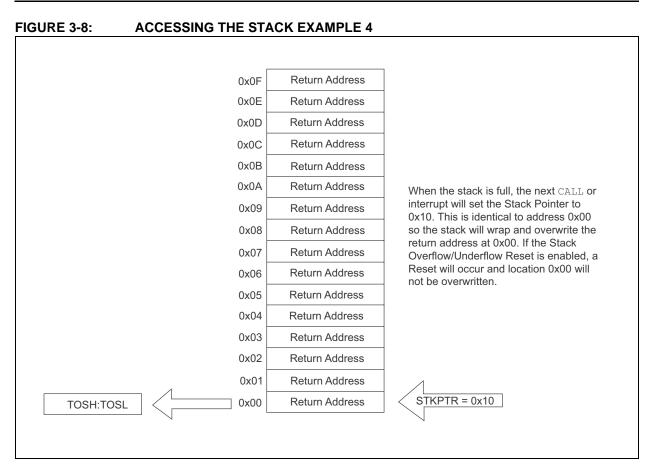

# 3.4.2 OVERFLOW/UNDERFLOW RESET

If the STVREN bit in Configuration Word 2 is programmed to '1', the device will be reset if the stack is PUSHed beyond the sixteenth level or POPed beyond the first level, setting the appropriate bits (STKOVF or STKUNF, respectively) in the PCON register.

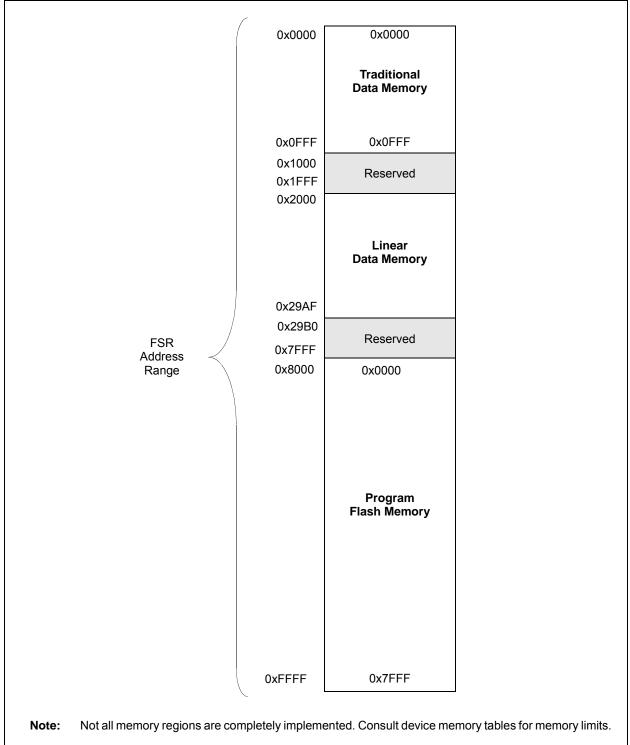

# 3.5 Indirect Addressing

The INDFn registers are not physical registers. Any instruction that accesses an INDFn register actually accesses the register at the address specified by the File Select Registers (FSR). If the FSRn address specifies one of the two INDFn registers, the read will return '0' and the write will not occur (though Status bits may be affected). The FSRn register value is created by the pair FSRnH and FSRnL.

The FSR registers form a 16-bit address that allows an addressing space with 65536 locations. These locations are divided into three memory regions:

- Traditional Data Memory

- Linear Data Memory

- Program Flash Memory

# PIC16(L)F1826/27

# 4.2 Code Protection

Code protection allows the device to be protected from unauthorized access. Program memory protection and data EEPROM protection are controlled independently. Internal access to the program memory and data EEPROM are unaffected by any code protection setting.

## 4.2.1 PROGRAM MEMORY PROTECTION

The entire program memory space is protected from external reads and writes by the  $\overline{CP}$  bit in Configuration Word 1. When  $\overline{CP} = 0$ , external reads and writes of program memory are inhibited and a read will return all '0's. The CPU can continue to read program memory, regardless of the protection bit settings. Writing the program memory is dependent upon the write protection setting. See **Section 4.3** "Write **Protection**" for more information.

# 4.2.2 DATA EEPROM PROTECTION

The entire data EEPROM is protected from external reads and writes by the CPD bit. When CPD = 0, external reads and writes of data EEPROM are inhibited. The CPU can continue to read and write data EEPROM regardless of the protection bit settings.

# 4.3 Write Protection

Write protection allows the device to be protected from unintended self-writes. Applications, such as bootloader software, can be protected while allowing other regions of the program memory to be modified.

The WRT<1:0> bits in Configuration Word 2 define the size of the program memory block that is protected.

# 4.4 User ID

Four memory locations (8000h-8003h) are designated as ID locations where the user can store checksum or other code identification numbers. These locations are readable and writable during normal execution. See **Section 11.5 "User ID, Device ID and Configuration Word Access"** for more information on accessing these memory locations. For more information on checksum calculation, see the "*PIC16F/LF1826/27 Memory Programming Specification*" (DS41390).

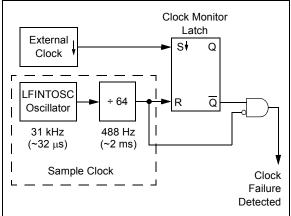

# 5.5 Fail-Safe Clock Monitor

The Fail-Safe Clock Monitor (FSCM) allows the device to continue operating should the external oscillator fail. The FSCM can detect oscillator failure any time after the Oscillator Start-up Timer (OST) has expired. The FSCM is enabled by setting the FCMEN bit in the Configuration Word 1. The FSCM is applicable to all external Oscillator modes (LP, XT, HS, EC, Timer1 Oscillator and RC).

FIGURE 5-9: FSCM BLOCK DIAGRAM

# 5.5.1 FAIL-SAFE DETECTION

The FSCM module detects a failed oscillator by comparing the external oscillator to the FSCM sample clock. The sample clock is generated by dividing the LFINTOSC by 64. See Figure 5-9. Inside the fail detector block is a latch. The external clock sets the latch on each falling edge of the external clock. The sample clock clears the latch on each rising edge of the sample clock. A failure is detected when an entire half-cycle of the sample clock elapses before the external clock goes low.

# 5.5.2 FAIL-SAFE OPERATION

When the external clock fails, the FSCM switches the device clock to an internal clock source and sets the bit flag OSFIF of the PIR2 register. Setting this flag will generate an interrupt if the OSFIE bit of the PIE2 register is also set. The device firmware can then take steps to mitigate the problems that may arise from a failed clock. The system clock will continue to be sourced from the internal clock source until the device firmware successfully restarts the external oscillator and switches back to external operation.

The internal clock source chosen by the FSCM is determined by the IRCF<3:0> bits of the OSCCON register. This allows the internal oscillator to be configured before a failure occurs.

# 5.5.3 FAIL-SAFE CONDITION CLEARING

The Fail-Safe condition is cleared after a Reset, executing a SLEEP instruction or changing the SCS bits of the OSCCON register. When the SCS bits are changed, the OST is restarted. While the OST is running, the device continues to operate from the INTOSC selected in OSCCON. When the OST times out, the Fail-Safe condition is cleared and the device will be operating from the external clock source. The Fail-Safe condition must be cleared before the OSFIF flag can be cleared.

# 5.5.4 RESET OR WAKE-UP FROM SLEEP

The FSCM is designed to detect an oscillator failure after the Oscillator Start-up Timer (OST) has expired. The OST is used after waking up from Sleep and after any type of Reset. The OST is not used with the EC or RC Clock modes so that the FSCM will be active as soon as the Reset or wake-up has completed. When the FSCM is enabled, the Two-Speed Start-up is also enabled. Therefore, the device will always be executing code while the OST is operating.

Note: Due to the wide range of oscillator start-up times, the Fail-Safe circuit is not active during oscillator start-up (i.e., after exiting Reset or Sleep). After an appropriate amount of time, the user should check the Status bits in the OSCSTAT register to verify the oscillator start-up and that the system clock switchover has successfully completed.

# 7.1 Power-on Reset (POR)

The POR circuit holds the device in Reset until VDD has reached an acceptable level for minimum operation. Slow rising VDD, fast operating speeds or analog performance may require greater than minimum VDD. The PWRT, BOR or MCLR features can be used to extend the start-up period until all device operation conditions have been met.

## 7.1.1 POWER-UP TIMER (PWRT)

The Power-up Timer provides a nominal 64 ms timeout on POR or Brown-out Reset.

The device is held in Reset as long as PWRT is active. The PWRT delay allows additional time for the VDD to rise to an acceptable level. The Power-up Timer is enabled by clearing the PWRTE bit in Configuration Word 1.

The Power-up Timer starts after the release of the POR and BOR.

For additional information, refer to Application Note AN607, *"Power-up Trouble Shooting"* (DS00607).

# 7.2 Brown-Out Reset (BOR)

The BOR circuit holds the device in Reset when Vdd reaches a selectable minimum level. Between the POR and BOR, complete voltage range coverage for execution protection can be implemented.

The Brown-out Reset module has four operating modes controlled by the BOREN<1:0> bits in Configuration Word 1. The four operating modes are:

- · BOR is always on

- · BOR is off when in Sleep

- · BOR is controlled by software

- · BOR is always off

Refer to Table 7-1 for more information.

The Brown-out Reset voltage level is selectable by configuring the BORV bit in Configuration Word 2.

A VDD noise rejection filter prevents the BOR from triggering on small events. If VDD falls below VBOR for a duration greater than parameter TBORDC, the device will reset. See Figure 7-2 for more information.

| BOREN<1:0> | SBOREN | Device Mode | BOR Mode | Device Operation<br>upon release of POR | Device Operation<br>upon wake- up from<br>Sleep |  |

|------------|--------|-------------|----------|-----------------------------------------|-------------------------------------------------|--|

| 11         | Х      | Х           | Active   | Waits for BOR ready <sup>(1)</sup>      |                                                 |  |

| 1.0        |        | Awake       | Active   |                                         |                                                 |  |

| 10         | Х      | Sleep       | Disabled | Waits for BOR ready                     |                                                 |  |

| 0.1        | 1      | X           | Active   | Begins immediately                      |                                                 |  |

| 01         | 0      | Х           | Disabled | Begins immediately                      |                                                 |  |

| 00         | Х      | х           | Disabled | Begins immediately                      |                                                 |  |

| 00         | -      | X           |          | Begins immediately                      |                                                 |  |

# TABLE 7-1:BOR OPERATING MODES

Note 1: Even though this case specifically waits for the BOR, the BOR is already operating, so there is no delay in start-up.

# 7.2.1 BOR IS ALWAYS ON

When the BOREN bits of Configuration Word 1 are set to '11', the BOR is always on. The device start-up will be delayed until the BOR is ready and VDD is higher than the BOR threshold.

BOR protection is active during Sleep. The BOR does not delay wake-up from Sleep.

# 7.2.2 BOR IS OFF IN SLEEP

When the BOREN bits of Configuration Word 1 are set to '10', the BOR is on, except in Sleep. The device start-up will be delayed until the BOR is ready and VDD is higher than the BOR threshold.

BOR protection is not active during Sleep. The device wake-up will be delayed until the BOR is ready.

# 7.2.3 BOR CONTROLLED BY SOFTWARE

When the BOREN bits of Configuration Word 1 are set to '01', the BOR is controlled by the SBOREN bit of the BORCON register. The device start-up is not delayed by the BOR ready condition or the VDD level.

BOR protection begins as soon as the BOR circuit is ready. The status of the BOR circuit is reflected in the BORRDY bit of the BORCON register.

BOR protection is unchanged by Sleep.

### 8.6.6 PIR1 REGISTER

The PIR1 register contains the interrupt flag bits, as shown in Register 8-6.

| Note: | Interrupt flag bits are set when an interrupt   |  |  |  |  |  |  |  |  |  |

|-------|-------------------------------------------------|--|--|--|--|--|--|--|--|--|

|       | condition occurs, regardless of the state of    |  |  |  |  |  |  |  |  |  |

|       | its corresponding enable bit or the Global      |  |  |  |  |  |  |  |  |  |

|       | Enable bit, GIE, of the INTCON register.        |  |  |  |  |  |  |  |  |  |

|       | User software should ensure the                 |  |  |  |  |  |  |  |  |  |

|       | appropriate interrupt flag bits are clear prior |  |  |  |  |  |  |  |  |  |

|       | to enabling an interrupt.                       |  |  |  |  |  |  |  |  |  |

# REGISTER 8-6: PIR1: PERIPHERAL INTERRUPT REQUEST REGISTER 1

| R/W-0/0 | R/W-0/0 | R-0/0 | R-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|---------|---------|-------|-------|---------|---------|---------|---------|

| TMR1GIF | ADIF    | RCIF  | TXIF  | SSP1IF  | CCP1IF  | TMR2IF  | TMR1IF  |

| bit 7   |         |       |       |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7 | TMR1GIF: Timer1 Gate Interrupt Flag bit                      |

|-------|--------------------------------------------------------------|

|       | 1 = Interrupt is pending                                     |

|       | 0 = Interrupt is not pending                                 |

| bit 6 | ADIF: A/D Converter Interrupt Flag bit                       |

|       | 1 = Interrupt is pending                                     |

|       | 0 = Interrupt is not pending                                 |

| bit 5 | RCIF: USART Receive Interrupt Flag bit                       |

|       | 1 = Interrupt is pending                                     |

|       | 0 = Interrupt is not pending                                 |

| bit 4 | TXIF: USART Transmit Interrupt Flag bit                      |

|       | 1 = Interrupt is pending                                     |

|       | 0 = Interrupt is not pending                                 |

| bit 3 | SSP1IF: Synchronous Serial Port 1 (MSSP1) Interrupt Flag bit |

|       | 1 = Interrupt is pending                                     |

|       | 0 = Interrupt is not pending                                 |

| bit 2 | CCP1IF: CCP1 Interrupt Flag bit                              |

|       | 1 = Interrupt is pending                                     |

|       | 0 = Interrupt is not pending                                 |

| bit 1 | TMR2IF: Timer2 to PR2 Interrupt Flag bit                     |

|       | 1 = Interrupt is pending                                     |

|       | 0 = Interrupt is not pending                                 |

| bit 0 | TMR1IF: Timer1 Overflow Interrupt Flag bit                   |

|       | 1 = Interrupt is pending                                     |

|       | 0 = Interrupt is not pending                                 |

|       |                                                              |

# PIC16(L)F1826/27

NOTES:

# 17.7 DAC Control Registers

# REGISTER 17-1: DACCON0: VOLTAGE REFERENCE CONTROL REGISTER 0

| R/W-0/0          | R/W-0/0                       | R/W-0/0                                   | U-0             | R/W-0/0         | R/W-0/0              | U-0              | R/W-0/0 |  |  |  |

|------------------|-------------------------------|-------------------------------------------|-----------------|-----------------|----------------------|------------------|---------|--|--|--|

| DACEN            | DACLPS                        | DACOE                                     | _               | DACP            | SS<1:0>              | _                | DACNSS  |  |  |  |

| bit 7            |                               |                                           |                 |                 |                      |                  | bit 0   |  |  |  |

|                  |                               |                                           |                 |                 |                      |                  |         |  |  |  |

| Legend:          |                               |                                           |                 |                 |                      | 01               |         |  |  |  |

| R = Readable     |                               | W = Writable bi                           | •               |                 | ented bit, read as ' |                  |         |  |  |  |

| u = Bit is unc   | 0                             | x = Bit is unkno                          |                 | -n/n = Value at | POR and BOR/Va       | lue at all other | Resets  |  |  |  |

| '1' = Bit is set | t                             | '0' = Bit is clear                        | ed              |                 |                      |                  |         |  |  |  |

|                  |                               |                                           |                 |                 |                      |                  |         |  |  |  |

| bit 7            | DACEN: DAC I<br>1 = DAC is en |                                           |                 |                 |                      |                  |         |  |  |  |

|                  | 0 = DAC is dis                |                                           |                 |                 |                      |                  |         |  |  |  |

| bit 6            |                               | Low-Power Volt                            | age State Selec | et bit          |                      |                  |         |  |  |  |

|                  |                               | tive reference so                         | •               |                 |                      |                  |         |  |  |  |

|                  | 0 = DAC Nega                  | ative reference so                        | ource selected  |                 |                      |                  |         |  |  |  |

| bit 5            | DACOE: DAC                    | Voltage Output E                          | nable bit       |                 |                      |                  |         |  |  |  |

|                  |                               | ige level is also a                       | •               | •               |                      |                  |         |  |  |  |

|                  |                               | ige level is discor                       | nected from th  | e DACOUT pin    |                      |                  |         |  |  |  |

| bit 4            | Unimplemente                  | ed: Read as '0'                           |                 |                 |                      |                  |         |  |  |  |

| bit 3-2          |                               | : DAC Positive S                          | ource Select bi | ts              |                      |                  |         |  |  |  |

|                  | 00 = VDD                      | in                                        |                 |                 |                      |                  |         |  |  |  |

|                  |                               | 01 = VREF+ pin<br>10 = FVR Buffer2 output |                 |                 |                      |                  |         |  |  |  |

|                  | 11 = Reserve                  | •                                         |                 |                 |                      |                  |         |  |  |  |

| bit 1            | Unimplemente                  | ed: Read as '0'                           |                 |                 |                      |                  |         |  |  |  |

| bit 0            | •                             | C Negative Sourc                          | e Select bits   |                 |                      |                  |         |  |  |  |

|                  | 1 = VREF-                     |                                           |                 |                 |                      |                  |         |  |  |  |

|                  | 0 = Vss                       |                                           |                 |                 |                      |                  |         |  |  |  |

# REGISTER 17-2: DACCON1: VOLTAGE REFERENCE CONTROL REGISTER 1

| U-0   | U-0 | U-0 | R/W-0/0 | R/W-0/0 | R/W-0/0   | R/W-0/0 | R/W-0/0 |

|-------|-----|-----|---------|---------|-----------|---------|---------|

| —     |     | —   |         |         | DACR<4:0> |         |         |

| bit 7 |     |     |         |         |           |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-5 Unimplemented: Read as '0'

bit 4-0 DACR<4:0>: DAC Voltage Output Select bits

### TABLE 17-1: SUMMARY OF REGISTERS ASSOCIATED WITH THE DAC MODULE

| Name    | Bit 7 | Bit 6  | Bit 5    | Bit 4    | Bit 3   | Bit 2   | Bit 1  | Bit 0  | Register<br>on page |

|---------|-------|--------|----------|----------|---------|---------|--------|--------|---------------------|

| FVRCON  | FVREN | FVRRDY | Reserved | Reserved | CDAFVR1 | CDAFVR0 | ADFVR1 | ADFVR0 | 138                 |

| DACCON0 | DACEN | DACLPS | DACOE    | _        | DACPSS1 | DACPSS0 | _      | DACNSS | 156                 |

| DACCON1 |       | _      | _        | DACR4    | DACR3   | DACR2   | DACR1  | DACR0  | 156                 |

**Legend:** — = unimplemented, read as '0'. Shaded cells are unused with the DAC module.

# PIC16(L)F1826/27

## 24.3.7 OPERATION IN SLEEP MODE

In Sleep mode, the TMRx register will not increment and the state of the module will not change. If the CCPx pin is driving a value, it will continue to drive that value. When the device wakes up, TMRx will continue from its previous state.

### 24.3.8 CHANGES IN SYSTEM CLOCK FREQUENCY

The PWM frequency is derived from the system clock frequency. Any changes in the system clock frequency will result in changes to the PWM frequency. See Section 5.0 "Oscillator Module (With Fail-Safe Clock Monitor)" for additional details.

#### 24.3.9 EFFECTS OF RESET

Any Reset will force all ports to Input mode and the CCP registers to their Reset states.

## 24.3.10 ALTERNATE PIN LOCATIONS

This module incorporates I/O pins that can be moved to other locations with the use of the alternate pin function registers, APFCON0 and APFCON1. To determine which pins can be moved and what their default locations are upon a reset, see **Section 12.1 "Alternate Pin Function"** for more information.

| Name     | Bit 7               | Bit 6               | Bit 5         | Bit 4                  | Bit 3                  | Bit 2   | Bit 1   | Bit 0   | Register<br>on Page |

|----------|---------------------|---------------------|---------------|------------------------|------------------------|---------|---------|---------|---------------------|

| APFCON0  | RXDTSEL             | SDO1SEL             | SS1SEL        | P2BSEL <sup>(2)</sup>  | CCP2SEL <sup>(2)</sup> | P1DSEL  | P1CSEL  | CCP1SEL | 119                 |

| CCPxCON  | PxM1 <sup>(1)</sup> | PxM0 <sup>(1)</sup> | DCxB1         | DCxB0                  | CCPxM3                 | CCPxM2  | CCPxM1  | CCPxM0  | 226                 |

| CCPxAS   | CCPxASE             | CCPxAS2             | CCPxAS1       | CCPxAS0                | PSSxAC1                | PSSxAC0 | PSSxBD1 | PSSxBD0 | 228                 |

| CCPTMRS  | C4TSEL1             | C4TSEL0             | C3TSEL1       | C3TSEL0                | C2TSEL1                | C2TSEL0 | C1TSEL1 | C1TSEL0 | 227                 |

| INTCON   | GIE                 | PEIE                | TMR0IE        | INTE                   | IOCIE                  | TMR0IF  | INTF    | IOCIF   | 86                  |

| PR2      | Timer2 Peric        | d Register          |               |                        |                        |         |         |         | 189*                |

| PR4      | Timer4 Modu         | ule Period Re       | gister        |                        |                        |         |         |         | 189*                |

| PR6      | Timer6 Modu         | ule Period Re       | gister        |                        |                        |         |         |         | 189*                |

| PSTRxCON | _                   | —                   | _             | STRxSYNC               | STRxD                  | STRxC   | STRxB   | STRxA   | 230                 |

| PWMxCON  | PxRSEN              | PxDC6               | PxDC5         | PxDC4                  | PxDC3                  | PxDC2   | PxDC1   | PxDC0   | 229                 |

| T2CON    | —                   | T2OUTPS3            | T2OUTPS2      | T2OUTPS1               | T2OUTPS0               | TMR2ON  | T2CKPS1 | T2CKPS0 | 191                 |

| T4CON    | —                   | T4OUTPS3            | T4OUTPS2      | T4OUTPS1               | T4OUTPS0               | TMR4ON  | T4CKPS1 | T4CKPS0 | 191                 |

| T6CON    | —                   | T6OUTPS3            | T6OUTPS2      | T6OUTPS1               | T6OUTPS0               | TMR6ON  | T6CKPS1 | T6CKPS0 | 191                 |

| TMR2     | Holding Reg         | ister for the 8     | -bit TMR2 Tin | ne Base                |                        |         |         |         | 189*                |

| TMR4     | Holding Reg         | ister for the 8-    | -bit TMR4 Tin | ne Base <sup>(1)</sup> |                        |         |         |         | 189*                |

| TMR6     | Holding Reg         | ister for the 8     | -bit TMR6 Tin | ne Base <sup>(1)</sup> |                        |         |         |         | 189*                |

| TRISB    | TRISB7              | TRISB6              | TRISB5        | TRISB4                 | TRISB3                 | TRISB2  | TRISB1  | TRISB0  | 127                 |

### TABLE 24-8: SUMMARY OF REGISTERS ASSOCIATED WITH STANDARD PWM

**Legend:** — = Unimplemented locations, read as '0'. Shaded cells are not used by the PWM.

\* Page provides register information.

Note 1: Applies to ECCP modules only.

2: PIC16(L)F1827 only.

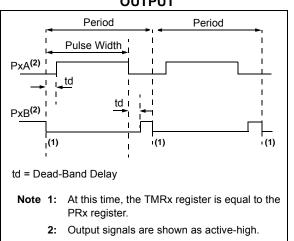

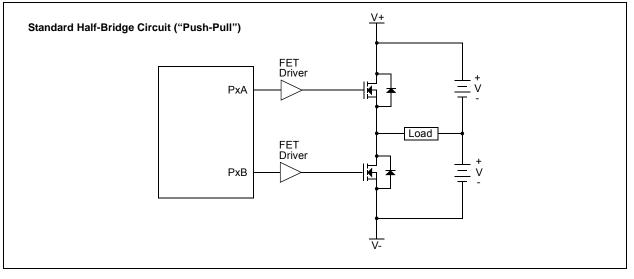

### 24.4.5 PROGRAMMABLE DEAD-BAND DELAY MODE

In Half-Bridge applications where all power switches are modulated at the PWM frequency, the power switches normally require more time to turn off than to turn on. If both the upper and lower power switches are switched at the same time (one turned on, and the other turned off), both switches may be on for a short period of time until one switch completely turns off. During this brief interval, a very high current (*shoot-through current*) will flow through both power switches, shorting the bridge supply. To avoid this potentially destructive shoot-through current from flowing during switching, turning on either of the power switches is normally delayed to allow the other switch to completely turn off.

In Half-Bridge mode, a digitally programmable dead-band delay is available to avoid shoot-through current from destroying the bridge power switches. The delay occurs at the signal transition from the non-active state to the active state. See Figure 24-16 for illustration. The lower seven bits of the associated PWMxCON register (Register 24-4) sets the delay period in terms of microcontroller instruction cycles (TcY or 4 Tosc).

#### FIGURE 24-16: EXAMPLE OF HALF-BRIDGE PWM OUTPUT

# FIGURE 24-17: EXAMPLE OF HALF-BRIDGE APPLICATIONS

| U-0            | U-0             | U-0                                                                                  | R/W-0/0          | R/W-0/0         | R/W-0/0           | R/W-0/0          | R/W-1/1      |  |  |  |  |  |

|----------------|-----------------|--------------------------------------------------------------------------------------|------------------|-----------------|-------------------|------------------|--------------|--|--|--|--|--|

| _              | —               | —                                                                                    | STRxSYNC         | STRxD           | STRxC             | STRxB            | STRxA        |  |  |  |  |  |

| bit 7          |                 |                                                                                      |                  |                 |                   |                  | bit 0        |  |  |  |  |  |

|                |                 |                                                                                      |                  |                 |                   |                  |              |  |  |  |  |  |

| Legend:        |                 |                                                                                      |                  |                 |                   |                  |              |  |  |  |  |  |

| R = Readab     | ole bit         | W = Writable                                                                         | bit              | U = Unimpler    | mented bit, read  | d as '0'         |              |  |  |  |  |  |

| u = Bit is un  | changed         | x = Bit is unk                                                                       | nown             | -n/n = Value a  | at POR and BO     | R/Value at all o | other Resets |  |  |  |  |  |

| '1' = Bit is s | et              | '0' = Bit is cle                                                                     | ared             |                 |                   |                  |              |  |  |  |  |  |

|                |                 |                                                                                      |                  |                 |                   |                  |              |  |  |  |  |  |

| bit 7-5        | Unimplemer      | nted: Read as                                                                        | '0'              |                 |                   |                  |              |  |  |  |  |  |

| bit 4          |                 | Steering Sync                                                                        |                  |                 |                   |                  |              |  |  |  |  |  |

|                |                 | 1 = Output steering update occurs on next PWM period                                 |                  |                 |                   |                  |              |  |  |  |  |  |

|                | 0 = Output st   | 0 = Output steering update occurs at the beginning of the instruction cycle boundary |                  |                 |                   |                  |              |  |  |  |  |  |

| bit 3          |                 | ering Enable bit D                                                                   |                  |                 |                   |                  |              |  |  |  |  |  |

|                | •               | 1 = PxD pin has the PWM waveform with polarity control from CCPxM<1:0>               |                  |                 |                   |                  |              |  |  |  |  |  |

|                | 0 = PxD pin i   | 0 = PxD pin is assigned to port pin                                                  |                  |                 |                   |                  |              |  |  |  |  |  |

| bit 2          |                 | ering Enable bi                                                                      |                  |                 |                   |                  |              |  |  |  |  |  |

|                |                 | 1 = PxC pin has the PWM waveform with polarity control from CCPxM<1:0>               |                  |                 |                   |                  |              |  |  |  |  |  |

|                | •               | 0 = PxC pin is assigned to port pin                                                  |                  |                 |                   |                  |              |  |  |  |  |  |

| bit 1          | STRxB: Stee     | TRxB: Steering Enable bit B                                                          |                  |                 |                   |                  |              |  |  |  |  |  |

|                | 1 = PxB pin h   | nas the PWM v                                                                        | vaveform with p  | olarity control | from CCPxM<1      | 1:0>             |              |  |  |  |  |  |

|                | 0 = PxB pin i   | 0 = PxB pin is assigned to port pin                                                  |                  |                 |                   |                  |              |  |  |  |  |  |

| bit 0          | STRxA: Stee     | ering Enable bi                                                                      | t A              |                 |                   |                  |              |  |  |  |  |  |

|                | 1 = PxA pin ł   | nas the PWM v                                                                        | vaveform with p  | olarity control | from CCPxM<1      | 1:0>             |              |  |  |  |  |  |

|                | 0 = PxA pin i   | s assigned to p                                                                      | oort pin         |                 |                   |                  |              |  |  |  |  |  |

| Note 1: 1      | The PWM Steerin | a modo is avai                                                                       | ilabla only whor |                 | N register bits ( | ~~DvM~3·2~ -     | - 11 ond     |  |  |  |  |  |

# **REGISTER 24-5: PSTRxCON: PWM STEERING CONTROL REGISTER<sup>(1)</sup>**

Note 1: The PWM Steering mode is available only when the CCPxCON register bits CCPxM<3:2> = 11 and PxM<1:0> = 00.

#### 25.5.2 SLAVE RECEPTION

When the  $R/\overline{W}$  bit of a matching received address byte is clear, the  $R/\overline{W}$  bit of the SSPxSTAT register is cleared. The received address is loaded into the SSPx-BUF register and acknowledged.

When the overflow condition exists for a received address, then not Acknowledge is given. An overflow condition is defined as either bit BF of the SSPxSTAT register is set, or bit SSPxOV of the SSPxCON1 register is set. The BOEN bit of the SSPxCON3 register modifies this operation. For more information see Register 25-4.

An MSSPx interrupt is generated for each transferred data byte. Flag bit, SSPxIF, must be cleared by software.

When the SEN bit of the SSPxCON2 register is set, SCLx will be held low (clock stretch) following each received byte. The clock must be released by setting the CKP bit of the SSPxCON1 register, except sometimes in 10-bit mode. See **Section 25.2.3 "SPI Master Mode"** for more detail.

#### 25.5.2.1 7-bit Addressing Reception

This section describes a standard sequence of events for the MSSPx module configured as an  $I^2C$  Slave in 7-bit Addressing mode. All decisions made by hardware or software and their effect on reception. Figure 25-13 and Figure 25-14 is used as a visual reference for this description.

This is a step by step process of what typically must be done to accomplish  $I^2C$  communication.

- 1. Start bit detected.

- 2. S bit of SSPxSTAT is set; SSPxIF is set if interrupt on Start detect is enabled.

- 3. Matching address with  $R/\overline{W}$  bit clear is received.

- 4. The slave pulls SDAx low sending an ACK to the master, and sets SSPxIF bit.

- 5. Software clears the SSPxIF bit.

- 6. Software reads received address from SSPx-BUF clearing the BF flag.

- 7. If SEN = 1; Slave software sets CKP bit to release the SCLx line.

- 8. The master clocks out a data byte.

- 9. Slave drives SDAx low sending an ACK to the master, and sets SSPxIF bit.

- 10. Software clears SSPxIF.

- 11. Software reads the received byte from SSPx-BUF clearing BF.

- 12. Steps 8-12 are repeated for all received bytes from the Master.

- 13. Master sends Stop condition, setting P bit of SSPxSTAT, and the bus goes Idle.

#### 25.5.2.2 7-bit Reception with AHEN and DHEN

Slave device reception with AHEN and DHEN set operate the same as without these options with extra interrupts and clock stretching added after the 8th falling edge of SCLx. These additional interrupts allow the slave software to decide whether it wants to ACK the receive address or data byte, rather than the hardware. This functionality adds support for PMBus<sup>™</sup> that was not present on previous versions of this module.

This list describes the steps that need to be taken by slave software to use these options for  $I^2C$  communcation. Figure 25-15 displays a module using both address and data holding. Figure 25-16 includes the operation with the SEN bit of the SSPxCON2 register set.

- 1. S bit of SSPxSTAT is set; SSPxIF is set if interrupt on Start detect is enabled.

- Matching address with R/W bit clear is clocked in. SSPxIF is set and CKP cleared after the 8th falling edge of SCLx.

- 3. Slave clears the SSPxIF.

- Slave can look at the ACKTIM bit of the SSPxCON3 register to determine if the SSPxIF was after or before the ACK.

- 5. Slave reads the address value from SSPxBUF, clearing the BF flag.

- 6. Slave sets ACK value clocked out to the master by setting ACKDT.

- 7. Slave releases the clock by setting CKP.

- 8. SSPxIF is set after an ACK, not after a NACK.

- 9. If SEN = 1 the slave hardware will stretch the clock after the ACK.

10. Slave clears SSPxIF.

Note: SSPxIF is still set after the 9th falling edge of SCLx even if there is no clock stretching and BF has been cleared. Only if NACK is sent to Master is SSPxIF not set

- 11. SSPxIF set and CKP cleared after 8th falling edge of SCLx for a received data byte.

- 12. Slave looks at ACKTIM bit of SSPxCON3 to determine the source of the interrupt.

- 13. Slave reads the received data from SSPxBUF clearing BF.

- 14. Steps 7-14 are the same for each received data byte.

- 15. Communication is ended by either the slave sending an ACK = 1, or the master sending a Stop condition. If a Stop is sent and Interrupt on Stop Detect is disabled, the slave will only know by polling the P bit of the SSTSTAT register.

# 26.1.2.4 Receive Framing Error

Each character in the receive FIFO buffer has a corresponding framing error Status bit. A framing error indicates that a Stop bit was not seen at the expected time. The framing error status is accessed via the FERR bit of the RCSTA register. The FERR bit represents the status of the top unread character in the receive FIFO. Therefore, the FERR bit must be read before reading the RCREG.

The FERR bit is read-only and only applies to the top unread character in the receive FIFO. A framing error (FERR = 1) does not preclude reception of additional characters. It is not necessary to clear the FERR bit. Reading the next character from the FIFO buffer will advance the FIFO to the next character and the next corresponding framing error.

The FERR bit can be forced clear by clearing the SPEN bit of the RCSTA register which resets the EUSART. Clearing the CREN bit of the RCSTA register does not affect the FERR bit. A framing error by itself does not generate an interrupt.

| Note: | If all receive characters in the receive  |

|-------|-------------------------------------------|

|       | FIFO have framing errors, repeated reads  |

|       | of the RCREG will not clear the FERR bit. |

## 26.1.2.5 Receive Overrun Error

The receive FIFO buffer can hold two characters. An overrun error will be generated if a third character, in its entirety, is received before the FIFO is accessed. When this happens the OERR bit of the RCSTA register is set. The characters already in the FIFO buffer can be read but no additional characters will be received until the error is cleared. The error must be cleared by either clearing the CREN bit of the RCSTA register or by resetting the EUSART by clearing the SPEN bit of the RCSTA register.

# 26.1.2.6 Receiving 9-bit Characters

The EUSART supports 9-bit character reception. When the RX9 bit of the RCSTA register is set the EUSART will shift 9 bits into the RSR for each character received. The RX9D bit of the RCSTA register is the ninth and Most Significant data bit of the top unread character in the receive FIFO. When reading 9-bit data from the receive FIFO buffer, the RX9D data bit must be read before reading the 8 Least Significant bits from the RCREG.

## 26.1.2.7 Address Detection

A special Address Detection mode is available for use when multiple receivers share the same transmission line, such as in RS-485 systems. Address detection is enabled by setting the ADDEN bit of the RCSTA register.

Address detection requires 9-bit character reception. When address detection is enabled, only characters with the ninth data bit set will be transferred to the receive FIFO buffer, thereby setting the RCIF interrupt bit. All other characters will be ignored.

Upon receiving an address character, user software determines if the address matches its own. Upon address match, user software must disable address detection by clearing the ADDEN bit before the next Stop bit occurs. When user software detects the end of the message, determined by the message protocol used, software places the receiver back into the Address Detection mode by setting the ADDEN bit.

## 26.4.1.5 Synchronous Master Reception

Data is received at the RX/DT pin. The RX/DT pin output driver is automatically disabled when the EUSART is configured for synchronous master receive operation.

In Synchronous mode, reception is enabled by setting either the Single Receive Enable bit (SREN of the RCSTA register) or the Continuous Receive Enable bit (CREN of the RCSTA register).

When SREN is set and CREN is clear, only as many clock cycles are generated as there are data bits in a single character. The SREN bit is automatically cleared at the completion of one character. When CREN is set, clocks are continuously generated until CREN is cleared. If CREN is cleared in the middle of a character the CK clock stops immediately and the partial character is discarded. If SREN and CREN are both set, then SREN is cleared at the completion of the first character and CREN takes precedence.

To initiate reception, set either SREN or CREN. Data is sampled at the RX/DT pin on the trailing edge of the TX/CK clock pin and is shifted into the Receive Shift Register (RSR). When a complete character is received into the RSR, the RCIF bit is set and the character is automatically transferred to the two character receive FIFO. The Least Significant eight bits of the top character in the receive FIFO are available in RCREG. The RCIF bit remains set as long as there are unread characters in the receive FIFO.

| Note: | If the RX/DT function is on an analog pin, |  |  |  |  |  |

|-------|--------------------------------------------|--|--|--|--|--|

|       | the corresponding ANSEL bit must be        |  |  |  |  |  |

|       | cleared for the receiver to function.      |  |  |  |  |  |

### 26.4.1.6 Slave Clock

Synchronous data transfers use a separate clock line, which is synchronous with the data. A device configured as a slave receives the clock on the TX/CK line. The TX/CK pin output driver is automatically disabled when the device is configured for synchronous slave transmit or receive operation. Serial data bits change on the leading edge to ensure they are valid at the trailing edge of each clock. One data bit is transferred for each clock cycle. Only as many clock cycles should be received as there are data bits.

Note: If the device is configured as a slave and the TX/CK function is on an analog pin, the corresponding ANSEL bit must be cleared.

# 26.4.1.7 Receive Overrun Error

The receive FIFO buffer can hold two characters. An overrun error will be generated if a third character, in its entirety, is received before RCREG is read to access the FIFO. When this happens the OERR bit of the RCSTA register is set. Previous data in the FIFO will not be overwritten. The two characters in the FIFO buffer can be read, however, no additional characters will be received until the error is cleared. The OERR bit can only be cleared by clearing the overrun condition. If the overrun error occurred when the SREN bit is set and CREN is clear then the error is cleared by reading RCREG. If the overrun occurred when the CREN bit is set then the error condition is cleared by either clearing the CREN bit of the RCSTA register or by clearing the SPEN bit which resets the EUSART.

### 26.4.1.8 Receiving 9-bit Characters

The EUSART supports 9-bit character reception. When the RX9 bit of the RCSTA register is set the EUSART will shift 9-bits into the RSR for each character received. The RX9D bit of the RCSTA register is the ninth, and Most Significant, data bit of the top unread character in the receive FIFO. When reading 9-bit data from the receive FIFO buffer, the RX9D data bit must be read before reading the 8 Least Significant bits from the RCREG.

# 26.4.1.9 Synchronous Master Reception Set-up:

- 1. Initialize the SPBRGH, SPBRGL register pair for the appropriate baud rate. Set or clear the BRGH and BRG16 bits, as required, to achieve the desired baud rate.

- 2. Clear the ANSEL bit for the RX pin (if applicable).

- 3. Enable the synchronous master serial port by setting bits SYNC, SPEN and CSRC.

- 4. Ensure bits CREN and SREN are clear.

- 5. If interrupts are desired, set the RCIE bit of the PIE1 register and the GIE and PEIE bits of the INTCON register.

- 6. If 9-bit reception is desired, set bit RX9.

- 7. Start reception by setting the SREN bit or for continuous reception, set the CREN bit.

- 8. Interrupt flag bit RCIF will be set when reception of a character is complete. An interrupt will be generated if the enable bit RCIE was set.

- Read the RCSTA register to get the ninth bit (if enabled) and determine if any error occurred during reception.

- 10. Read the 8-bit received data by reading the RCREG register.

- 11. If an overrun error occurs, clear the error by either clearing the CREN bit of the RCSTA register or by clearing the SPEN bit which resets the EUSART.

# 26.5 EUSART Operation During Sleep

The EUSART will remain active during Sleep only in the Synchronous Slave mode. All other modes require the system clock and therefore cannot generate the necessary signals to run the Transmit or Receive Shift registers during Sleep.

Synchronous Slave mode uses an externally generated clock to run the Transmit and Receive Shift registers.

#### 26.5.1 SYNCHRONOUS RECEIVE DURING SLEEP

To receive during Sleep, all the following conditions must be met before entering Sleep mode:

- RCSTA and TXSTA Control registers must be configured for Synchronous Slave Reception (see Section 26.4.2.4 "Synchronous Slave Reception Set-up:").

- If interrupts are desired, set the RCIE bit of the PIE1 register and the GIE and PEIE bits of the INTCON register.

- The RCIF interrupt flag must be cleared by reading RCREG to unload any pending characters in the receive buffer.

Upon entering Sleep mode, the device will be ready to accept data and clocks on the RX/DT and TX/CK pins, respectively. When the data word has been completely clocked in by the external device, the RCIF interrupt flag bit of the PIR1 register will be set. Thereby, waking the processor from Sleep.

Upon waking from Sleep, the instruction following the SLEEP instruction will be executed. If the GIE global interrupt enable bit of the INTCON register is also set, then the Interrupt Service Routine at address 004h will be called.

## 26.5.2 SYNCHRONOUS TRANSMIT DURING SLEEP

To transmit during Sleep, all the following conditions must be met before entering Sleep mode:

- RCSTA and TXSTA Control registers must be configured for Synchronous Slave Transmission (see Section 26.4.2.2 "Synchronous Slave Transmission Set-up:").

- The TXIF interrupt flag must be cleared by writing the output data to the TXREG, thereby filling the TSR and transmit buffer.

- If interrupts are desired, set the TXIE bit of the PIE1 register and the PEIE bit of the INTCON register.

- Interrupt enable bits TXIE of the PIE1 register and PEIE of the INTCON register must set.

Upon entering Sleep mode, the device will be ready to accept clocks on TX/CK pin and transmit data on the RX/DT pin. When the data word in the TSR has been completely clocked out by the external device, the pending byte in the TXREG will transfer to the TSR and the TXIF flag will be set. Thereby, waking the processor from Sleep. At this point, the TXREG is available to accept another character for transmission, which will clear the TXIF flag.

Upon waking from Sleep, the instruction following the SLEEP instruction will be executed. If the Global Interrupt Enable (GIE) bit is also set then the Interrupt Service Routine at address 0004h will be called.

# 26.5.3 ALTERNATE PIN LOCATIONS

This module incorporates I/O pins that can be moved to other locations with the use of the alternate pin function registers, APFCON0 and APFCON1. To determine which pins can be moved and what their default locations are upon a reset, see **Section 12.1 "Alternate Pin Function"** for more information.

# REGISTER 27-2: CPSCON1: CAPACITIVE SENSING CONTROL REGISTER 1

| U-0              | U-0          | U-0                                | U-0            | R/W-0/0        | R/W-0/0            | R/W-0/0          | R/W-0/0   |

|------------------|--------------|------------------------------------|----------------|----------------|--------------------|------------------|-----------|

| 0-0              | 0-0          | 0-0                                | 0-0            |                |                    |                  |           |

|                  | _            | —                                  | —              | CPSCH3         | CPSCH2             | CPSCH1           | CPSCH0    |

| oit 7            |              |                                    |                |                |                    |                  | bit (     |

|                  |              |                                    |                |                |                    |                  |           |

| Legend:          |              |                                    |                |                |                    |                  |           |

| R = Readable b   | oit          | W = Writable b                     | it             | U = Unimplem   | nented bit, read a | as '0'           |           |

| u = Bit is uncha | anged        | x = Bit is unkno                   | own            | -n/n = Value a | t POR and BOR      | Value at all oth | er Resets |

| 1' = Bit is set  | Ū            | '0' = Bit is clea                  | red            |                |                    |                  |           |

|                  |              |                                    |                |                |                    |                  |           |

| oit 7-4          | Unimplemen   | ted: Read as '0'                   |                |                |                    |                  |           |

|                  | •            |                                    |                | 0.1.1.1.1.1.1. |                    |                  |           |

| oit 3-0          | If CPSON = 0 | <ul> <li>Capacitive Sen</li> </ul> | sing Channel   | Select bits    |                    |                  |           |

|                  |              | <u>.</u><br>ts are ignored. N      | o obonnol io c | alacted        |                    |                  |           |

|                  | If CPSON = 1 | -                                  |                | Selected.      |                    |                  |           |

|                  |              | channel 0, (CPS                    | 50)            |                |                    |                  |           |

|                  |              | channel 1, (CPS                    | ,              |                |                    |                  |           |

|                  |              | channel 2, (CPS                    | ,              |                |                    |                  |           |

|                  |              | channel 3, (CPS                    | ,              |                |                    |                  |           |

|                  | 0100 =       | channel 4, (CPS                    | S4)            |                |                    |                  |           |

|                  | 0101 =       | channel 5, (CPS                    | S5)            |                |                    |                  |           |

|                  | 0110 =       | channel 6, (CPS                    | 6)             |                |                    |                  |           |

|                  |              | channel 7, (CPS                    | ,              |                |                    |                  |           |

|                  |              | channel 8, (CPS                    | ,              |                |                    |                  |           |

|                  |              | channel 9, (CPS                    | ,              |                |                    |                  |           |

|                  |              | channel 10, (CF                    | ,              |                |                    |                  |           |

|                  |              | channel 11, (CF                    | ,              |                |                    |                  |           |

|                  |              | Reserved. Do n                     |                |                |                    |                  |           |

|                  |              | Reserved. Do n                     |                |                |                    |                  |           |

|                  |              | Reserved. Do n                     |                |                |                    |                  |           |

|                  | 1111 =       | Reserved. Do n                     | ot use.        |                |                    |                  |           |

#### TABLE 27-2: SUMMARY OF REGISTERS ASSOCIATED WITH CAPACITIVE SENSING

| Name       | Bit 7   | Bit 6    | Bit 5    | Bit 4    | Bit 3    | Bit 2   | Bit 1   | Bit 0   | Register<br>on Page |

|------------|---------|----------|----------|----------|----------|---------|---------|---------|---------------------|

| ANSELA     | -       | —        | —        | ANSA4    | ANSA3    | ANSA2   | ANSA1   | ANSA0   | 123                 |

| ANSELB     | ANSB7   | ANSB6    | ANSB5    | ANSB4    | ANSB3    | ANSB2   | ANSB1   | _       | 128                 |

| CPSCON0    | CPSON   | —        | _        |          | CPSRNG1  | CPSRNG0 | CPSOUT  | T0XCS   | 318                 |

| CPSCON1    |         | —        | _        |          | CPSCH3   | CPSCH2  | CPSCH1  | CPSCH0  | 319                 |

| INTCON     | GIE     | PEIE     | TMR0IE   | INTE     | IOCIE    | TMR0IF  | INTF    | IOCIF   | 86                  |

| OPTION_REG | WPUEN   | INTEDG   | TMR0CS   | TMR0SE   | PSA      | PS2     | PS1     | PS0     | 176                 |

| PIE1       | TMR1GIE | ADIE     | RCIE     | TXIE     | SSP1IE   | CCP1IE  | TMR2IE  | TMR1IE  | 87                  |

| PIR1       | TMR1GIF | ADIF     | RCIF     | TXIF     | SSP1IF   | CCP1IF  | TMR2IF  | TMR1IF  | 91                  |

| T1CON      | TMR1CS1 | TMR1CS0  | T1CKPS1  | T1CKPS0  | T1OSCEN  | T1SYNC  |         | TMR10N  | 185                 |

| TxCON      | _       | TxOUTPS3 | TxOUTPS2 | TxOUTPS1 | TxOUTPS0 | TMRxON  | TxCKPS1 | TxCKPS0 | 185                 |

| TRISA      | TRISA7  | TRISA6   | TRISA5   | TRISA4   | TRISA3   | TRISA2  | TRISA1  | TRISA0  | 122                 |

| TRISB      | TRISB7  | TRISB6   | TRISB5   | TRISB4   | TRISB3   | TRISB2  | TRISB1  | TRISB0  | 127                 |

Legend: — = Unimplemented locations, read as '0'. Shaded cells are not used by the capacitive sensing module.

#### 30.4 DC Characteristics: PIC16(L)F1826/27-I/E

| DC CHARACTERISTICS |           |                                      | $\begin{array}{l} \mbox{Standard Operating Conditions (unless otherwise stated)} \\ \mbox{Operating temperature -40°C $\le$ TA $\le$ +85°C for industrial} \\ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ $ |      |          |                                                                         |                                                                                         |  |

|--------------------|-----------|--------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|----------|-------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|--|

| Param<br>No.       | Sym.      | Characteristic                       | Min.                                                                                                                                                                                                | Тур† | Max.     | Units                                                                   | Conditions                                                                              |  |

|                    | VIL       | Input Low Voltage                    |                                                                                                                                                                                                     |      |          |                                                                         |                                                                                         |  |

|                    |           | I/O PORT:                            |                                                                                                                                                                                                     |      |          |                                                                         |                                                                                         |  |

| D030               |           | with TTL buffer                      |                                                                                                                                                                                                     | _    | 0.8      | V                                                                       | $4.5V \leq V\text{DD} \leq 5.5V$                                                        |  |

| D030A              |           |                                      |                                                                                                                                                                                                     | _    | 0.15 VDD | V                                                                       | $1.8V \leq V\text{DD} \leq 4.5V$                                                        |  |

| D031               |           | with Schmitt Trigger buffer          | —                                                                                                                                                                                                   | _    | 0.2 VDD  | V                                                                       | $2.0V \leq V\text{DD} \leq 5.5V$                                                        |  |

|                    |           | with I <sup>2</sup> C™ levels        | —                                                                                                                                                                                                   | —    | 0.3 VDD  | V                                                                       |                                                                                         |  |

|                    |           | with SMBus™ levels                   | —                                                                                                                                                                                                   | —    | 0.8      | V                                                                       | $2.7V \leq V\text{DD} \leq 5.5V$                                                        |  |

| D032               |           | MCLR, OSC1 (RC mode) <sup>(1)</sup>  | —                                                                                                                                                                                                   |      | 0.2 VDD  | V                                                                       |                                                                                         |  |

| D033               |           | OSC1 (HS mode)                       |                                                                                                                                                                                                     |      | 0.3 VDD  | V                                                                       |                                                                                         |  |

|                    | VIH       | Input High Voltage                   | 1                                                                                                                                                                                                   |      |          | •                                                                       |                                                                                         |  |

|                    |           | I/O ports:                           |                                                                                                                                                                                                     | _    | —        |                                                                         |                                                                                         |  |

| D040               |           | with TTL buffer                      | 2.0                                                                                                                                                                                                 | _    | —        | V                                                                       | $4.5V \le V \text{DD} \le 5.5V$                                                         |  |

| D040A              |           |                                      | 0.25 VDD+<br>0.8                                                                                                                                                                                    | _    | —        | V                                                                       | $1.8V \leq V\text{DD} \leq 4.5V$                                                        |  |

| D041               |           | with Schmitt Trigger buffer          | 0.8 VDD                                                                                                                                                                                             |      | _        | V                                                                       | $2.0V \le V\text{DD} \le 5.5V$                                                          |  |

|                    |           | with I <sup>2</sup> C™ levels        | 0.7 VDD                                                                                                                                                                                             | _    | —        | V                                                                       |                                                                                         |  |

|                    |           | with SMBus™ levels                   | 2.1                                                                                                                                                                                                 | _    | _        | V                                                                       | $2.7V \le V\text{DD} \le 5.5V$                                                          |  |

| D042               |           | MCLR                                 | 0.8 VDD                                                                                                                                                                                             | _    | _        | V                                                                       |                                                                                         |  |

| D043A              |           | OSC1 (HS mode)                       | 0.7 VDD                                                                                                                                                                                             | _    | _        | V                                                                       |                                                                                         |  |

| D043B              |           | OSC1 (RC mode)                       | 0.9 VDD                                                                                                                                                                                             | _    |          | V                                                                       | (Note 1)                                                                                |  |

|                    | lil       | Input Leakage Current <sup>(2)</sup> | 1 1                                                                                                                                                                                                 |      |          |                                                                         |                                                                                         |  |

| D060               |           | I/O ports                            | —                                                                                                                                                                                                   | ± 5  | ± 100    | nA                                                                      | $\label{eq:VSS} VSS \leq VPIN \leq VDD, \ Pin \ at \ high-impedance \ at \ 85^{\circ}C$ |  |

|                    |           |                                      |                                                                                                                                                                                                     | ± 5  | ± 1000   | nA                                                                      | 125°C                                                                                   |  |

| D061               |           | MCLR <sup>(3)</sup>                  | —                                                                                                                                                                                                   | ± 50 | ± 200    | nA                                                                      | $VSS \le VPIN \le VDD \text{ at } 85^{\circ}C$                                          |  |

|                    | IPUR      | Weak Pull-up Current                 |                                                                                                                                                                                                     |      |          |                                                                         |                                                                                         |  |

| D070*              |           |                                      | 25                                                                                                                                                                                                  | 100  | 200      |                                                                         | VDD = 3.3V, VPIN = VSS                                                                  |  |

|                    |           |                                      | 25                                                                                                                                                                                                  | 140  | 300      | μA                                                                      | VDD = 5.0V, VPIN = VSS                                                                  |  |

|                    | Vol       | Output Low Voltage <sup>(4)</sup>    | ,                                                                                                                                                                                                   |      |          | 1                                                                       |                                                                                         |  |

| D080               | I/O ports | —                                    | _                                                                                                                                                                                                   | 0.6  | v        | IOL = 8mA, VDD = 5V<br>IOL = 6mA, VDD = 3.3V<br>IOL = 1.8mA, VDD = 1.8V |                                                                                         |  |

|                    | Voн       | Output High Voltage <sup>(4)</sup>   | 11                                                                                                                                                                                                  |      |          |                                                                         | -                                                                                       |  |

| D090               |           | I/O ports                            |                                                                                                                                                                                                     |      |          |                                                                         | Юн = 3.5mA, VDD = 5V                                                                    |  |

|                    |           | Vdd - 0.7                            | _                                                                                                                                                                                                   | —    | V        | ІОН = 3mA, VDD = 3.3V<br>ІОН = 1mA, VDD = 1.8V                          |                                                                                         |  |

|                    |           | Capacitive Loading Specs on          | <b>Output Pins</b>                                                                                                                                                                                  |      |          |                                                                         |                                                                                         |  |

| D101*              | COSC2     | OSC2 pin                             | —                                                                                                                                                                                                   | _    | 15       | pF                                                                      | In XT, HS and LP modes when<br>external clock is used to drive<br>OSC1                  |  |

| D101A*             | Cio       | All I/O pins                         |                                                                                                                                                                                                     | _    | 50       | pF                                                                      |                                                                                         |  |

| *                  |           | arameters are characterized but      | not tested                                                                                                                                                                                          |      |          | 1 P.                                                                    | I                                                                                       |  |

Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are † not tested.

Note 1: In RC oscillator configuration, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended to use an external clock in RC mode.

2: Negative current is defined as current sourced by the pin.

3: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

4: Including OSC2 in CLKOUT mode.

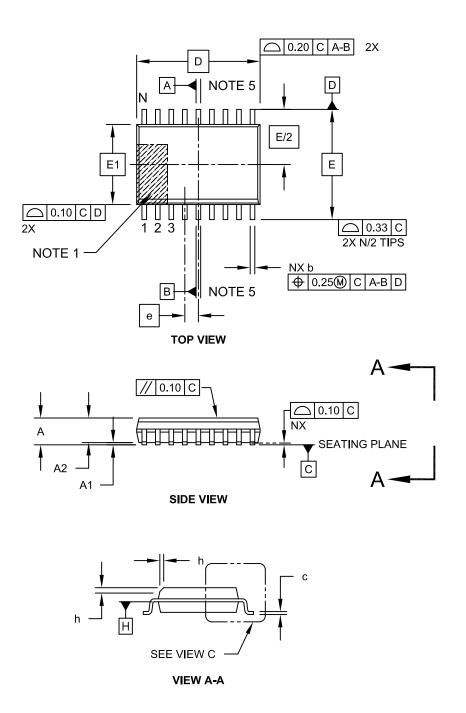

# 18-Lead Plastic Small Outline (SO) - Wide, 7.50 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-051C Sheet 1 of 2

# APPENDIX A: DATA SHEET REVISION HISTORY

# **Revision A**

Original release (06/2009)

# Revision B (08/09)

Revised Tables 5-3, 6-2, 12-2, 12-3; Updated Electrical Specifications; Added UQFN Package; Added SOIC and QFN Land Patterns; Updated Product ID section.

# Revision C (06/10)

Updated Electrical Specification and included Enhanced Core Golden Chapters.

# Revision D (04/11)

Added Char Data to release Final data sheet.

# APPENDIX B: MIGRATING FROM OTHER PIC® DEVICES