Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Details                    |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Product Status             | Active                                                                   |

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 32MHz                                                                    |

| Connectivity               | I²C, SPI, UART/USART                                                     |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 16                                                                       |

| Program Memory Size        | 7KB (4K x 14)                                                            |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 256 x 8                                                                  |

| RAM Size                   | 384 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                              |

| Data Converters            | A/D 12x10b                                                               |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Through Hole                                                             |

| Package / Case             | 18-DIP (0.300", 7.62mm)                                                  |

| Supplier Device Package    | 18-PDIP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f1827-i-p |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### TABLE 1: 18/20/28-PIN SUMMARY (PIC16(L)F1826/27)

|     |                  |             |                 |       |      |                 | •(=): :•: |                           |          |                |                                                                           |                                                                                    |                                                                     |            |           |                  |                        |

|-----|------------------|-------------|-----------------|-------|------|-----------------|-----------|---------------------------|----------|----------------|---------------------------------------------------------------------------|------------------------------------------------------------------------------------|---------------------------------------------------------------------|------------|-----------|------------------|------------------------|

| ю   | 18-Pin PDIP/SOIC | 20-Pin SSOP | 28-Pin QFN/UQFN | ANSEL | A/D  | Reference       | Cap Sense | Comparator                | SR Latch | Timers         | ССР                                                                       | EUSART                                                                             | MSSP                                                                | Interrupt  | Modulator | Pull-up          | Basic                  |

| RA0 | 17               | 19          | 23              | Y     | AN0  | —               | CPS0      | C12IN0-                   | —        | —              | _                                                                         | —                                                                                  | SDO2 <sup>(2)</sup>                                                 | —          | —         | Ν                | —                      |

| RA1 | 18               | 20          | 24              | Y     | AN1  | —               | CPS1      | C12IN1-                   | _        | _              | _                                                                         | _                                                                                  | SS2 <sup>(2)</sup>                                                  | _          | —         | N                | —                      |

| RA2 | 1                | 1           | 26              | Y     | AN2  | VREF-<br>DACOUT | CPS2      | C12IN2-<br>C12IN+         | -        | -              | —                                                                         | -                                                                                  | —                                                                   | —          | -         | N                | -                      |

| RA3 | 2                | 2           | 27              | Y     | AN3  | VREF+           | CPS3      | C12IN3-<br>C1IN+<br>C1OUT | SRQ      | _              | CCP3 <sup>(2)</sup>                                                       |                                                                                    | _                                                                   |            | —         | Ν                | —                      |

| RA4 | 3                | 3           | 28              | Y     | AN4  | —               | CPS4      | C2OUT                     | SRNQ     | TOCKI          | CCP4 <sup>(2)</sup>                                                       | _                                                                                  | —                                                                   | —          | —         | N                | —                      |

| RA5 | 4                | 4           | 1               | Ν     | —    | —               | _         | —                         | —        | —              | _                                                                         | —                                                                                  | SS1 <sup>(1)</sup>                                                  | —          | —         | Y <sup>(3)</sup> | MCLR, VPP              |

| RA6 | 15               | 17          | 20              | Ν     | _    | _               | —         | _                         | _        | _              | P1D <sup>(1)</sup><br>P2B <sup>(1,2)</sup>                                | _                                                                                  | SDO1 <sup>(1)</sup>                                                 |            | —         | Ν                | OSC2<br>CLKOUT<br>CLKR |

| RA7 | 16               | 18          | 21              | Ν     | —    | —               | —         | _                         | —        | —              | P1C <sup>(1)</sup><br>CCP2 <sup>(1,2)</sup><br>P2A <sup>(1,2)</sup>       | —                                                                                  | _                                                                   | _          | —         | Ν                | OSC1<br>CLKIN          |

| RB0 | 6                | 7           | 7               | Ν     | -    | _               | —         | _                         | SRI      | T1G            | CCP1 <sup>(1)</sup><br>P1A <sup>(1)</sup><br>FLT0                         | _                                                                                  | _                                                                   | INT<br>IOC | -         | Y                | —                      |

| RB1 | 7                | 8           | 8               | Y     | AN11 | —               | CPS11     | —                         | —        | —              |                                                                           | RX <sup>(1,4)</sup><br>DT <sup>(1,4)</sup>                                         | SDA1<br>SDI1                                                        | IOC        | —         | Y                | —                      |

| RB2 | 8                | 9           | 9               | Y     | AN10 | _               | CPS10     | _                         | —        | _              |                                                                           | RX <sup>(1)</sup> ,DT <sup>(1)</sup><br>TX <sup>(1,4)</sup><br>CK <sup>(1,4)</sup> | SDA2 <sup>(2)</sup><br>SDI2 <sup>(2)</sup><br>SDO1 <sup>(1,4)</sup> | IOC        | MDMIN     | Y                | —                      |

| RB3 | 9                | 10          | 10              | Y     | AN9  | _               | CPS9      | _                         | —        | —              | CCP1 <sup>(1,4)</sup><br>P1A <sup>(1,4)</sup>                             | _                                                                                  |                                                                     | IOC        | MDOUT     | Y                | —                      |

| RB4 | 10               | 11          | 12              | Y     | AN8  | —               | CPS8      |                           | —        | —              | _                                                                         | —                                                                                  | SCL1<br>SCK1                                                        | IOC        | MDCIN2    | Y                | -                      |

| RB5 | 11               | 12          | 13              | Y     | AN7  | -               | CPS7      | —                         | _        | _              | P1B                                                                       | TX <sup>(1)</sup><br>CK <sup>(1)</sup>                                             | SCL2 <sup>(2)</sup><br>SCK2 <sup>(2)</sup><br>SS1 <sup>(1,4)</sup>  | IOC        | -         | Y                | -                      |

| RB6 | 12               | 13          | 15              | Y     | AN5  | —               | CPS5      | _                         | _        | T1CKI<br>T1OSI | P1C <sup>(1,4)</sup><br>CCP2 <sup>(1,2,4)</sup><br>P2A <sup>(1,2,4)</sup> | —                                                                                  |                                                                     | IOC        | —         | Y                | ICSPCLK/<br>ICDCLK     |

| RB7 | 13               | 14          | 16              | Y     | AN6  | —               | CPS6      | —                         | —        | T1OSO          | P1D <sup>(1,4)</sup><br>P2B <sup>(1,2,4)</sup>                            | —                                                                                  | _                                                                   | IOC        | MDCIN1    | Y                | ICSPDAT/<br>ICDDAT     |

| Vdd | 14               | 15,16       | 17,19           | —     | —    | —               | —         | —                         | —        | —              | _                                                                         | —                                                                                  | —                                                                   | _          | —         | _                | Vdd                    |

| Vss | 5                | 5,6         | 3,5             | -     | —    | —               | —         | —                         | —        | —              | _                                                                         | —                                                                                  | —                                                                   | _          | —         | _                | Vss                    |

|     |                  |             |                 |       |      |                 |           |                           |          |                |                                                                           |                                                                                    |                                                                     |            |           |                  |                        |

PIC16(L)F1826/27

Note

1: Pin functions can be moved using the APFCON0 or APFCON1 register.

2: Functions are only available on the PIC16(L)F1827.

3: Weak pull-up always enabled when MCLR is enabled, otherwise the pull-up is under user control.

4: Default function location.

# TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com** or fax the **Reader Response Form** in the back of this data sheet to (480) 792-4150. We welcome your feedback.

# **Most Current Data Sheet**

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

## Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

# **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

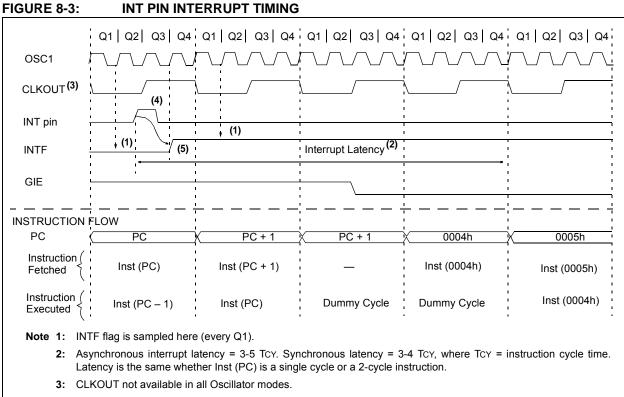

4: For minimum width of INT pulse, refer to AC specifications in Section 30.0 "Electrical Specifications"".

5: INTF is enabled to be set any time during the Q4-Q1 cycles.

# 8.6 Interrupt Control Registers

## 8.6.1 INTCON REGISTER

The INTCON register is a readable and writable register, that contains the various enable and flag bits for TMR0 register overflow, interrupt-on-change and external INT pin interrupts.

Note: Interrupt flag bits are set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the Global Enable bit, GIE, of the INTCON register. User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

# REGISTER 8-1: INTCON: INTERRUPT CONTROL REGISTER

| R/W-0/0 | R-0/0                |

|---------|---------|---------|---------|---------|---------|---------|----------------------|

| GIE     | PEIE    | TMR0IE  | INTE    | IOCIE   | TMR0IF  | INTF    | IOCIF <sup>(1)</sup> |

| bit 7   |         |         |         |         |         |         | bit 0                |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7 | GIE: Global Interrupt Enable bit                                                                                                                                                                                                  |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <ul><li>1 = Enables all active interrupts</li><li>0 = Disables all interrupts</li></ul>                                                                                                                                           |

| bit 6 | <b>PEIE:</b> Peripheral Interrupt Enable bit<br>1 = Enables all active peripheral interrupts<br>0 = Disables all peripheral interrupts                                                                                            |

| bit 5 | <b>TMROIE:</b> Timer0 Overflow Interrupt Enable bit<br>1 = Enables the Timer0 interrupt<br>0 = Disables the Timer0 interrupt                                                                                                      |

| bit 4 | INTE: INT External Interrupt Enable bit<br>1 = Enables the INT external interrupt<br>0 = Disables the INT external interrupt                                                                                                      |

| bit 3 | IOCIE: Interrupt-on-Change Enable bit<br>1 = Enables the interrupt-on-change<br>0 = Disables the interrupt-on-change                                                                                                              |

| bit 2 | <b>TMR0IF:</b> Timer0 Overflow Interrupt Flag bit<br>1 = TMR0 register has overflowed<br>0 = TMR0 register did not overflow                                                                                                       |

| bit 1 | INTF: INT External Interrupt Flag bit<br>1 = The INT external interrupt occurred<br>0 = The INT external interrupt did not occur                                                                                                  |

| bit 0 | <ul> <li>IOCIF: Interrupt-on-Change Interrupt Flag bit<sup>(1)</sup></li> <li>1 = When at least one of the interrupt-on-change pins changed state</li> <li>0 = None of the interrupt-on-change pins have changed state</li> </ul> |

|       |                                                                                                                                                                                                                                   |

**Note 1:** The IOCIF Flag bit is read-only and cleared when all the Interrupt-on-Change flags in the IOCBF register have been cleared by software.

# 9.0 POWER-DOWN MODE (SLEEP)

The Power-Down mode is entered by executing a SLEEP instruction.

Upon entering Sleep mode, the following conditions exist:

- 1. WDT will be cleared but keeps running, if enabled for operation during Sleep.

- 2. PD bit of the STATUS register is cleared.

- 3.  $\overline{\text{TO}}$  bit of the STATUS register is set.

- 4. CPU clock is disabled.

- 5. 31 kHz LFINTOSC is unaffected and peripherals that operate from it may continue operation in Sleep.

- 6. Timer1 oscillator is unaffected and peripherals that operate from it may continue operation in Sleep.

- 7. ADC is unaffected, if the dedicated FRC clock is selected.

- 8. Capacitive Sensing oscillator is unaffected.

- I/O ports maintain the status they had before SLEEP was executed (driving high, low or highimpedance).

- 10. Resets other than WDT are not affected by Sleep mode.

Refer to individual chapters for more details on peripheral operation during Sleep.

To minimize current consumption, the following conditions should be considered:

- I/O pins should not be floating

- External circuitry sinking current from I/O pins

- · Internal circuitry sourcing current from I/O pins

- · Current draw from pins with internal weak pull-ups

- Modules using 31 kHz LFINTOSC

- Modules using Timer1 oscillator

I/O pins that are high-impedance inputs should be pulled to VDD or Vss externally to avoid switching currents caused by floating inputs.

Examples of internal circuitry that might be sourcing current include modules such as the DAC and FVR modules. See Section 17.0 "Digital-to-Analog Converter (DAC) Module" and Section 14.0 "Fixed Voltage Reference (FVR)" for more information on these modules.

# 9.1 Wake-up from Sleep

The device can wake-up from Sleep through one of the following events:

- 1. External Reset input on MCLR pin, if enabled

- 2. BOR Reset, if enabled

- 3. POR Reset

- 4. Watchdog Timer, if enabled

- 5. Any external interrupt

- 6. Interrupts by peripherals capable of running during Sleep (see individual peripheral for more information)

The first three events will cause a device Reset. The last three events are considered a continuation of program execution. To determine whether a device Reset or wake-up event occurred, refer to **Section 7.10 "Determining the Cause of a Reset"**.

When the SLEEP instruction is being executed, the next instruction (PC + 1) is prefetched. For the device to wake-up through an interrupt event, the corresponding interrupt enable bit must be enabled. Wake-up will occur regardless of the state of the GIE bit. If the GIE bit is disabled, the device continues execution at the instruction after the SLEEP instruction. If the GIE bit is enabled, the device executes the instruction after the SLEEP instruction, the device will then call the Interrupt Service Routine. In cases where the execution of the instruction following SLEEP is not desirable, the user should have a NOP after the SLEEP instruction.

The WDT is cleared when the device wakes up from Sleep, regardless of the source of wake-up.

| R/W-0/0          | R/W-0/0               | R/W-0/0                       | R/W/HC-0/0                           | R/W-x/q           | R/W-0/0         | R/S/HC-0/0               | R/S/HC-0/0      |

|------------------|-----------------------|-------------------------------|--------------------------------------|-------------------|-----------------|--------------------------|-----------------|

| EEPGD            | CFGS                  | LWLO                          | FREE                                 | WRERR             | WREN            | WR                       | RD              |

| bit 7            |                       |                               |                                      |                   |                 |                          | bit (           |

|                  |                       |                               |                                      |                   |                 |                          |                 |

| Legend:          | <b>b</b> :4           |                               | <b>b</b> :4                          |                   | nanted bit was  | d aa (0)                 |                 |

| R = Readable     |                       | W = Writable                  |                                      | •                 | nented bit, rea |                          | than Decete     |

| S = Bit can or   | 5                     | x = Bit is unk                |                                      |                   |                 | R/Value at all o         | iner Resets     |

| '1' = Bit is set |                       | '0' = Bit is cl€              | eared                                | HC = Bit is cl    | eared by hardv  | vare                     |                 |

| bit 7            | EEPGD: Flas           | sh Program/Da                 | ta EEPROM M                          | emory Select      | bit             |                          |                 |

|                  | 1 = Accesse           | s program spa                 | ce Flash memo                        | -                 |                 |                          |                 |

|                  |                       | s data EEPRC                  | -                                    |                   |                 |                          |                 |

| bit 6            |                       | -                             | EEPROM or C                          | -                 |                 |                          |                 |

|                  |                       |                               | n, User ID and I<br>Im or data EEP   |                   |                 |                          |                 |

| bit 5            |                       | Write Latches                 |                                      |                   |                 |                          |                 |

| bit 0            |                       |                               | <u>space)</u> OR <u>CFC</u>          | SS = 0 and $FF$   | PGD = 1 (proc   | oram Flash) <sup>.</sup> |                 |

|                  |                       | -                             |                                      |                   |                 | program memoi            | v latches are   |

|                  | upda                  | ated.                         |                                      |                   |                 | C                        | -               |

|                  |                       |                               |                                      |                   |                 | into program m           | emory latche    |

|                  | and                   | initiates a write             | e of all the data                    | stored in the     | program memo    | bry latches.             |                 |

|                  | <u> If CFGS = 0 a</u> | and EEPGD =                   | 0: (Accessing c                      | lata EEPROM       | 1)              |                          |                 |

|                  |                       |                               | WR command i                         |                   |                 | EPROM.                   |                 |

| bit 4            | FREE: Progr           | am Flash Eras                 | e Enable bit                         |                   |                 |                          |                 |

|                  |                       | -                             | <u>space)</u> OR <u>CFC</u>          |                   |                 | -                        |                 |

|                  |                       |                               | operation on the                     | he next WR co     | ommand (clear   | ed by hardware           | after comple    |

|                  |                       | of erase).<br>forms a write o | peration on the                      | next WR com       | mand            |                          |                 |

|                  | 0 - 1 Ch              |                               | peration on the                      |                   | inana.          |                          |                 |

|                  |                       |                               | 0: (Accessing c                      |                   |                 |                          |                 |

|                  | -                     |                               |                                      | will initiate bot | h a erase cycle | e and a write cyc        | de.             |

| bit 3            |                       | PROM Error F                  | •                                    |                   |                 |                          |                 |

|                  |                       |                               | improper prog<br>et attempt (write   |                   |                 | empt or termination      | tion (bit is se |

|                  |                       |                               | operation comp                       |                   |                 |                          |                 |

| bit 2            |                       | ram/Erase Ena                 | • •                                  | j                 |                 |                          |                 |

|                  | -                     | rogram/erase o                |                                      |                   |                 |                          |                 |

|                  |                       |                               | rasing of progra                     | am Flash and      | data EEPROM     | l                        |                 |

| bit 1            | WR: Write Co          | ontrol bit                    |                                      |                   |                 |                          |                 |

|                  |                       |                               | sh or data EEPI                      |                   |                 |                          |                 |

|                  |                       |                               | ned and the bit<br>e set (not cleare |                   |                 | operation is co          | mplete.         |

|                  |                       | •                             | on to the Flash                      |                   |                 | e and inactive.          |                 |

| bit 0            | RD: Read Co           | -                             |                                      |                   |                 |                          |                 |

|                  |                       |                               | lash or data E                       | EPROM read        | d. Read takes   | one cycle. RD            | is cleared in   |

|                  |                       |                               |                                      |                   |                 | , <b>.</b>               |                 |

|                  | nardware              | e. The RD bit o               | an only be set                       | (not cleared) i   | n software.     |                          |                 |

# REGISTER 11-5: EECON1: EEPROM CONTROL 1 REGISTER

NOTES:

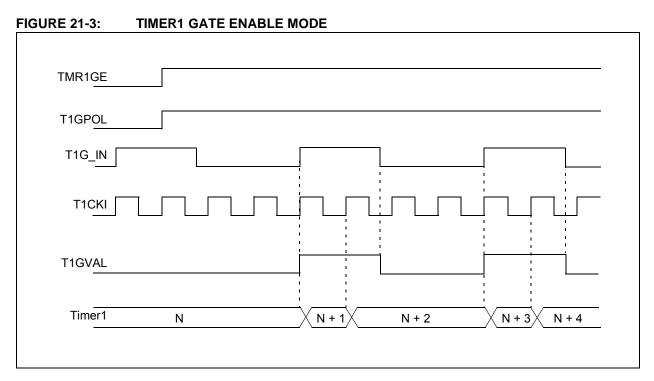

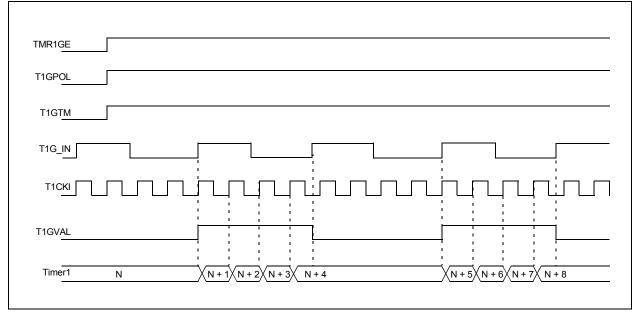

# FIGURE 21-4: TIMER1 GATE TOGGLE MODE

# 24.3.7 OPERATION IN SLEEP MODE

In Sleep mode, the TMRx register will not increment and the state of the module will not change. If the CCPx pin is driving a value, it will continue to drive that value. When the device wakes up, TMRx will continue from its previous state.

# 24.3.8 CHANGES IN SYSTEM CLOCK FREQUENCY

The PWM frequency is derived from the system clock frequency. Any changes in the system clock frequency will result in changes to the PWM frequency. See Section 5.0 "Oscillator Module (With Fail-Safe Clock Monitor)" for additional details.

# 24.3.9 EFFECTS OF RESET

Any Reset will force all ports to Input mode and the CCP registers to their Reset states.

# 24.3.10 ALTERNATE PIN LOCATIONS

This module incorporates I/O pins that can be moved to other locations with the use of the alternate pin function registers, APFCON0 and APFCON1. To determine which pins can be moved and what their default locations are upon a reset, see **Section 12.1 "Alternate Pin Function"** for more information.

| Name     | Bit 7               | Bit 6               | Bit 5         | Bit 4                  | Bit 3                  | Bit 2   | Bit 1   | Bit 0   | Register<br>on Page |

|----------|---------------------|---------------------|---------------|------------------------|------------------------|---------|---------|---------|---------------------|

| APFCON0  | RXDTSEL             | SDO1SEL             | SS1SEL        | P2BSEL <sup>(2)</sup>  | CCP2SEL <sup>(2)</sup> | P1DSEL  | P1CSEL  | CCP1SEL | 119                 |

| CCPxCON  | PxM1 <sup>(1)</sup> | PxM0 <sup>(1)</sup> | DCxB1         | DCxB0                  | CCPxM3                 | CCPxM2  | CCPxM1  | CCPxM0  | 226                 |

| CCPxAS   | CCPxASE             | CCPxAS2             | CCPxAS1       | CCPxAS0                | PSSxAC1                | PSSxAC0 | PSSxBD1 | PSSxBD0 | 228                 |

| CCPTMRS  | C4TSEL1             | C4TSEL0             | C3TSEL1       | C3TSEL0                | C2TSEL1                | C2TSEL0 | C1TSEL1 | C1TSEL0 | 227                 |

| INTCON   | GIE                 | PEIE                | TMR0IE        | INTE                   | IOCIE                  | TMR0IF  | INTF    | IOCIF   | 86                  |

| PR2      | Timer2 Peric        | d Register          |               |                        |                        |         |         |         | 189*                |

| PR4      | Timer4 Modu         | ule Period Re       | gister        |                        |                        |         |         |         | 189*                |

| PR6      | Timer6 Modu         | ule Period Re       | gister        |                        |                        |         |         |         | 189*                |

| PSTRxCON | _                   | —                   | _             | STRxSYNC               | STRxD                  | STRxC   | STRxB   | STRxA   | 230                 |

| PWMxCON  | PxRSEN              | PxDC6               | PxDC5         | PxDC4                  | PxDC3                  | PxDC2   | PxDC1   | PxDC0   | 229                 |

| T2CON    | —                   | T2OUTPS3            | T2OUTPS2      | T2OUTPS1               | T2OUTPS0               | TMR2ON  | T2CKPS1 | T2CKPS0 | 191                 |

| T4CON    | —                   | T4OUTPS3            | T4OUTPS2      | T4OUTPS1               | T4OUTPS0               | TMR4ON  | T4CKPS1 | T4CKPS0 | 191                 |

| T6CON    | —                   | T6OUTPS3            | T6OUTPS2      | T6OUTPS1               | T6OUTPS0               | TMR6ON  | T6CKPS1 | T6CKPS0 | 191                 |

| TMR2     | Holding Reg         | ister for the 8     | -bit TMR2 Tin | ne Base                |                        |         |         |         | 189*                |

| TMR4     | Holding Reg         | ister for the 8-    | -bit TMR4 Tin | ne Base <sup>(1)</sup> |                        |         |         |         | 189*                |

| TMR6     | Holding Reg         | ister for the 8     | -bit TMR6 Tin | ne Base <sup>(1)</sup> |                        |         |         |         | 189*                |

| TRISB    | TRISB7              | TRISB6              | TRISB5        | TRISB4                 | TRISB3                 | TRISB2  | TRISB1  | TRISB0  | 127                 |

# TABLE 24-8: SUMMARY OF REGISTERS ASSOCIATED WITH STANDARD PWM

**Legend:** — = Unimplemented locations, read as '0'. Shaded cells are not used by the PWM.

\* Page provides register information.

Note 1: Applies to ECCP modules only.

2: PIC16(L)F1827 only.

| ECCP Mode            | PxM<1:0> | CCPx/PxA           | PxB                | PxC                | PxD                |

|----------------------|----------|--------------------|--------------------|--------------------|--------------------|

| Single               | 00       | Yes <sup>(1)</sup> | Yes <sup>(1)</sup> | Yes <sup>(1)</sup> | Yes <sup>(1)</sup> |

| Half-Bridge          | 10       | Yes                | Yes                | No                 | No                 |

| Full-Bridge, Forward | 01       | Yes                | Yes                | Yes                | Yes                |

| Full-Bridge, Reverse | 11       | Yes                | Yes                | Yes                | Yes                |

#### **EXAMPLE PIN ASSIGNMENTS FOR VARIOUS PWM ENHANCED MODES** TABLE 24-9

**Note 1:** PWM Steering enables outputs in Single mode.

#### **EXAMPLE PWM (ENHANCED MODE) OUTPUT RELATIONSHIPS (ACTIVE-HIGH FIGURE 24-6:** STATE)

| PxM<1:0>               | Signal        | 0 Pulso<br>Widtl  |              | PRX+1       |

|------------------------|---------------|-------------------|--------------|-------------|

|                        |               |                   | Period       | <b>→</b>    |

| 00 (Single Output)     | PxA Modulated |                   |              |             |

|                        | PxA Modulated | Delay             | Delay<br>◀ ► |             |

| 10 (Half-Bridge)       | PxB Modulated | _ i<br>_ <u>i</u> |              |             |

|                        | PxA Active    | _ <u>'</u>        | ' '          | i           |

| (Full-Bridge,          | PxB Inactive  | — i<br>— ·        |              |             |

| <sup>01</sup> Forward) | PxC Inactive  |                   | 1<br>1<br>   |             |

|                        | PxD Modulated |                   |              | 1<br>1<br>  |

|                        | PxA Inactive  | _ ¦               | 1<br>1       |             |

| (Full-Bridge,          | PxB Modulated |                   | <u>_</u>     | 1<br>1<br>1 |

| Reverse)               | PxC Active —  |                   |              |             |

|                        | PxD Inactive  | _ '<br>_ <u>'</u> | -<br>-<br>   |             |

Period = 4 \* Tosc \* (PRx + 1) \* (TMRx Prescale Value)

Pulse Width = Tosc \* (CCPRxL<7:0>:CCPxCON<5:4>) \* (TMRx Prescale Value)

Delay = 4 \* Tosc \* (PWMxCON<6:0>)

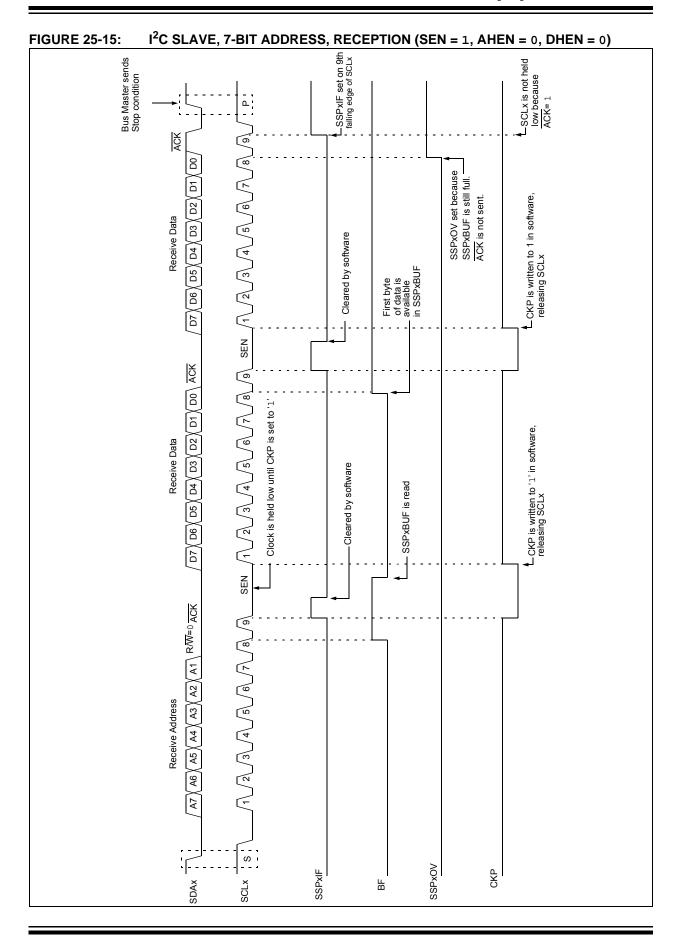

# 25.5.6 CLOCK STRETCHING

Clock stretching occurs when a device on the bus holds the SCLx line low effectively pausing communication. The slave may stretch the clock to allow more time to handle data or prepare a response for the master device. A master device is not concerned with stretching as anytime it is active on the bus and not transferring data it is stretching. Any stretching done by a slave is invisible to the master software and handled by the hardware that generates SCLx.

The CKP bit of the SSPxCON1 register is used to control stretching in software. Any time the CKP bit is cleared, the module will wait for the SCLx line to go low and then hold it. Setting CKP will release SCLx and allow more communication.

## 25.5.6.1 Normal Clock Stretching

Following an ACK if the R/W bit of SSPxSTAT is set, a read request, the slave hardware will clear CKP. This allows the slave time to update SSPxBUF with data to transfer to the master. If the SEN bit of SSPxCON2 is set, the slave hardware will always stretch the clock after the ACK sequence. Once the slave is ready; CKP is set by software and communication resumes.

- **Note 1:** The BF bit has no effect on if the clock will be stretched or not. This is different than previous versions of the module that would not stretch the clock, clear CKP, if SSPxBUF was read before the 9th falling edge of SCLx.

- 2: Previous versions of the module did not stretch the clock for a transmission if SSPxBUF was loaded before the 9th falling edge of SCLx. It is now always cleared for read requests.

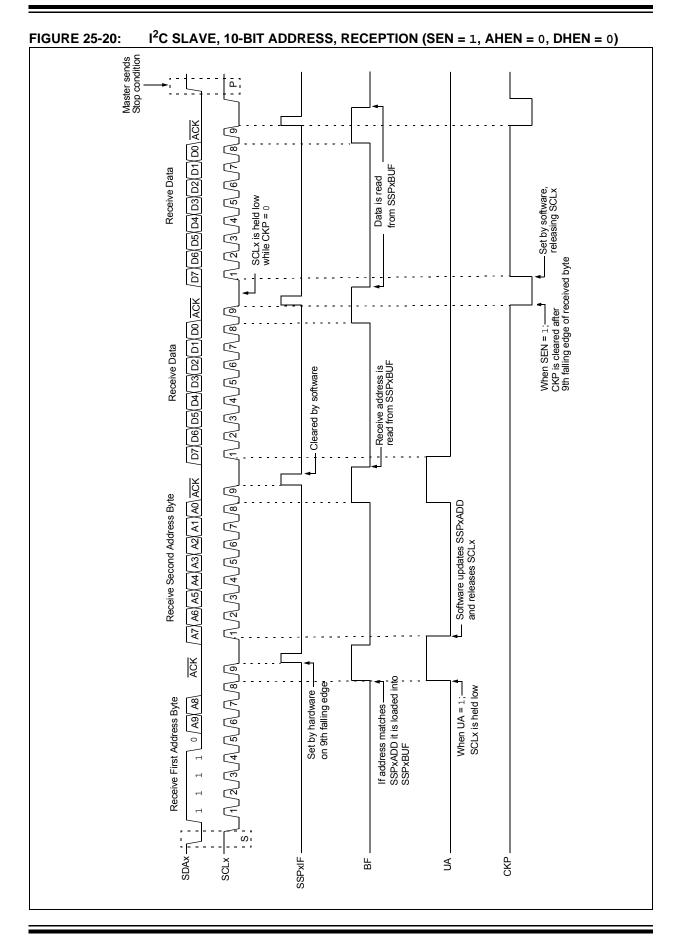

## 25.5.6.2 10-bit Addressing Mode

In 10-bit Addressing mode, when the UA bit is set, the clock is always stretched. This is the only time the SCLx is stretched without CKP being cleared. SCLx is released immediately after a write to SSPxADD.

| Note: | Previous versions of the module did not      |

|-------|----------------------------------------------|

|       | stretch the clock if the second address byte |

|       | did not match.                               |

### 25.5.6.3 Byte NACKing

When AHEN bit of SSPxCON3 is set; CKP is cleared by hardware after the 8th falling edge of SCLx for a received matching address byte. When DHEN bit of SSPxCON3 is set; CKP is cleared after the 8th falling edge of SCLx for received data.

Stretching after the 8th falling edge of SCLx allows the slave to look at the received address or data and decide if it wants to ACK the received data.

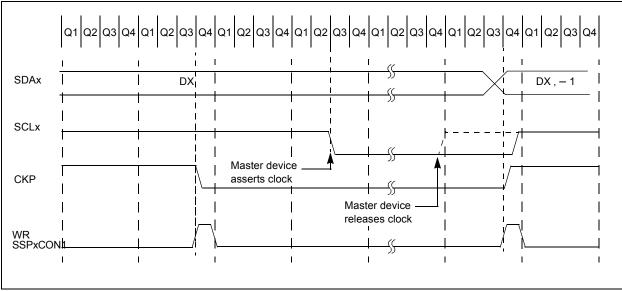

## 25.5.7 CLOCK SYNCHRONIZATION AND THE CKP BIT

Any time the CKP bit is cleared, the module will wait for the SCLx line to go low and then hold it. However, clearing the CKP bit will not assert the SCLx output low until the SCLx output is already sampled low. Therefore, the CKP bit will not assert the SCLx line until an external  $I^2C$  master device has already asserted the SCLx line. The SCLx output will remain low until the CKP bit is set and all other devices on the  $I^2C$  bus have released SCLx. This ensures that a write to the CKP bit will not violate the minimum high time requirement for SCLx (see Figure 25-22).

# FIGURE 25-23: CLOCK SYNCHRONIZATION TIMING

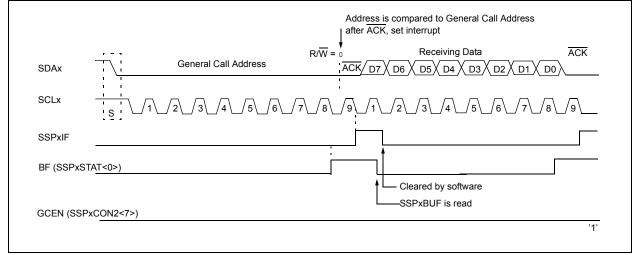

## 25.5.8 GENERAL CALL ADDRESS SUPPORT

The addressing procedure for the  $I^2C$  bus is such that the first byte after the Start condition usually determines which device will be the slave addressed by the master device. The exception is the general call address which can address all devices. When this address is used, all devices should, in theory, respond with an acknowledge.

The general call address is a reserved address in the  $I^2C$  protocol, defined as address 0x00. When the GCEN bit of the SSPxCON2 register is set, the slave module will automatically ACK the reception of this address regardless of the value stored in SSPxADD. After the slave clocks in an address of all zeros with the R/W bit clear, an interrupt is generated and slave software can read SSPxBUF and respond. Figure 25-23 shows a general call reception sequence.

In 10-bit Address mode, the UA bit will not be set on the reception of the general call address. The slave will prepare to receive the second byte as data, just as it would in 7-bit mode.

If the AHEN bit of the SSPxCON3 register is set, just as with any other address reception, the slave hardware will stretch the clock after the 8th falling edge of SCLx. The slave must then set its ACKDT value and release the clock with communication progressing as it would normally.

### 25.5.9 SSPX MASK REGISTER

An SSPx Mask (SSPxMSK) register (Register 25-5) is available in I<sup>2</sup>C Slave mode as a mask for the value held in the SSPxSR register during an address comparison operation. A zero ('0') bit in the SSPxMSK register has the effect of making the corresponding bit of the received address a "don't care".

This register is reset to all '1's upon any Reset condition and, therefore, has no effect on standard SSPx operation until written with a mask value.

The SSPx Mask register is active during:

- 7-bit Address mode: address compare of A<7:1>.

- 10-bit Address mode: address compare of A<7:0> only. The SSPx mask has no effect during the reception of the first (high) byte of the address.

# 25.6.7 I<sup>2</sup>C MASTER MODE RECEPTION

Master mode reception is enabled by programming the Receive Enable bit, RCEN bit of the SSPxCON2 register.

| Note: | The MSSPx module must be in an Idle     |

|-------|-----------------------------------------|

|       | state before the RCEN bit is set or the |

|       | RCEN bit will be disregarded.           |

The Baud Rate Generator begins counting and on each rollover, the state of the SCLx pin changes (high-to-low/low-to-high) and data is shifted into the SSPxSR. After the falling edge of the eighth clock, the receive enable flag is automatically cleared, the contents of the SSPxSR are loaded into the SSPxBUF, the BF flag bit is set, the SSPxIF flag bit is set and the Baud Rate Generator is suspended from counting, holding SCLx low. The MSSPx is now in Idle state awaiting the next command. When the buffer is read by the CPU, the BF flag bit is automatically cleared. The user can then send an Acknowledge bit at the end of reception by setting the Acknowledge Sequence Enable, ACKEN bit of the SSPxCON2 register.

# 25.6.7.1 BF Status Flag

In receive operation, the BF bit is set when an address or data byte is loaded into SSPxBUF from SSPxSR. It is cleared when the SSPxBUF register is read.

# 25.6.7.2 SSPxOV Status Flag

In receive operation, the SSPxOV bit is set when 8 bits are received into the SSPxSR and the BF flag bit is already set from a previous reception.

# 25.6.7.3 WCOL Status Flag

If the user writes the SSPxBUF when a receive is already in progress (i.e., SSPxSR is still shifting in a data byte), the WCOL bit is set and the contents of the buffer are unchanged (the write does not occur). 25.6.7.4 Typical Receive Sequence:

- 1. The user generates a Start condition by setting the SEN bit of the SSPxCON2 register.

- 2. SSPxIF is set by hardware on completion of the Start.

- 3. SSPxIF is cleared by software.

- 4. User writes SSPxBUF with the slave address to transmit and the R/W bit set.

- 5. Address is shifted out the SDAx pin until all 8 bits are transmitted. Transmission begins as soon as SSPxBUF is written to.

- The MSSPx module shifts in the ACK bit from the slave device and writes its value into the ACKSTAT bit of the SSPxCON2 register.

- 7. The MSSPx module generates an interrupt at the end of the ninth clock cycle by setting the SSPxIF bit.

- 8. User sets the RCEN bit of the SSPxCON2 register and the Master clocks in a byte from the slave.

- 9. After the 8th falling edge of SCLx, SSPxIF and BF are set.

- 10. Master clears SSPxIF and reads the received byte from SSPxUF, clears BF.

- Master sets ACK value sent to slave in ACKDT bit of the SSPxCON2 register and initiates the ACK by setting the ACKEN bit.

- 12. Masters ACK is clocked out to the Slave and SSPxIF is set.

- 13. User clears SSPxIF.

- 14. Steps 8-13 are repeated for each received byte from the slave.

- 15. Master sends a not ACK or Stop to end communication.

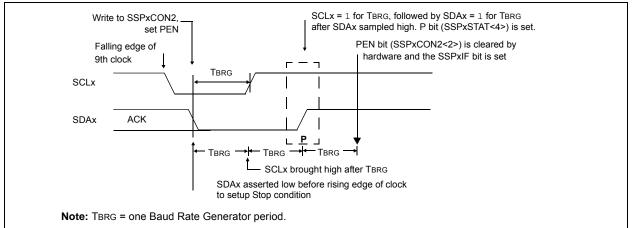

# FIGURE 25-31: STOP CONDITION RECEIVE OR TRANSMIT MODE

# 25.6.10 SLEEP OPERATION

While in Sleep mode, the I<sup>2</sup>C slave module can receive addresses or data and when an address match or complete byte transfer occurs, wake the processor from Sleep (if the MSSPx interrupt is enabled).

# 25.6.11 EFFECTS OF A RESET

A Reset disables the MSSPx module and terminates the current transfer.

# 25.6.12 MULTI-MASTER MODE

In Multi-Master mode, the interrupt generation on the detection of the Start and Stop conditions allows the determination of when the bus is free. The Stop (P) and Start (S) bits are cleared from a Reset or when the MSSPx module is disabled. Control of the I<sup>2</sup>C bus may be taken when the P bit of the SSPxSTAT register is set, or the bus is Idle, with both the S and P bits clear. When the bus is busy, enabling the SSPx interrupt will generate the interrupt when the Stop condition occurs.

In multi-master operation, the SDAx line must be monitored for arbitration to see if the signal level is the expected output level. This check is performed by hardware with the result placed in the BCLxIF bit.

The states where arbitration can be lost are:

- Address Transfer

- · Data Transfer

- A Start Condition

- A Repeated Start Condition

- An Acknowledge Condition

# 25.6.13 MULTI -MASTER COMMUNICATION, BUS COLLISION AND BUS ARBITRATION

Multi-Master mode support is achieved by bus arbitration. When the master outputs address/data bits onto the SDAx pin, arbitration takes place when the master outputs a '1' on SDAx, by letting SDAx float high and another master asserts a '0'. When the SCLx pin floats high, data should be stable. If the expected data on SDAx is a '1' and the data sampled on the SDAx pin is '0', then a bus collision has taken place. The master will set the Bus Collision Interrupt Flag, BCLxIF and reset the I<sup>2</sup>C port to its Idle state (Figure 25-31).

If a transmit was in progress when the bus collision occurred, the transmission is halted, the BF flag is cleared, the SDAx and SCLx lines are deasserted and the SSPxBUF can be written to. When the user services the bus collision Interrupt Service Routine and if the  $l^2C$  bus is free, the user can resume communication by asserting a Start condition.

If a Start, Repeated Start, Stop or Acknowledge condition was in progress when the bus collision occurred, the condition is aborted, the SDAx and SCLx lines are deasserted and the respective control bits in the SSPxCON2 register are cleared. When the user services the bus collision Interrupt Service Routine and if the I<sup>2</sup>C bus is free, the user can resume communication by asserting a Start condition.

The master will continue to monitor the SDAx and SCLx pins. If a Stop condition occurs, the SSPxIF bit will be set.

A write to the SSPxBUF will start the transmission of data at the first data bit, regardless of where the transmitter left off when the bus collision occurred.

In Multi-Master mode, the interrupt generation on the detection of Start and Stop conditions allows the determination of when the bus is free. Control of the  $I^2C$  bus can be taken when the P bit is set in the SSPxSTAT register, or the bus is Idle and the S and P bits are cleared.

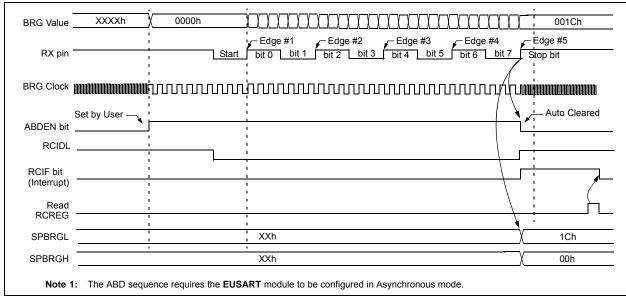

# 26.3.1 AUTO-BAUD DETECT

The EUSART module supports automatic detection and calibration of the baud rate.

In the Auto-Baud Detect (ABD) mode, the clock to the BRG is reversed. Rather than the BRG clocking the incoming RX signal, the RX signal is timing the BRG. The Baud Rate Generator is used to time the period of a received 55h (ASCII "U") which is the Sync character for the LIN bus. The unique feature of this character is that it has five rising edges including the Stop bit edge.

Setting the ABDEN bit of the BAUDCON register starts the auto-baud calibration sequence (Figure 26-6). While the ABD sequence takes place, the EUSART state machine is held in Idle. On the first rising edge of the receive line, after the Start bit, the SPBRG begins counting up using the BRG counter clock as shown in Table 26-6. The fifth rising edge will occur on the RX pin at the end of the eighth bit period. At that time, an accumulated value totaling the proper BRG period is left in the SPBRGH, SPBRGL register pair, the ABDEN bit is automatically cleared and the RCIF interrupt flag is set. The value in the RCREG needs to be read to clear the RCIF interrupt. RCREG content should be discarded. When calibrating for modes that do not use the SPBRGH register the user can verify that the SPBRGL register did not overflow by checking for 00h in the SPBRGH register.

The BRG auto-baud clock is determined by the BRG16 and BRGH bits as shown in Table 26-6. During ABD, both the SPBRGH and SPBRGL registers are used as a 16-bit counter, independent of the BRG16 bit setting. While calibrating the baud rate period, the SPBRGH and SPBRGL registers are clocked at 1/8th the BRG base clock rate. The resulting byte measurement is the average bit time when clocked at full speed.

- Note 1: If the WUE bit is set with the ABDEN bit, auto-baud detection will occur on the byte following the Break character (see Section 26.3.3 "Auto-Wake-up on Break").

- 2: It is up to the user to determine that the incoming character baud rate is within the range of the selected BRG clock source. Some combinations of oscillator frequency and EUSART baud rates are not possible.

- 3: During the auto-baud process, the auto-baud counter starts counting at 1. Upon completion of the auto-baud sequence, to achieve maximum accuracy, subtract 1 from the SPBRGH:SPBRGL register pair.

| TABLE 26-6: BRG COUNTER CLOCI |

|-------------------------------|

|-------------------------------|

| BRG16 | BRGH | BRG Base<br>Clock | BRG ABD<br>Clock |

|-------|------|-------------------|------------------|

| 0     | 0    | Fosc/64           | Fosc/512         |

| 0     | 1    | Fosc/16           | Fosc/128         |

| 1     | 0    | Fosc/16           | Fosc/128         |

| 1     | 1    | Fosc/4            | Fosc/32          |

**Note:** During the ABD sequence, SPBRGL and SPBRGH registers are both used as a 16-bit counter, independent of BRG16 setting.

# FIGURE 26-6: AUTOMATIC BAUD RATE CALIBRATION

# 26.4 EUSART Synchronous Mode

Synchronous serial communications are typically used in systems with a single master and one or more slaves. The master device contains the necessary circuitry for baud rate generation and supplies the clock for all devices in the system. Slave devices can take advantage of the master clock by eliminating the internal clock generation circuitry.

There are two signal lines in Synchronous mode: a bidirectional data line and a clock line. Slaves use the external clock supplied by the master to shift the serial data into and out of their respective receive and transmit shift registers. Since the data line is bidirectional, synchronous operation is half-duplex only. Half-duplex refers to the fact that master and slave devices can receive and transmit data but not both simultaneously. The EUSART can operate as either a master or slave device.

Start and Stop bits are not used in synchronous transmissions.

## 26.4.1 SYNCHRONOUS MASTER MODE

The following bits are used to configure the EUSART for Synchronous Master operation:

- SYNC = 1

- CSRC = 1

- SREN = 0 (for transmit); SREN = 1 (for receive)

- CREN = 0 (for transmit); CREN = 1 (for receive)

- SPEN = 1

Setting the SYNC bit of the TXSTA register configures the device for synchronous operation. Setting the CSRC bit of the TXSTA register configures the device as a master. Clearing the SREN and CREN bits of the RCSTA register ensures that the device is in the Transmit mode, otherwise the device will be configured to receive. Setting the SPEN bit of the RCSTA register enables the EUSART.

# 26.4.1.1 Master Clock

Synchronous data transfers use a separate clock line, which is synchronous with the data. A device configured as a master transmits the clock on the TX/CK line. The TX/CK pin output driver is automatically enabled when the EUSART is configured for synchronous transmit or receive operation. Serial data bits change on the leading edge to ensure they are valid at the trailing edge of each clock. One clock cycle is generated for each data bit. Only as many clock cycles are generated as there are data bits.

# 26.4.1.2 Clock Polarity

A clock polarity option is provided for Microwire compatibility. Clock polarity is selected with the SCKP bit of the BAUDCON register. Setting the SCKP bit sets the clock Idle state as high. When the SCKP bit is set, the data changes on the falling edge of each clock. Clearing the SCKP bit sets the Idle state as low. When the SCKP bit is cleared, the data changes on the rising edge of each clock.

# 26.4.1.3 Synchronous Master Transmission

Data is transferred out of the device on the RX/DT pin. The RX/DT and TX/CK pin output drivers are automatically enabled when the EUSART is configured for synchronous master transmit operation.

A transmission is initiated by writing a character to the TXREG register. If the TSR still contains all or part of a previous character the new character data is held in the TXREG until the last bit of the previous character has been transmitted. If this is the first character, or the previous character has been completely flushed from the TSR, the data in the TXREG is immediately transferred to the TSR. The transmission of the character commences immediately following the transfer of the data to the TSR from the TXREG.

Each data bit changes on the leading edge of the master clock and remains valid until the subsequent leading clock edge.

| Note: | The TSR register is not mapped in data      |  |  |

|-------|---------------------------------------------|--|--|

|       | memory, so it is not available to the user. |  |  |

- 26.4.1.4 Synchronous Master Transmission Set-up:

- Initialize the SPBRGH, SPBRGL register pair and the BRGH and BRG16 bits to achieve the desired baud rate (see Section 26.3 "EUSART Baud Rate Generator (BRG)").

- 2. Enable the synchronous master serial port by setting bits SYNC, SPEN and CSRC.

- 3. Disable Receive mode by clearing bits SREN and CREN.

- 4. Enable Transmit mode by setting the TXEN bit.

- 5. If 9-bit transmission is desired, set the TX9 bit.

- 6. If interrupts are desired, set the TXIE bit of the PIE1 register and the GIE and PEIE bits of the INTCON register.

- 7. If 9-bit transmission is selected, the ninth bit should be loaded in the TX9D bit.

- 8. Start transmission by loading data to the TXREG register.

# 30.7 Timing Parameter Symbology

The timing parameter symbols have been created with one of the following formats:

- 1. TppS2ppS

- 2. TppS

| т                                     |                                            |     |                |  |  |  |

|---------------------------------------|--------------------------------------------|-----|----------------|--|--|--|

| F                                     | Frequency                                  | Т   | Time           |  |  |  |

| Lowerc                                | Lowercase letters (pp) and their meanings: |     |                |  |  |  |

| рр                                    |                                            |     |                |  |  |  |

| СС                                    | CCP1                                       | osc | OSC1           |  |  |  |

| ck                                    | CLKOUT                                     | rd  | RD             |  |  |  |

| CS                                    | CS                                         | rw  | RD or WR       |  |  |  |

| di                                    | SDIx                                       | sc  | SCKx           |  |  |  |

| do                                    | SDO                                        | SS  | SS             |  |  |  |

| dt                                    | Data in                                    | tO  | ТОСКІ          |  |  |  |

| io                                    | I/O PORT                                   | t1  | T1CKI          |  |  |  |

| mc                                    | MCLR                                       | wr  | WR             |  |  |  |

| Uppercase letters and their meanings: |                                            |     |                |  |  |  |

| S                                     |                                            |     |                |  |  |  |

| F                                     | Fall                                       | Р   | Period         |  |  |  |

| н                                     | High                                       | R   | Rise           |  |  |  |

| I                                     | Invalid (High-impedance)                   | V   | Valid          |  |  |  |

| L                                     | Low                                        | Z   | High-impedance |  |  |  |

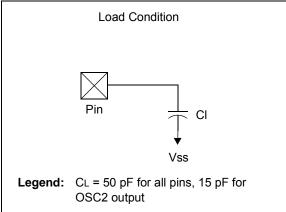

# FIGURE 30-5: LOAD CONDITIONS

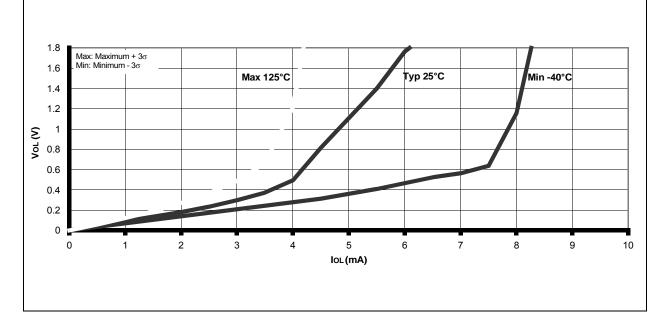

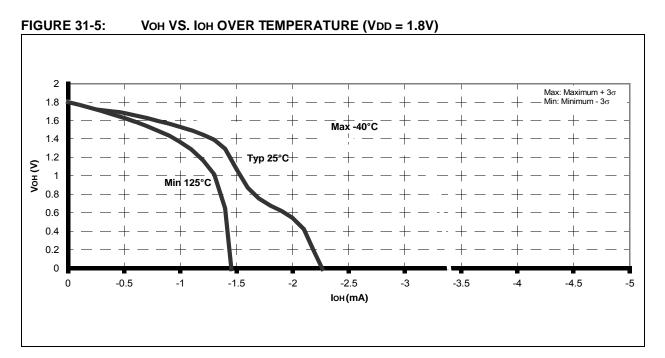

FIGURE 31-6: Vol VS. IoL OVER TEMPERATURE (VDD = 1.8V)