Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 32MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 16                                                                        |

| Program Memory Size        | 7KB (4K x 14)                                                             |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 256 x 8                                                                   |

| RAM Size                   | 384 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                               |

| Data Converters            | A/D 12x10b                                                                |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 18-SOIC (0.295", 7.50mm Width)                                            |

| Supplier Device Package    | 18-SOIC                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f1827-i-so |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

TABLE 3-4: PIC16(L)F1826/27 MEMORY MAP (CONTINUED)

|      | Bank 31                               |

|------|---------------------------------------|

| F80h | Core Registers<br>(Table 3-2)         |

| F8Bh |                                       |

| F8Ch | Unimplemented<br>Read as '0'          |

| FE3h |                                       |

| FE4h | STATUS_SHAD                           |

| FE5h | WREG_SHAD                             |

| FE6h | BSR_SHAD                              |

| FE7h | PCLATH_SHAD                           |

| FE8h | FSR0L_SHAD                            |

| FE9h | FSR0H_SHAD                            |

| FEAh | FSR1L_SHAD                            |

| FEBh | FSR1H_SHAD                            |

| FECh | _                                     |

| FEDh | STKPTR                                |

| FEEh | TOSL                                  |

| FEFh | TOSH                                  |

| FF0h | Common RAM<br>(Accesses<br>70h – 7Fh) |

| FFFh |                                       |

= Unimplemented data memory locations, read as '0',

FIGURE 3-6: **ACCESSING THE STACK EXAMPLE 2** 0x0F 0x0E 0x0D 0x0C 0x0B 0x0A This figure shows the stack configuration 0x09 after the first CALL or a single interrupt. If a RETURN instruction is executed, the 0x08 return address will be placed in the Program Counter and the Stack Pointer 0x07 decremented to the empty state (0x1F). 0x06 0x05 0x04 0x03 0x02 0x01 STKPTR = 0x00 Return Address 0x00 TOSH:TOSL

#### FIGURE 3-7: **ACCESSING THE STACK EXAMPLE 3** 0x0F 0x0E 0x0D 0x0C After seven CALLs, or six CALLs and an interrupt, the stack looks like the figure 0x0B on the left. A series of ${\tt RETURN}$ instructions will repeatedly place the return addresses 0x0A into the Program Counter and pop the stack. 0x09 80x0 0x07 STKPTR = 0x06 TOSH:TOSL 0x06 Return Address 0x05 Return Address 0x04 Return Address 0x03 Return Address 0x02 Return Address 0x01 Return Address Return Address 0x00

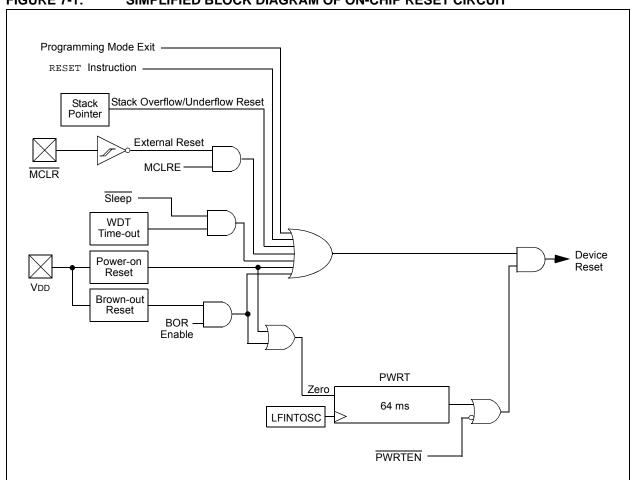

#### 7.0 RESETS

There are multiple ways to reset this device:

- Power-on Reset (POR)

- · Brown-out Reset (BOR)

- MCLR Reset

- · WDT Reset

- RESET instruction

- · Stack Overflow

- · Stack Underflow

- · Programming mode exit

To allow VDD to stabilize, an optional power-up timer can be enabled to extend the Reset time after a BOR or POR event.

A simplified block diagram of the On-Chip Reset Circuit is shown in Figure 7-1.

FIGURE 7-1: SIMPLIFIED BLOCK DIAGRAM OF ON-CHIP RESET CIRCUIT

#### 7.11 Power Control (PCON) Register

The Power Control (PCON) register contains flag bits to differentiate between a:

- Power-on Reset (POR)

- Brown-out Reset (BOR)

- Reset Instruction Reset (RI)

- MCLR Reset (RMCLR)

Legend:

bit 0

R = Readable bit

u = Bit is unchanged

- Stack Underflow Reset (STKUNF)

- Stack Overflow Reset (STKOVF)

HC = Bit is cleared by hardware

The PCON register bits are shown in Register 7-2.

#### REGISTER 7-2: PCON: POWER CONTROL REGISTER

1 = No Power-on Reset occurred

**BOR:** Brown-out Reset Status bit

1 = No Brown-out Reset occurred

W = Writable bit

x = Bit is unknown

| R/W/HS-0/q | R/W/HS-0/q | U-0 | U-0 | R/W/HC-1/q | R/W/HC-1/q | R/W/HC-q/u | R/W/HC-q/u |

|------------|------------|-----|-----|------------|------------|------------|------------|

| STKOVF     | STKUNF     | _   | _   | RMCLR      | RI         | POR        | BOR        |

| bit 7      |            |     |     |            |            |            | bit 0      |

HS = Bit is set by hardware

U = Unimplemented bit, read as '0'

-m/n = Value at POR and BOR/Value at all other Resets

| 9                                                                                                         |

|-----------------------------------------------------------------------------------------------------------|

| '0' = Bit is cleared q = Value depends on condition                                                       |

| STKOVF: Stack Overflow Flag bit                                                                           |

| 1 = A Stack Overflow occurred                                                                             |

| 0 = A Stack Overflow has not occurred or set to '0' by firmware                                           |

| STKUNF: Stack Underflow Flag bit                                                                          |

| 1 = A Stack Underflow occurred                                                                            |

| 0 = A Stack Underflow has not occurred or set to '0' by firmware                                          |

| Unimplemented: Read as '0'                                                                                |

| RMCLR: MCLR Reset Flag bit                                                                                |

| 1 = A MCLR Reset has not occurred or set to '1' by firmware                                               |

| $0 = A \overline{MCLR}$ Reset has occurred (set to '0' in hardware when a $\overline{MCLR}$ Reset occurs) |

| RI: RESET Instruction Flag bit                                                                            |

| 1 = A RESET instruction has not been executed or set to '1' by firmware                                   |

| 0 = A RESET instruction has been executed (set to '0' in hardware upon executing a RESET instruction)     |

| POR: Power-on Reset Status bit                                                                            |

|                                                                                                           |

0 = A Power-on Reset occurred (must be set in software after a Power-on Reset occurs)

#### 10.1 Independent Clock Source

The WDT derives its time base from the 31 kHz LFINTOSC internal oscillator. Time intervals in this chapter are based on a nominal interval of 1 ms. See **Section 30.0 "Electrical Specifications"** for the LFINTOSC tolerances.

#### 10.2 WDT Operating Modes

The Watchdog Timer module has four operating modes controlled by the WDTE<1:0> bits in Configuration Word 1. See Table 10-1.

#### 10.2.1 WDT IS ALWAYS ON

When the WDTE bits of Configuration Word 1 are set to '11', the WDT is always on.

WDT protection is active during Sleep.

#### 10.2.2 WDT IS OFF IN SLEEP

When the WDTE bits of Configuration Word 1 are set to '10', the WDT is on, except in Sleep.

WDT protection is not active during Sleep.

#### 10.2.3 WDT CONTROLLED BY SOFTWARE

When the WDTE bits of Configuration Word 1 are set to '01', the WDT is controlled by the SWDTEN bit of the WDTCON register.

WDT protection is unchanged by Sleep. See Table 10-1 for more details.

TABLE 10-1: WDT OPERATING MODES

| WDTE<1:0> | SWDTEN | Device<br>Mode | WDT<br>Mode |

|-----------|--------|----------------|-------------|

| 11        | Х      | Х              | Active      |

| 1.0       | 37     | Awake          | Active      |

| 10        | Х      | Sleep          | Disabled    |

| 0.1       | 1      | Х              | Active      |

| 01        | 0      | ^              | Disabled    |

| 00        | Х      | Х              | Disabled    |

#### 10.3 Time-Out Period

The WDTPS bits of the WDTCON register set the time-out period from 1 ms to 256 seconds (nominal). After a Reset, the default time-out period is 2 seconds.

#### 10.4 Clearing the WDT

The WDT is cleared when any of the following conditions occur:

- · Any Reset

- CLRWDT instruction is executed

- · Device enters Sleep

- · Device wakes up from Sleep

- · Oscillator fail event

- · WDT is disabled

- · Oscillator Start-up TImer (OST) is running

See Table 10-2 for more information.

#### 10.5 Operation During Sleep

When the device enters Sleep, the WDT is cleared. If the WDT is enabled during Sleep, the WDT resumes counting.

When the device exits Sleep, the WDT is cleared again. The WDT remains clear until the OST, if enabled, completes. See Section 5.0 "Oscillator Module (With Fail-Safe Clock Monitor)" for more information on the OST.

When a WDT time-out occurs while the device is in Sleep, no Reset is generated. Instead, the <u>device</u> wakes up and resumes operation. The  $\overline{\text{TO}}$  and  $\overline{\text{PD}}$  bits in the STATUS register are changed to indicate the event. See **Register 3-1** for more information.

**TABLE 10-2: WDT CLEARING CONDITIONS**

| Conditions                                               | WDT                          |

|----------------------------------------------------------|------------------------------|

| WDTE<1:0> = 00                                           |                              |

| WDTE<1:0> = 01 and SWDTEN = 0                            |                              |

| WDTE<1:0> = 10 and enter Sleep                           | Cleared                      |

| CLRWDT Command                                           | Cleared                      |

| Oscillator Fail Detected                                 |                              |

| Exit Sleep + System Clock = T1OSC, EXTRC, INTOSC, EXTCLK |                              |

| Exit Sleep + System Clock = XT, HS, LP                   | Cleared until the end of OST |

| Change INTOSC divider (IRCF bits)                        | Unaffected                   |

#### 11.4 Modifying Flash Program Memory

When modifying existing data in a program memory row, and data within that row must be preserved, it must first be read and saved in a RAM image. Program memory is modified using the following steps:

- Load the starting address of the row to be modified.

- Read the existing data from the row into a RAM image.

- 3. Modify the RAM image to contain the new data to be written into program memory.

- Load the starting address of the row to be rewritten.

- 5. Erase the program memory row.

- Load the write latches with data from the RAM image.

- 7. Initiate a programming operation.

- 8. Repeat steps 6 and 7 as many times as required to reprogram the erased row.

### 11.5 User ID, Device ID and Configuration Word Access

Instead of accessing program memory or EEPROM data memory, the User ID's, Device ID/Revision ID and Configuration Words can be accessed when CFGS = 1 in the EECON1 register. This is the region that would be pointed to by PC<15> = 1, but not all addresses are accessible. Different access may exist for reads and writes. Refer to Table 11-2.

When read access is initiated on an address outside the parameters listed in Table 11-2, the EEDATH:EED-ATL register pair is cleared.

#### TABLE 11-2: USER ID, DEVICE ID AND CONFIGURATION WORD ACCESS (CFGS = 1)

| Address     | Function                    | Read Access | Write Access |

|-------------|-----------------------------|-------------|--------------|

| 8000h-8003h | User IDs                    | Yes         | Yes          |

| 8006h       | Device ID/Revision ID       | Yes         | No           |

| 8007h-8008h | Configuration Words 1 and 2 | Yes         | No           |

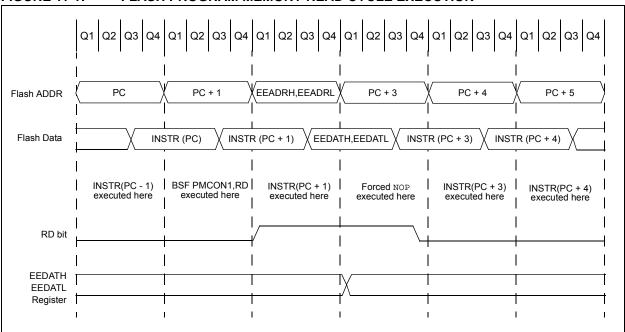

#### **EXAMPLE 11-3: CONFIGURATION WORD AND DEVICE ID ACCESS**

```

This code block will read 1 word of program memory at the memory address:

PROG_ADDR_LO (must be 00h-08h) data will be returned in the variables;

PROG_DATA_HI, PROG_DATA_LO

BANKSEL EEADRL

; Select correct Bank

MOVLW PROG_ADDR_LO ;

; Store LSB of address

MOVWF

EEADRL

CLRF

EEADRH

; Clear MSB of address

BSF

EECON1, CFGS

; Select Configuration Space

INTCON, GIE

BCF

; Disable interrupts

EECON1,RD

; Initiate read

BSF

; Executed (See Figure 11-1)

NOP

NOP

; Ignored (See Figure 11-1)

INTCON,GIE

BSF

; Restore interrupts

MOVF

EEDATL,W

; Get LSB of word

MOVWF

PROG_DATA_LO

; Store in user location

MOVF

EEDATH, W

; Get MSB of word

MOVWF

PROG_DATA_HI

; Store in user location

```

#### 11.6 Write Verify

Depending on the application, good programming practice may dictate that the value written to the data EEPROM or program memory should be verified (see Example 11-6) to the desired value to be written. Example 11-6 shows how to verify a write to EEPROM.

#### **EXAMPLE 11-6: EEPROM WRITE VERIFY**

```

BANKSEL EEDATL ;

MOVF EEDATL, W ;EEDATL not changed ;from previous write

BSF EECON1, RD ;YES, Read the ;value written

XORWF EEDATL, W ;

BTFSS STATUS, Z ;Is data the same

GOTO WRITE_ERR ;No, handle error ;Yes, continue

```

# 17.0 DIGITAL-TO-ANALOG CONVERTER (DAC) MODULE

The Digital-to-Analog Converter supplies a variable voltage reference, ratiometric with the input source, with 32 selectable output levels.

The input of the DAC can be connected to:

- · External VREF pins

- · VDD supply voltage

- FVR (Fixed Voltage Reference)

The output of the DAC can be configured to supply a reference voltage to the following:

- · Comparator positive input

- · ADC input channel

- DACOUT pin

- · Capacitive Sensing module (CSM)

The Digital-to-Analog Converter (DAC) can be enabled by setting the DACEN bit of the DACCON0 register.

#### 17.1 Output Voltage Selection

The DAC has 32 voltage level ranges. The 32 levels are set with the DACR<4:0> bits of the DACCON1 register.

The DAC output voltage is determined by the equations in Equation 17-1.

#### **EQUATION 17-1: DAC OUTPUT VOLTAGE**

#### IF DACEN = 1

$$VOUT = \left( (VSOURCE + - VSOURCE -) \times \frac{DACR[4:0]}{2^5} \right) + VSOURCE - VSOUR$$

#### IF DACEN = 0 and DACLPS = 1 and DACR[4:0] = 11111

VOUT = VSOURCE +

#### IF DACEN = 0 and DACLPS = 0 and DACR[4:0] = 00000

VOUT = VSOURCE -

VSOURCE+ = VDD, VREF, or FVR BUFFER 2

VSOURCE-=VSS

#### 17.2 Ratiometric Output Level

The DAC output value is derived using a resistor ladder with each end of the ladder tied to a positive and negative voltage reference input source. If the voltage of either input source fluctuates, a similar fluctuation will result in the DAC output value.

The value of the individual resistors within the ladder can be found in **Section 29.0** "**Electrical Specifications**".

#### 17.3 DAC Voltage Reference Output

The DAC can be output to the DACOUT pin by setting the DACOE bit of the DACCON0 register to '1'. Selecting the DAC reference voltage for output on the DACOUT pin automatically overrides the digital output buffer and digital input threshold detector functions of that pin. Reading the DACOUT pin when it has been configured for DAC reference voltage output will always return a '0'.

Due to the limited current drive capability, a buffer must be used on the DAC voltage reference output for external connections to DACOUT. Figure 17-2 shows an example buffering technique.

#### 18.0 SR LATCH

The module consists of a single SR Latch with multiple Set and Reset inputs as well as separate latch outputs. The SR Latch module includes the following features:

- · Programmable input selection

- · SR Latch output is available externally

- Separate Q and Q outputs

- · Firmware Set and Reset

The SR Latch can be used in a variety of analog applications, including oscillator circuits, one-shot circuit, hysteretic controllers, and analog timing applications.

#### 18.1 Latch Operation

The latch is a Set-Reset Latch that does not depend on a clock source. Each of the Set and Reset inputs are active-high. The latch can be Set or Reset by:

- Software control (SRPS and SRPR bits)

- Comparator C1 output (SYNCC1OUT)

- Comparator C2 output (SYNCC2OUT)

- SRI pin

- Programmable clock (SRCLK)

The SRPS and the SRPR bits of the SRCON0 register may be used to set or reset the SR Latch, respectively. The latch is Reset-dominant. Therefore, if both Set and Reset inputs are high, the latch will go to the Reset state. Both the SRPS and SRPR bits are self resetting which means that a single write to either of the bits is all that is necessary to complete a latch Set or Reset operation.

The output from Comparator C1 or C2 can be used as the Set or Reset inputs of the SR Latch. The output of either comparator can be synchronized to the Timer1 clock source. See Section 19.0 "Comparator Module" and Section 21.0 "Timer1 Module with Gate Control" for more information.

An external source on the SRI pin can be used as the Set or Reset inputs of the SR Latch.

An internal clock source is available that can periodically set or reset the SR Latch. The SRCLK<2:0> bits in the SRCON0 register are used to select the clock source period. The SRSCKE and SRRCKE bits of the SRCON1 register enable the clock source to set or reset the SR Latch, respectively.

Note:

Enabling both the Set and Reset inputs from any one source at the same time may result in indeterminate operation, as the Reset dominance cannot be assured.

#### 18.2 Latch Output

The SRQEN and SRNQEN bits of the SRCON0 register control the Q and  $\overline{Q}$  latch outputs. Both of the SR Latch outputs may be directly output to an I/O pin at the same time.

The applicable TRIS bit of the corresponding port must be cleared to enable the port pin output driver.

#### 18.3 Effects of a Reset

Upon any device Reset, the SR Latch output is not initialized to a known state. The user's firmware is responsible for initializing the latch output before enabling the output pins.

NOTES:

#### 25.2.6 SPI OPERATION IN SLEEP MODE

In SPI Master mode, module clocks may be operating at a different speed than when in full power mode; in the case of the Sleep mode, all clocks are halted.

Special care must be taken by the user when the MSSPx clock is much faster than the system clock.

In Slave mode, when MSSPx interrupts are enabled, after the master completes sending data, an MSSPx interrupt will wake the controller from Sleep.

If an exit from Sleep mode is not desired, MSSPx interrupts should be disabled.

In SPI Master mode, when the Sleep mode is selected, all module clocks are halted and the transmission/reception will remain in that state until the device wakes. After the device returns to Run mode, the module will resume transmitting and receiving data.

In SPI Slave mode, the SPI Transmit/Receive Shift register operates asynchronously to the device. This allows the device to be placed in Sleep mode and data to be shifted into the SPI Transmit/Receive Shift register. When all 8 bits have been received, the MSSPx interrupt flag bit will be set and if enabled, will wake the device.

TABLE 25-1: SUMMARY OF REGISTERS ASSOCIATED WITH SPI OPERATION

| Name     | Bit 7       | Bit 6           | Bit 5         | Bit 4                 | Bit 3                  | Bit 2  | Bit 1  | Bit 0   | Register on Page |

|----------|-------------|-----------------|---------------|-----------------------|------------------------|--------|--------|---------|------------------|

| APFCON0  | RXDTSEL     | SDO1SEL         | SS1SEL        | P2BSEL <sup>(1)</sup> | CCP2SEL <sup>(1)</sup> | P1DSEL | P1CSEL | CCP1SEL | 119              |

| ANSELA   | _           | _               | _             | ANSA4                 | ANSA3                  | ANSA2  | ANSA1  | ANSA0   | 123              |

| ANSELB   | ANSB7       | ANSB6           | ANSB5         | ANSB4                 | ANSB3                  | ANSB2  | ANSB1  |         | 128              |

| INTCON   | GIE         | PEIE            | TMR0IE        | INTE                  | IOCIE                  | TMR0IF | INTF   | IOCIF   | 86               |

| PIE1     | TMR1GIE     | ADIE            | RCIE          | TXIE                  | SSP1IE                 | CCP1IE | TMR2IE | TMR1IE  | 87               |

| PIR1     | TMR1GIF     | ADIF            | RCIF          | TXIF                  | SSP1IF                 | CCP1IF | TMR2IF | TMR1IF  | 91               |

| SSPxBUF  | Synchronous | s Serial Port F | Receive Buffe | r/Transmit Re         | egister                |        |        |         | 235*             |

| SSPxCON1 | WCOL        | SSPxOV          | SSPxEN        | CKP                   | SSPxM3                 | SSPxM2 | SSPxM1 | SSPxM0  | 280              |

| SSPxCON3 | ACKTIM      | PCIE            | SCIE          | BOEN                  | SDAHT                  | SBCDE  | AHEN   | DHEN    | 282              |

| SSPxSTAT | SMP         | CKE             | D/A           | Р                     | S                      | R/W    | UA     | BF      | 279              |

| TRISA    | TRISA7      | TRISA6          | TRISA5        | TRISA4                | TRISA3                 | TRISA2 | TRISA1 | TRISA0  | 122              |

| TRISB    | TRISB7      | TRISB6          | TRISB5        | TRISB4                | TRISB3                 | TRISB2 | TRISB1 | TRISB0  | 127              |

**Legend:** — = Unimplemented location, read as '0'. Shaded cells are not used by the MSSPx in SPI mode.

Page provides register information.

Note 1: PIC16(L)F1827 only.

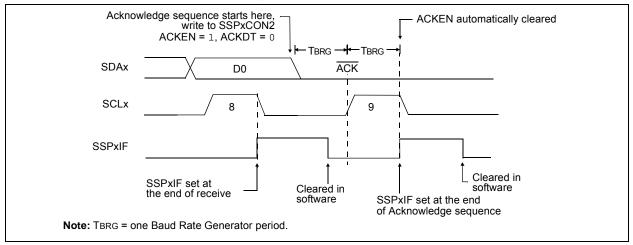

### 25.6.8 ACKNOWLEDGE SEQUENCE TIMING

An Acknowledge sequence is enabled by setting the Acknowledge Sequence Enable bit, ACKEN bit of the SSPxCON2 register. When this bit is set, the SCLx pin is pulled low and the contents of the Acknowledge data bit are presented on the SDAx pin. If the user wishes to generate an Acknowledge, then the ACKDT bit should be cleared. If not, the user should set the ACKDT bit before starting an Acknowledge sequence. The Baud Rate Generator then counts for one rollover period (TBRG) and the SCLx pin is deasserted (pulled high). When the SCLx pin is sampled high (clock arbitration), the Baud Rate Generator counts for TBRG. The SCLx pin is then pulled low. Following this, the ACKEN bit is automatically cleared, the Baud Rate Generator is turned off and the MSSPx module then goes into Idle mode (Figure 25-29).

#### 25.6.8.1 WCOL Status Flag

If the user writes the SSPxBUF when an Acknowledge sequence is in progress, then WCOL is set and the contents of the buffer are unchanged (the write does not occur).

#### 25.6.9 STOP CONDITION TIMING

A Stop bit is asserted on the SDAx pin at the end of a receive/transmit by setting the Stop Sequence Enable bit, PEN bit of the SSPxCON2 register. At the end of a receive/transmit, the SCLx line is held low after the falling edge of the ninth clock. When the PEN bit is set, the master will assert the SDAx line low. When the SDAx line is sampled low, the Baud Rate Generator is reloaded and counts down to '0'. When the Baud Rate Generator times out, the SCLx pin will be brought high and one TBRG (Baud Rate Generator rollover count) later, the SDAx pin will be deasserted. When the SDAx pin is sampled high while SCLx is high, the P bit of the SSPxSTAT register is set. A TBRG later, the PEN bit is cleared and the SSPxIF bit is set (Figure 25-30).

#### 25.6.9.1 WCOL Status Flag

If the user writes the SSPxBUF when a Stop sequence is in progress, then the WCOL bit is set and the contents of the buffer are unchanged (the write does not occur).

FIGURE 25-30: ACKNOWLEDGE SEQUENCE WAVEFORM

### 26.1.2 EUSART ASYNCHRONOUS RECEIVER

The Asynchronous mode is typically used in RS-232 systems. The receiver block diagram is shown in Figure 26-2. The data is received on the RX/DT pin and drives the data recovery block. The data recovery block is actually a high-speed shifter operating at 16 times the baud rate, whereas the serial Receive Shift Register (RSR) operates at the bit rate. When all 8 or 9 bits of the character have been shifted in, they are immediately transferred to a two character First-In-First-Out (FIFO) memory. The FIFO buffering allows reception of two complete characters and the start of a third character before software must start servicing the EUSART receiver. The FIFO and RSR registers are not directly accessible by software. Access to the received data is via the RCREG register.

#### 26.1.2.1 Enabling the Receiver

The EUSART receiver is enabled for asynchronous operation by configuring the following three control bits:

- CREN = 1

- SYNC = 0

- SPEN = 1

All other EUSART control bits are assumed to be in their default state.

Setting the CREN bit of the RCSTA register enables the receiver circuitry of the EUSART. Clearing the SYNC bit of the TXSTA register configures the EUSART for asynchronous operation. Setting the SPEN bit of the RCSTA register enables the EUSART. The programmer must set the corresponding TRIS bit to configure the RX/DT I/O pin as an input.

Note:

If the RX/DT function is on an analog pin, the corresponding ANSEL bit must be cleared for the receiver to function.

#### 26.1.2.2 Receiving Data

The receiver data recovery circuit initiates character reception on the falling edge of the first bit. The first bit, also known as the Start bit, is always a zero. The data recovery circuit counts one-half bit time to the center of the Start bit and verifies that the bit is still a zero. If it is not a zero then the data recovery circuit aborts character reception, without generating an error, and resumes looking for the falling edge of the Start bit. If the Start bit zero verification succeeds then the data recovery circuit counts a full bit time to the center of the next bit. The bit is then sampled by a majority detect circuit and the resulting '0' or '1' is shifted into the RSR. This repeats until all data bits have been sampled and shifted into the RSR. One final bit time is measured and the level sampled. This is the Stop bit, which is always a '1'. If the data recovery circuit samples a '0' in the Stop bit position then a framing error is set for this character, otherwise the framing error is cleared for this character. See Section 26.1.2.4 "Receive Framing Error" for more information on framing errors.

Immediately after all data bits and the Stop bit have been received, the character in the RSR is transferred to the EUSART receive FIFO and the RCIF interrupt flag bit of the PIR1 register is set. The top character in the FIFO is transferred out of the FIFO by reading the RCREG register.

Note:

If the receive FIFO is overrun, no additional characters will be received until the overrun condition is cleared. See **Section 26.1.2.5** "**Receive Overrun Error**" for more information on overrun errors.

#### 26.1.2.3 Receive Interrupts

The RCIF interrupt flag bit of the PIR1 register is set whenever the EUSART receiver is enabled and there is an unread character in the receive FIFO. The RCIF interrupt flag bit is read-only, it cannot be set or cleared by software.

RCIF interrupts are enabled by setting all of the following bits:

- · RCIE interrupt enable bit of the PIE1 register

- PEIE peripheral interrupt enable bit of the INTCON register

- GIE global interrupt enable bit of the INTCON register

The RCIF interrupt flag bit will be set when there is an unread character in the FIFO, regardless of the state of interrupt enable bits.

#### REGISTER 26-2: RCSTA: RECEIVE STATUS AND CONTROL REGISTER<sup>(1)</sup>

| R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R-0/0 | R-0/0 | R-0/0 |

|---------|---------|---------|---------|---------|-------|-------|-------|

| SPEN    | RX9     | SREN    | CREN    | ADDEN   | FERR  | OERR  | RX9D  |

| bit 7   |         |         |         |         |       |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared

bit 7 SPEN: Serial Port Enable bit

1 = Serial port enabled (configures RX/DT and TX/CK pins as serial port pins)

0 = Serial port disabled (held in Reset)

bit 6 **RX9:** 9-bit Receive Enable bit

1 = Selects 9-bit reception

0 = Selects 8-bit reception

bit 5 SREN: Single Receive Enable bit

Asynchronous mode:

Don't care

Synchronous mode – Master:

1 = Enables single receive

0 = Disables single receive

This bit is cleared after reception is complete.

Synchronous mode - Slave

Don't care

bit 4 CREN: Continuous Receive Enable bit

Asynchronous mode:

1 = Enables receiver

0 = Disables receiver

Synchronous mode:

1 = Enables continuous receive until enable bit CREN is cleared (CREN overrides SREN)

0 = Disables continuous receive

bit 3 ADDEN: Address Detect Enable bit

Asynchronous mode 9-bit (RX9 = 1):

1 = Enables address detection, enable interrupt and load the receive buffer when RSR<8> is set

0 = Disables address detection, all bytes are received and ninth bit can be used as parity bit

Asynchronous mode 8-bit (RX9 = 0):

Don't care

bit 2 **FERR:** Framing Error bit

1 = Framing error (can be updated by reading RCREG register and receive next valid byte)

0 = No framing error

bit 1 **OERR:** Overrun Error bit

1 = Overrun error (can be cleared by clearing bit CREN)

0 = No overrun error

bit 0 **RX9D:** Ninth bit of Received Data

This can be address/data bit or a parity bit and must be calculated by user firmware.

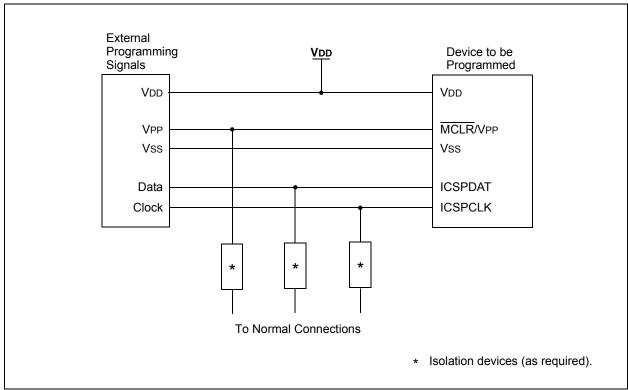

For additional interface recommendations, refer to your specific device programmer manual prior to PCB design.

It is recommended that isolation devices be used to separate the programming pins from other circuitry. The type of isolation is highly dependent on the specific application and may include devices such as resistors, diodes, or even jumpers. See Figure 28-4 for more information.

FIGURE 28-4: TYPICAL CONNECTION FOR ICSP™ PROGRAMMING

#### 30.4 DC Characteristics: PIC16(L)F1826/27-I/E

|              | DC CI | HARACTERISTICS                       | Standard Operating Conditions (unless otherwise stated)<br>Operating temperature -40°C $\leq$ TA $\leq$ +85°C for industrial<br>-40°C $\leq$ TA $\leq$ +125°C for extended |      |          |       |                                                                         |  |  |

|--------------|-------|--------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|----------|-------|-------------------------------------------------------------------------|--|--|

| Param<br>No. | Sym.  | Characteristic                       | Min.                                                                                                                                                                       | Тур† | Max.     | Units | Conditions                                                              |  |  |

|              | VIL   | Input Low Voltage                    |                                                                                                                                                                            |      |          |       |                                                                         |  |  |

|              |       | I/O PORT:                            |                                                                                                                                                                            |      |          |       |                                                                         |  |  |

| D030         |       | with TTL buffer                      | _                                                                                                                                                                          | _    | 0.8      | V     | $4.5V \le VDD \le 5.5V$                                                 |  |  |

| D030A        |       |                                      | _                                                                                                                                                                          | _    | 0.15 VDD | V     | $1.8V \le VDD \le 4.5V$                                                 |  |  |

| D031         |       | with Schmitt Trigger buffer          | _                                                                                                                                                                          | _    | 0.2 VDD  | V     | $2.0V \le VDD \le 5.5V$                                                 |  |  |

|              |       | with I <sup>2</sup> C™ levels        | _                                                                                                                                                                          | _    | 0.3 VDD  | V     |                                                                         |  |  |

|              |       | with SMBus™ levels                   | _                                                                                                                                                                          | _    | 0.8      | V     | $2.7V \le VDD \le 5.5V$                                                 |  |  |

| D032         |       | MCLR, OSC1 (RC mode) <sup>(1)</sup>  | _                                                                                                                                                                          | _    | 0.2 VDD  | V     |                                                                         |  |  |

| D033         |       | OSC1 (HS mode)                       | _                                                                                                                                                                          | _    | 0.3 VDD  | V     |                                                                         |  |  |

|              | VIH   | Input High Voltage                   | <u>,                                      </u>                                                                                                                             |      |          |       |                                                                         |  |  |

|              |       | I/O ports:                           |                                                                                                                                                                            | _    | _        |       |                                                                         |  |  |

| D040         |       | with TTL buffer                      | 2.0                                                                                                                                                                        | _    | _        | V     | 4.5V ≤ VDD ≤ 5.5V                                                       |  |  |

| D040A        |       |                                      | 0.25 VDD + 0.8                                                                                                                                                             | _    | _        | V     | $1.8V \le VDD \le 4.5V$                                                 |  |  |

| D041         |       | with Schmitt Trigger buffer          | 0.8 VDD                                                                                                                                                                    | _    | _        | V     | 2.0V ≤ VDD ≤ 5.5V                                                       |  |  |

|              |       | with I <sup>2</sup> C™ levels        | 0.7 VDD                                                                                                                                                                    | _    | _        | V     |                                                                         |  |  |

|              |       | with SMBus™ levels                   | 2.1                                                                                                                                                                        | _    | _        | V     | 2.7V ≤ VDD ≤ 5.5V                                                       |  |  |

| D042         |       | MCLR                                 | 0.8 VDD                                                                                                                                                                    | _    | _        | V     |                                                                         |  |  |

| D043A        |       | OSC1 (HS mode)                       | 0.7 VDD                                                                                                                                                                    | _    | _        | V     |                                                                         |  |  |

| D043B        |       | OSC1 (RC mode)                       | 0.9 VDD                                                                                                                                                                    | _    | _        | V     | (Note 1)                                                                |  |  |

|              | lıL   | Input Leakage Current <sup>(2)</sup> |                                                                                                                                                                            |      | 1        |       | ,                                                                       |  |  |

| D060         |       | I/O ports                            | _                                                                                                                                                                          | ± 5  | ± 100    | nA    | Vss ≤ VPIN ≤ VDD, Pin at high-<br>impedance at 85°C                     |  |  |

|              |       |                                      |                                                                                                                                                                            | ± 5  | ± 1000   | nA    | 125°C                                                                   |  |  |

| D061         |       | MCLR <sup>(3)</sup>                  | _                                                                                                                                                                          | ± 50 | ± 200    | nA    | Vss ≤ Vpin ≤ Vdd at 85°C                                                |  |  |

|              | IPUR  | Weak Pull-up Current                 |                                                                                                                                                                            |      |          |       |                                                                         |  |  |

| D070*        |       |                                      | 25                                                                                                                                                                         | 100  | 200      |       | VDD = 3.3V, VPIN = VSS                                                  |  |  |

|              |       | /A                                   | 25                                                                                                                                                                         | 140  | 300      | μΑ    | VDD = 5.0V, VPIN = VSS                                                  |  |  |

|              | VOL   | Output Low Voltage <sup>(4)</sup>    | 1                                                                                                                                                                          |      | 1        | 1     |                                                                         |  |  |

| D080         |       | I/O ports                            | _                                                                                                                                                                          | _    | 0.6      | V     | IOL = 8mA, VDD = 5V<br>IOL = 6mA, VDD = 3.3V<br>IOL = 1.8mA, VDD = 1.8V |  |  |

|              | Voн   | Output High Voltage <sup>(4)</sup>   | <u>.                                      </u>                                                                                                                             |      | 1        | 1     | , -                                                                     |  |  |

| D090         |       | I/O ports                            | VDD - 0.7                                                                                                                                                                  | _    | _        | V     | IOH = 3.5mA, VDD = 5V<br>IOH = 3mA, VDD = 3.3V<br>IOH = 1mA, VDD = 1.8V |  |  |

|              |       | Capacitive Loading Specs on          | Output Pins                                                                                                                                                                |      | 1        | 1     | , -                                                                     |  |  |

| D101*        | COSC2 | OSC2 pin                             |                                                                                                                                                                            | _    | 15       | pF    | In XT, HS and LP modes when external clock is used to drive OSC1        |  |  |

| D101A*       | Cio   | All I/O pins                         |                                                                                                                                                                            |      | 50       | pF    |                                                                         |  |  |

| PIOIN        | CIU   | All I/O pills                        |                                                                                                                                                                            |      | 50       | þι    |                                                                         |  |  |

<sup>\*</sup> These parameters are characterized but not tested.

<sup>†</sup> Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: In RC oscillator configuration, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended to use an external clock in RC mode.

<sup>2:</sup> Negative current is defined as current sourced by the pin.

<sup>3:</sup> The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

<sup>4:</sup> Including OSC2 in CLKOUT mode.

#### TABLE 30-6: TIMERO AND TIMER1 EXTERNAL CLOCK REQUIREMENTS

Standard Operating Conditions (unless otherwise stated) Operating Temperature -40°C ≤ TA ≤ +125°C **Param** Characteristic Min. Units **Conditions** Sym. Typ† Max. No. 40\* Тт0Н T0CKI High Pulse Width No Prescaler 0.5 Tcy + 20 ns With Prescaler 10 ns 41\* TT0L T0CKI Low Pulse Width No Prescaler 0.5 Tcy + 20 ns With Prescaler 10 ns 42\* Тт0Р T0CKI Period Greater of: ns N = prescale value 20 or TCY + 40 (2, 4, ..., 256) 45\* TT1H T1CKI High Synchronous, No Prescaler 0.5 Tcy + 20ns Time Synchronous, 15 ns with Prescaler Asynchronous 30 ns 46\* TT1L T1CKI Low Synchronous, No Prescaler 0.5 Tcy + 20 ns Time Synchronous, with Prescaler 15 ns 30 Asynchronous ns 47\* TT1P T1CKI Input Synchronous Greater of: ns Period 30 or TCY + 40 Ν 60 Asynchronous ns 48 FT1 Timer1 Oscillator Input Frequency Range 32.768 33.1 kHz 32.4 (oscillator enabled by setting bit T1OSCEN) 49\* TCKEZTMR1 Delay from External Clock Edge to Timer 2 Tosc 7 Tosc Timers in Sync Increment mode

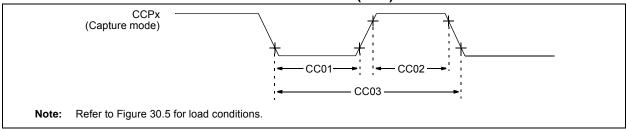

#### FIGURE 30-11: CAPTURE/COMPARE/PWM TIMINGS (CCP)

#### TABLE 30-7: CAPTURE/COMPARE/PWM REQUIREMENTS (CCP)

|              | •    | ating Conditions (unless perature $-40^{\circ}$ C $\leq$ TA $\leq$ +12 |                | 1)             |      |      |       |                                 |

|--------------|------|------------------------------------------------------------------------|----------------|----------------|------|------|-------|---------------------------------|

| Param<br>No. | Sym. | Characteris                                                            | stic           | Min.           | Тур† | Max. | Units | Conditions                      |

| CC01*        | TccL | CCPx Input Low Time                                                    | No Prescaler   | 0.5Tcy + 20    | _    | _    | ns    |                                 |

|              |      |                                                                        | With Prescaler | 20             | _    | _    | ns    |                                 |

| CC02*        | TccH | CCPx Input High Time                                                   | No Prescaler   | 0.5Tcy + 20    | _    | _    | ns    |                                 |

|              |      |                                                                        | With Prescaler | 20             | _    | _    | ns    |                                 |

| CC03*        | TccP | CCPx Input Period                                                      |                | 3Tcy + 40<br>N | _    | _    | ns    | N = prescale value (1, 4 or 16) |

<sup>\*</sup> These parameters are characterized but not tested.

<sup>\*</sup> These parameters are characterized but not tested.

<sup>†</sup> Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

<sup>†</sup> Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

#### 32.0 DEVELOPMENT SUPPORT

The PIC® microcontrollers and dsPIC® digital signal controllers are supported with a full range of software and hardware development tools:

- · Integrated Development Environment

- MPLAB® IDE Software

- · Compilers/Assemblers/Linkers

- MPLAB C Compiler for Various Device Families

- HI-TECH C for Various Device Families

- MPASM™ Assembler

- MPLINK<sup>TM</sup> Object Linker/ MPLIB<sup>TM</sup> Object Librarian

- MPLAB Assembler/Linker/Librarian for Various Device Families

- Simulators

- MPLAB SIM Software Simulator

- Emulators

- MPLAB REAL ICE™ In-Circuit Emulator

- · In-Circuit Debuggers

- MPLAB ICD 3

- PICkit™ 3 Debug Express

- · Device Programmers

- PICkit™ 2 Programmer

- MPLAB PM3 Device Programmer

- Low-Cost Demonstration/Development Boards, Evaluation Kits, and Starter Kits

### 32.1 MPLAB Integrated Development Environment Software

The MPLAB IDE software brings an ease of software development previously unseen in the 8/16/32-bit microcontroller market. The MPLAB IDE is a Windows® operating system-based application that contains:

- · A single graphical interface to all debugging tools

- Simulator

- Programmer (sold separately)

- In-Circuit Emulator (sold separately)

- In-Circuit Debugger (sold separately)

- · A full-featured editor with color-coded context

- · A multiple project manager

- Customizable data windows with direct edit of contents

- · High-level source code debugging

- · Mouse over variable inspection

- Drag and drop variables from source to watch windows

- · Extensive on-line help

- Integration of select third party tools, such as IAR C Compilers

The MPLAB IDE allows you to:

- Edit your source files (either C or assembly)

- One-touch compile or assemble, and download to emulator and simulator tools (automatically updates all project information)

- · Debug using:

- Source files (C or assembly)

- Mixed C and assembly

- Machine code

MPLAB IDE supports multiple debugging tools in a single development paradigm, from the cost-effective simulators, through low-cost in-circuit debuggers, to full-featured emulators. This eliminates the learning curve when upgrading to tools with increased flexibility and power.

| Steering Synchronization                                       | . 224 | PIE3 (Peripheral Interrupt Enable 3)   | 89              |

|----------------------------------------------------------------|-------|----------------------------------------|-----------------|

| PWM Mode. See Enhanced Capture/Compare/PWM                     | 212   | PIE4 (Peripheral Interrupt Enable 4)   |                 |

| PWM Steering                                                   | . 223 | PIR1 (Peripheral Interrupt Register 1) |                 |

| PWMxCON Register                                               | . 229 | PIR2 (Peripheral Interrupt Request 2)  |                 |

| R                                                              |       | PIR3 (Peripheral Interrupt Request 3)  |                 |

|                                                                |       | PIR4 (Peripheral Interrupt Request 4)  |                 |

| RCREG                                                          |       | PORTA                                  |                 |

| RCREG Register                                                 |       | PORTB                                  |                 |

| RCSTA Register                                                 |       | PSTRxCON (PWM Steering Control)        |                 |

| Reader Response                                                |       | PWMxCON (Enhanced PWM Control)         |                 |

| Read-Modify-Write Operations                                   |       | RCREG                                  |                 |

| Reference Clock                                                |       | RCSTA (Receive Status and Control)     |                 |

| Associated Registers                                           | 71    | SPBRGH                                 |                 |

| Registers                                                      |       | SPBRGL                                 |                 |

| ADCON0 (ADC Control 0)                                         |       | Special Function, Summary              |                 |

| ADCON1 (ADC Control 1)                                         |       | SRCON0 (SR Latch Control 0)            |                 |

| ADRESH (ADC Result High) with ADFM = 0)                        |       | SRCON1 (SR Latch Control 1)            | 160             |

| ADRESH (ADC Result High) with ADFM = 1)                        |       | SSPxADD (MSSPx Address and Baud Rate,  |                 |

| ADRESL (ADC Result Low) with ADFM = 0)                         |       | I <sup>2</sup> C Mode)                 |                 |

| ADRESL (ADC Result Low) with ADFM = 1)                         |       | SSPxCON1 (MSSPx Control 1)             |                 |

| ANSELA (PORTA Analog Select)                                   |       | SSPxCON2 (SSPx Control 2)              |                 |

| ANSELB (PORTB Analog Select)                                   |       | SSPxCON3 (SSPx Control 3)              |                 |

| APECONA (Alternate Pin Function Control 0)                     |       | SSPxMSK (SSPx Mask)                    |                 |

| APFCON1 (Alternate Pin Function Control 1)                     |       | SSPxSTAT (SSPx Status)                 |                 |

| BAUDCON (Baud Rate Control)                                    |       | STATUS                                 |                 |

| BORCON Brown-out Reset Control)                                |       | T1CON (Timer1 Control)                 |                 |

| CCPTMRS (PWM Timer Selection Control)                          |       | T1GCON (Timer1 Gate Control)           |                 |

| CCPxAS (CCPx Auto-Shutdown Control)<br>CCPxCON (ECCPx Control) |       | TRISA (Tri-State PORTA)                |                 |

| ,                                                              |       | TRISB (Tri-State PORTB)                |                 |

| CLKRCON (Reference Clock Control)<br>CMOUT (Comparator Output) |       | TXCON                                  |                 |

| CMxCON0 (Cx Control)                                           |       | TXSTA (Transmit Status and Control)    |                 |

| CMxCON1 (Cx Control 1)                                         |       | WDTCON (Watchdog Timer Control)        |                 |

| Configuration Word 1                                           |       | WPUB (Weak Pull-up PORTB)RESET         |                 |

| Configuration Word 2                                           |       |                                        |                 |

| Core Function, Summary                                         |       | Reset Instruction                      |                 |

| CPSCON0 (Capacitive Sensing Control Register 0)                |       | Reset InstructionResets                |                 |

| CPSCON1 (Capacitive Sensing Control Register 1)                |       | Associated Registers                   |                 |

| DACCONO                                                        |       | Revision History                       |                 |

| DACCON1                                                        |       | revision mistory                       | 55.             |

| Device ID                                                      |       | S                                      |                 |

| EEADRL (EEPROM Address)                                        |       | Shoot-through Current                  | 22              |

| EECON1 (EEPROM Control 1)                                      |       | Software Simulator (MPLAB SIM)         |                 |

| EECON2 (EEPROM Control 2)                                      |       | SPBRG Register                         |                 |

| EEDATH (EEPROM Data)113,                                       |       | SPBRGH Register                        |                 |

| EEDATL (EEPROM Data)                                           | .113  | SPBRGL Register                        |                 |

| FVRCON                                                         |       | Special Event Trigger                  |                 |

| INTCON (Interrupt Control)                                     | 86    | Special Function Registers (SFRs)      | 28              |

| IOCBF (Interrupt-on-Change Flag)                               |       | SPI Mode (MSSPx)                       |                 |

| IOCBN (Interrupt-on-Change Negative Edge)                      | 132   | Associated Registers                   | 24              |

| IOCBP (Interrupt-on-Change Positive Edge)                      | 132   | SPI Clock                              |                 |

| LATA (Data Latch PORTA)                                        |       | SR Latch                               | 15 <sup>-</sup> |

| LATB (Data Latch PORTB)                                        | . 127 | Associated registers w/ SR Latch       | 16 <sup>-</sup> |

| MDCARH (Modulation High Carrier Control                        |       | SRCON0 Register                        | 159             |

| Register)                                                      | . 200 | SRCON1 Register                        | 160             |

| MDCARL (Modulation Low Carrier Control Register)               | 201   | SSP1ADD Register                       | 30              |

| MDCON (Modulation Control Register)                            |       | SSP1BUF Register                       | 30              |

| MDSRC (Modulation Source Control Register)                     | 199   | SSP1CON Register                       |                 |

| OPTION_REG (OPTION)                                            | . 176 | SSP1CON2 Register                      | 30              |

| OSCCON (Oscillator Control)                                    | 65    | SSP1CON3 Register                      | 30              |

| OSCSTAT (Oscillator Status)                                    | 66    | SSP1MSK Register                       | 30              |

| OSCTUNE (Oscillator Tuning)                                    | 67    | SSP1STAT Register                      | 30              |

| PCON (Power Control Register)                                  | 79    | SSP2ADD Register                       | 30              |

| PCON (Power Control)                                           | 79    | SSP2BUF Register                       | 30              |

| PIE1 (Peripheral Interrupt Enable 1)                           | 87    | SSP2CON1 Register                      |                 |

| PIE2 (Peripheral Interrupt Enable 2)                           | 88    | SSP2CON2 Register                      | 30              |