Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 32MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 16                                                                        |

| Program Memory Size        | 3.5KB (2K x 14)                                                           |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 256 x 8                                                                   |

| RAM Size                   | 256 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                               |

| Data Converters            | A/D 12x10b                                                                |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

| Mounting Type              | Through Hole                                                              |

| Package / Case             | 18-DIP (0.300", 7.62mm)                                                   |

| Supplier Device Package    | 18-PDIP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1826-e-p |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| NameFunctionInput<br>TypeOutput<br>TypeDescriptionRA0/AN0/CPS0/C12IN0-/<br>SDO2 <sup>(2)</sup> RA0TTLCMOSGeneral purpose I/O.AN0AN-A/D Channel 0 input.CPS0AN-Capacitive sensing input 0.C12IN0-AN-Comparator C1 or C2 negative input.SDO2-CMOSSPI data output.RA1/AN1/CPS1/C12IN1-/SS2 <sup>(2)</sup> RA1TTLCMOSRA1/AN1/CPS1/C12IN1-/SS2 <sup>(2)</sup> RA1-Capacitive sensing input 1.C12IN1-AN-Capacitive sensing input 1.C12IN1-AN-Capacitive sensing input 2.RA2/AN2/CPS2/C12IN2-/<br>C12IN+/VREF-/DACOUTRA2TTLC12IN+/VREF-/DACOUTAN-A/D Channel 2 input.C12IN+/VREF-/DACOUTRA2TTLCMOSGeneral purpose I/OAN-C12IN2-AN-Comparator C1 or C2 negative input.C12IN2-AN-Comparator C1 or C2 negative input.C12IN2-AN-A/D Negative Voltage Reference input.VREF+AN-CApacitive sen                                                                                                                                                                                                |   |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| SD02 <sup>(2)</sup> AN0         AN         —         A/D Channel 0 input.           CPS0         AN         —         Capacitive sensing input 0.           C12IN0-         AN         —         Comparator C1 or C2 negative input.           SD02         —         CMOS         SPI data output.           RA1/AN1/CPS1/C12IN1-/SS2 <sup>(2)</sup> RA1         TTL         CMOS         General purpose I/O.           AN1         AN         —         Capacitive sensing input 1.         C           C12IN1-         AN         —         Comparator C1 or C2 negative input.           C12IN+/VREF-/DACOUT         RA2         TTL         CMOS         General purpose I/O.           AN2         AN         —         Capacitive sensing input 2.         C12IN+         AN         —         Capacitive sensing input 2.           C12IN+         AN         —         Comparator C1                                          |   |

| ANU       AN       —       AD Craniner Origin.         CPS0       AN       —       Capacitive sensing input 0.         C12IN0-       AN       —       Comparator C1 or C2 negative input.         SD02       —       CMOS       SPI data output.         RA1/AN1/CPS1/C12IN1-/SS2 <sup>(2)</sup> RA1       TTL       CMOS       General purpose I/O.         AN1       AN       —       A/D Channel 1 input.         CPS1       AN       —       Capacitive sensing input 1.         C12IN1-       AN       —       Capacitive sensing input 1.         C12IN1-       AN       —       Capacitive sensing input 1.         C12IN1-       AN       —       Capacitive sensing input 1.         C12IN1-/VREF-/DACOUT       RA2       TTL       CMOS         AN2       AN       —       Capacitive sensing input 2.         C12IN+/VREF-/DACOUT       RA2       TL       CMOS       General purpose I/O.         C12IN2-       AN       —       Comparator C1 or C2 negative input.         C12IN2-       AN       —       Capacitive sensing input 2.         C12IN2-       AN       —       Comparator C1 or C2 negative input.         VREF-       AN       —       A/                                                                                                                      |   |

| C12IN0-       AN       —       Comparator C1 or C2 negative input.         SD02       —       CMOS       SPI data output.         RA1/AN1/CPS1/C12IN1-/SS2 <sup>(2)</sup> RA1       TTL       CMOS       General purpose I/O.         AN1       AN       —       A/D Channel 1 input.         CPS1       AN       —       Capacitive sensing input 1.         C12IN1-       AN       —       Comparator C1 or C2 negative input.         C12IN+/VREF-/DACOUT       RA2       TTL       CMOS       General purpose I/O.         AN2       AN       —       A/D Channel 2 input.       C12IN2         C12IN+/VREF-/DACOUT       AN       —       Comparator C1 or C2 negative input.         C12IN+       AN       —       Comparator C1 or C2 negative input.         C12IN+       AN       —       Comparator C1 or C2 negative input.                                                                                                       |   |

| SD02       —       CMOS       SPI data output.         RA1/AN1/CPS1/C12IN1-/SS2 <sup>(2)</sup> RA1       TTL       CMOS       General purpose I/O.         AN1       AN       —       A/D Channel 1 input.         CPS1       AN       —       Capacitive sensing input 1.         C12IN1-       AN       —       Capacitive sensing input 1.         C12IN1-       AN       —       Capacitive sensing input 1.         C12IN1-       AN       —       Comparator C1 or C2 negative input.         SS2       ST       —       Slave Select input 2.         RA2/AN2/CPS2/C12IN2-/       RA2       TTL       CMOS         C12IN+/VREF-/DACOUT       RA2       TTL       CMOS         AN2       AN       —       A/D Channel 2 input.         C12IN+/VREF-/DACOUT       RA2       AN       —         AN2       AN       —       Capacitive sensing input 2.         C12IN+       AN       —       Comparator C1 or C2 negative input.         C12IN+       AN       —       Comparator C1 or C2 positive input.         VREF-       AN       —       A/D Nolage Reference output.         RA3/AN3/CPS3/C12IN3-/C1IN+/       RA3       TTL       CMOS       General purp                                                                                                                      |   |

| RA1/AN1/CPS1/C12IN1-/SS2 <sup>(2)</sup> RA1       TTL       CMOS       General purpose I/O.         AN1       AN       —       A/D Channel 1 input.         CPS1       AN       —       Capacitive sensing input 1.         C12IN1-       AN       —       Capacitive sensing input 1.         C12IN1-       AN       —       Comparator C1 or C2 negative input.         SS2       ST       —       Slave Select input 2.         RA2/AN2/CPS2/C12IN2-/<br>C12IN+/VREF-/DACOUT       RA2       TTL       CMOS       General purpose I/O.         AN2       AN       —       Capacitive sensing input 2.       C12IN+/VREF-/DACOUT       CPS2       AN       —       Capacitive sensing input 2.         C12IN+/VREF-/DACOUT       RA2       AN       —       Capacitive sensing input 2.       C12IN-         C12IN+       AN       —       Comparator C1 or C2 negative input.       C12IN+       AN       —       Comparator C1 or C2 positive input.         VREF-       AN       —       A/D Negative Voltage Reference input.       DACOUT       —       A/D Channel 3 input.         VREF+/C10UT/CCP3 <sup>(2)</sup> /SRQ       RA3       TTL       CMOS       General purpose I/O.         VREF+       AN       —       Comparator C1 or C2 negative inpu                           |   |

| AN1       AN       —       A/D Channel 1 input.         CPS1       AN       —       Capacitive sensing input 1.         C12IN1-       AN       —       Comparator C1 or C2 negative input.         SS2       ST       —       Slave Select input 2.         RA2/AN2/CPS2/C12IN2-/<br>C12IN+/VREF-/DACOUT       RA2       TTL       CMOS       General purpose I/O.         AN2       AN       —       A/D Channel 2 input.         CPS2       AN       —       Capacitive sensing input 2.         C12IN+/VREF-/DACOUT       AN2       AN       —       Capacitive sensing input 2.         C12IN+/VREF-/DACOUT       AN2       AN       —       Capacitive sensing input 2.         C12IN+/VREF-/DACOUT       AN2       AN       —       Comparator C1 or C2 negative input.         CPS2       AN       —       Comparator C1 or C2 positive input.       C12IN+         VREF-       AN       —       A/D Negative Voltage Reference input.         DACOUT       —       AN       Voltage Reference output.         RA3/AN3/CPS3/C12IN3-/C1IN+/<br>VREF+/C1OUT/CCP3 <sup>(2)</sup> /SRQ       RA3       TTL       CMOS         AN3       AN       —       A/D Channel 3 input.       CPS3         CPS3       AN                                                                           |   |

| CPS1AN—Capacitive sensing input 1.C12IN1-AN—Comparator C1 or C2 negative input.SS2ST—Slave Select input 2.RA2/AN2/CPS2/C12IN2-/<br>C12IN+/VREF-/DACOUTRA2TTLCMOSGeneral purpose I/O.AN2AN—A/D Channel 2 input.CPS2AN—Capacitive sensing input 2.C12IN+/VREF-/DACOUTAN2AN—Capacitive sensing input 2.C12IN-C12IN-AN—Comparator C1 or C2 negative input.C12IN-AN—Comparator C1 or C2 negative input.C12IN+AN—Comparator C1 or C2 positive input.VREF-AN—A/D Negative Voltage Reference input.DACOUT—ANVoltage Reference output.RA3/AN3/CPS3/C12IN3-/C1IN+/<br>VREF+/C1OUT/CCP3 <sup>(2)</sup> /SRQAN3AN—AN3AN—Capacitive sensing input 3.C12IN3-AN—Comparator C1 or C2 negative input.CPS3AN—Comparator C1 or C2 negative input.C12IN3-AN—Comparator C1 or C2 negative input.C12IN3-AN—Comparator C1 or C2 negative input.C12IN3-AN—Comparator C1 or C2 negative input.VREF+AN—A/D Voltage Reference input.                                                                                                                                                                                                                                                                                                                                                                                   |   |

| C12IN1-AN—Comparator C1 or C2 negative input.SS2ST—Slave Select input 2.RA2/AN2/CPS2/C12IN2-/<br>C12IN+/VREF-/DACOUTRA2TTLCMOSGeneral purpose I/O.AN2AN—A/D Channel 2 input.CPS2AN—C12IN2-AN—Capacitive sensing input 2.C12IN2-AN—Comparator C1 or C2 negative input.C12IN2-AN—Comparator C1 or C2 negative input.C12IN2-AN—Comparator C1 or C2 negative input.C12IN2-AN—Comparator C1 or C2 negative input.VREF-AN—A/D Negative Voltage Reference input.DACOUT—ANVoltage Reference output.RA3/AN3/CPS3/C12IN3-/C1IN+/<br>VREF+/C10UT/CCP3 <sup>(2)</sup> /SRQRA3TTLCPS3AN—A/D Channel 3 input.CPS3AN—Capacitive sensing input 3.C12IN3-AN—Comparator C1 or C2 negative input.VREF+AN—Comparator C1 or C2 negative input.VREF+AN—Comparator C1 or C2 negative input.VREF+AN—A/D Voltage Reference input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |   |

| RA2/AN2/CPS2/C12IN2-/<br>C12IN+/VREF-/DACOUT       RA2       TTL       CMOS       General purpose I/O.         AN2       AN       —       A/D Channel 2 input.         CPS2       AN       —       Capacitive sensing input 2.         C12IN+/VREF-/DACOUT       CPS2       AN       —       Capacitive sensing input 2.         C12IN2-       AN       —       Capacitive sensing input 2.         C12IN2-       AN       —       Comparator C1 or C2 negative input.         C12IN4       AN       —       Comparator C1 or C2 positive input.         VREF-       AN       —       A/D Negative Voltage Reference input.         DACOUT       —       AN       Voltage Reference output.         RA3/AN3/CPS3/C12IN3-/C1IN+/<br>VREF+/C1OUT/CCP3 <sup>(2)</sup> /SRQ       RA3       TTL       CMOS       General purpose I/O.         RA3/AN3/CPS3/C12IN3-/C1IN+/<br>VREF+/C1OUT/CCP3 <sup>(2)</sup> /SRQ       AN3       AN       —       A/D Channel 3 input.         CPS3       AN       —       Capacitive sensing input 3.       C12IN3-       AN       —         C12IN3-       AN       —       Comparator C1 or C2 negative input.       C11N+       AN       —         C12IN3-       AN       —       Comparator C1 or C2 negative input.       C11N+ <t< td=""><td>-</td></t<> | - |

| RA2/AN2/CPS2/C12IN2-/<br>C12IN+/VREF-/DACOUTRA2TTLCMOSGeneral purpose I/O.AN2AN—A/D Channel 2 input.CPS2AN—Capacitive sensing input 2.C12IN2-AN—Comparator C1 or C2 negative input.C12IN2-AN—Comparator C1 or C2 positive input.VREF-AN—A/D Negative Voltage Reference input.VREF-AN—A/D Negative Voltage Reference input.DACOUT—ANVoltage Reference output.RA3/AN3/CPS3/C12IN3-/C1IN+/<br>VREF+/C10UT/CCP3 <sup>(2)</sup> /SRQRA3TTLCMOSGeneral purpose I/O.CPS3AN—CPS3AN—C12IN3-AN—C12IN3-AN—C12IN3-AN—C12IN3-AN—C12IN3-AN—C11N+AN—Comparator C1 or C2 negative input.C11N+AN—Comparator C1 positive input.VREF+AN—A/D Voltage Reference input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |   |

| C12IN+/VREF-/DACOUT       AN2       AN       —       A/D Channel 2 input.         CPS2       AN       —       Capacitive sensing input 2.         C12IN2-       AN       —       Comparator C1 or C2 negative input.         C12IN+       AN       —       Comparator C1 or C2 positive input.         C12IN+       AN       —       Comparator C1 or C2 positive input.         VREF-       AN       —       A/D Negative Voltage Reference input.         DACOUT       —       AN       Voltage Reference output.         RA3/AN3/CPS3/C12IN3-/C1IN+/       RA3       TTL       CMOS         VREF+/C1OUT/CCP3 <sup>(2)</sup> /SRQ       AN3       AN       —         AN3       AN       —       Capacitive sensing input 3.         C12IN3-       AN       —       Comparator C1 or C2 negative input.         CPS3       AN       —       Capacitive sensing input 3.         C12IN3-       AN       —       Comparator C1 or C2 negative input.         C1IN+       AN       —       Comparator C1 or C2 negative input.                                                                                                                                                                                                                                                                |   |

| ANZAN—AND Chainler 2 input.CPS2AN—Capacitive sensing input 2.C12IN2-AN—Comparator C1 or C2 negative input.C12IN+AN—Comparator C1 or C2 positive input.VREF-AN—A/D Negative Voltage Reference input.DACOUT—ANVoltage Reference output.DACOUT—ANVoltage Reference output.CPS3AN—A/D Channel 3 input.CPS3AN—Capacitive sensing input 3.C12IN3-AN—Comparator C1 or C2 negative input.CPS3AN—Capacitive sensing input 3.C12IN3-AN—Comparator C1 or C2 negative input.VREF+AN—Comparator C1 or C2 negative input.VREF+AN—A/D Voltage Reference input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |   |

| C12IN2-       AN       —       Comparator C1 or C2 negative input.         C12IN+       AN       —       Comparator C1 or C2 positive input.         VREF-       AN       —       A/D Negative Voltage Reference input.         DACOUT       —       AN       Voltage Reference output.         RA3/AN3/CPS3/C12IN3-/C1IN+/       RA3       TTL       CMOS         VREF+/C1OUT/CCP3 <sup>(2)</sup> /SRQ       AN3       AN       —         AN3       AN       —       Capacitive sensing input.         CPS3       AN       —       Capacitive sensing input 3.         C12IN3-       AN       —       Comparator C1 or C2 negative input.         VREF+       AN       —       Comparator C1 or C2 negative input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |   |

| C12IN+       AN       —       Comparator C1 or C2 positive input.         VREF-       AN       —       A/D Negative Voltage Reference input.         DACOUT       —       AN       Voltage Reference output.         RA3/AN3/CPS3/C12IN3-/C1IN+/<br>VREF+/C1OUT/CCP3 <sup>(2)</sup> /SRQ       RA3       TTL       CMOS         General purpose I/O.       AN3       AN       —       A/D Channel 3 input.         CPS3       AN       —       Capacitive sensing input 3.         C12IN3-       AN       —       Comparator C1 or C2 negative input.         C1IN+       AN       —       Comparator C1 or C2 negative input.         VREF+       AN       —       A/D Voltage Reference input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |   |

| VREF-       AN       —       A/D Negative Voltage Reference input.         DACOUT       —       AN       Voltage Reference output.         RA3/AN3/CPS3/C12IN3-/C1IN+/<br>VREF+/C1OUT/CCP3 <sup>(2)</sup> /SRQ       RA3       TTL       CMOS       General purpose I/O.         AN3       AN       —       A/D Channel 3 input.         CPS3       AN       —       Capacitive sensing input 3.         C12IN3-       AN       —       Comparator C1 or C2 negative input.         C1IN+       AN       —       Comparator C1 positive input.         VREF+       AN       —       A/D Voltage Reference input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |   |

| DACOUT       AN       Voltage Reference output.         RA3/AN3/CPS3/C12IN3-/C1IN+/<br>VREF+/C1OUT/CCP3 <sup>(2)</sup> /SRQ       RA3       TTL       CMOS       General purpose I/O.         AN3       AN       —       A/D Channel 3 input.         CPS3       AN       —       Capacitive sensing input 3.         C12IN3-       AN       —       Comparator C1 or C2 negative input.         VREF+       AN       —       A/D Voltage Reference input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |   |

| RA3/AN3/CPS3/C12IN3-/C1IN+/<br>VREF+/C1OUT/CCP3 <sup>(2)</sup> /SRQ       RA3       TTL       CMOS       General purpose I/O.         AN3       AN       —       A/D Channel 3 input.         CPS3       AN       —       Capacitive sensing input 3.         C12IN3-       AN       —       Comparator C1 or C2 negative input.         VREF+       AN       —       Comparator C1 positive input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |   |

| VREF+/C1OUT/CCP3 <sup>(2)</sup> /SRQ       AN3       AN       —       A/D Channel 3 input.         CPS3       AN       —       Capacitive sensing input 3.         C12IN3-       AN       —       Comparator C1 or C2 negative input.         C1IN+       AN       —       Comparator C1 positive input.         VREF+       AN       —       A/D Voltage Reference input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |   |

| ANS       AN       —       AND Chainler's lingut.         CPS3       AN       —       Capacitive sensing input 3.         C12IN3-       AN       —       Comparator C1 or C2 negative input.         C1IN+       AN       —       Comparator C1 positive input.         VREF+       AN       —       A/D Voltage Reference input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |   |

| C12IN3-       AN       —       Comparator C1 or C2 negative input.         C1IN+       AN       —       Comparator C1 positive input.         VREF+       AN       —       A/D Voltage Reference input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |   |

| C1IN+     AN     —     Comparator C1 positive input.       VREF+     AN     —     A/D Voltage Reference input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | - |

| VREF+ AN — A/D Voltage Reference input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |   |

| C1OUT — CMOS Comparator C1 output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |   |

| CCP3 ST CMOS Capture/Compare/PWM3.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |   |

| SRQ — CMOS SR latch non-inverting output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | - |

| RA4/AN4/CPS4/C2OUT/T0CKI/ RA4 TTL CMOS General purpose I/O.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |   |

| CCP4 <sup>(2)</sup> /SRNQ AN4 AN — A/D Channel 4 input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |   |

| CPS4 AN — Capacitive sensing input 4.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |   |

| C2OUT — CMOS Comparator C2 output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |   |

| T0CKI ST — Timer0 clock input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |   |

| CCP4 ST CMOS Capture/Compare/PWM4.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |   |

| SRNQ — CMOS SR latch inverting output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |   |

| RA5/MCLR/VPP/SS1 <sup>(1,2)</sup> RA5 TTL CMOS General purpose I/O.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |   |

| MCLR ST — Master Clear with internal pull-up.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |   |

| VPP HV — Programming voltage.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |   |

| SS1   ST   —   Slave Select input 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |   |

TABLE 1-2: PIC16(L)F1826/27 PINOUT DESCRIPTION

Legend:AN= Analog input or outputCMOS = CMOS compatible input or outputOD= Open DrainTTL = TTL compatible inputST= Schmitt Trigger input with CMOS levels $I^2C^{TM}$ = Schmitt Trigger input with  $I^2C$ HV= High VoltageXTAL= Crystallevels

Note 1: Pin functions can be moved using the APFCON0 or APFCON1 register.

**2:** Functions are only available on the PIC16(L)F1827.

**3:** Default function location.

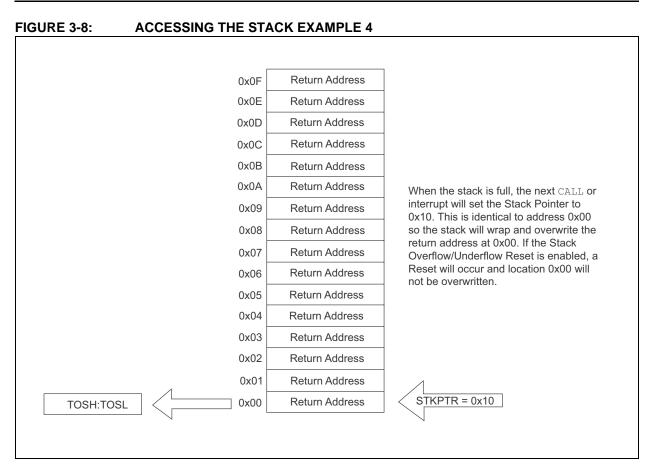

#### 3.4.2 OVERFLOW/UNDERFLOW RESET

If the STVREN bit in Configuration Word 2 is programmed to '1', the device will be reset if the stack is PUSHed beyond the sixteenth level or POPed beyond the first level, setting the appropriate bits (STKOVF or STKUNF, respectively) in the PCON register.

#### 3.5 Indirect Addressing

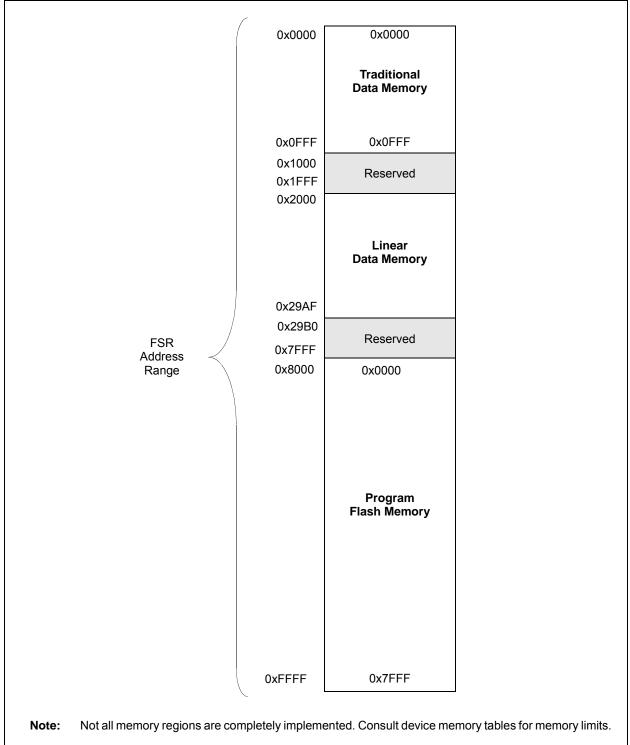

The INDFn registers are not physical registers. Any instruction that accesses an INDFn register actually accesses the register at the address specified by the File Select Registers (FSR). If the FSRn address specifies one of the two INDFn registers, the read will return '0' and the write will not occur (though Status bits may be affected). The FSRn register value is created by the pair FSRnH and FSRnL.

The FSR registers form a 16-bit address that allows an addressing space with 65536 locations. These locations are divided into three memory regions:

- Traditional Data Memory

- Linear Data Memory

- Program Flash Memory

| FIGURE 5-7:             | INTERNAL OSCILLATOR SWITCH TIMING                                        |

|-------------------------|--------------------------------------------------------------------------|

| SENETORC/               | UFBNTOSC (FBCSS and WDT (Fbablad)<br>                                    |

| IRCF <3:0>              | $\neq 0$ $X = 0$                                                         |

| System Clock            |                                                                          |

| nfintosc/ i<br>Mfintosc | LENETCISC (ENNET FISCHI es WIDT enabled)                                 |

| HFINTOSC/<br>MEINTOSC   |                                                                          |

| LFINTOSC                |                                                                          |

| IRCF <3:0>              | $\neq 0$ $\chi = 0$                                                      |

| System Clock            |                                                                          |

| LEPEROSC 1<br>LEPEROSC  | EFIRITOSCARFINITOSC<br>LEVELOUSC turns of univer WET or FICER is enabled |

| KUT DIR EKARDKA         | Control Paris, Republic Sono, Second Receiver                            |

| MENTOSC/                |                                                                          |

| \$2CF <330>             | <u>+ C X 19 0</u>                                                        |

| System Grook            |                                                                          |

#### 12.3.4 PORTB FUNCTIONS AND OUTPUT PRIORITIES

Each PORTB pin is multiplexed with other functions. The pins, their combined functions and their output priorities are shown in Table 12-5.

When multiple outputs are enabled, the actual pin control goes to the peripheral with the highest priority.

Analog input and some digital input functions are not included in the list below. These input functions can remain active when the pin is configured as an output. Certain digital input functions, such as the EUSART RX signal, override other port functions and are included in the priority list.

#### TABLE 12-5: PORTB OUTPUT PRIORITY

| Pin Name | Function Priority <sup>(1)</sup>                                                                      |

|----------|-------------------------------------------------------------------------------------------------------|

| RB0      | P1A<br>RB0                                                                                            |

| RB1      | SDA1<br>RX/DT<br>RB1                                                                                  |

| RB2      | SDA2 (PIC16(L)F1827 only)<br>TX/CK<br>RX/DT<br>SDO1<br>RB2                                            |

| RB3      | MDOUT<br>CCP1/P1A<br>RB3                                                                              |

| RB4      | SCL1<br>SCK1<br>RB4                                                                                   |

| RB5      | SCL2 (PIC16(L)F1827 only)<br>TX/CK<br>SCK2 (PIC16(L)F1827 only)<br>P1B<br>RB5                         |

| RB6      | ICSPCLK (Programming)<br>T1OSI<br>P1C<br>CCP2 (PIC16(L)F1827 only)<br>P2A (PIC16(L)F1827 only)<br>RB6 |

| RB7      | ICSPDAT (Programming)<br>T1OSO<br>P1D<br>P2B (PIC16(L)F1827 only)<br>RB7                              |

Note 1: Priority listed from highest to lowest.

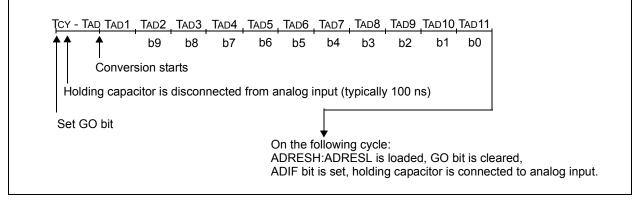

#### TABLE 16-1: ADC CLOCK PERIOD (TAD) Vs. DEVICE OPERATING FREQUENCIES

| ADC Clock P         | eriod (TAD) | Device Frequency (Fosc)     |                             |                             |                             |                             |                               |

|---------------------|-------------|-----------------------------|-----------------------------|-----------------------------|-----------------------------|-----------------------------|-------------------------------|

| ADC<br>Clock Source | ADCS<2:0>   | 32 MHz                      | 20 MHz                      | 16 MHz                      | 8 MHz                       | 4 MHz                       | 1 MHz                         |

| Fosc/2              | 000         | 62.5ns <sup>(2)</sup>       | 100 ns <sup>(2)</sup>       | 125 ns <sup>(2)</sup>       | 250 ns <sup>(2)</sup>       | 500 ns <sup>(2)</sup>       | 2.0 μs                        |

| Fosc/4              | 100         | 125 ns <sup>(2)</sup>       | 200 ns <sup>(2)</sup>       | 250 ns <sup>(2)</sup>       | 500 ns <sup>(2)</sup>       | 1.0 μs                      | 4.0 μs                        |

| Fosc/8              | 001         | 0.5 μs <sup>(2)</sup>       | 400 ns <sup>(2)</sup>       | 0.5 μs <sup>(2)</sup>       | 1.0 μs                      | 2.0 μs                      | 8.0 μs <sup>(3)</sup>         |

| Fosc/16             | 101         | 800 ns                      | 800 ns                      | 1.0 μs                      | 2.0 μs                      | 4.0 μs                      | 16.0 μs <b><sup>(3)</sup></b> |

| Fosc/32             | 010         | 1.0 μs                      | 1.6 μs                      | 2.0 μs                      | 4.0 μs                      | 8.0 μs <sup>(3)</sup>       | 32.0 μs <sup>(3)</sup>        |

| Fosc/64             | 110         | 2.0 μs                      | 3.2 μs                      | 4.0 μs                      | 8.0 μs <sup>(3)</sup>       | 16.0 μs <sup>(3)</sup>      | 64.0 μs <sup>(3)</sup>        |

| FRC                 | x11         | 1.0-6.0 μs <sup>(1,4)</sup>   |

Legend: Shaded cells are outside of recommended range.

**Note 1:** The FRC source has a typical TAD time of 1.6  $\mu$ s for VDD.

2: These values violate the minimum required TAD time.

3: For faster conversion times, the selection of another clock source is recommended.

4: The ADC clock period (TAD) and total ADC conversion time can be minimized when the ADC clock is derived from the system clock FOSC. However, the FRC clock source must be used when conversions are to be performed with the device in Sleep mode.

## 18.0 SR LATCH

The module consists of a single SR Latch with multiple Set and Reset inputs as well as separate latch outputs. The SR Latch module includes the following features:

- · Programmable input selection

- SR Latch output is available externally

- Separate Q and  $\overline{Q}$  outputs

- · Firmware Set and Reset

The SR Latch can be used in a variety of analog applications, including oscillator circuits, one-shot circuit, hysteretic controllers, and analog timing applications.

#### 18.1 Latch Operation

The latch is a Set-Reset Latch that does not depend on a clock source. Each of the Set and Reset inputs are active-high. The latch can be Set or Reset by:

- Software control (SRPS and SRPR bits)

- Comparator C1 output (SYNCC1OUT)

- Comparator C2 output (SYNCC2OUT)

- SRI pin

- Programmable clock (SRCLK)

The SRPS and the SRPR bits of the SRCON0 register may be used to set or reset the SR Latch, respectively. The latch is Reset-dominant. Therefore, if both Set and Reset inputs are high, the latch will go to the Reset state. Both the SRPS and SRPR bits are self resetting which means that a single write to either of the bits is all that is necessary to complete a latch Set or Reset operation.

The output from Comparator C1 or C2 can be used as the Set or Reset inputs of the SR Latch. The output of either comparator can be synchronized to the Timer1 clock source. See **Section 19.0 "Comparator Module"** and **Section 21.0 "Timer1 Module with Gate Control"** for more information.

An external source on the SRI pin can be used as the Set or Reset inputs of the SR Latch.

An internal clock source is available that can periodically set or reset the SR Latch. The SRCLK<2:0> bits in the SRCON0 register are used to select the clock source period. The SRSCKE and SRRCKE bits of the SRCON1 register enable the clock source to set or reset the SR Latch, respectively.

**Note:** Enabling both the Set and Reset inputs from any one source at the same time may result in indeterminate operation, as the Reset dominance cannot be assured.

#### 18.2 Latch Output

The SRQEN and SRNQEN bits of the SRCON0 register control the Q and  $\overline{Q}$  latch outputs. Both of the SR Latch outputs may be directly output to an I/O pin at the same time.

The applicable TRIS bit of the corresponding port must be cleared to enable the port pin output driver.

#### 18.3 Effects of a Reset

Upon any device Reset, the SR Latch output is not initialized to a known state. The user's firmware is responsible for initializing the latch output before enabling the output pins.

#### 19.7 Comparator Negative Input Selection

The CxNCH<1:0> bits of the CMxCON0 register direct one of four analog pins to the comparator inverting input.

| Note: | To use CxIN+ and CxINx- pins as analog     |

|-------|--------------------------------------------|

|       | input, the appropriate bits must be set in |

|       | the ANSEL register and the correspond-     |

|       | ing TRIS bits must also be set to disable  |

|       | the output drivers.                        |

#### 19.8 Comparator Response Time

The comparator output is indeterminate for a period of time after the change of an input source or the selection of a new reference voltage. This period is referred to as the response time. The response time of the comparator differs from the settling time of the voltage reference. Therefore, both of these times must be considered when determining the total response time to a comparator input change. See the Comparator and Voltage Reference Specifications in **Section 29.0 "Electrical Specifications"** for more details.

#### 19.9 Interaction with ECCP Logic

The C1 and C2 comparators can be used as general purpose comparators. Their outputs can be brought out to the C1OUT and C2OUT pins. When the ECCP Auto-Shutdown is active it can use one or both comparator signals. If auto-restart is also enabled, the comparators can be configured as a closed loop analog feedback to the ECCP, thereby, creating an analog controlled PWM.

**Note:** When the comparator module is first initialized the output state is unknown. Upon initialization, the user should verify the output state of the comparator prior to relying on the result, primarily when using the result in connection with other peripheral features, such as the ECCP Auto-Shutdown mode.

#### 19.10 Analog Input Connection Considerations

A simplified circuit for an analog input is shown in Figure 19-4. Since the analog input pins share their connection with a digital input, they have reverse biased ESD protection diodes to VDD and VSS. The analog input, therefore, must be between VSS and VDD. If the input voltage deviates from this range by more than 0.6V in either direction, one of the diodes is forward biased and a latch-up may occur.

A maximum source impedance of  $10 \text{ k}\Omega$  is recommended for the analog sources. Also, any external component connected to an analog input pin, such as a capacitor or a Zener diode, should have very little leakage current to minimize inaccuracies introduced.

Note 1: When reading a PORT register, all pins configured as analog inputs will read as a '0'. Pins configured as digital inputs will convert as an analog input, according to the input specification.

> Analog levels on any pin defined as a digital input, may cause the input buffer to consume more current than is specified.

#### 24.3.6 PWM RESOLUTION

The resolution determines the number of available duty cycles for a given period. For example, a 10-bit resolution will result in 1024 discrete duty cycles, whereas an 8-bit resolution will result in 256 discrete duty cycles.

The maximum PWM resolution is 10 bits when PRx is 255. The resolution is a function of the PRx register value as shown by Equation 24-4.

#### EQUATION 24-4: PWM RESOLUTION

Resolution =

$$\frac{\log[4(PRx+1)]}{\log(2)}$$

bits

Note: If the pulse width value is greater than the period the assigned PWM pin(s) will remain unchanged.

| PWM Frequency             | 1.95 kHz | 7.81 kHz | 31.25 kHz | 125 kHz | 250 kHz | 333.3 kHz |

|---------------------------|----------|----------|-----------|---------|---------|-----------|

| Timer Prescale (1, 4, 16) | 16       | 4        | 1         | 1       | 1       | 1         |

| PRx Value                 | 0xFF     | 0xFF     | 0xFF      | 0x3F    | 0x1F    | 0x17      |

| Maximum Resolution (bits) | 10       | 10       | 10        | 8       | 7       | 6.6       |

#### TABLE 24-6: EXAMPLE PWM FREQUENCIES AND RESOLUTIONS (Fosc = 20 MHz)

| PWM Frequency             | 1.22 kHz | 4.88 kHz | 19.53 kHz | 78.12 kHz | 156.3 kHz | 208.3 kHz |

|---------------------------|----------|----------|-----------|-----------|-----------|-----------|

| Timer Prescale (1, 4, 16) | 16       | 4        | 1         | 1         | 1         | 1         |

| PRx Value                 | 0xFF     | 0xFF     | 0xFF      | 0x3F      | 0x1F      | 0x17      |

| Maximum Resolution (bits) | 10       | 10       | 10        | 8         | 7         | 6.6       |

#### TABLE 24-7: EXAMPLE PWM FREQUENCIES AND RESOLUTIONS (Fosc = 8 MHz)

| PWM Frequency             | 1.22 kHz | 4.90 kHz | 19.61 kHz | 76.92 kHz | 153.85 kHz | 200.0 kHz |

|---------------------------|----------|----------|-----------|-----------|------------|-----------|

| Timer Prescale (1, 4, 16) | 16       | 4        | 1         | 1         | 1          | 1         |

| PRx Value                 | 0x65     | 0x65     | 0x65      | 0x19      | 0x0C       | 0x09      |

| Maximum Resolution (bits) | 8        | 8        | 8         | 6         | 5          | 5         |

| U-0            | U-0             | U-0                                                                              | R/W-0/0          | R/W-0/0         | R/W-0/0           | R/W-0/0          | R/W-1/1      |  |  |  |

|----------------|-----------------|----------------------------------------------------------------------------------|------------------|-----------------|-------------------|------------------|--------------|--|--|--|

| _              | —               | _                                                                                | STRxSYNC         | STRxD           | STRxC             | STRxB            | STRxA        |  |  |  |

| bit 7          |                 |                                                                                  |                  |                 |                   |                  | bit C        |  |  |  |

|                |                 |                                                                                  |                  |                 |                   |                  |              |  |  |  |

| Legend:        |                 |                                                                                  |                  |                 |                   |                  |              |  |  |  |

| R = Readab     | ole bit         | W = Writable                                                                     | bit              | U = Unimpler    | mented bit, read  | d as '0'         |              |  |  |  |

| u = Bit is un  | changed         | x = Bit is unk                                                                   | nown             | -n/n = Value a  | at POR and BO     | R/Value at all o | other Resets |  |  |  |

| '1' = Bit is s | et              | '0' = Bit is cle                                                                 | ared             |                 |                   |                  |              |  |  |  |

|                |                 |                                                                                  |                  |                 |                   |                  |              |  |  |  |

| bit 7-5        | Unimplemen      | ted: Read as                                                                     | '0'              |                 |                   |                  |              |  |  |  |

| bit 4          |                 | Steering Sync                                                                    |                  |                 |                   |                  |              |  |  |  |

|                |                 | 1 = Output steering update occurs on next PWM period                             |                  |                 |                   |                  |              |  |  |  |

|                | 0 = Output st   | Output steering update occurs at the beginning of the instruction cycle boundary |                  |                 |                   |                  |              |  |  |  |

| bit 3          |                 | STRxD: Steering Enable bit D                                                     |                  |                 |                   |                  |              |  |  |  |

|                | •               |                                                                                  | vaveform with p  | olarity control | from CCPxM<       | 1:0>             |              |  |  |  |

|                | 0 = PxD pin i   | s assigned to p                                                                  | port pin         |                 |                   |                  |              |  |  |  |

| bit 2          |                 | ring Enable bi                                                                   |                  |                 |                   |                  |              |  |  |  |

|                | •               | 1 = PxC pin has the PWM waveform with polarity control from CCPxM<1:0>           |                  |                 |                   |                  |              |  |  |  |

|                | •               | s assigned to p                                                                  | •                |                 |                   |                  |              |  |  |  |

| bit 1          | STRxB: Stee     | STRxB: Steering Enable bit B                                                     |                  |                 |                   |                  |              |  |  |  |

|                | 1 = PxB pin h   | nas the PWM v                                                                    | vaveform with p  | olarity control | from CCPxM<1      | 1:0>             |              |  |  |  |

|                | 0 = PxB pin is  | 0 = PxB pin is assigned to port pin                                              |                  |                 |                   |                  |              |  |  |  |

| bit 0          | STRxA: Stee     | STRxA: Steering Enable bit A                                                     |                  |                 |                   |                  |              |  |  |  |

|                | 1 = PxA pin h   | nas the PWM v                                                                    | vaveform with p  | olarity control | from CCPxM<1      | 1:0>             |              |  |  |  |

|                | 0 = PxA pin is  | s assigned to p                                                                  | port pin         |                 |                   |                  |              |  |  |  |

| Note 1: 7      | The PWM Steerin | a modo is avai                                                                   | ilabla only whor |                 | N register bits ( |                  | - 11 ond     |  |  |  |

## **REGISTER 24-5: PSTRxCON: PWM STEERING CONTROL REGISTER<sup>(1)</sup>**

Note 1: The PWM Steering mode is available only when the CCPxCON register bits CCPxM<3:2> = 11 and PxM<1:0> = 00.

#### REGISTER 25-2: SSPxCON1: SSPx CONTROL REGISTER 1

| R/C/HS-0/0              | R/C/HS-0/0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | R/W-0/0                                                                                                                                                                      | R/W-0/0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | R/W-0/0                                                                                                 | R/W-0/0                                    | R/W-0/0                                            | R/W-0/0                                     |