Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 16                                                                         |

| Program Memory Size        | 3.5KB (2K x 14)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 256 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                |

| Data Converters            | A/D 12x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                                             |

| Supplier Device Package    | 20-SSOP                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1826-e-ss |

#### Note the following details of the code protection feature on Microchip devices:

- Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not

mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION. QUALITY, PERFORMANCE, MERCHANTABILITY FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights.

#### **Trademarks**

The Microchip name and logo, the Microchip logo, dsPIC, Keeloq, Keeloq logo, MPLAB, PIC, PICmicro, PICSTART, PIC<sup>32</sup> logo, rfPIC and UNI/O are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

FilterLab, Hampshire, HI-TECH C, Linear Active Thermistor, MXDEV, MXLAB, SEEVAL and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Analog-for-the-Digital Age, Application Maestro, CodeGuard, dsPICDEM, dsPICDEM.net, dsPICworks, dsSPEAK, ECAN, ECONOMONITOR, FanSense, HI-TIDE, In-Circuit Serial Programming, ICSP, Mindi, MiWi, MPASM, MPLAB Certified logo, MPLIB, MPLINK, mTouch, Omniscient Code Generation, PICC, PICC-18, PICDEM, PICDEM.net, PICkit, PICtail, REAL ICE, rfLAB, Select Mode, Total Endurance, TSHARC, UniWinDriver, WiperLock and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

$\ensuremath{\mathsf{SQTP}}$  is a service mark of Microchip Technology Incorporated in the U.S.A.

All other trademarks mentioned herein are property of their respective companies.

© 2011, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

Printed on recycled paper.

ISBN: 978-1-61341-124-7

Microchip received ISO/TS-16949:2002 certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona; Gresham, Oregon and design centers in California and India. The Company's quality system processes and procedures are for its PIC® MCUs and dsPIC® DSCs, KEŁLOQ® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001:2000 certified.

# QUALITY MANAGEMENT SYSTEM CERTIFIED BY DNV ISO/TS 16949:2002

DS41391D-page 6

| NO  | 18-Pin PDIP/SOIC | 20-Pin SSOP | 28-Pin QFN/UQFN | ANSEL | A/D  | Reference       | Cap Sense | Comparator                | SR Latch | Timers         | ССР                                                                       | EUSART                                                                             | MSSP                                                                | Interrupt  | Modulator | Pull-up          | Basic                  |

|-----|------------------|-------------|-----------------|-------|------|-----------------|-----------|---------------------------|----------|----------------|---------------------------------------------------------------------------|------------------------------------------------------------------------------------|---------------------------------------------------------------------|------------|-----------|------------------|------------------------|

| RA0 | 17               | 19          | 23              | Y     | AN0  | _               | CPS0      | C12IN0-                   | _        | _              | _                                                                         | _                                                                                  | SDO2 <sup>(2)</sup>                                                 | _          | _         | N                | _                      |

| RA1 | 18               | 20          | 24              | Y     | AN1  | _               | CPS1      | C12IN1-                   | _        | _              | _                                                                         | _                                                                                  | SS2 <sup>(2)</sup>                                                  | _          | _         | N                | _                      |

| RA2 | 1                | 1           | 26              | Y     | AN2  | VREF-<br>DACOUT | CPS2      | C12IN2-<br>C12IN+         | _        | _              | _                                                                         | _                                                                                  | _                                                                   | _          | _         | N                | _                      |

| RA3 | 2                | 2           | 27              | Y     | AN3  | VREF+           | CPS3      | C12IN3-<br>C1IN+<br>C1OUT | SRQ      | -              | CCP3 <sup>(2)</sup>                                                       | _                                                                                  | -                                                                   | _          | _         | N                | _                      |

| RA4 | 3                | 3           | 28              | Y     | AN4  | _               | CPS4      | C2OUT                     | SRNQ     | T0CKI          | CCP4 <sup>(2)</sup>                                                       | _                                                                                  | -                                                                   | _          | _         | Ν                | _                      |

| RA5 | 4                | 4           | 1               | N     | _    | _               | _         | _                         | _        | _              | _                                                                         | _                                                                                  | SS1 <sup>(1)</sup>                                                  | _          | _         | Y <sup>(3)</sup> | MCLR, VPP              |

| RA6 | 15               | 17          | 20              | N     | _    | _               | 1         | _                         | 1        | 1              | P1D <sup>(1)</sup><br>P2B <sup>(1,2)</sup>                                | _                                                                                  | SDO1 <sup>(1)</sup>                                                 | 1          | _         | N                | OSC2<br>CLKOUT<br>CLKR |

| RA7 | 16               | 18          | 21              | N     | -    | _               | ١         | _                         | ı        | ı              | P1C <sup>(1)</sup><br>CCP2 <sup>(1,2)</sup><br>P2A <sup>(1,2)</sup>       |                                                                                    |                                                                     | ١          | _         | N                | OSC1<br>CLKIN          |

| RB0 | 6                | 7           | 7               | N     | ı    | _               | ı         |                           | SRI      | T1G            | CCP1 <sup>(1)</sup><br>P1A <sup>(1)</sup><br>FLT0                         | 1                                                                                  |                                                                     | INT<br>IOC | _         | Υ                | _                      |

| RB1 | 7                | 8           | 8               | Y     | AN11 | _               | CPS11     | _                         |          |                | _                                                                         | RX <sup>(1,4)</sup><br>DT <sup>(1,4)</sup>                                         | SDA1<br>SDI1                                                        | IOC        | _         | Υ                | _                      |

| RB2 | 8                | 9           | 9               | Y     | AN10 |                 | CPS10     | _                         |          |                | _                                                                         | RX <sup>(1)</sup> ,DT <sup>(1)</sup><br>TX <sup>(1,4)</sup><br>CK <sup>(1,4)</sup> | SDA2 <sup>(2)</sup><br>SDI2 <sup>(2)</sup><br>SDO1 <sup>(1,4)</sup> | IOC        | MDMIN     | Υ                | _                      |

| RB3 | 9                | 10          | 10              | Υ     | AN9  | _               | CPS9      | _                         | _        |                | CCP1 <sup>(1,4)</sup><br>P1A <sup>(1,4)</sup>                             | _                                                                                  | _                                                                   | IOC        | MDOUT     | Υ                | _                      |

| RB4 | 10               | 11          | 12              | Y     | AN8  | _               | CPS8      | _                         |          | -              | _                                                                         | _                                                                                  | SCL1<br>SCK1                                                        | IOC        | MDCIN2    | Υ                | _                      |

| RB5 | 11               | 12          | 13              | Y     | AN7  |                 | CPS7      | _                         | ĺ        | 1              | P1B                                                                       | TX <sup>(1)</sup><br>CK <sup>(1)</sup>                                             | SCL2 <sup>(2)</sup><br>SCK2 <sup>(2)</sup><br>SS1 <sup>(1,4)</sup>  | IOC        | _         | Y                | _                      |

| RB6 | 12               | 13          | 15              | Y     | AN5  | _               | CPS5      | _                         | 1        | T1CKI<br>T1OSI | P1C <sup>(1,4)</sup><br>CCP2 <sup>(1,2,4)</sup><br>P2A <sup>(1,2,4)</sup> | _                                                                                  | _                                                                   | IOC        | _         | Y                | ICSPCLK/<br>ICDCLK     |

| RB7 | 13               | 14          | 16              | Y     | AN6  | _               | CPS6      | _                         |          | T10S0          | P1D <sup>(1,4)</sup><br>P2B <sup>(1,2,4)</sup>                            | _                                                                                  | _                                                                   | IOC        | MDCIN1    | Y                | ICSPDAT/<br>ICDDAT     |

| VDD | 14               | 15,16       | 17,19           | _     | _    | _               | I         | _                         | 1        | 1              | ı                                                                         | _                                                                                  | _                                                                   |            | _         | _                | VDD                    |

| Vss | 5                | 5,6         | 3,5             | _     | _    | _               |           | _                         | _        | _              | _                                                                         | _                                                                                  | _                                                                   | _          | _         | _                | Vss                    |

Note 1: Pin functions can be moved using the APFCON0 or APFCON1 register.

2: Functions are only available on the PIC16(L)F1827.

3: Weak pull-up always enabled when MCLR is enabled, otherwise the pull-up is under user control.

4: Default function location.

TABLE 3-3: PIC16(L)F1826/27 MEMORY MAP (CONTINUED)

|      | BANK16                                |      | BANK17                                |      | BANK18                                |      | BANK19                                |      | BANK20                                |      | BANK21                                |      | BANK22                                |      | BANK23                                |

|------|---------------------------------------|------|---------------------------------------|------|---------------------------------------|------|---------------------------------------|------|---------------------------------------|------|---------------------------------------|------|---------------------------------------|------|---------------------------------------|

| 800h | Core Registers<br>(Table 3-2)         | 880h | Core Registers<br>(Table 3-2)         | 900h | Core Registers<br>(Table 3-2)         | 980h | Core Registers<br>(Table 3-2)         | A00h | Core Registers<br>(Table 3-2)         | A80h | Core Registers<br>(Table 3-2)         | B00h | Core Registers<br>(Table 3-2)         | B80h | Core Registers<br>(Table 3-2)         |

| 80Bh |                                       | 88Bh |                                       | 90Bh |                                       | 98Bh |                                       | A0Bh |                                       | A8Bh |                                       | B0Bh |                                       | B8Bh |                                       |

| 80Ch |                                       | 88Ch |                                       | 90Ch |                                       | 98Ch |                                       | A0Ch |                                       | A8Ch |                                       | B0Ch |                                       | B8Ch |                                       |

|      | Unimplemented<br>Read as '0'          |

| 86Fh |                                       | 8EFh |                                       | 96Fh |                                       | 9EFh |                                       | A6Fh |                                       | AEFh |                                       | B6Fh |                                       | BEFh |                                       |

| 870h | Common RAM<br>(Accesses<br>70h – 7Fh) | 8F0h | Common RAM<br>(Accesses<br>70h – 7Fh) | 970h | Common RAM<br>(Accesses<br>70h – 7Fh) | 9F0h | Common RAM<br>(Accesses<br>70h – 7Fh) | A70h | Common RAM<br>(Accesses<br>70h – 7Fh) | AF0h | Common RAM<br>(Accesses<br>70h – 7Fh) | B70h | Common RAM<br>(Accesses<br>70h – 7Fh) | BF0h | Common RAM<br>(Accesses<br>70h – 7Fh) |

| 87Fh |                                       | 8FFh |                                       | 97Fh |                                       | 9FFh |                                       | A7Fh |                                       | AFFh |                                       | B7Fh |                                       | BFFh |                                       |

|              | BANK 24                       |      | BANK 25                       |              | BANK 26                       |      | BANK 27                       |      | BANK 28                       |      | BANK 29                       |      | BANK 30                               |                      | BANK 31                                                             |

|--------------|-------------------------------|------|-------------------------------|--------------|-------------------------------|------|-------------------------------|------|-------------------------------|------|-------------------------------|------|---------------------------------------|----------------------|---------------------------------------------------------------------|

| C00h         | Core Registers<br>(Table 3-2) | C80h | Core Registers<br>(Table 3-2) | D00h         | Core Registers<br>(Table 3-2) | D80h | Core Registers<br>(Table 3-2) | E00h | Core Registers<br>(Table 3-2) | E80h | Core Registers<br>(Table 3-2) | F00h | Core Registers<br>(Table 3-2)         | F80h                 | Core Registers<br>(Table 3-2)                                       |

| C0Bh         |                               | C8Bh |                               | D0Bh         |                               | D8Bh |                               | E0Bh |                               | E8Bh |                               | F0Bh |                                       | F8Bh                 |                                                                     |

| C0Ch         |                               | C8Ch |                               | D0Ch         |                               | D8Ch |                               | E0Ch |                               | E8Ch |                               | F0Ch |                                       | F8Ch                 |                                                                     |

| C6Fh         | Unimplemented<br>Read as '0'  | CEFh | Unimplemented<br>Read as '0'  | D6Fh         | Unimplemented<br>Read as '0'  | DEFh | Unimplemented<br>Read as '0'  | E6Fh | Unimplemented<br>Read as '0'  | EEFh | Unimplemented<br>Read as '0'  | F6Fh | Unimplemented<br>Read as '0'          | F9Fh<br>FA0h<br>FEFh | Unimplemented<br>Read as '0'  See Table 3-4 for<br>more information |

| C70h<br>C7Fh | Accesses<br>70h – 7Fh         | CF0h | Accesses<br>70h – 7Fh         | D70h<br>D7Fh | Accesses<br>70h – 7Fh         | DF0h | Accesses<br>70h – 7Fh         | E70h | Accesses<br>70h – 7Fh         | EF0h | Accesses<br>70h – 7Fh         | F70h | Common RAM<br>(Accesses<br>70h – 7Fh) | FF0h                 | Common RAM<br>(Accesses<br>70h – 7Fh)                               |

**Legend:** = Unimplemented data memory locations, read as '0'

SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED) **TABLE 3-6:**

| Address | Name                 | Bit 7                                                       | Bit 6         | Bit 5    | Bit 4    | Bit 3    | Bit 2  | Bit 1   | Bit 0   | Value on<br>POR, BOR | Value on all<br>other<br>Resets |

|---------|----------------------|-------------------------------------------------------------|---------------|----------|----------|----------|--------|---------|---------|----------------------|---------------------------------|

| Bank 8  |                      |                                                             |               |          |          |          |        |         |         |                      | Ц                               |

| 40Ch    | _                    | Unimplement                                                 | ed            |          | _        | _        |        |         |         |                      |                                 |

| 40Dh    | _                    | Unimplement                                                 | ed            |          |          |          |        |         |         | _                    | _                               |

| 40Eh    | _                    | Unimplement                                                 | ed            |          |          |          |        |         |         | _                    | _                               |

| 40Fh    | _                    | Unimplement                                                 | ed            |          |          |          |        |         |         | _                    | _                               |

| 410h    | _                    | Unimplement                                                 | ed            |          |          |          |        |         |         | _                    | _                               |

| 411h    | _                    | Unimplement                                                 | ed            |          |          |          |        |         |         | _                    | _                               |

| 412h    | _                    | Unimplement                                                 | ed            |          |          |          |        |         |         | _                    | _                               |

| 413h    | _                    | Unimplement                                                 | Jnimplemented |          |          |          |        |         |         | _                    | _                               |

| 414h    | _                    | Unimplement                                                 | Jnimplemented |          |          |          |        |         |         |                      | _                               |

| 415h    | TMR4 <sup>(1)</sup>  | Timer4 Modu                                                 | le Register   |          |          |          |        |         |         | 0000 0000            | 0000 0000                       |

| 416h    | PR4 <sup>(1)</sup>   | Timer4 Perio                                                | d Register    |          |          |          |        |         |         | 1111 1111            | 1111 1111                       |

| 417h    | T4CON <sup>(1)</sup> | _                                                           | T4OUTPS3      | T4OUTPS2 | T4OUTPS1 | T4OUTPS0 | TMR4ON | T4CKPS1 | T4CKPS0 | -000 0000            | -000 0000                       |

| 418h    | _                    | Unimplement                                                 | ed            |          |          |          |        |         |         | _                    | _                               |

| 419h    | _                    | Unimplement                                                 | ed            |          |          |          |        |         |         | _                    | _                               |

| 41Ah    | _                    | Unimplement                                                 | Unimplemented |          |          |          |        |         |         | _                    | _                               |

| 41Bh    | _                    | Unimplemented                                               |               |          |          |          |        |         |         | _                    | _                               |

| 41Ch    | TMR6 <sup>(1)</sup>  | Timer6 Module Register                                      |               |          |          |          |        |         |         | 0000 0000            | 0000 0000                       |

| 41Dh    | PR6 <sup>(1)</sup>   | Timer6 Period Register                                      |               |          |          |          |        |         |         | 1111 1111            | 1111 1111                       |

| 41Eh    | T6CON <sup>(1)</sup> | - T6OUTPS3 T6OUTPS2 T6OUTPS1 T6OUTPS0 TMR6ON T6CKPS1 T6CKPS |               |          |          |          |        |         |         | -000 0000            | -000 0000                       |

| 41Fh    | _                    | Unimplement                                                 | ed            |          |          |          |        |         |         | _                    | _                               |

${\bf x}$  = unknown,  ${\bf u}$  = unchanged,  ${\bf q}$  = value depends on condition, - = unimplemented,  ${\bf r}$  = reserved. Shaded locations are unimplemented, read as '0'. Legend:

Note 1: PIC16(L)F1827 only.

#### REGISTER 4-3: DEVICEID: DEVICE ID REGISTER<sup>(1)</sup>

| R      | R | R    | R     | R | R     |

|--------|---|------|-------|---|-------|

|        |   | DEV- | <8:3> |   |       |

| bit 13 |   |      |       |   | bit 8 |

| R     | R        | R | R | R | R        | R | R     |

|-------|----------|---|---|---|----------|---|-------|

|       | DEV<2:0> |   |   |   | REV<4:0> |   |       |

| bit 7 |          |   |   |   |          |   | bit 0 |

Legend:R = Readable bitW = Writable bitU = Unimplemented bit, read as '1'u = Bit is unchangedx = Bit is unknown-n/n = Value at POR and BOR/Value at all other Resets'1' = Bit is set'0' = Bit is clearedP = Programmable bit

#### bit 13-5 **DEV<8:0>:** Device ID bits

| Device      | DEVICEID<13:0> Values |          |  |  |  |  |  |  |

|-------------|-----------------------|----------|--|--|--|--|--|--|

| Device      | DEV<8:0>              | REV<4:0> |  |  |  |  |  |  |

| PIC16F1826  | 10 0111 100           | x xxxx   |  |  |  |  |  |  |

| PIC16F1827  | 10 0111 101           | x xxxx   |  |  |  |  |  |  |

| PIC16LF1826 | 10 1000 100           | x xxxx   |  |  |  |  |  |  |

| PIC16LF1827 | 10 1000 101           | x xxxx   |  |  |  |  |  |  |

bit 4-0 **REV<4:0>:** Revision ID bits

These bits are used to identify the revision.

Note 1: This location cannot be written.

## 12.2.3 PORTA FUNCTIONS AND OUTPUT PRIORITIES

Each PORTA pin is multiplexed with other functions. The pins, their combined functions and their output priorities are shown in Table 12-2.

When multiple outputs are enabled, the actual pin control goes to the peripheral with the highest priority.

Analog input functions, such as ADC, comparator and CapSense inputs, are not shown in the priority lists. These inputs are active when the I/O pin is set for Analog mode using the ANSELx registers. Digital output functions may control the pin when it is in Analog mode with the priority shown in Table 12-2.

TABLE 12-2: PORTA OUTPUT PRIORITY

| IABLE IZ Z. 10 | KIA OOTI OTT KIOKITT                                                                                                 |

|----------------|----------------------------------------------------------------------------------------------------------------------|

| Pin Name       | Function Priority <sup>(1)</sup>                                                                                     |

| RA0            | SDO2 (PIC16(L)F1827 only)<br>RA0                                                                                     |

| RA1            | SS2 (PIC16(L)F1827 only)<br>RA1                                                                                      |

| RA2            | DACOUT (DAC)<br>RA2                                                                                                  |

| RA3            | SRQ (SR latch)<br>CCP3 (PIC16(L)F1827 only)<br>C1OUT (Comparator)<br>RA3                                             |

| RA4            | SRNQ (SR latch) CCP4 (PIC16(L)F1827 only) T0CKI C2OUT (Comparator) RA4                                               |

| RA5            | Input only pin                                                                                                       |

| RA6            | OSC2 (enabled by Configuration Word) CLKOUT CLKR SDO1 P1D P2B (PIC16(L)F1827 only) RA6                               |

| RA7            | OSC1/CLKIN (enabled by<br>Configuration Word)<br>P1C<br>CCP2 (PIC16(L)F1827 only)<br>P2A (PIC16(L)F1827 only)<br>RA7 |

**Note 1:** Priority listed from highest to lowest.

Each PORTA pin is multiplexed with other functions. The pins, their combined functions and their output priorities are briefly described here. For additional information, refer to the appropriate section in this data sheet.

When multiple outputs are enabled, the actual pin control goes to the peripheral with the lowest number in the following lists.

## 12.3.4 PORTB FUNCTIONS AND OUTPUT PRIORITIES

Each PORTB pin is multiplexed with other functions. The pins, their combined functions and their output priorities are shown in Table 12-5.

When multiple outputs are enabled, the actual pin control goes to the peripheral with the highest priority.

Analog input and some digital input functions are not included in the list below. These input functions can remain active when the pin is configured as an output. Certain digital input functions, such as the EUSART RX signal, override other port functions and are included in the priority list.

**TABLE 12-5: PORTB OUTPUT PRIORITY**

| Pin Name | Function Priority <sup>(1)</sup>                                                       |

|----------|----------------------------------------------------------------------------------------|

| RB0      | P1A<br>RB0                                                                             |

| RB1      | SDA1<br>RX/DT<br>RB1                                                                   |

| RB2      | SDA2 (PIC16(L)F1827 only)<br>TX/CK<br>RX/DT<br>SDO1<br>RB2                             |

| RB3      | MDOUT<br>CCP1/P1A<br>RB3                                                               |

| RB4      | SCL1<br>SCK1<br>RB4                                                                    |

| RB5      | SCL2 (PIC16(L)F1827 only) TX/CK SCK2 (PIC16(L)F1827 only) P1B RB5                      |

| RB6      | ICSPCLK (Programming) T10SI P1C CCP2 (PIC16(L)F1827 only) P2A (PIC16(L)F1827 only) RB6 |

| RB7      | ICSPDAT (Programming)<br>T1OSO<br>P1D<br>P2B (PIC16(L)F1827 only)<br>RB7               |

Note 1: Priority listed from highest to lowest.

#### 14.3 FVR Control Registers

#### REGISTER 14-1: FVRCON: FIXED VOLTAGE REFERENCE CONTROL REGISTER

| R/W-0/0 | R-q/q                 | R/W-0/0  | R/W-0/0  | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|---------|-----------------------|----------|----------|---------|---------|---------|---------|

| FVREN   | FVRRDY <sup>(1)</sup> | Reserved | Reserved | CDAF\   | VR<1:0> | ADFV    | R<1:0>  |

| bit 7   |                       |          |          |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | q = Value depends on condition                        |

| bit 7   | FVREN: Fixed Voltage Reference Enable bit  0 = Fixed Voltage Reference is disabled  1 = Fixed Voltage Reference is enabled                                                                                                                                                                                                                                                                               |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6   | FVRRDY: Fixed Voltage Reference Ready Flag bit <sup>(1)</sup> 0 = Fixed Voltage Reference output is not ready or not enabled 1 = Fixed Voltage Reference output is ready for use                                                                                                                                                                                                                         |

| bit 5-4 | Reserved: Read as '0'. Maintain these bits clear.                                                                                                                                                                                                                                                                                                                                                        |

| bit 3-2 | CDAFVR<1:0>: Comparator and DAC Fixed Voltage Reference Selection bit 00 = Comparator and DAC Fixed Voltage Reference Peripheral output is off. 01 = Comparator and DAC Fixed Voltage Reference Peripheral output is 1x (1.024V) 10 = Comparator and DAC Fixed Voltage Reference Peripheral output is 2x (2.048V)(2) 11 = Comparator and DAC Fixed Voltage Reference Peripheral output is 4x (4.096V)(2) |

| bit 1-0 | ADFVR<1:0>: ADC Fixed Voltage Reference Selection bit  00 = ADC Fixed Voltage Reference Peripheral output is off.  01 = ADC Fixed Voltage Reference Peripheral output is 1x (1.024V)  10 = ADC Fixed Voltage Reference Peripheral output is 2x (2.048V)(2)  11 = ADC Fixed Voltage Reference Peripheral output is 4x (4.096V)(2)                                                                         |

Note 1: FVRRDY is always '1' on devices with LDO (PIC16F1826/27).

2: Fixed Voltage Reference output cannot exceed VDD.

#### TABLE 14-1: SUMMARY OF REGISTERS ASSOCIATED WITH THE FVR MODULE

| Name   | Bit 7 | Bit 6  | Bit 5    | Bit 4    | Bit 3   | Bit 2   | Bit 1  | Bit 0  | Register on page |

|--------|-------|--------|----------|----------|---------|---------|--------|--------|------------------|

| FVRCON | FVREN | FVRRDY | Reserved | Reserved | CDAFVR1 | CDAFVR0 | ADFVR1 | ADFVR0 | 136              |

Legend: Shaded cells are unused by the FVR module.

#### REGISTER 19-1: CMxCON0: COMPARATOR Cx CONTROL REGISTER 0

| R/W-0/0 | R-0/0 | R/W-0/0 | R/W-0/0 | U-0 | R/W-1/1 | R/W-0/0 | R/W-0/0 |

|---------|-------|---------|---------|-----|---------|---------|---------|

| CxON    | CxOUT | CxOE    | CxPOL   | _   | CxSP    | CxHYS   | CxSYNC  |

| bit 7   |       |         |         |     |         |         | bit 0   |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared

bit 7 **CxON:** Comparator Enable bit

1 = Comparator is enabled and consumes no active power

0 = Comparator is disabled

bit 6 **CxOUT:** Comparator Output bit

If CxPOL = 1 (inverted polarity):

1 = CxVP < CxVN0 = CxVP > CxVN

If CxPOL = 0 (non-inverted polarity):

1 = CxVP > CxVN

0 = CxVP < CxVN

bit 5 **CxOE:** Comparator Output Enable bit

1 = CXOUT is present on the CXOUT pin. Requires that the associated TRIS bit be cleared to actually drive the pin. Not affected by CXON.

0 = CxOUT is internal only

1 = Comparator output is inverted0 = Comparator output is not inverted

bit 3 **Unimplemented:** Read as '0'

bit 2 CxSP: Comparator Speed/Power Select bit

${\tt 1}$  = Comparator operates in normal power, higher speed mode

0 = Comparator operates in low-power, low-speed mode

bit 1 CxHYS: Comparator Hysteresis Enable bit

1 = Comparator hysteresis enabled0 = Comparator hysteresis disabled

CxSYNC: Comparator Output Synchronous Mode bit

1 = Comparator output to Timer1 and I/O pin is synchronous to changes on Timer1 clock source. Output updated on the falling edge of Timer1 clock source.

0 = Comparator output to Timer1 and I/O pin is asynchronous.

bit 0

NOTES:

#### 24.3.2 SETUP FOR PWM OPERATION

The following steps should be taken when configuring the CCP module for standard PWM operation:

- 1. Disable the CCPx pin output driver by setting the associated TRIS bit.

- Load the PRx register with the PWM period value

- 3. Configure the CCP module for the PWM mode by loading the CCPxCON register with the appropriate values.

- Load the CCPRxL register and the DCxBx bits of the CCPxCON register, with the PWM duty cycle value.

- 5. Configure and start Timer2/4/6:

- Select the Timer2/4/6 resource to be used for PWM generation by setting the CxTSEL<1:0> bits in the CCPTMRS register.

- •Clear the TMRxIF interrupt flag bit of the PIRx register. See Note below.

- •Configure the TxCKPS bits of the TxCON register with the Timer prescale value.

- •Enable the Timer by setting the TMRxON bit of the TxCON register.

- 6. Enable PWM output pin:

- Wait until the Timer overflows and the TMRxIF bit of the PIRx register is set. See Note below.

- •Enable the CCPx pin output driver by clearing the associated TRIS bit.

Note: In order to send a complete duty cycle and period on the first PWM output, the above steps must be included in the setup sequence. If it is not critical to start with a complete PWM signal on the first output, then step 6 may be ignored.

#### 24.3.3 TIMER2/4/6 TIMER RESOURCE

The PWM standard mode makes use of one of the 8-bit Timer2/4/6 timer resources to specify the PWM period.

Configuring the CxTSEL<1:0> bits in the CCPTMRS register selects which Timer2/4/6 timer is used.

#### 24.3.4 PWM PERIOD

The PWM period is specified by the PRx register of Timer2/4/6. The PWM period can be calculated using the formula of Equation 24-1.

#### **EQUATION 24-1: PWM PERIOD**

$$PWM \ Period = [(PRx) + 1] \bullet 4 \bullet TOSC \bullet$$

$(TMRx \ Prescale \ Value)$

Note 1: Tosc = 1/Fosc

When TMRx is equal to PRx, the following three events occur on the next increment cycle:

- · TMRx is cleared

- The CCPx pin is set. (Exception: If the PWM duty cycle = 0%, the pin will not be set.)

- The PWM duty cycle is latched from CCPRxL into CCPRxH.

Note: The Timer postscaler (see Section 22.1 "Timer2/4/6 Operation") is not used in the determination of the PWM frequency.

#### 24.3.5 PWM DUTY CYCLE

The PWM duty cycle is specified by writing a 10-bit value to multiple registers: CCPRxL register and DCxB<1:0> bits of the CCPxCON register. The CCPRxL contains the eight MSbs and the DCxB<1:0> bits of the CCPxCON register contain the two LSbs. CCPRxL and DCxB<1:0> bits of the CCPxCON register can be written to at any time. The duty cycle value is not latched into CCPRxH until after the period completes (i.e., a match between PRx and TMRx registers occurs). While using the PWM, the CCPRxH register is read-only.

Equation 24-2 is used to calculate the PWM pulse width.

Equation 24-3 is used to calculate the PWM duty cycle ratio.

#### **EQUATION 24-2: PULSE WIDTH**

Pulse Width = (CCPRxL:CCPxCON<5:4>) •

TOSC • (TMRx Prescale Value)

#### **EQUATION 24-3: DUTY CYCLE RATIO**

Duty Cycle Ratio =  $\frac{(CCPRxL:CCPxCON<5:4>)}{4(PRx+1)}$

The CCPRxH register and a 2-bit internal latch are used to double buffer the PWM duty cycle. This double buffering is essential for glitchless PWM operation.

The 8-bit timer TMRx register is concatenated with either the 2-bit internal system clock (Fosc), or 2 bits of the prescaler, to create the 10-bit time base. The system clock is used if the Timer2/4/6 prescaler is set to 1:1.

When the 10-bit time base matches the CCPRxH and 2-bit latch, then the CCPx pin is cleared (see Figure 24-4).

#### 24.3.7 OPERATION IN SLEEP MODE

In Sleep mode, the TMRx register will not increment and the state of the module will not change. If the CCPx pin is driving a value, it will continue to drive that value. When the device wakes up, TMRx will continue from its previous state.

## 24.3.8 CHANGES IN SYSTEM CLOCK FREQUENCY

The PWM frequency is derived from the system clock frequency. Any changes in the system clock frequency will result in changes to the PWM frequency. See Section 5.0 "Oscillator Module (With Fail-Safe Clock Monitor)" for additional details.

#### 24.3.9 EFFECTS OF RESET

Any Reset will force all ports to Input mode and the CCP registers to their Reset states.

#### 24.3.10 ALTERNATE PIN LOCATIONS

This module incorporates I/O pins that can be moved to other locations with the use of the alternate pin function registers, APFCON0 and APFCON1. To determine which pins can be moved and what their default locations are upon a reset, see **Section 12.1 "Alternate Pin Function"** for more information.

TABLE 24-8: SUMMARY OF REGISTERS ASSOCIATED WITH STANDARD PWM

| Name     | Bit 7                                         | Bit 6               | Bit 5         | Bit 4                  | Bit 3                  | Bit 2   | Bit 1   | Bit 0   | Register on Page |

|----------|-----------------------------------------------|---------------------|---------------|------------------------|------------------------|---------|---------|---------|------------------|

| APFCON0  | RXDTSEL                                       | SDO1SEL             | SS1SEL        | P2BSEL <sup>(2)</sup>  | CCP2SEL <sup>(2)</sup> | P1DSEL  | P1CSEL  | CCP1SEL | 119              |

| CCPxCON  | PxM1 <sup>(1)</sup>                           | PxM0 <sup>(1)</sup> | DCxB1         | DCxB0                  | CCPxM3                 | CCPxM2  | CCPxM1  | CCPxM0  | 226              |

| CCPxAS   | CCPxASE                                       | CCPxAS2             | CCPxAS1       | CCPxAS0                | PSSxAC1                | PSSxAC0 | PSSxBD1 | PSSxBD0 | 228              |

| CCPTMRS  | C4TSEL1                                       | C4TSEL0             | C3TSEL1       | C3TSEL0                | C2TSEL1                | C2TSEL0 | C1TSEL1 | C1TSEL0 | 227              |

| INTCON   | GIE                                           | PEIE                | TMR0IE        | INTE                   | IOCIE                  | TMR0IF  | INTF    | IOCIF   | 86               |

| PR2      | Timer2 Perio                                  | d Register          |               |                        |                        |         |         |         | 189*             |

| PR4      | Timer4 Module Period Register                 |                     |               |                        |                        |         |         |         | 189*             |

| PR6      | Timer6 Modu                                   | ule Period Re       | gister        |                        |                        |         |         |         | 189*             |

| PSTRxCON | _                                             | _                   | _             | STRxSYNC               | STRxD                  | STRxC   | STRxB   | STRxA   | 230              |

| PWMxCON  | PxRSEN                                        | PxDC6               | PxDC5         | PxDC4                  | PxDC3                  | PxDC2   | PxDC1   | PxDC0   | 229              |

| T2CON    | _                                             | T2OUTPS3            | T2OUTPS2      | T2OUTPS1               | T2OUTPS0               | TMR2ON  | T2CKPS1 | T2CKPS0 | 191              |

| T4CON    | _                                             | T4OUTPS3            | T4OUTPS2      | T4OUTPS1               | T4OUTPS0               | TMR4ON  | T4CKPS1 | T4CKPS0 | 191              |

| T6CON    | _                                             | T6OUTPS3            | T6OUTPS2      | T6OUTPS1               | T6OUTPS0               | TMR6ON  | T6CKPS1 | T6CKPS0 | 191              |

| TMR2     | Holding Register for the 8-bit TMR2 Time Base |                     |               |                        |                        |         |         |         |                  |

| TMR4     | Holding Reg                                   | ister for the 8-    | -bit TMR4 Tin | ne Base <sup>(1)</sup> |                        |         |         |         | 189*             |

| TMR6     | Holding Reg                                   | ister for the 8-    | -bit TMR6 Tin | ne Base <sup>(1)</sup> |                        |         |         |         | 189*             |

| TRISB    | TRISB7                                        | TRISB6              | TRISB5        | TRISB4                 | TRISB3                 | TRISB2  | TRISB1  | TRISB0  | 127              |

**Legend:** — = Unimplemented locations, read as '0'. Shaded cells are not used by the PWM.

\* Page provides register information.

Note 1: Applies to ECCP modules only.

2: PIC16(L)F1827 only.

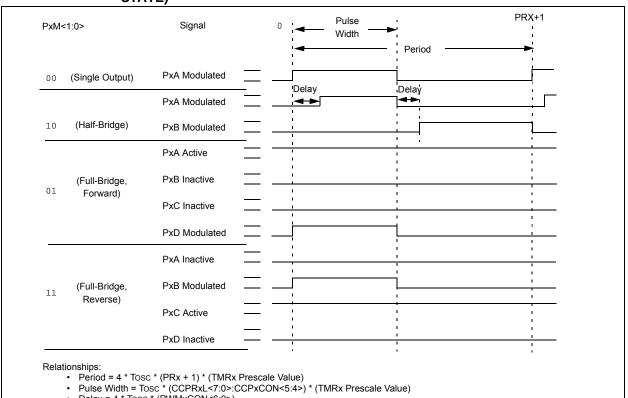

**TABLE 24-9: EXAMPLE PIN ASSIGNMENTS FOR VARIOUS PWM ENHANCED MODES**

| ECCP Mode            | PxM<1:0> | CCPx/PxA           | PxB                | PxC                | PxD                |

|----------------------|----------|--------------------|--------------------|--------------------|--------------------|

| Single               | 00       | Yes <sup>(1)</sup> | Yes <sup>(1)</sup> | Yes <sup>(1)</sup> | Yes <sup>(1)</sup> |

| Half-Bridge          | 10       | Yes                | Yes                | No                 | No                 |

| Full-Bridge, Forward | 01       | Yes                | Yes                | Yes                | Yes                |

| Full-Bridge, Reverse | 11       | Yes                | Yes                | Yes                | Yes                |

Note 1: PWM Steering enables outputs in Single mode.

**FIGURE 24-6: EXAMPLE PWM (ENHANCED MODE) OUTPUT RELATIONSHIPS (ACTIVE-HIGH**

Delay = 4 \* Tosc \* (PWMxCON<6:0>)

#### 24.5 CCP Control Registers

#### REGISTER 24-1: CCPxCON: CCPx CONTROL REGISTER

| R/W-00                  | R/W-0/0 |

|-------------------------|---------|---------|---------|---------|---------|---------|---------|

| PxM<1:0> <sup>(1)</sup> |         | DCxE    | 3<1:0>  |         | CCPxN   | M<3:0>  |         |

| bit 7                   |         |         |         |         |         |         | bit 0   |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Reset

'1' = Bit is set '0' = Bit is cleared

bit 7-6 PxM<1:0>: Enhanced PWM Output Configuration bits<sup>(1)</sup>

Capture mode:

Unused

Compare mode:

Unused

If CCPxM<3:2> = 00, 01, 10:

xx = PxA assigned as Capture/Compare input; PxB, PxC, PxD assigned as port pins

If CCPxM<3:2> = 11:

00 = Single output; PxA modulated; PxB, PxC, PxD assigned as port pins

01 = Full-Bridge output forward; PxD modulated; PxA active; PxB, PxC inactive

10 = Half-Bridge output; PxA, PxB modulated with dead-band control; PxC, PxD assigned as port pins

11 = Full-Bridge output reverse; PxB modulated; PxC active; PxA, PxD inactive

bit 5-4 DCxB<1:0>: PWM Duty Cycle Least Significant bits

Capture mode:

Unused

Compare mode:

Unused

PWM mode:

These bits are the two LSbs of the PWM duty cycle. The eight MSbs are found in CCPRxL.

bit 3-0 CCPxM<3:0>: ECCPx Mode Select bits

0000 =Capture/Compare/PWM off (resets ECCPx module)

0001 =Reserved

0010 =Compare mode: toggle output on match

0011 =Reserved

0100 =Capture mode: every falling edge

0101 =Capture mode: every rising edge

0110 =Capture mode: every 4th rising edge

0111 =Capture mode: every 16th rising edge

1000 =Compare mode: initialize ECCPx pin low; set output on compare match (set CCPxIF)

1001 =Compare mode: initialize ECCPx pin high; clear output on compare match (set CCPxIF)

1010 =Compare mode: generate software interrupt only; ECCPx pin reverts to I/O state

1011 =Compare mode: Special Event Trigger (ECCPx resets Timer, sets CCPxIF bit, starts A/D conversion if A/D module is enabled)<sup>(1)</sup>

CCP Modules only:

11xx =PWM mode

**ECCP Modules only:**

1100 =PWM mode: PxA, PxC active-high; PxB, PxD active-high

1101 =PWM mode: PxA, PxC active-high; PxB, PxD active-low

1110 =PWM mode: PxA, PxC active-low; PxB, PxD active-high

1111 =PWM mode: PxA, PxC active-low; PxB, PxD active-low

Note 1: These bits are not implemented on CCP<4:3>.

#### 25.6.7 I<sup>2</sup>C MASTER MODE RECEPTION

Master mode reception is enabled by programming the Receive Enable bit, RCEN bit of the SSPxCON2 register.

Note:

The MSSPx module must be in an Idle state before the RCEN bit is set or the RCEN bit will be disregarded.

The Baud Rate Generator begins counting and on each rollover, the state of the SCLx pin changes (high-to-low/low-to-high) and data is shifted into the SSPxSR. After the falling edge of the eighth clock, the receive enable flag is automatically cleared, the contents of the SSPxSR are loaded into the SSPxBUF, the BF flag bit is set, the SSPxIF flag bit is set and the Baud Rate Generator is suspended from counting, holding SCLx low. The MSSPx is now in Idle state awaiting the next command. When the buffer is read by the CPU, the BF flag bit is automatically cleared. The user can then send an Acknowledge bit at the end of reception by setting the Acknowledge Sequence Enable, ACKEN bit of the SSPxCON2 register.

#### 25.6.7.1 BF Status Flag

In receive operation, the BF bit is set when an address or data byte is loaded into SSPxBUF from SSPxSR. It is cleared when the SSPxBUF register is read.

#### 25.6.7.2 SSPxOV Status Flag

In receive operation, the SSPxOV bit is set when 8 bits are received into the SSPxSR and the BF flag bit is already set from a previous reception.

#### 25.6.7.3 WCOL Status Flag

If the user writes the SSPxBUF when a receive is already in progress (i.e., SSPxSR is still shifting in a data byte), the WCOL bit is set and the contents of the buffer are unchanged (the write does not occur).

#### 25.6.7.4 Typical Receive Sequence:

- 1. The user generates a Start condition by setting the SEN bit of the SSPxCON2 register.

- SSPxIF is set by hardware on completion of the Start

- 3. SSPxIF is cleared by software.

- User writes SSPxBUF with the slave address to transmit and the R/W bit set.

- Address is shifted out the SDAx pin until all 8 bits are transmitted. Transmission begins as soon as SSPxBUF is written to.

- The MSSPx module shifts in the ACK bit from the slave device and writes its value into the ACKSTAT bit of the SSPxCON2 register.

- The MSSPx module generates an interrupt at the end of the ninth clock cycle by setting the SSPxIF bit.

- 8. User sets the RCEN bit of the SSPxCON2 register and the Master clocks in a byte from the slave.

- After the 8th falling edge of SCLx, SSPxIF and BF are set.

- 10. Master clears SSPxIF and reads the received byte from SSPxUF, clears BF.

- Master sets ACK value sent to slave in ACKDT bit of the SSPxCON2 register and initiates the ACK by setting the ACKEN bit.

- Masters ACK is clocked out to the Slave and SSPxIF is set.

- 13. User clears SSPxIF.

- 14. Steps 8-13 are repeated for each received byte from the slave.

- 15. Master sends a not  $\overline{\mathsf{ACK}}$  or Stop to end communication.

#### REGISTER 26-3: BAUDCON: BAUD RATE CONTROL REGISTER

| R-0/0  | R-1/1 | U-0 | R/W-0/0 | R/W-0/0 | U-0 | R/W-0/0 | R/W-0/0 |

|--------|-------|-----|---------|---------|-----|---------|---------|

| ABDOVF | RCIDL | _   | SCKP    | BRG16   | _   | WUE     | ABDEN   |

| bit 7  |       |     |         |         |     |         | bit 0   |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared

bit 7 ABDOVF: Auto-Baud Detect Overflow bit

Asynchronous mode:

1 = Auto-baud timer overflowed0 = Auto-baud timer did not overflow

Synchronous mode:

Don't care

bit 6 RCIDL: Receive Idle Flag bit

<u>Asynchronous mode</u>: 1 = Receiver is Idle

0 = Start bit has been received and the receiver is receiving

Synchronous mode:

Don't care

bit 5 **Unimplemented:** Read as '0'

bit 4 SCKP: Synchronous Clock Polarity Select bit

Asynchronous mode:

1 = Transmit inverted data to the TX/CK pin0 = Transmit non-inverted data to the TX/CK pin

Synchronous mode:

1 = Data is clocked on rising edge of the clock0 = Data is clocked on falling edge of the clock

bit 3 BRG16: 16-bit Baud Rate Generator bit

1 = 16-bit Baud Rate Generator is used0 = 8-bit Baud Rate Generator is used

bit 2 **Unimplemented:** Read as '0' bit 1 **WUE:** Wake-up Enable bit

Asynchronous mode:

1 = Receiver is waiting for a falling edge. No character will be received, byte RCIF will be set. WUE will automatically clear after RCIF is set.

0 = Receiver is operating normally

Synchronous mode:

Don't care

bit 0 ABDEN: Auto-Baud Detect Enable bit

Asynchronous mode:

1 = Auto-Baud Detect mode is enabled (clears when auto-baud is complete)

0 = Auto-Baud Detect mode is disabled

Synchronous mode:

Don't care

# 28.2 Low-Voltage Programming Entry Mode

The Low-Voltage Programming Entry mode allows the PIC16(L)F1826/27 devices to be programmed using VDD only, without high voltage. When the LVP bit of Configuration Word 2 is set to '1', the low-voltage ICSP programming entry is enabled. To disable the Low-Voltage ICSP mode, the LVP bit must be programmed to '0'.

Entry into the Low-Voltage Programming Entry mode requires the following steps:

- 1. MCLR is brought to VIL.

- A 32-bit key sequence is presented on ICSPDAT, while clocking ICSPCLK.

Once the key sequence is complete,  $\overline{\text{MCLR}}$  must be held at VIL for as long as Program/Verify mode is to be maintained.

If low-voltage programming is enabled (LVP = 1), the  $\overline{\text{MCLR}}$  Reset function is automatically enabled and cannot be disabled. See **Section 7.3** "**MCLR**" for more information.

The LVP bit can only be reprogrammed to '0' by using the High-Voltage Programming mode.

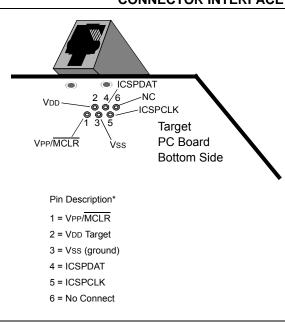

#### 28.3 Common Programming Interfaces

Connection to a target device is typically done through an ICSP™ header. A commonly found connector on development tools is the RJ-11 in the 6P6C (6 pin, 6 connector) configuration. See Figure 28-2.

FIGURE 28-2: ICD RJ-11 STYLE CONNECTOR INTERFACE

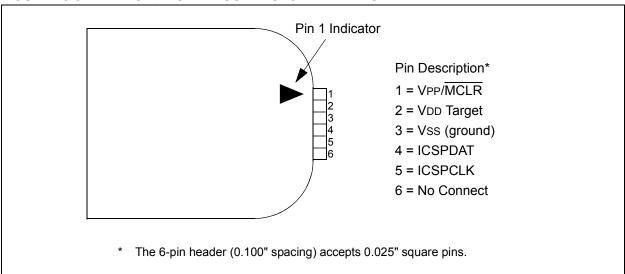

Another connector often found in use with the PICkit™ programmers is a standard 6-pin header with 0.1 inch spacing. Refer to Figure 28-3.

FIGURE 28-3: PICkit™ STYLE CONNECTOR INTERFACE

#### 32.7 MPLAB SIM Software Simulator

The MPLAB SIM Software Simulator allows code development in a PC-hosted environment by simulating the PIC MCUs and dsPIC® DSCs on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a comprehensive stimulus controller. Registers can be logged to files for further run-time analysis. The trace buffer and logic analyzer display extend the power of the simulator to record and track program execution, actions on I/O, most peripherals and internal registers.

The MPLAB SIM Software Simulator fully supports symbolic debugging using the MPLAB C Compilers, and the MPASM and MPLAB Assemblers. The software simulator offers the flexibility to develop and debug code outside of the hardware laboratory environment, making it an excellent, economical software development tool.

#### 32.8 MPLAB REAL ICE In-Circuit Emulator System

MPLAB REAL ICE In-Circuit Emulator System is Microchip's next generation high-speed emulator for Microchip Flash DSC and MCU devices. It debugs and programs PIC<sup>®</sup> Flash MCUs and dsPIC<sup>®</sup> Flash DSCs with the easy-to-use, powerful graphical user interface of the MPLAB Integrated Development Environment (IDE), included with each kit.

The emulator is connected to the design engineer's PC using a high-speed USB 2.0 interface and is connected to the target with either a connector compatible with incircuit debugger systems (RJ11) or with the new high-speed, noise tolerant, Low-Voltage Differential Signal (LVDS) interconnection (CAT5).

The emulator is field upgradable through future firmware downloads in MPLAB IDE. In upcoming releases of MPLAB IDE, new devices will be supported, and new features will be added. MPLAB REAL ICE offers significant advantages over competitive emulators including low-cost, full-speed emulation, run-time variable watches, trace analysis, complex breakpoints, a ruggedized probe interface and long (up to three meters) interconnection cables.

# 32.9 MPLAB ICD 3 In-Circuit Debugger System

MPLAB ICD 3 In-Circuit Debugger System is Microchip's most cost effective high-speed hardware debugger/programmer for Microchip Flash Digital Signal Controller (DSC) and microcontroller (MCU) devices. It debugs and programs PIC® Flash microcontrollers and dsPIC® DSCs with the powerful, yet easy-to-use graphical user interface of MPLAB Integrated Development Environment (IDE).

The MPLAB ICD 3 In-Circuit Debugger probe is connected to the design engineer's PC using a high-speed USB 2.0 interface and is connected to the target with a connector compatible with the MPLAB ICD 2 or MPLAB REAL ICE systems (RJ-11). MPLAB ICD 3 supports all MPLAB ICD 2 headers.

# 32.10 PICkit 3 In-Circuit Debugger/ Programmer and PICkit 3 Debug Express

The MPLAB PICkit 3 allows debugging and programming of PIC<sup>®</sup> and dsPIC<sup>®</sup> Flash microcontrollers at a most affordable price point using the powerful graphical user interface of the MPLAB Integrated Development Environment (IDE). The MPLAB PICkit 3 is connected to the design engineer's PC using a full speed USB interface and can be connected to the target via an Microchip debug (RJ-11) connector (compatible with MPLAB ICD 3 and MPLAB REAL ICE). The connector uses two device I/O pins and the reset line to implement in-circuit debugging and In-Circuit Serial Programming ™.

The PICkit 3 Debug Express include the PICkit 3, demo board and microcontroller, hookup cables and CDROM with user's guide, lessons, tutorial, compiler and MPLAB IDE software.

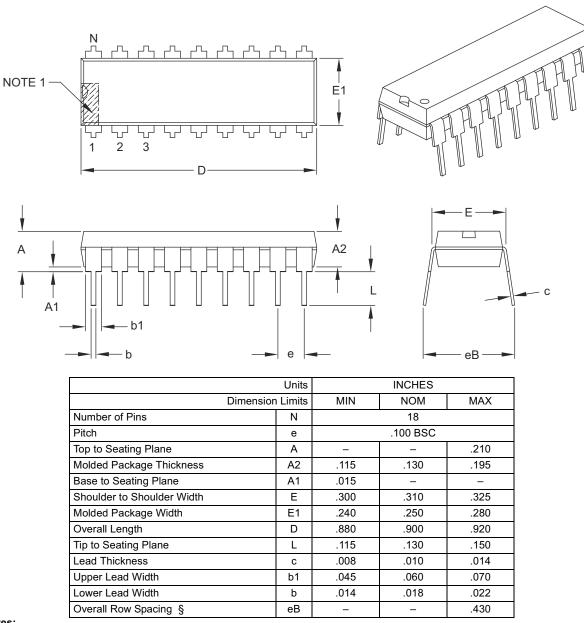

#### 33.2 Package Details

The following sections give the technical details of the packages.

#### 18-Lead Plastic Dual In-Line (P) - 300 mil Body [PDIP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. § Significant Characteristic.

- 3. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing C04-007B