#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 16                                                                         |

| Program Memory Size        | 3.5KB (2K x 14)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 256 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                |

| Data Converters            | A/D 12x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

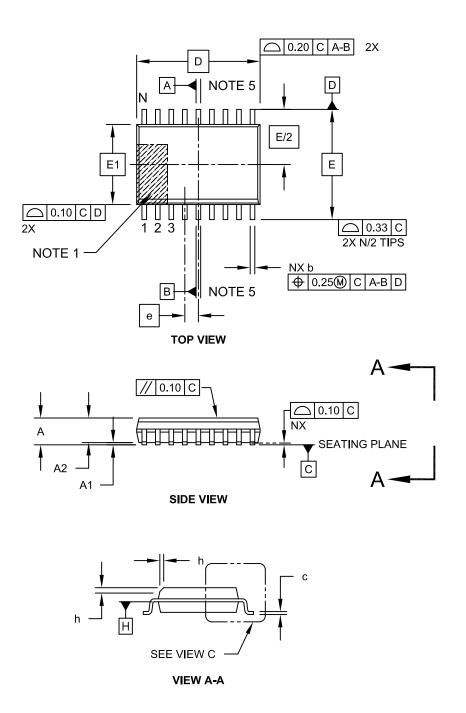

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 28-VQFN Exposed Pad                                                        |

| Supplier Device Package    | 28-QFN (6x6)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1826-i-ml |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

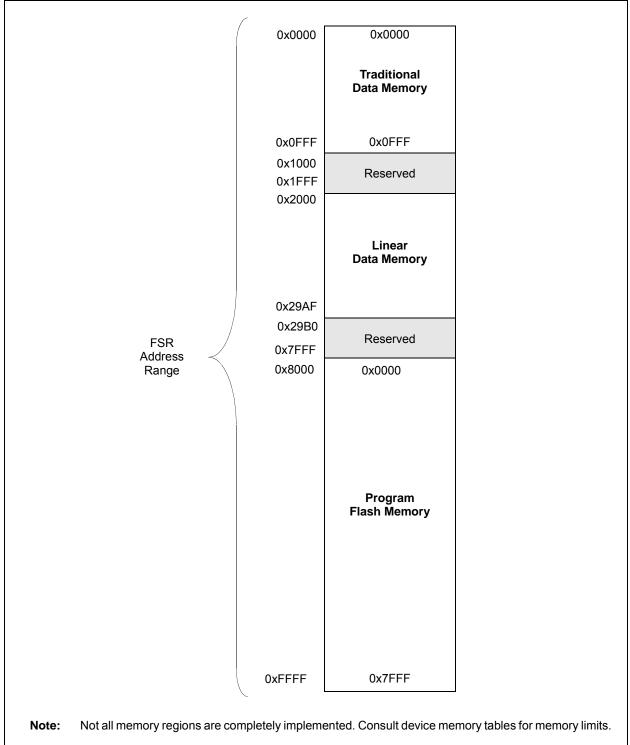

#### TABLE 3-3: PIC16(L)F1826/27 MEMORY MAP (CONTINUED)

|      | BANK 8                        |      | BANK 9                        |      | BANK 10                       |      | BANK 11                       |      | BANK 12                       |      | BANK 13                       |      | BANK 14                       |      | BANK 15                       |

|------|-------------------------------|------|-------------------------------|------|-------------------------------|------|-------------------------------|------|-------------------------------|------|-------------------------------|------|-------------------------------|------|-------------------------------|

| 400h | Core Registers<br>(Table 3-2) | 480h | Core Registers<br>(Table 3-2) | 500h | Core Registers<br>(Table 3-2) | 580h | Core Registers<br>(Table 3-2) | 600h | Core Registers<br>(Table 3-2) | 680h | Core Registers<br>(Table 3-2) | 700h | Core Registers<br>(Table 3-2) | 780h | Core Registers<br>(Table 3-2) |

| 40Bh |                               | 48Bh |                               | 50Bh |                               | 58Bh |                               | 60Bh |                               | 68Bh |                               | 70Bh |                               | 78Bh |                               |

| 40Ch | —                             | 48Ch | —                             | 50Ch | —                             | 58Ch |                               | 60Ch | —                             | 68Ch | —                             | 70Ch | —                             | 78Ch | —                             |

| 40Dh | —                             | 48Dh | —                             | 50Dh | —                             | 58Dh | —                             | 60Dh | —                             | 68Dh | —                             | 70Dh | —                             | 78Dh | —                             |

| 40Eh | _                             | 48Eh | —                             | 50Eh | _                             | 58Eh | _                             | 60Eh | _                             | 68Eh | _                             | 70Eh | _                             | 78Eh | —                             |

| 40Fh | —                             | 48Fh | —                             | 50Fh | _                             | 58Fh |                               | 60Fh | —                             | 68Fh | —                             | 70Fh | —                             | 78Fh | —                             |

| 410h | —                             | 490h | —                             | 510h | _                             | 590h | —                             | 610h | —                             | 690h | —                             | 710h | —                             | 790h | _                             |

| 411h | —                             | 491h | _                             | 511h | _                             | 591h | _                             | 611h | —                             | 691h | —                             | 711h | —                             | 791h | _                             |

| 412h | —                             | 492h | _                             | 512h | —                             | 592h | —                             | 612h | —                             | 692h | —                             | 712h | —                             | 792h | _                             |

| 413h | —                             | 493h | _                             | 513h | —                             | 593h | _                             | 613h | —                             | 693h | —                             | 713h | —                             | 793h | _                             |

| 414h | -                             | 494h | —                             | 514h | —                             | 594h | —                             | 614h | —                             | 694h | —                             | 714h | —                             | 794h | —                             |

| 415h | TMR4 <sup>(1)</sup>           | 495h | —                             | 515h | —                             | 595h | —                             | 615h | —                             | 695h | —                             | 715h | —                             | 795h | —                             |

| 416h | PR4 <sup>(1)</sup>            | 496h | _                             | 516h | _                             | 596h |                               | 616h | —                             | 696h | —                             | 716h | —                             | 796h | _                             |

| 417h | T4CON <sup>(1)</sup>          | 497h | —                             | 517h | —                             | 597h | —                             | 617h | —                             | 697h | —                             | 717h | —                             | 797h | —                             |

| 418h | —                             | 498h | —                             | 518h | —                             | 598h | —                             | 618h | —                             | 698h | —                             | 718h | —                             | 798h | —                             |

| 419h | —                             | 499h | —                             | 519h | —                             | 599h | _                             | 619h | —                             | 699h | —                             | 719h | —                             | 799h | _                             |

| 41Ah | —                             | 49Ah | —                             | 51Ah | _                             | 59Ah | _                             | 61Ah | —                             | 69Ah | —                             | 71Ah | —                             | 79Ah | _                             |

| 41Bh | —                             | 49Bh | —                             | 51Bh | —                             | 59Bh | _                             | 61Bh | —                             | 69Bh | —                             | 71Bh | —                             | 79Bh | _                             |

| 41Ch | TMR6 <sup>(1)</sup>           | 49Ch | _                             | 51Ch | _                             | 59Ch |                               | 61Ch | _                             | 69Ch | _                             | 71Ch | _                             | 79Ch | —                             |

| 41Dh | PR6 <sup>(1)</sup>            | 49Dh | —                             | 51Dh | —                             | 59Dh | _                             | 61Dh | —                             | 69Dh | —                             | 71Dh | —                             | 79Dh | —                             |

| 41Eh | T6CON <sup>(1)</sup>          | 49Eh | _                             | 51Eh | —                             | 59Eh | —                             | 61Eh | —                             | 69Eh | —                             | 71Eh | —                             | 79Eh | —                             |

| 41Fh | —                             | 49Fh | _                             | 51Fh | —                             | 59Fh | _                             | 61Fh | —                             | 69Fh | —                             | 71Fh | —                             | 79Fh | _                             |

| 420h |                               | 4A0h |                               | 520h |                               | 5A0h |                               | 620h |                               | 6A0h |                               | 720h |                               | 7A0h |                               |

|      | Unimplemented<br>Read as '0'  |

| 46Fh |                               | 4EFh |                               | 56Fh |                               | 5EFh |                               | 66Fh |                               | 6EFh |                               | 76Fh |                               | 7EFh |                               |

| 470h |                               | 4F0h |                               | 570h |                               | 5F0h |                               | 670h |                               | 6F0h |                               | 770h |                               | 7F0h |                               |

|      | Accesses<br>70h – 7Fh         |

| 47Fh |                               | 4FFh |                               | 57Fh |                               | 5FFh |                               | 67Fh |                               | 6FFh |                               | 77Fh |                               | 7FFh |                               |

Legend: = Unimplemented data memory locations, read as '0'

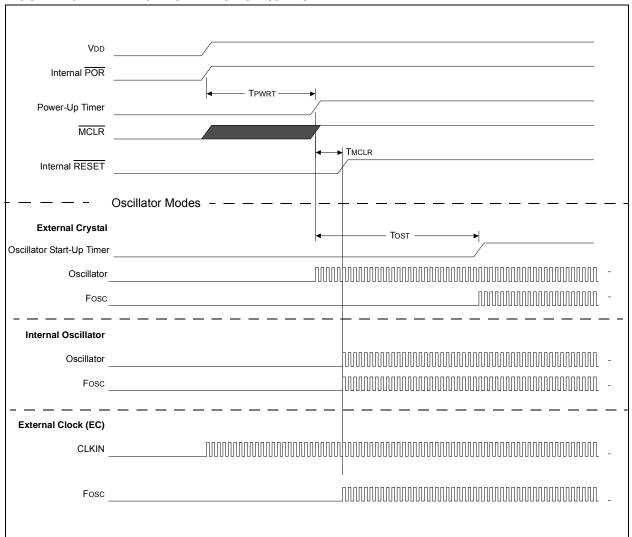

FIGURE 7-3: RESET START-UP SEQUENCE

#### 8.6.3 PIE2 REGISTER

The PIE2 register contains the interrupt enable bits, as shown in Register 8-3.

**Note:** Bit PEIE of the INTCON register must be set to enable any peripheral interrupt.

| REGISTER 8-3: | PIE2: PERIPHERAL INTERRUPT ENABLE REGISTER 2 |

|---------------|----------------------------------------------|

|               |                                              |

| R/W-0/0     | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | U-0 | U-0 | R/W-0/0               |

|-------------|---------|---------|---------|---------|-----|-----|-----------------------|

| OSFIE       | C2IE    | C1IE    | EEIE    | BCL1IE  | —   | _   | CCP2IE <sup>(1)</sup> |

| bit 7 bit 0 |         |         |         |         |     |     |                       |

| Legend:          |                                          |                                                             |                                                       |  |  |  |  |  |

|------------------|------------------------------------------|-------------------------------------------------------------|-------------------------------------------------------|--|--|--|--|--|

| R = Readable bit |                                          | W = Writable bit                                            | U = Unimplemented bit, read as '0'                    |  |  |  |  |  |

| u = Bit is uncha | anged                                    | x = Bit is unknown                                          | -n/n = Value at POR and BOR/Value at all other Resets |  |  |  |  |  |

| '1' = Bit is set |                                          | '0' = Bit is cleared                                        |                                                       |  |  |  |  |  |

| bit 7            |                                          | lator Fail Interrupt Enable                                 |                                                       |  |  |  |  |  |

|                  |                                          | the Oscillator Fail interrup<br>the Oscillator Fail interru |                                                       |  |  |  |  |  |

| bit 6            | C2IE: Compa                              | rator C2 Interrupt Enable                                   | e bit                                                 |  |  |  |  |  |

|                  |                                          | the Comparator C2 interr<br>the Comparator C2 inter         | •                                                     |  |  |  |  |  |

| bit 5            | C1IE: Comparator C1 Interrupt Enable bit |                                                             |                                                       |  |  |  |  |  |

|                  |                                          | the Comparator C1 interr<br>the Comparator C1 inter         | •                                                     |  |  |  |  |  |

| bit 4            | EEIE: EEPRO                              | OM Write Completion Inte                                    | errupt Enable bit                                     |  |  |  |  |  |

|                  |                                          | the EEPROM Write Com<br>the EEPROM Write Com                | · · ·                                                 |  |  |  |  |  |

| bit 3            | BCL1IE: MSS                              | SP1 Bus Collision Interrup                                  | pt Enable bit                                         |  |  |  |  |  |

|                  |                                          | the MSSP1 Bus Collision<br>the MSSP1 Bus Collisior          |                                                       |  |  |  |  |  |

| bit 2-1          | Unimplemen                               | ted: Read as '0'                                            |                                                       |  |  |  |  |  |

| bit 0            | CCP2IE: CCF                              | P2 Interrupt Enable bit                                     |                                                       |  |  |  |  |  |

|                  |                                          | the CCP2 interrupt the CCP2 interrupt                       |                                                       |  |  |  |  |  |

Note 1: PIC16(L)F1827 only.

#### EXAMPLE 11-5: WRITING TO FLASH PROGRAM MEMORY

| ; This                                                                                 | write rout                                                                          | ine assumes the f  | ollowing:                                                                       |  |  |  |  |  |  |

|----------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|--------------------|---------------------------------------------------------------------------------|--|--|--|--|--|--|

| ; 1. The 16 bytes of data are loaded, starting at the address in DATA_ADDR             |                                                                                     |                    |                                                                                 |  |  |  |  |  |  |

| ; 2. Ea                                                                                | ; 2. Each word of data to be written is made up of two adjacent bytes in DATA_ADDR, |                    |                                                                                 |  |  |  |  |  |  |

| ; st                                                                                   | cored in li                                                                         | ittle endian forma | t                                                                               |  |  |  |  |  |  |

| ; 3. A                                                                                 | valid star                                                                          | ting address (the  | e least significant bits = 000) is loaded in ADDRH:ADDRL                        |  |  |  |  |  |  |

| ; $4$ . ADDRH and ADDRL are located in shared data memory $0x70$ - $0x7F$ (common RAM) |                                                                                     |                    |                                                                                 |  |  |  |  |  |  |

| ;                                                                                      |                                                                                     |                    |                                                                                 |  |  |  |  |  |  |

|                                                                                        | BCF                                                                                 |                    | ; Disable ints so required sequences will execute properly                      |  |  |  |  |  |  |

|                                                                                        | BANKSEL EEADRH ; Bank 3                                                             |                    |                                                                                 |  |  |  |  |  |  |

|                                                                                        | MOVE                                                                                |                    | ; Load initial address                                                          |  |  |  |  |  |  |

|                                                                                        | MOVWF<br>MOVF                                                                       |                    | ;<br>;                                                                          |  |  |  |  |  |  |

|                                                                                        | MOVF<br>MOVWF                                                                       | EEADRL             | ;                                                                               |  |  |  |  |  |  |

|                                                                                        | MOVLW                                                                               |                    | ; Load initial data address                                                     |  |  |  |  |  |  |

|                                                                                        | MOVWF                                                                               | FSR0L              | ;                                                                               |  |  |  |  |  |  |

|                                                                                        | MOVLW                                                                               |                    | ; Load initial data address                                                     |  |  |  |  |  |  |

|                                                                                        | MOVWF                                                                               | FSR0H -            | ;                                                                               |  |  |  |  |  |  |

|                                                                                        | BSF                                                                                 | EECON1, EEPGD      | ; Point to program memory                                                       |  |  |  |  |  |  |

|                                                                                        | BCF                                                                                 | EECON1,CFGS        | ; Not configuration space                                                       |  |  |  |  |  |  |

|                                                                                        | BSF                                                                                 | EECON1,WREN        | ; Enable writes                                                                 |  |  |  |  |  |  |

|                                                                                        | BSF                                                                                 | EECON1,LWLO        | ; Only Load Write Latches                                                       |  |  |  |  |  |  |

| LOOP                                                                                   |                                                                                     |                    |                                                                                 |  |  |  |  |  |  |

|                                                                                        | MOVIW                                                                               | FSR0++             | ; Load first data byte into lower                                               |  |  |  |  |  |  |

|                                                                                        | MOVWF                                                                               |                    | ;                                                                               |  |  |  |  |  |  |

|                                                                                        | MOVIW                                                                               |                    | ; Load second data byte into upper                                              |  |  |  |  |  |  |

|                                                                                        | MOVWF                                                                               | EEDATH             | ;                                                                               |  |  |  |  |  |  |

|                                                                                        | MOME                                                                                |                    | ; Check if lower bits of address are '000'                                      |  |  |  |  |  |  |

|                                                                                        | MOVF<br>XORLW                                                                       |                    | ; Check if we're on the last of 8 addresses                                     |  |  |  |  |  |  |

|                                                                                        | ANDLW                                                                               |                    | ;                                                                               |  |  |  |  |  |  |

|                                                                                        | BTFSC                                                                               |                    | ,<br>; Exit if last of eight words,                                             |  |  |  |  |  |  |

|                                                                                        | GOTO                                                                                |                    | ;                                                                               |  |  |  |  |  |  |

|                                                                                        |                                                                                     |                    |                                                                                 |  |  |  |  |  |  |

|                                                                                        | MOVLW                                                                               | 55h                | ; Start of required write sequence:                                             |  |  |  |  |  |  |

|                                                                                        | MOVWF                                                                               | EECON2             | ; Write 55h                                                                     |  |  |  |  |  |  |

| ъ 8                                                                                    | MOVLW                                                                               | 0AAh               | ;                                                                               |  |  |  |  |  |  |

| enc                                                                                    | MOVWF                                                                               |                    | ; Write AAh                                                                     |  |  |  |  |  |  |

| Required<br>Sequence                                                                   | BSF                                                                                 |                    | ; Set WR bit to begin write                                                     |  |  |  |  |  |  |

| ጁ ∾                                                                                    | NOP                                                                                 |                    | ; Any instructions here are ignored as processor                                |  |  |  |  |  |  |

|                                                                                        | NOD                                                                                 |                    | ; halts to begin write sequence                                                 |  |  |  |  |  |  |

|                                                                                        | NOP                                                                                 |                    | ; Processor will stop here and wait for write to complete.                      |  |  |  |  |  |  |

|                                                                                        |                                                                                     |                    | ; After write processor continues with 3rd instruction.                         |  |  |  |  |  |  |

|                                                                                        | INCE                                                                                |                    | · Otill looding latebox Transmost address                                       |  |  |  |  |  |  |

|                                                                                        | INCF<br>GOTO                                                                        |                    | ; Still loading latches Increment address<br>; Write next latches               |  |  |  |  |  |  |

|                                                                                        | 9010                                                                                | HOOF               | / WITCH MEAL TALCHES                                                            |  |  |  |  |  |  |

| START_V                                                                                | VRITE                                                                               |                    |                                                                                 |  |  |  |  |  |  |

| _                                                                                      | BCF                                                                                 | EECON1,LWLO        | ; No more loading latches - Actually start Flash program                        |  |  |  |  |  |  |

|                                                                                        |                                                                                     |                    | ; memory write                                                                  |  |  |  |  |  |  |

|                                                                                        |                                                                                     |                    |                                                                                 |  |  |  |  |  |  |

|                                                                                        | MOVLW                                                                               |                    | ; Start of required write sequence:                                             |  |  |  |  |  |  |

|                                                                                        | MOVWF                                                                               |                    | ; Write 55h                                                                     |  |  |  |  |  |  |

| nce                                                                                    | MOVLW                                                                               |                    | ;<br>: Write AAb                                                                |  |  |  |  |  |  |

| Required<br>Sequence                                                                   | MOVWF                                                                               |                    | ; Write AAh<br>: Set WP bit to begin write                                      |  |  |  |  |  |  |

| Sec                                                                                    | BSF<br>NOP                                                                          |                    | ; Set WR bit to begin write<br>; Any instructions here are ignored as processor |  |  |  |  |  |  |

|                                                                                        | 1105                                                                                |                    | ; halts to begin write sequence                                                 |  |  |  |  |  |  |

|                                                                                        | NOP                                                                                 |                    | ; Processor will stop here and wait for write complete.                         |  |  |  |  |  |  |

|                                                                                        |                                                                                     |                    |                                                                                 |  |  |  |  |  |  |

|                                                                                        |                                                                                     |                    | ; after write processor continues with 3rd instruction                          |  |  |  |  |  |  |

|                                                                                        | BCF                                                                                 |                    | ; Disable writes                                                                |  |  |  |  |  |  |

|                                                                                        | BSF                                                                                 | INTCON, GIE        | ; Enable interrupts                                                             |  |  |  |  |  |  |

|                                                                                        |                                                                                     |                    |                                                                                 |  |  |  |  |  |  |

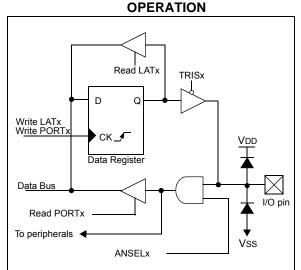

#### 12.0 I/O PORTS

Depending on the device selected and peripherals enabled, there are two ports available. In general, when a peripheral is enabled, that pin may not be used as a general purpose I/O pin.

Each port has three registers for its operation. These registers are:

- TRISx registers (data direction register)

- PORTx registers (reads the levels on the pins of the device)

- LATx registers (output latch)

Some ports may have one or more of the following additional registers. These registers are:

- ANSELx (analog select)

- WPUx (weak pull-up)

### TABLE 12-1:PORT AVAILABILITY PER<br/>DEVICE

| Device        | PORTA | РОКТВ | PORTC |

|---------------|-------|-------|-------|

| PIC16(L)F1826 | •     | ٠     |       |

| PIC16(L)F1827 | •     | •     | •     |

The Data Latch (LATx registers) is useful for read-modify-write operations on the value that the I/O pins are driving.

A write operation to the LATx register has the same effect as a write to the corresponding PORTx register. A read of the LATx register reads of the values held in the I/O PORT latches, while a read of the PORTx register reads the actual I/O pin value.

Ports with analog functions also have an ANSELx register which can disable the digital input and save power. A simplified model of a generic I/O port, without the interfaces to other peripherals, is shown in Figure 12-1.

### FIGURE 12-1: GENERIC I/O PORT

#### EXAMPLE 12-1: INITIALIZING PORTA

- ; initializing the PORTA register. The

- ; other ports are initialized in the same

- ; manner.

| BANKSEL | PORTA       | ;                      |

|---------|-------------|------------------------|

| CLRF    | PORTA       | ;Init PORTA            |

| BANKSEL | LATA        | ;Data Latch            |

| CLRF    | LATA        | ;                      |

| BANKSEL | ANSELA      | ;                      |

| CLRF    | ANSELA      | ;digital I/O           |

| BANKSEL | TRISA       | ;                      |

| MOVLW   | B'00111000' | ;Set RA<5:3> as inputs |

| MOVWF   | TRISA       | ;and set RA<2:0> as    |

|         |             | ;outputs               |

|         |             |                        |

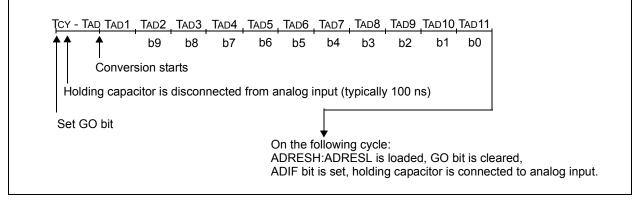

#### TABLE 16-1: ADC CLOCK PERIOD (TAD) Vs. DEVICE OPERATING FREQUENCIES

| ADC Clock Period (TAD) |           | Device Frequency (Fosc)     |                             |                             |                             |                             |                               |  |  |

|------------------------|-----------|-----------------------------|-----------------------------|-----------------------------|-----------------------------|-----------------------------|-------------------------------|--|--|

| ADC<br>Clock Source    | ADCS<2:0> | 32 MHz                      | 20 MHz                      | 16 MHz                      | 8 MHz                       | 4 MHz                       | 1 MHz                         |  |  |

| Fosc/2                 | 000       | 62.5ns <sup>(2)</sup>       | 100 ns <sup>(2)</sup>       | 125 ns <sup>(2)</sup>       | 250 ns <sup>(2)</sup>       | 500 ns <sup>(2)</sup>       | 2.0 μs                        |  |  |

| Fosc/4                 | 100       | 125 ns <sup>(2)</sup>       | 200 ns <sup>(2)</sup>       | 250 ns <sup>(2)</sup>       | 500 ns <sup>(2)</sup>       | 1.0 μs                      | 4.0 μs                        |  |  |

| Fosc/8                 | 001       | 0.5 μs <sup>(2)</sup>       | 400 ns <sup>(2)</sup>       | 0.5 μs <sup>(2)</sup>       | 1.0 μs                      | 2.0 μs                      | 8.0 μs <sup>(3)</sup>         |  |  |

| Fosc/16                | 101       | 800 ns                      | 800 ns                      | 1.0 μs                      | 2.0 μs                      | 4.0 μs                      | 16.0 μs <b><sup>(3)</sup></b> |  |  |

| Fosc/32                | 010       | 1.0 μs                      | 1.6 μs                      | 2.0 μs                      | 4.0 μs                      | 8.0 μs <sup>(3)</sup>       | 32.0 μs <sup>(3)</sup>        |  |  |

| Fosc/64                | 110       | 2.0 μs                      | 3.2 μs                      | 4.0 μs                      | 8.0 μs <sup>(3)</sup>       | 16.0 μs <sup>(3)</sup>      | 64.0 μs <sup>(3)</sup>        |  |  |

| FRC                    | x11       | 1.0-6.0 μs <sup>(1,4)</sup>   |  |  |

Legend: Shaded cells are outside of recommended range.

**Note 1:** The FRC source has a typical TAD time of 1.6  $\mu$ s for VDD.

2: These values violate the minimum required TAD time.

3: For faster conversion times, the selection of another clock source is recommended.

4: The ADC clock period (TAD) and total ADC conversion time can be minimized when the ADC clock is derived from the system clock FOSC. However, the FRC clock source must be used when conversions are to be performed with the device in Sleep mode.

| R/W-x/u          | U-0          | U-0                                | U-0            | R/W-x/u           | R/W-x/u          | R/W-x/u          | R/W-x/u      |

|------------------|--------------|------------------------------------|----------------|-------------------|------------------|------------------|--------------|

| MDMSODIS         | _            | _                                  | _              |                   | MDMS             | S<3:0>           |              |

| bit 7            |              |                                    |                |                   |                  |                  | bit 0        |

|                  |              |                                    |                |                   |                  |                  |              |

| Legend:          |              |                                    |                |                   |                  |                  |              |

| R = Readable     | bit          | W = Writable                       | bit            | U = Unimplen      | nented bit, read | as '0'           |              |

| u = Bit is uncha | anged        | x = Bit is unkr                    | iown           | -n/n = Value a    | at POR and BO    | R/Value at all c | other Resets |

| '1' = Bit is set |              | '0' = Bit is clea                  | ared           |                   |                  |                  |              |

|                  |              |                                    |                |                   |                  |                  |              |

| bit 7            | MDMSODIS:    | Modulation So                      | urce Output    | Disable bit       |                  |                  |              |

|                  | 1 = Output s | ignal driving the                  | e peripheral o | output pin (selec | ted by MDMS<     | 3:0>) is disable | ed           |

|                  | 0 = Output s | ignal driving the                  | e peripheral o | output pin (selec | ted by MDMS<     | 3:0>) is enable  | ed           |

| bit 6-4          | Unimplemen   | ted: Read as '                     | כי             |                   |                  |                  |              |

| bit 3-0          | MDMS<3:0>    | Modulation Sou                     | urce Selectio  | n bits            |                  |                  |              |

|                  | 1111 = Res   | erved. No char                     | nnel connect   | ed.               |                  |                  |              |

|                  | 1110 = Res   | erved. No char                     | nnel connect   | ed.               |                  |                  |              |

|                  | 1101 = Res   | erved. No char                     | nnel connect   | ed.               |                  |                  |              |

|                  |              | erved. No char                     |                |                   |                  |                  |              |

|                  |              | erved. No char                     |                | ed.               |                  |                  |              |

|                  |              | SART TX output                     |                |                   |                  |                  |              |

|                  |              | SP2 SDOx outp                      |                |                   |                  |                  |              |

|                  |              | SP1 SDOx outp                      |                |                   |                  |                  |              |

|                  |              | nparator2 outpu<br>nparator1 outpu |                |                   |                  |                  |              |

|                  |              | P4 output (PWN                     |                | le only)          |                  |                  |              |

|                  |              | P3 output (PWN                     |                |                   |                  |                  |              |

|                  |              | P2 output (PWN                     |                |                   |                  |                  |              |

|                  | 0010 = CCF   |                                    |                |                   |                  |                  |              |

|                  | 0001 = MDN   |                                    |                | <i>,</i>          |                  |                  |              |

|                  | 0000 = MDE   | BIT bit of MDCC                    | DN register is | modulation sou    | urce             |                  |              |

#### REGISTER 23-2: MDSRC: MODULATION SOURCE CONTROL REGISTER

Note 1: Narrowed carrier pulse widths or spurs may occur in the signal stream if the carrier is not synchronized.

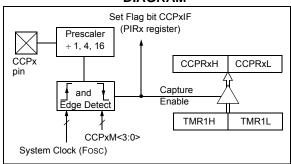

#### 24.1 Capture Mode

The Capture mode function described in this section is available and identical for CCP modules ECCP1, ECCP2, CCP3 and CCP4.

Capture mode makes use of the 16-bit Timer1 resource. When an event occurs on the CCPx pin, the 16-bit CCPRxH:CCPRxL register pair captures and stores the 16-bit value of the TMR1H:TMR1L register pair, respectively. An event is defined as one of the following and is configured by the CCPxM<3:0> bits of the CCPxCON register:

- · Every falling edge

- Every rising edge

- Every 4th rising edge

- · Every 16th rising edge

When a capture is made, the Interrupt Request Flag bit CCPxIF of the PIRx register is set. The interrupt flag must be cleared in software. If another capture occurs before the value in the CCPRxH, CCPRxL register pair is read, the old captured value is overwritten by the new captured value.

Figure 24-1 shows a simplified diagram of the Capture operation.

#### 24.1.1 CCP PIN CONFIGURATION

In Capture mode, the CCPx pin should be configured as an input by setting the associated TRIS control bit.

Also, the CCPx pin function can be moved to alternative pins using the APFCON0 register. Refer to **Section 12.1 "Alternate Pin Function"** for more details.

**Note:** If the CCPx pin is configured as an output, a write to the port can cause a capture condition.

#### FIGURE 24-1: CAPTURE MODE OPERATION BLOCK DIAGRAM

#### 24.1.2 TIMER1 MODE RESOURCE

Timer1 must be running in Timer mode or Synchronized Counter mode for the CCP module to use the capture feature. In Asynchronous Counter mode, the capture operation may not work.

See Section 21.0 "Timer1 Module with Gate Control" for more information on configuring Timer1.

#### 24.1.3 SOFTWARE INTERRUPT MODE

When the Capture mode is changed, a false capture interrupt may be generated. The user should keep the CCPxIE interrupt enable bit of the PIEx register clear to avoid false interrupts. Additionally, the user should clear the CCPxIF interrupt flag bit of the PIRx register following any change in Operating mode.

#### 24.1.4 CCP PRESCALER

There are four prescaler settings specified by the CCPxM<3:0> bits of the CCPxCON register. Whenever the CCP module is turned off, or the CCP module is not in Capture mode, the prescaler counter is cleared. Any Reset will clear the prescaler counter.

Switching from one capture prescaler to another does not clear the prescaler and may generate a false interrupt. To avoid this unexpected operation, turn the module off by clearing the CCPxCON register before changing the prescaler. Equation 24-1 demonstrates the code to perform this function.

#### EXAMPLE 24-1: CHANGING BETWEEN CAPTURE PRESCALERS

| BANKSEL | CCPxCON     | ;Set Bank bits to point |

|---------|-------------|-------------------------|

|         |             | ;to CCPxCON             |

| CLRF    | CCPxCON     | ;Turn CCP module off    |

| MOVLW   | NEW_CAPT_PS | ;Load the W reg with    |

|         |             | ;the new prescaler      |

|         |             | ;move value and CCP ON  |

| MOVWF   | CCPxCON     | ;Load CCPxCON with this |

|         |             | ;value                  |

|         |             |                         |

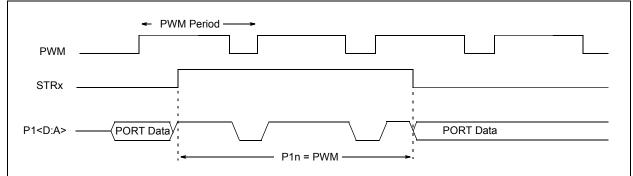

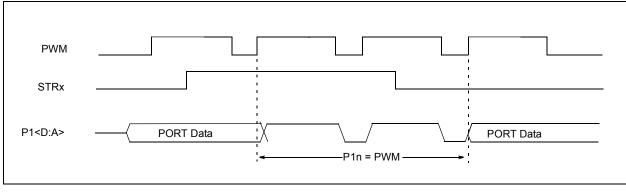

#### 24.4.6.1 Steering Synchronization

The STRxSYNC bit of the PSTRxCON register gives the user two selections of when the steering event will happen. When the STRxSYNC bit is '0', the steering event will happen at the end of the instruction that writes to the PSTRxCON register. In this case, the output signal at the Px<D:A> pins may be an incomplete PWM waveform. This operation is useful when the user firmware needs to immediately remove a PWM signal from the pin.

When the STRxSYNC bit is '1', the effective steering update will happen at the beginning of the next PWM period. In this case, steering on/off the PWM output will always produce a complete PWM waveform.

Figures 24-19 and 24-20 illustrate the timing diagrams of the PWM steering depending on the STRxSYNC setting.

#### 24.4.7 START-UP CONSIDERATIONS

When any PWM mode is used, the application hardware must use the proper external pull-up and/or pull-down resistors on the PWM output pins.

The CCPxM<1:0> bits of the CCPxCON register allow the user to choose whether the PWM output signals are active-high or active-low for each pair of PWM output pins (PxA/PxC and PxB/PxD). The PWM output polarities must be selected before the PWM pin output drivers are enabled. Changing the polarity configuration while the PWM pin output drivers are enable is not recommended since it may result in damage to the application circuits.

The PxA, PxB, PxC and PxD output latches may not be in the proper states when the PWM module is initialized. Enabling the PWM pin output drivers at the same time as the Enhanced PWM modes may cause damage to the application circuit. The Enhanced PWM modes must be enabled in the proper Output mode and complete a full PWM cycle before enabling the PWM pin output drivers. The completion of a full PWM cycle is indicated by the TMRxIF bit of the PIRx register being set as the second PWM period begins.

Note: When the microcontroller is released from Reset, all of the I/O pins are in the high-impedance state. The external circuits must keep the power switch devices in the Off state until the microcontroller drives the I/O pins with the proper signal levels or activates the PWM output(s).

#### 24.4.8 ALTERNATE PIN LOCATIONS

This module incorporates I/O pins that can be moved to other locations with the use of the alternate pin function registers, APFCON0 and APFCON1. To determine which pins can be moved and what their default locations are upon a reset, see **Section 12.1 "Alternate Pin Function"** for more information.

#### FIGURE 24-19: EXAMPLE OF STEERING EVENT AT END OF INSTRUCTION (STRxSYNC = 0)

#### FIGURE 24-20: EXAMPLE OF STEERING EVENT AT BEGINNING OF INSTRUCTION (STRxSYNC = 1)

#### 25.6.6 I<sup>2</sup>C MASTER MODE TRANSMISSION

Transmission of a data byte, a 7-bit address or the other half of a 10-bit address is accomplished by simply writing a value to the SSPxBUF register. This action will set the Buffer Full flag bit, BF and allow the Baud Rate Generator to begin counting and start the next transmission. Each bit of address/data will be shifted out onto the SDAx pin after the falling edge of SCLx is asserted. SCLx is held low for one Baud Rate Generator rollover count (TBRG). Data should be valid before SCLx is released high. When the SCLx pin is released high, it is held that way for TBRG. The data on the SDAx pin must remain stable for that duration and some hold time after the next falling edge of SCLx. After the eighth bit is shifted out (the falling edge of the eighth clock), the BF flag is cleared and the master releases SDAx. This allows the slave device being addressed to respond with an ACK bit during the ninth bit time if an address match occurred, or if data was received properly. The status of  $\overline{ACK}$  is written into the ACKSTAT bit on the rising edge of the ninth clock. If the master receives an Acknowledge, the Acknowledge Status bit, ACKSTAT, is cleared. If not, the bit is set. After the ninth clock, the SSPxIF bit is set and the master clock (Baud Rate Generator) is suspended until the next data byte is loaded into the SSPxBUF, leaving SCLx low and SDAx unchanged (Figure 25-27).

After the write to the SSPxBUF, each bit of the address will be shifted out on the falling edge of SCLx until all seven address bits and the R/W bit are completed. On the falling edge of the eighth clock, the master will release the SDAx pin, allowing the slave to respond with an Acknowledge. On the falling edge of the ninth clock, the master will sample the SDAx pin to see if the address was recognized by a slave. The status of the ACK bit is loaded into the ACKSTAT Status bit of the SSPxCON2 register. Following the falling edge of the ninth clock transmission of the address, the SSPxIF is set, the BF flag is cleared and the Baud Rate Generator is turned off until another write to the SSPxBUF takes place, holding SCLx low and allowing SDAx to float.

#### 25.6.6.1 BF Status Flag

In Transmit mode, the BF bit of the SSPxSTAT register is set when the CPU writes to SSPxBUF and is cleared when all 8 bits are shifted out.

#### 25.6.6.2 WCOL Status Flag

If the user writes the SSPxBUF when a transmit is already in progress (i.e., SSPxSR is still shifting out a data byte), the WCOL is set and the contents of the buffer are unchanged (the write does not occur).

WCOL must be cleared by software before the next transmission.

#### 25.6.6.3 ACKSTAT Status Flag

In Transmit mode, the ACKSTAT bit of the SSPxCON2 register is cleared when the slave has sent an Acknowledge (ACK = 0) and is set when the slave does not Acknowledge (ACK = 1). A slave sends an Acknowledge when it has recognized its address (including a general call), or when the slave has properly received its data.

25.6.6.4 Typical transmit sequence:

- 1. The user generates a Start condition by setting the SEN bit of the SSPxCON2 register.

- 2. SSPxIF is set by hardware on completion of the Start.

- 3. SSPxIF is cleared by software.

- 4. The MSSPx module will wait the required start time before any other operation takes place.

- 5. The user loads the SSPxBUF with the slave address to transmit.

- Address is shifted out the SDAx pin until all 8 bits are transmitted. Transmission begins as soon as SSPxBUF is written to.

- The MSSPx module shifts in the ACK bit from the slave device and writes its value into the ACKSTAT bit of the SSPxCON2 register.

- The MSSPx module generates an interrupt at the end of the ninth clock cycle by setting the SSPxIF bit.

- 9. The user loads the SSPxBUF with eight bits of data.

- 10. Data is shifted out the SDAx pin until all 8 bits are transmitted.

- 11. The MSSPx module shifts in the ACK bit from the slave device and writes its value into the ACKSTAT bit of the SSPxCON2 register.

- 12. Steps 8-11 are repeated for all transmitted data bytes.

- 13. The user generates a Stop or Restart condition by setting the PEN or RSEN bits of the SSPxCON2 register. Interrupt is generated once the Stop/Restart condition is complete.

| BAUD<br>RATE | SYNC = 0, BRGH = 1, BRG16 = 1 or SYNC = 1, BRG16 = 1 |            |                             |                   |            |                             |                   |            |                             |                    |            |                             |

|--------------|------------------------------------------------------|------------|-----------------------------|-------------------|------------|-----------------------------|-------------------|------------|-----------------------------|--------------------|------------|-----------------------------|

|              | Fosc = 32.000 MHz                                    |            |                             | Fosc = 20.000 MHz |            |                             | Fosc = 18.432 MHz |            |                             | Fosc = 11.0592 MHz |            |                             |

|              | Actual<br>Rate                                       | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate    | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate    | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate     | %<br>Error | SPBRG<br>value<br>(decimal) |

| 300          | 300.0                                                | 0.00       | 26666                       | 300.0             | 0.00       | 16665                       | 300.0             | 0.00       | 15359                       | 300.0              | 0.00       | 9215                        |

| 1200         | 1200                                                 | 0.00       | 6666                        | 1200              | -0.01      | 4166                        | 1200              | 0.00       | 3839                        | 1200               | 0.00       | 2303                        |

| 2400         | 2400                                                 | 0.01       | 3332                        | 2400              | 0.02       | 2082                        | 2400              | 0.00       | 1919                        | 2400               | 0.00       | 1151                        |

| 9600         | 9604                                                 | 0.04       | 832                         | 9597              | -0.03      | 520                         | 9600              | 0.00       | 479                         | 9600               | 0.00       | 287                         |

| 10417        | 10417                                                | 0.00       | 767                         | 10417             | 0.00       | 479                         | 10425             | 0.08       | 441                         | 10433              | 0.16       | 264                         |

| 19.2k        | 19.18k                                               | -0.08      | 416                         | 19.23k            | 0.16       | 259                         | 19.20k            | 0.00       | 239                         | 19.20k             | 0.00       | 143                         |

| 57.6k        | 57.55k                                               | -0.08      | 138                         | 57.47k            | -0.22      | 86                          | 57.60k            | 0.00       | 79                          | 57.60k             | 0.00       | 47                          |

| 115.2k       | 115.9k                                               | 0.64       | 68                          | 116.3k            | 0.94       | 42                          | 115.2k            | 0.00       | 39                          | 115.2k             | 0.00       | 23                          |

#### TABLE 26-5: BAUD RATES FOR ASYNCHRONOUS MODES (CONTINUED)

|        |                  | SYNC = 0, BRGH = 1, BRG16 = 1 or SYNC = 1, BRG16 = 1 |                             |                  |            |                             |                |            |                             |                |            |                             |

|--------|------------------|------------------------------------------------------|-----------------------------|------------------|------------|-----------------------------|----------------|------------|-----------------------------|----------------|------------|-----------------------------|

| BAUD   | Fosc = 8.000 MHz |                                                      |                             | Fosc = 4.000 MHz |            | Fosc = 3.6864 MHz           |                |            | Fosc = 1.000 MHz            |                |            |                             |

| RATE   | Actual<br>Rate   | %<br>Error                                           | SPBRG<br>value<br>(decimal) | Actual<br>Rate   | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) |

| 300    | 300.0            | 0.00                                                 | 6666                        | 300.0            | 0.01       | 3332                        | 300.0          | 0.00       | 3071                        | 300.1          | 0.04       | 832                         |

| 1200   | 1200             | -0.02                                                | 1666                        | 1200             | 0.04       | 832                         | 1200           | 0.00       | 767                         | 1202           | 0.16       | 207                         |

| 2400   | 2401             | 0.04                                                 | 832                         | 2398             | 0.08       | 416                         | 2400           | 0.00       | 383                         | 2404           | 0.16       | 103                         |

| 9600   | 9615             | 0.16                                                 | 207                         | 9615             | 0.16       | 103                         | 9600           | 0.00       | 95                          | 9615           | 0.16       | 25                          |

| 10417  | 10417            | 0                                                    | 191                         | 10417            | 0.00       | 95                          | 10473          | 0.53       | 87                          | 10417          | 0.00       | 23                          |

| 19.2k  | 19.23k           | 0.16                                                 | 103                         | 19.23k           | 0.16       | 51                          | 19.20k         | 0.00       | 47                          | 19.23k         | 0.16       | 12                          |

| 57.6k  | 57.14k           | -0.79                                                | 34                          | 58.82k           | 2.12       | 16                          | 57.60k         | 0.00       | 15                          | —              | _          | _                           |

| 115.2k | 117.6k           | 2.12                                                 | 16                          | 111.1k           | -3.55      | 8                           | 115.2k         | 0.00       | 7                           | —              | —          | —                           |

#### 27.5 Software Control

The software portion of the capacitive sensing module is required to determine the change in frequency of the capacitive sensing oscillator. This is accomplished by the following:

- Setting a fixed time base to acquire counts on Timer0 or Timer1

- Establishing the nominal frequency for the capacitive sensing oscillator

- Establishing the reduced frequency for the capacitive sensing oscillator due to an additional capacitive load

- Set the frequency threshold

#### 27.5.1 NOMINAL FREQUENCY (NO CAPACITIVE LOAD)

To determine the nominal frequency of the capacitive sensing oscillator:

- Remove any extra capacitive load on the selected CPSx pin

- At the start of the fixed time base, clear the timer resource

- At the end of the fixed time base save the value in the timer resource

The value of the timer resource is the number of oscillations of the capacitive sensing oscillator for the given time base. The frequency of the capacitive sensing oscillator is equal to the number of counts on in the timer divided by the period of the fixed time base.

#### 27.5.2 REDUCED FREQUENCY (ADDITIONAL CAPACITIVE LOAD)

The extra capacitive load will cause the frequency of the capacitive sensing oscillator to decrease. To determine the reduced frequency of the capacitive sensing oscillator:

- Add a typical capacitive load on the selected CPSx pin

- Use the same fixed time base as the nominal frequency measurement

- At the start of the fixed time base, clear the timer resource

- At the end of the fixed time base save the value in the timer resource

The value of the timer resource is the number of oscillations of the capacitive sensing oscillator with an additional capacitive load. The frequency of the capacitive sensing oscillator is equal to the number of counts on in the timer divided by the period of the fixed time base. This frequency should be less than the value obtained during the nominal frequency measurement.

#### 27.5.3 FREQUENCY THRESHOLD

The frequency threshold should be placed midway between the value of nominal frequency and the reduced frequency of the capacitive sensing oscillator. Refer to Application Note AN1103, "*Software Handling for Capacitive Sensing*" (DS01103) for more detailed information on the software required for capacitive sensing module.

| Note: | For more information on general capacitive sensing refer to Application Notes:                               |

|-------|--------------------------------------------------------------------------------------------------------------|

|       | <ul> <li>AN1101, "Introduction to Capacitive<br/>Sensing" (DS01101)</li> </ul>                               |

|       | <ul> <li>AN1102, "Layout and Physical<br/>Design Guidelines for Capacitive<br/>Sensing" (DS01102)</li> </ul> |

#### 27.6 Operation during Sleep

The capacitive sensing oscillator will continue to run as long as the module is enabled, independent of the part being in Sleep. In order for the software to determine if a frequency change has occurred, the part must be awake. However, the part does not have to be awake when the timer resource is acquiring counts.

Note: Timer0 does not operate when in Sleep, and therefore cannot be used for capacitive sense measurements in Sleep.

| BCF              | Bit Clear f                                                         |

|------------------|---------------------------------------------------------------------|

| Syntax:          | [label]BCF f,b                                                      |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$ |

| Operation:       | $0 \rightarrow (f \le b >)$                                         |

| Status Affected: | None                                                                |

| Description:     | Bit 'b' in register 'f' is cleared.                                 |

| BTFSC            | Bit Test f, Skip if Clear                                                                                                                                                                                                     |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label]BTFSC f,b                                                                                                                                                                                                              |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$                                                                                                                                                           |

| Operation:       | skip if (f <b>) = 0</b>                                                                                                                                                                                                       |

| Status Affected: | None                                                                                                                                                                                                                          |

| Description:     | If bit 'b' in register 'f' is '1', the next<br>instruction is executed.<br>If bit 'b', in register 'f', is '0', the next<br>instruction is discarded, and a NOP is<br>executed instead, making this a<br>2-cycle instruction. |

| BRA              | Relative Branch                                                                                                                                                                                                                    |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] BRA label<br>[ <i>label</i> ] BRA \$+k                                                                                                                                                                            |

| Operands:        | -256 $\leq$ label - PC + 1 $\leq$ 255 -256 $\leq$ k $\leq$ 255                                                                                                                                                                     |

| Operation:       | $(PC) + 1 + k \rightarrow PC$                                                                                                                                                                                                      |

| Status Affected: | None                                                                                                                                                                                                                               |

| Description:     | Add the signed 9-bit literal 'k' to the PC. Since the PC will have incremented to fetch the next instruction, the new address will be PC + $1 + k$ . This instruction is a two-cycle instruction. This branch has a limited range. |

| BTFSS            | Bit Test f, Skip if Set                                                                                                                                                                                         |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] BTFSS f,b                                                                                                                                                                                             |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b < 7 \end{array}$                                                                                                                                                |

| Operation:       | skip if (f <b>) = 1</b>                                                                                                                                                                                         |

| Status Affected: | None                                                                                                                                                                                                            |

| Description:     | If bit 'b' in register 'f' is '0', the next<br>instruction is executed.<br>If bit 'b' is '1', then the next<br>instruction is discarded and a NOP is<br>executed instead, making this a<br>2-cycle instruction. |

| BRW              | Relative Branch with W                                                                                                                                                                                                 |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] BRW                                                                                                                                                                                                          |

| Operands:        | None                                                                                                                                                                                                                   |

| Operation:       | $(PC) + (W) \to PC$                                                                                                                                                                                                    |

| Status Affected: | None                                                                                                                                                                                                                   |

| Description:     | Add the contents of W (unsigned) to<br>the PC. Since the PC will have incre-<br>mented to fetch the next instruction,<br>the new address will be $PC + 1 + (W)$ .<br>This instruction is a two-cycle instruc-<br>tion. |

| BSF              | Bit Set f                                                           |

|------------------|---------------------------------------------------------------------|

| Syntax:          | [label]BSF f,b                                                      |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$ |

| Operation:       | $1 \rightarrow (f \le b >)$                                         |

| Status Affected: | None                                                                |

| Description:     | Bit 'b' in register 'f' is set.                                     |

| CALL             | Call Subroutine                                                                                                                                                                                                                                 |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] CALL k                                                                                                                                                                                                                         |

| Operands:        | $0 \leq k \leq 2047$                                                                                                                                                                                                                            |

| Operation:       | (PC)+ 1 $\rightarrow$ TOS,<br>k $\rightarrow$ PC<10:0>,<br>(PCLATH<6:3>) $\rightarrow$ PC<14:11>                                                                                                                                                |

| Status Affected: | None                                                                                                                                                                                                                                            |

| Description:     | Call Subroutine. First, return address<br>(PC + 1) is pushed onto the stack.<br>The eleven-bit immediate address is<br>loaded into PC bits <10:0>. The upper<br>bits of the PC are loaded from<br>PCLATH. CALL is a two-cycle instruc-<br>tion. |

| CLRWDT           | Clear Watchdog Timer                                                                                                              |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] CLRWDT                                                                                                                    |

| Operands:        | None                                                                                                                              |

| Operation:       | $00h \rightarrow WDT$ $0 \rightarrow WDT \text{ prescaler,}$ $1 \rightarrow \overline{TO}$ $1 \rightarrow PD$ $\overline{TO}  DD$ |

| Status Affected: | TO, PD                                                                                                                            |

| Description:     | CLRWDT instruction resets the Watch-<br>dog Timer. It also resets the prescaler<br>of the WDT.<br>Status bits TO and PD are set.  |

| CALLW            | Subroutine Call With W                                                                                                                                                                                                  | COM             |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

| Syntax:          | [ label ] CALLW                                                                                                                                                                                                         | Synta           |

| Operands:        | None                                                                                                                                                                                                                    | Opera           |

| Operation:       | (PC) +1 $\rightarrow$ TOS,<br>(W) $\rightarrow$ PC<7:0>,<br>(PCLATH<6:0>) $\rightarrow$ PC<14:8>                                                                                                                        | Opera<br>Status |

| Status Affected: | None                                                                                                                                                                                                                    | Desci           |