Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 16                                                                         |

| Program Memory Size        | 3.5KB (2K x 14)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 256 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                |

| Data Converters            | A/D 12x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 28-UFQFN Exposed Pad                                                       |

| Supplier Device Package    | 28-UQFN (4x4)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1826-i-mv |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 18/20/28-Pin Flash Microcontrollers with nanoWatt XLP Technology

## High-Performance RISC CPU:

- C Compiler Optimized Architecture

- 256 bytes Data EEPROM

- Up to 8 Kbytes Linear Program Memory Addressing

- Up to 384 bytes Linear Data Memory Addressing

- Interrupt Capability with Automatic Context Saving

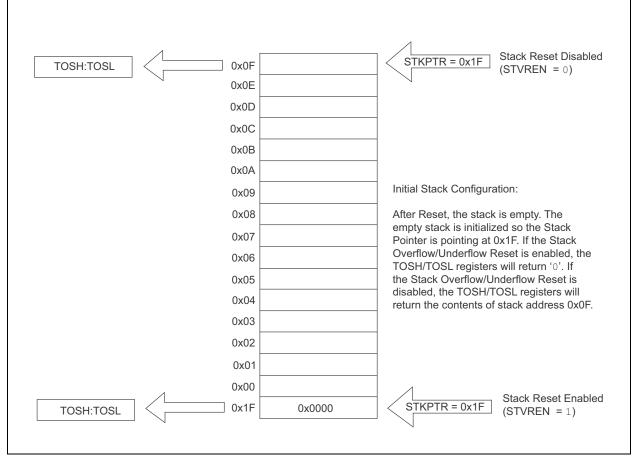

- 16-Level Deep Hardware Stack with Optional Overflow/Underflow Reset

- Direct, Indirect and Relative Addressing modes:

- Two full 16-bit File Select Registers (FSRs)

- FSRs can read program and data memory

### Flexible Oscillator Structure:

- Precision 32 MHz Internal Oscillator Block:

- Factory calibrated to ± 1%, typical

- Software selectable frequencies range of 31 kHz to 32 MHz

- 31 kHz Low-Power Internal Oscillator

- · Four Crystal modes up to 32 MHz

- Three External Clock modes up to 32 MHz

- 4X Phase-Lock Loop (PLL)

- Fail-Safe Clock Monitor:

- Allows for safe shutdown if peripheral clock stops

- Two-Speed Oscillator Start-up

- Reference Clock Module:

- Programmable clock output frequency and duty-cycle

### **Special Microcontroller Features:**

- 1.8V-5.5V Operation PIC16F1826/27

- 1.8V-3.6V Operation PIC16LF1826/27

- Self-Programmable under Software Control

- Power-on Reset (POR), Power-up Timer (PWRT) and Oscillator Start-up Timer (OST)

- Programmable Brown-out Reset (BOR)

- Extended Watchdog Timer (WDT):

- Programmable period from 1ms to 268s

- Programmable Code Protection

- In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) via two pins

- In-Circuit Debug (ICD) via two pins

- Enhance Low-Voltage Programming

- · Power-Saving Sleep mode

## Extreme Low-Power Management PIC16LF1826/27 with nanoWatt XLP:

- Operating Current: 75 μA @ 1 MHz, 1.8V, typical

- Sleep mode: 30 nA

- Watchdog Timer: 500 nA

- Timer1 Oscillator: 600 nA @ 32 kHz

## **Analog Features:**

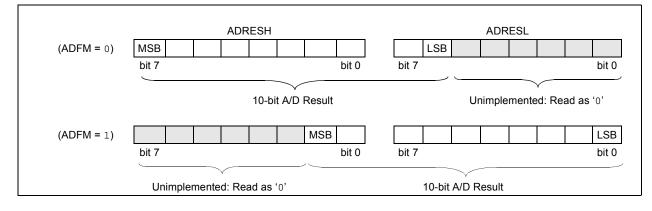

- Analog-to-Digital Converter (ADC) Module:

- 10-bit resolution, 12 channels

- Auto acquisition capability

- Conversion available during Sleep

- Analog Comparator Module:

- Two rail-to-rail analog comparators

- Power mode control

- Software controllable hysteresis

- Voltage Reference Module:

- Fixed Voltage Reference (FVR) with 1.024V, 2.048V and 4.096V output levels

- 5-bit rail-to-rail resistive DAC with positive and negative reference selection

## **Peripheral Highlights:**

- 15 I/O Pins and 1 Input Only Pin:

- High current sink/source 25 mA/25 mA

- Programmable weak pull-ups

- Programmable interrupt-on- change pins

- Timer0: 8-Bit Timer/Counter with 8-Bit Prescaler

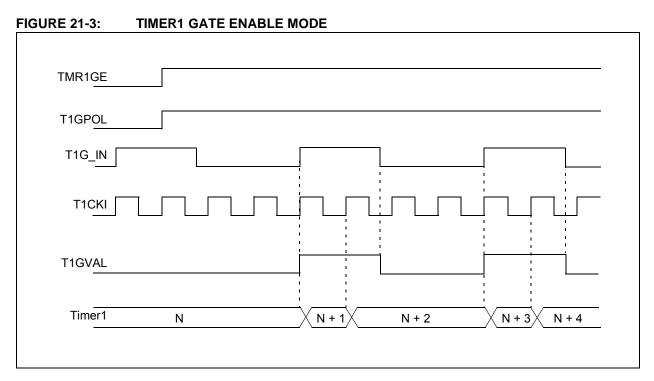

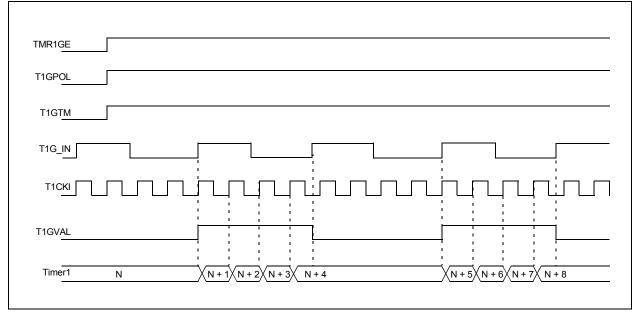

- Enhanced Timer1:

- 16-bit timer/counter with prescaler

- External Gate Input mode

- Dedicated, low-power 32 kHz oscillator driver

- Up to three Timer2-types: 8-Bit Timer/Counter with 8-Bit Period Register, Prescaler and Postscaler

- Up to two Capture, Compare, PWM (CCP) Modules

- Up to two Enhanced CCP (ECCP) Modules:

- Software selectable time bases

- Auto-shutdown and auto-restart

- PWM steering

- Up to two Master Synchronous Serial Port (MSSP) with SPI and I<sup>2</sup>C<sup>™</sup> with:

- 7-bit address masking

- SMBus/PMBus™ compatibility

- Enhanced Universal Synchronous Asynchronous Receiver Transmitter (EUSART) Module

- mTouch™ Sensing Oscillator Module:

- Up to 12 input channelsData Signal Modulator Module:

- Selectable modulator and carrier sources

- SR Latch:

- Multiple Set/Reset input options

- Emulates 555 Timer applications

#### **TABLE 1-2:** PIC16(L)F1826/27 PINOUT DESCRIPTION (CONTINUED)

| Name                                                                                                      | Function | Input<br>Type     | Output<br>Type | Description                                                                                        |

|-----------------------------------------------------------------------------------------------------------|----------|-------------------|----------------|----------------------------------------------------------------------------------------------------|

| RA6/OSC2/CLKOUT/CLKR/                                                                                     | RA6      | TTL               | CMOS           | General purpose I/O.                                                                               |

| P1D <sup>(1)</sup> /P2B <sup>(1,2)</sup> /SDO1 <sup>(1)</sup>                                             | OSC2     | —                 | XTAL           | Crystal/Resonator (LP, XT, HS modes).                                                              |

|                                                                                                           | CLKOUT   | _                 | CMOS           | Fosc/4 output.                                                                                     |

|                                                                                                           | CLKR     | —                 | CMOS           | Clock Reference Output.                                                                            |

|                                                                                                           | P1D      | —                 | CMOS           | PWM output.                                                                                        |

|                                                                                                           | P2B      | —                 | CMOS           | PWM output.                                                                                        |

|                                                                                                           | SDO1     | —                 | CMOS           | SPI data output 1.                                                                                 |

| RA7/OSC1/CLKIN/P1C <sup>(1)</sup> /                                                                       | RA7      | TTL               | CMOS           | General purpose I/O.                                                                               |

| CCP2 <sup>(1,2)</sup> /P2A <sup>(1,2)</sup>                                                               | OSC1     | XTAL              | _              | Crystal/Resonator (LP, XT, HS modes).                                                              |

|                                                                                                           | CLKIN    | CMOS              | —              | External clock input (EC mode).                                                                    |

|                                                                                                           | P1C      | —                 | CMOS           | PWM output.                                                                                        |

|                                                                                                           | CCP2     | ST                | CMOS           | Capture/Compare/PWM2.                                                                              |

|                                                                                                           | P2A      | —                 | CMOS           | PWM output.                                                                                        |

| RB0/T1G/CCP1 <sup>(1)</sup> /P1A <sup>(1)</sup> /INT/<br>SRI/FLT0                                         | RB0      | TTL               | CMOS           | General purpose I/O. Individually controlled interrupt-on-change.<br>Individually enabled pull-up. |

|                                                                                                           | T1G      | ST                | _              | Timer1 Gate input.                                                                                 |

|                                                                                                           | CCP1     | ST                | CMOS           | Capture/Compare/PWM1.                                                                              |

|                                                                                                           | P1A      | _                 | CMOS           | PWM output.                                                                                        |

|                                                                                                           | INT      | ST                | —              | External interrupt.                                                                                |

|                                                                                                           | SRI      | ST                |                | SR latch input.                                                                                    |

|                                                                                                           | FLT0     | ST                |                | ECCP Auto-Shutdown Fault input.                                                                    |

| RB1/AN11/CPS11/RX <sup>(1,3)</sup> /<br>DT <sup>(1,3)</sup> /SDA1/SDI1                                    | RB1      | TTL               | CMOS           | General purpose I/O. Individually controlled interrupt-on-change.<br>Individually enabled pull-up. |

|                                                                                                           | AN11     | AN                |                | A/D Channel 11 input.                                                                              |

|                                                                                                           | CPS11    | AN                |                | Capacitive sensing input 11.                                                                       |

|                                                                                                           | RX       | ST                |                | USART asynchronous input.                                                                          |

|                                                                                                           | DT       | ST                | CMOS           | USART synchronous data.                                                                            |

|                                                                                                           | SDA1     | I <sup>2</sup> C™ | OD             | I <sup>2</sup> C™ data input/output 1.                                                             |

|                                                                                                           | SDI1     | CMOS              |                | SPI data input 1.                                                                                  |

| RB2/AN10/CPS10/MDMIN/<br>TX <sup>(1,3)</sup> /CK <sup>(1,3)</sup> /RX <sup>(1)</sup> /DT <sup>(1)</sup> / | RB2      | TTL               | CMOS           | General purpose I/O. Individually controlled interrupt-on-change.<br>Individually enabled pull-up. |

| SDA2 <sup>(2)</sup> /SDI2 <sup>(2)</sup> /SDO1 <sup>(1,3)</sup>                                           | AN10     | AN                |                | A/D Channel 10 input.                                                                              |

|                                                                                                           | CPS10    | AN                |                | Capacitive sensing input 10.                                                                       |

|                                                                                                           | MDMIN    | _                 | CMOS           | Modulator source input.                                                                            |

|                                                                                                           | TX       | _                 | CMOS           | USART asynchronous transmit.                                                                       |

|                                                                                                           | СК       | ST                | CMOS           | USART synchronous clock.                                                                           |

|                                                                                                           | RX       | ST                | —              | USART asynchronous input.                                                                          |

|                                                                                                           | DT       | ST                | CMOS           | USART synchronous data.                                                                            |

|                                                                                                           | SDA2     | I <sup>2</sup> C™ | OD             | I <sup>2</sup> C™ data input/output 2.                                                             |

|                                                                                                           |          |                   |                |                                                                                                    |

|                                                                                                           | SDI2     | ST                | _              | SPI data input 2.                                                                                  |

Legend: AN = Analog input or output CMOS = CMOS compatible input or output

OD = Open Drain

TTL = TTL compatible input ST = Schmitt Trigger input with CMOS levels  $I^2C^{TM}$  = Schmitt Trigger input with  $I^2C$ HV = High Voltage XTAL = Crystal

levels

Note 1: Pin functions can be moved using the APFCON0 or APFCON1 register.

2: Functions are only available on the PIC16(L)F1827.

3: Default function location.

### 3.4 Stack

All devices have a 16-level x 15-bit wide hardware stack (refer to Figures 3-5 through 3-8). The stack space is not part of either program or data space. The PC is PUSHed onto the stack when CALL or CALLW instructions are executed or an interrupt causes a branch. The stack is POPed in the event of a RETURN, RETLW or a RETFIE instruction execution. PCLATH is not affected by a PUSH or POP operation.

The stack operates as a circular buffer if the STVREN bit is programmed to '0' (Configuration Word 2). This means that after the stack has been PUSHed sixteen times, the seventeenth PUSH overwrites the value that was stored from the first PUSH. The eighteenth PUSH overwrites the second PUSH (and so on). The STKOVF and STKUNF flag bits will be set on an Overflow/Underflow, regardless of whether the Reset is enabled.

Note 1: There are no instructions/mnemonics called PUSH or POP. These are actions that occur from the execution of the CALL, CALLW, RETURN, RETLW and RETFIE instructions or the vectoring to an interrupt address.

### 3.4.1 ACCESSING THE STACK

The stack is available through the TOSH, TOSL and STKPTR registers. STKPTR is the current value of the Stack Pointer. TOSH:TOSL register pair points to the TOP of the stack. Both registers are read/writable. TOS is split into TOSH and TOSL due to the 15-bit size of the PC. To access the stack, adjust the value of STKPTR, which will position TOSH:TOSL, then read/write to TOSH:TOSL. STKPTR is 5 bits to allow detection of overflow and underflow.

| Note: | Care should be taken when modifying the |

|-------|-----------------------------------------|

|       | STKPTR while interrupts are enabled.    |

During normal program operation, CALL, CALLW and Interrupts will increment STKPTR while RETLW, RETURN, and RETFIE will decrement STKPTR. At any time STKPTR can be inspected to see how much stack is left. The STKPTR always points at the currently used place on the stack. Therefore, a CALL or CALLW will increment the STKPTR and then write the PC, and a return will unload the PC and then decrement STKPTR.

Reference Figure 3-5 through Figure 3-8 for examples of accessing the stack.

# PIC16(L)F1826/27

| EXAM                 | EXAMPLE 11-4: ERASING ONE ROW OF PROGRAM MEMORY -     |                                                                                |                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |

|----------------------|-------------------------------------------------------|--------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

|                      |                                                       | routine assumes                                                                | -                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |

| ; 1. A               | valid addr                                            | ess within the                                                                 | erase block is loaded in ADDRH:ADDRL                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |

| ; 2. AI              | DDRH and AD                                           | DRL are located                                                                | in shared data memory 0x70 - 0x7F (common RAM)                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |

|                      | BCF<br>BANKSEL<br>MOVF<br>MOVWF<br>MOVF<br>BSF        | INTCON,GIE<br>EEADRL<br>ADDRL,W<br>EEADRL<br>ADDRH,W<br>EEADRH<br>EECON1,EEPGD | <ul> <li>; Disable ints so required sequences will execute properly</li> <li>; Load lower 8 bits of erase address boundary</li> <li>; Load upper 6 bits of erase address boundary</li> <li>; Point to program memory</li> </ul>                                                                                                                 |  |  |  |  |  |  |

|                      | BCF                                                   | EECON1, EEFGD                                                                  | ; Not configuration space                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |

|                      | BSF                                                   | EECON1, FREE                                                                   | ; Specify an erase operation                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

|                      | BSF                                                   | EECON1, WREN                                                                   | ; Enable writes                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |

| Required<br>Sequence | MOVLW<br>MOVWF<br>MOVLW<br>MOVWF<br>BSF<br>NOP<br>NOP | 55h<br>EECON2<br>0AAh<br>EECON2<br>EECON1,WR                                   | <pre>; Start of required sequence to initiate erase<br/>; Write 55h<br/>;<br/>; Write AAh<br/>; Set WR bit to begin erase<br/>; Any instructions here are ignored as processor<br/>; halts to begin erase sequence<br/>; Processor will stop here and wait for erase complete.<br/>; after erase processor continues with 3rd instruction</pre> |  |  |  |  |  |  |

|                      | BCF<br>BSF                                            | EECON1,WREN<br>INTCON,GIE                                                      | ; Disable writes<br>; Enable interrupts                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |

| R/W-1/1                        | R/W-1/1 | R/W-1/1      | R/W-1/1 | R/W-1/1      | R/W-1/1          | R/W-1/1 | R/W-1/1 |  |

|--------------------------------|---------|--------------|---------|--------------|------------------|---------|---------|--|

| WPUB7                          | WPUB6   | WPUB5        | WPUB4   | WPUB3        | WPUB2            | WPUB1   | WPUB0   |  |

| bit 7 bit 0                    |         |              |         |              |                  |         |         |  |

|                                |         |              |         |              |                  |         |         |  |

|                                |         |              |         |              |                  |         |         |  |

| Legend:                        |         |              |         |              |                  |         |         |  |

| <b>Legend:</b><br>R = Readable | bit     | W = Writable | bit     | U = Unimplen | nented bit, read | as '0'  |         |  |

#### REGISTER 12-11: WPUB: WEAK PULL-UP PORTB REGISTER

bit 7-0 WPUB<7:0>: Weak Pull-up Register bits

1 = Pull-up enabled

'1' = Bit is set

0 = Pull-up disabled

Note 1: Global WPUEN bit of the OPTION register must be cleared for individual pull-ups to be enabled.

2: The weak pull-up device is automatically disabled if the pin is in configured as an output.

#### REGISTER 12-12: ANSELB: PORTB ANALOG SELECT REGISTER

'0' = Bit is cleared

| R/W-1/1 | U-0   |

|---------|---------|---------|---------|---------|---------|---------|-------|

| ANSB7   | ANSB6   | ANSB5   | ANSB4   | ANSB3   | ANSB2   | ANSB1   | —     |

| bit 7   |         |         |         |         |         |         | bit 0 |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-1 **ANSB<7:1>**: Analog Select between Analog or Digital Function on Pins RB<7:1>, respectively 0 = Digital I/O. Pin is assigned to port or digital special function.

1 = Analog input. Pin is assigned as analog input<sup>(1)</sup>. Digital input buffer disabled.

#### bit 0 Unimplemented: Read as '0'

**Note 1:** When setting a pin to an analog input, the corresponding TRIS bit must be set to Input mode in order to allow external control of the voltage on the pin.

#### 16.1.5 INTERRUPTS

The ADC module allows for the ability to generate an interrupt upon completion of an Analog-to-Digital conversion. The ADC Interrupt Flag is the ADIF bit in the PIR1 register. The ADC Interrupt Enable is the ADIE bit in the PIE1 register. The ADIF bit must be cleared in software.

| he ADIF bit is set at the completion of                                       |

|-------------------------------------------------------------------------------|

| very conversion, regardless of whether<br>r not the ADC interrupt is enabled. |

|                                                                               |

**2:** The ADC operates during Sleep only when the FRC oscillator is selected.

This interrupt can be generated while the device is operating or while in Sleep. If the device is in Sleep, the interrupt will wake-up the device. Upon waking from Sleep, the next instruction following the SLEEP instruction is always executed. If the user is attempting to wake-up from Sleep and resume in-line code execution, the GIE and PEIE bits of the INTCON register must be disabled. If the GIE and PEIE bits of the INTCON register are enabled, execution will switch to the Interrupt Service Routine.

#### 16.1.6 RESULT FORMATTING

The 10-bit A/D conversion result can be supplied in two formats, left justified or right justified. The ADFM bit of the ADCON1 register controls the output format.

Figure 16-3 shows the two output formats.

### FIGURE 16-3: 10-BIT A/D CONVERSION RESULT FORMAT

## PIC16(L)F1826/27

## FIGURE 21-4: TIMER1 GATE TOGGLE MODE

| R/W-0/       | /0 R/W-0/0           | R/W-1/1                                                                                         | R/W-0/0         | R-0/0          | U-0                | U-0                | R/W-0/0      |  |  |  |  |

|--------------|----------------------|-------------------------------------------------------------------------------------------------|-----------------|----------------|--------------------|--------------------|--------------|--|--|--|--|

| MDEN         | N MDOE               | MDSLR                                                                                           | MDOPOL          | MDOUT          | —                  |                    | MDBIT        |  |  |  |  |

| bit 7        |                      |                                                                                                 |                 |                |                    |                    | bit 0        |  |  |  |  |

| <u> </u>     |                      |                                                                                                 |                 |                |                    |                    |              |  |  |  |  |

| Legend:      |                      |                                                                                                 |                 |                |                    |                    |              |  |  |  |  |

| R = Read     |                      | W = Writable                                                                                    |                 | •              | mented bit, read   |                    |              |  |  |  |  |

|              | unchanged            | x = Bit is unk                                                                                  |                 | -n/n = Value   | at POR and BOF     | R/Value at all     | other Resets |  |  |  |  |

| '1' = Bit is | set                  | '0' = Bit is cle                                                                                | ared            |                |                    |                    |              |  |  |  |  |

|              |                      |                                                                                                 |                 |                |                    |                    |              |  |  |  |  |

| bit 7        |                      | ulator Module E                                                                                 |                 |                |                    |                    |              |  |  |  |  |

|              |                      | or module is er                                                                                 |                 | 0 1 0          | als                |                    |              |  |  |  |  |

|              |                      | or module is di                                                                                 |                 |                |                    |                    |              |  |  |  |  |

| bit 6        |                      | odulator Module Pin Output Enable bit                                                           |                 |                |                    |                    |              |  |  |  |  |

|              |                      | <ul> <li>1 = Modulator pin output enabled</li> <li>0 = Modulator pin output disabled</li> </ul> |                 |                |                    |                    |              |  |  |  |  |

| bit 5        |                      | OUT Pin Slew                                                                                    |                 | ait            |                    |                    |              |  |  |  |  |

| DIL 5        |                      | pin slew rate li                                                                                | 0               |                |                    |                    |              |  |  |  |  |

|              |                      | pin slew rate li                                                                                |                 |                |                    |                    |              |  |  |  |  |

| bit 4        |                      | Iodulator Outpu                                                                                 | •               |                |                    |                    |              |  |  |  |  |

|              |                      | or output signa                                                                                 |                 |                |                    |                    |              |  |  |  |  |

|              |                      | or output signa                                                                                 |                 | b              |                    |                    |              |  |  |  |  |

| bit 3        | MDOUT: Mo            | dulator Output                                                                                  | bit             |                |                    |                    |              |  |  |  |  |

|              | Displays the         | current output                                                                                  | value of the me | odulator modu  | le. <sup>(1)</sup> |                    |              |  |  |  |  |

| bit 2-1      | Unimpleme            | nted: Read as                                                                                   | 0'              |                |                    |                    |              |  |  |  |  |

| bit 0        | MDBIT: Allo          | ws software to r                                                                                | nanually set m  | odulation sou  | rce input to mod   | ule <sup>(2)</sup> |              |  |  |  |  |

|              |                      | or uses High C                                                                                  |                 |                | ·                  |                    |              |  |  |  |  |

|              | 0 = Modulat          | or uses Low Ca                                                                                  | arrier source   |                |                    |                    |              |  |  |  |  |

| Note 1:      | The modulated o      | utput frequency                                                                                 | can be greate   | r and asynchro | onous from the c   | lock that upd      | ates this    |  |  |  |  |

|              | register bit, the bi |                                                                                                 |                 |                |                    |                    |              |  |  |  |  |

### **REGISTER 23-1: MDCON: MODULATION CONTROL REGISTER**

2: MDBIT must be selected as the modulation source in the MDSRC register for this operation.

## 24.0 CAPTURE/COMPARE/PWM MODULES

The Capture/Compare/PWM module is a peripheral which allows the user to time and control different events, and to generate Pulse-Width Modulation (PWM) signals. In Capture mode, the peripheral allows the timing of the duration of an event. The Compare mode allows the user to trigger an external event when a predetermined amount of time has expired. The PWM mode can generate Pulse-Width Modulated signals of varying frequency and duty cycle.

This family of devices contains two Enhanced Capture/Compare/PWM modules (ECCP1 and ECCP2) and two standard Capture/Compare/PWM modules (CCP3 and CCP4).

The Capture and Compare functions are identical for all four CCP modules (ECCP1, ECCP2, CCP3 and CCP4). The only differences between CCP modules are in the Pulse-Width Modulation (PWM) function. The standard PWM function is identical in modules, CCP3 and CCP4. In CCP modules ECCP1 and ECCP2, the Enhanced PWM function has slight variations from one another. Full-Bridge ECCP modules have four available I/O pins while Half-Bridge ECCP modules only have two available I/O pins. See Table 24-1 for more information.

- Note 1: In devices with more than one CCP module, it is very important to pay close attention to the register names used. A number placed after the module acronym is used to distinguish between separate modules. For example, the CCP1CON and CCP2CON control the same operational aspects of two completely different CCP modules.

- 2: Throughout this section, generic references to a CCP module in any of its operating modes may be interpreted as being equally applicable to ECCP1, ECCP2, CCP3 and CCP4. Register names, module signals, I/O pins, and bit names may use the generic designator 'x' to indicate the use of a numeral to distinguish a particular module, when required.

### TABLE 24-1:PWM RESOURCES

| Device Name   | ECCP1                       | ECCP1 ECCP2                 |               | CCP4          |  |

|---------------|-----------------------------|-----------------------------|---------------|---------------|--|

| PIC16(L)F1826 | Enhanced PWM<br>Full-Bridge | Not Available               | Not Available | Not Available |  |

| PIC16(L)F1827 | Enhanced PWM<br>Full-Bridge | Enhanced PWM<br>Half-Bridge | Standard PWM  | Standard PWM  |  |

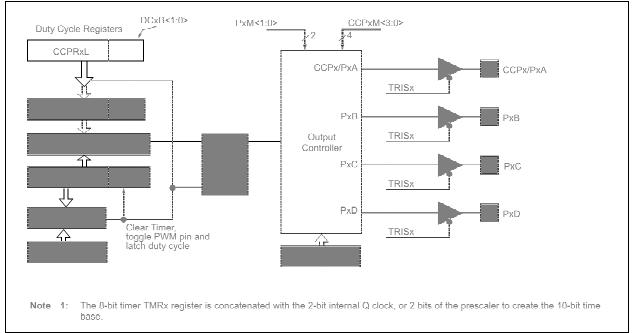

## 24.4 PWM (Enhanced Mode)

The enhanced PWM function described in this section is available for CCP modules ECCP1 and ECCP2, with any differences between modules noted.

The enhanced PWM mode generates a Pulse-Width Modulation (PWM) signal on up to four different output pins with up to 10 bits of resolution. The period, duty cycle, and resolution are controlled by the following registers:

- PRx registers

- TxCON registers

- · CCPRxL registers

- CCPxCON registers

The ECCP modules have the following additional PWM registers which control Auto-shutdown, Auto-restart, Dead-band Delay and PWM Steering modes:

- · CCPxAS registers

- PSTRxCON registers

- PWMxCON registers

The enhanced PWM module can generate the following five PWM Output modes:

- Single PWM

- Half-Bridge PWM

- Full-Bridge PWM, Forward Mode

- Full-Bridge PWM, Reverse Mode

- · Single PWM with PWM Steering Mode

To select an Enhanced PWM Output mode, the PxM bits of the CCPxCON register must be configured appropriately.

The PWM outputs are multiplexed with I/O pins and are designated PxA, PxB, PxC and PxD. The polarity of the PWM pins is configurable and is selected by setting the CCPxM bits in the CCPxCON register appropriately.

Figure 24-5 shows an example of a simplified block diagram of the Enhanced PWM module.

Figure 24-9 shows the pin assignments for various Enhanced PWM modes.

- Note 1: The corresponding TRIS bit must be cleared to enable the PWM output on the CCPx pin.

- 2: Clearing the CCPxCON register will relinquish control of the CCPx pin.

- **3:** Any pin not used in the enhanced PWM mode is available for alternate pin functions, if applicable.

- 4: To prevent the generation of an incomplete waveform when the PWM is first enabled, the ECCP module waits until the start of a new PWM period before generating a PWM signal.

### FIGURE 24-5: EXAMPLE SIMPLIFIED BLOCK DIAGRAM OF THE ENHANCED PWM MODE

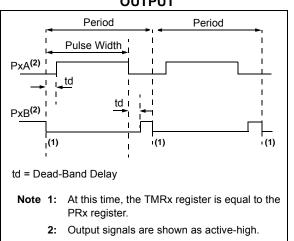

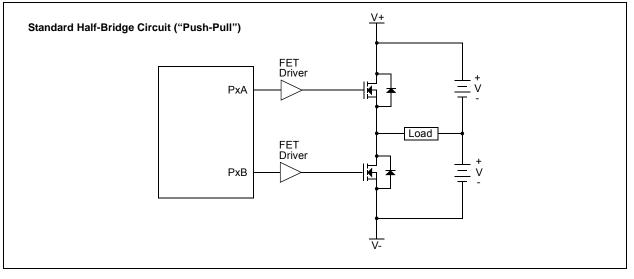

#### 24.4.5 PROGRAMMABLE DEAD-BAND DELAY MODE

In Half-Bridge applications where all power switches are modulated at the PWM frequency, the power switches normally require more time to turn off than to turn on. If both the upper and lower power switches are switched at the same time (one turned on, and the other turned off), both switches may be on for a short period of time until one switch completely turns off. During this brief interval, a very high current (*shoot-through current*) will flow through both power switches, shorting the bridge supply. To avoid this potentially destructive shoot-through current from flowing during switching, turning on either of the power switches is normally delayed to allow the other switch to completely turn off.

In Half-Bridge mode, a digitally programmable dead-band delay is available to avoid shoot-through current from destroying the bridge power switches. The delay occurs at the signal transition from the non-active state to the active state. See Figure 24-16 for illustration. The lower seven bits of the associated PWMxCON register (Register 24-4) sets the delay period in terms of microcontroller instruction cycles (TcY or 4 Tosc).

#### FIGURE 24-16: EXAMPLE OF HALF-BRIDGE PWM OUTPUT

### FIGURE 24-17: EXAMPLE OF HALF-BRIDGE APPLICATIONS

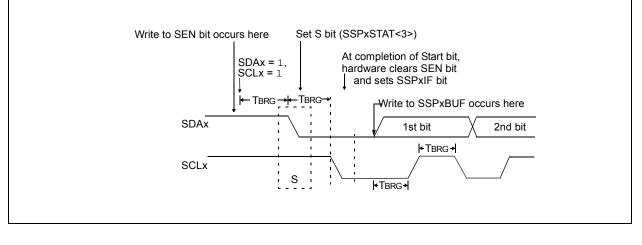

#### 25.6.4 I<sup>2</sup>C MASTER MODE START CONDITION TIMING

To initiate a Start condition, the user sets the Start Enable bit, SEN bit of the SSPxCON2 register. If the SDAx and SCLx pins are sampled high, the Baud Rate Generator is reloaded with the contents of SSPxADD<7:0> and starts its count. If SCLx and SDAx are both sampled high when the Baud Rate Generator times out (TBRG), the SDAx pin is driven low. The action of the SDAx being driven low while SCLx is high is the Start condition and causes the S bit of the SSPxSTAT1 register to be set. Following this, the Baud Rate Generator is reloaded with the contents of SSPxADD<7:0> and resumes its count. When the Baud Rate Generator times out (TBRG), the SEN bit of the SSPxCON2 register will be automatically cleared

#### FIGURE 25-26: FIRST START BIT TIMING

by hardware; the Baud Rate Generator is suspended, leaving the SDAx line held low and the Start condition is complete.

- Note 1: If at the beginning of the Start condition, the SDAx and SCLx pins are already sampled low, or if during the Start condition, the SCLx line is sampled low before the SDAx line is driven low, a bus collision occurs, the Bus Collision Interrupt Flag, BCLxIF, is set, the Start condition is aborted and the I<sup>2</sup>C module is reset into its Idle state.

- **2:** The Philips I<sup>2</sup>C Specification states that a bus collision cannot occur on a Start.

| R/W-1/1              | R/W-1/1                                                                | R/W-1/1                                                                                              | R/W-1/1          | R/W-1/1                                               | R/W-1/1                            | R/W-1/1 | R/W-1/1 |  |  |  |

|----------------------|------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|------------------|-------------------------------------------------------|------------------------------------|---------|---------|--|--|--|

|                      |                                                                        |                                                                                                      | MSł              | <<7:0>                                                |                                    |         |         |  |  |  |

| bit 7                |                                                                        |                                                                                                      |                  |                                                       |                                    |         | bit C   |  |  |  |

|                      |                                                                        |                                                                                                      |                  |                                                       |                                    |         |         |  |  |  |

| Legend:              |                                                                        |                                                                                                      |                  |                                                       |                                    |         |         |  |  |  |

| R = Readable bit W = |                                                                        | W = Writable                                                                                         | W = Writable bit |                                                       | U = Unimplemented bit, read as '0' |         |         |  |  |  |

| u = Bit is unchanged |                                                                        | x = Bit is unknown                                                                                   |                  | -n/n = Value at POR and BOR/Value at all other Resets |                                    |         |         |  |  |  |

| '1' = Bit is se      | et                                                                     | '0' = Bit is cle                                                                                     | ared             |                                                       |                                    |         |         |  |  |  |

|                      |                                                                        |                                                                                                      |                  |                                                       |                                    |         |         |  |  |  |

| bit 7-1              | MSK<7:1>:                                                              |                                                                                                      |                  |                                                       |                                    |         |         |  |  |  |

|                      | 1 = The rec                                                            | 1 = The received address bit n is compared to SSPxADD <n> to detect I<sup>2</sup>C address match</n> |                  |                                                       |                                    |         |         |  |  |  |

|                      | 0 = The rec                                                            | eived address b                                                                                      | it n is not use  | ed to detect I <sup>2</sup> C                         | address match                      |         |         |  |  |  |

| bit 0                | <b>MSK&lt;0&gt;:</b> M                                                 | ask bit for I <sup>2</sup> C S                                                                       | lave mode, 1     | 0-bit Address                                         |                                    |         |         |  |  |  |

|                      | $1^{2}$ Olever model 40 bit address (OOD: M (200) $\sim$ 0111 an 1111) |                                                                                                      |                  |                                                       |                                    |         |         |  |  |  |

## REGISTER 25-5: SSPxMSK: SSPx MASK REGISTER

- $I^2C$  Slave mode, 10-bit address (SSPxM<3:0> = 0111 or 1111): 1 = The received address bit 0 is compared to SSPxADD<0> to detect  $I^2C$  address match

- 0 = The received address bit 0 is not used to detect I<sup>2</sup>C address match

- I<sup>2</sup>C Slave mode, 7-bit address, the bit is ignored

## REGISTER 25-6: SSPxADD: MSSPx ADDRESS AND BAUD RATE REGISTER (I<sup>2</sup>C MODE)

| R/W-0/0  | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |  |  |  |

|----------|---------|---------|---------|---------|---------|---------|---------|--|--|--|

| ADD<7:0> |         |         |         |         |         |         |         |  |  |  |

| bit 7    |         |         |         |         |         |         |         |  |  |  |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

### Master mode:

| bit 7-0 | ADD<7:0>: Baud Rate Clock Divider bits           |

|---------|--------------------------------------------------|

|         | SCLx pin clock period = ((ADD<7:0> + 1) *4)/Fosc |

### <u>10-Bit Slave mode — Most Significant Address byte:</u>

- bit 7-3 **Not used:** Unused for Most Significant Address byte. Bit state of this register is a "don't care". Bit pattern sent by master is fixed by I<sup>2</sup>C specification and must be equal to '11110'. However, those bits are compared by hardware and are not affected by the value in this register.

- bit 2-1 ADD<2:1>: Two Most Significant bits of 10-bit address

- bit 0 Not used: Unused in this mode. Bit state is a "don't care".

## <u>10-Bit Slave mode — Least Significant Address byte:</u>

bit 7-0 ADD<7:0>: Eight Least Significant bits of 10-bit address

## 7-Bit Slave mode:

| bit 7-1 | ADD<7:1>: 7-bit address |

|---------|-------------------------|

|         |                         |

bit 0 Not used: Unused in this mode. Bit state is a "don't care".

### 28.2 Low-Voltage Programming Entry Mode

The Low-Voltage Programming Entry mode allows the PIC16(L)F1826/27 devices to be programmed using VDD only, without high voltage. When the LVP bit of Configuration Word 2 is set to '1', the low-voltage ICSP programming entry is enabled. To disable the Low-Voltage ICSP mode, the LVP bit must be programmed to '0'.

Entry into the Low-Voltage Programming Entry mode requires the following steps:

- 1.  $\overline{\text{MCLR}}$  is brought to VIL.

- 2. A 32-bit key sequence is presented on ICSPDAT, while clocking ICSPCLK.

Once the key sequence is complete,  $\overline{\text{MCLR}}$  must be held at VIL for as long as Program/Verify mode is to be maintained.

If low-voltage programming is enabled (LVP = 1), the  $\overline{\text{MCLR}}$  Reset function is automatically enabled and cannot be disabled. See **Section 7.3 "MCLR"** for more information.

The LVP bit can only be reprogrammed to '0' by using the High-Voltage Programming mode.

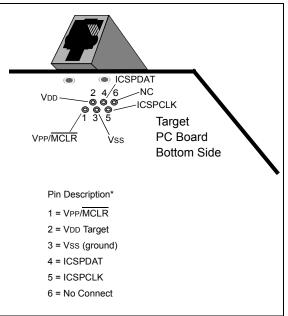

## 28.3 Common Programming Interfaces

Connection to a target device is typically done through an ICSP<sup>™</sup> header. A commonly found connector on development tools is the RJ-11 in the 6P6C (6 pin, 6 connector) configuration. See Figure 28-2.

#### FIGURE 28-2: ICD RJ-11 STYLE CONNECTOR INTERFACE

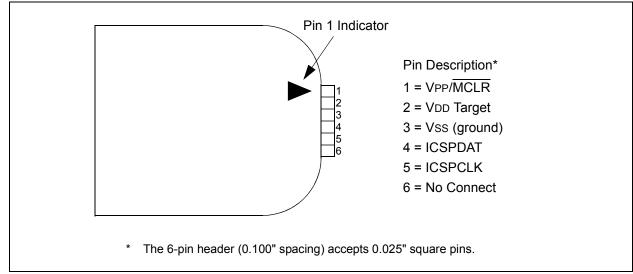

Another connector often found in use with the PICkit<sup>™</sup> programmers is a standard 6-pin header with 0.1 inch spacing. Refer to Figure 28-3.

### FIGURE 28-3: PICkit<sup>™</sup> STYLE CONNECTOR INTERFACE

# PIC16(L)F1826/27

| BCF              | Bit Clear f                                                         |

|------------------|---------------------------------------------------------------------|

| Syntax:          | [label]BCF f,b                                                      |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$ |

| Operation:       | $0 \rightarrow (f \le b >)$                                         |

| Status Affected: | None                                                                |

| Description:     | Bit 'b' in register 'f' is cleared.                                 |

| BTFSC            | Bit Test f, Skip if Clear                                                                                                                                                                                                     |  |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [label]BTFSC f,b                                                                                                                                                                                                              |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$                                                                                                                                                           |  |  |  |  |

| Operation:       | skip if (f <b>) = 0</b>                                                                                                                                                                                                       |  |  |  |  |

| Status Affected: | None                                                                                                                                                                                                                          |  |  |  |  |

| Description:     | If bit 'b' in register 'f' is '1', the next<br>instruction is executed.<br>If bit 'b', in register 'f', is '0', the next<br>instruction is discarded, and a NOP is<br>executed instead, making this a<br>2-cycle instruction. |  |  |  |  |

| BRA              | Relative Branch                                                                                                                                                                                                                    |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] BRA label<br>[ <i>label</i> ] BRA \$+k                                                                                                                                                                            |

| Operands:        | -256 $\leq$ label - PC + 1 $\leq$ 255 -256 $\leq$ k $\leq$ 255                                                                                                                                                                     |

| Operation:       | $(PC) + 1 + k \rightarrow PC$                                                                                                                                                                                                      |

| Status Affected: | None                                                                                                                                                                                                                               |

| Description:     | Add the signed 9-bit literal 'k' to the PC. Since the PC will have incremented to fetch the next instruction, the new address will be PC + $1 + k$ . This instruction is a two-cycle instruction. This branch has a limited range. |

| BTFSS            | Bit Test f, Skip if Set                                                                                                                                                                                         |  |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [ label ] BTFSS f,b                                                                                                                                                                                             |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b < 7 \end{array}$                                                                                                                                                |  |  |  |  |

| Operation:       | skip if (f <b>) = 1</b>                                                                                                                                                                                         |  |  |  |  |

| Status Affected: | None                                                                                                                                                                                                            |  |  |  |  |

| Description:     | If bit 'b' in register 'f' is '0', the next<br>instruction is executed.<br>If bit 'b' is '1', then the next<br>instruction is discarded and a NOP is<br>executed instead, making this a<br>2-cycle instruction. |  |  |  |  |

| BRW              | Relative Branch with W                                                                                                                                                                                                 |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:          | [ label ] BRW                                                                                                                                                                                                          |  |  |  |

| Operands:        | None                                                                                                                                                                                                                   |  |  |  |

| Operation:       | $(PC) + (W) \to PC$                                                                                                                                                                                                    |  |  |  |

| Status Affected: | None                                                                                                                                                                                                                   |  |  |  |

| Description:     | Add the contents of W (unsigned) to<br>the PC. Since the PC will have incre-<br>mented to fetch the next instruction,<br>the new address will be $PC + 1 + (W)$ .<br>This instruction is a two-cycle instruc-<br>tion. |  |  |  |

| BSF              | Bit Set f                                                           |  |  |

|------------------|---------------------------------------------------------------------|--|--|

| Syntax:          | [label]BSF f,b                                                      |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$ |  |  |

| Operation:       | $1 \rightarrow (f \le b >)$                                         |  |  |

| Status Affected: | None                                                                |  |  |

| Description:     | Bit 'b' in register 'f' is set.                                     |  |  |

## 30.7 Timing Parameter Symbology

The timing parameter symbols have been created with one of the following formats:

- 1. TppS2ppS

- 2. TppS

| 2. 1000 |                                      |     |                |

|---------|--------------------------------------|-----|----------------|

| т       |                                      |     |                |

| F       | Frequency                            | Т   | Time           |

| Lowerc  | ase letters (pp) and their meanings: |     |                |

| рр      |                                      |     |                |

| СС      | CCP1                                 | osc | OSC1           |

| ck      | CLKOUT                               | rd  | RD             |

| CS      | CS                                   | rw  | RD or WR       |

| di      | SDIx                                 | sc  | SCKx           |

| do      | SDO                                  | SS  | SS             |

| dt      | Data in                              | tO  | ТОСКІ          |

| io      | I/O PORT                             | t1  | T1CKI          |

| mc      | MCLR                                 | wr  | WR             |

| Upperc  | ase letters and their meanings:      |     |                |

| S       |                                      |     |                |

| F       | Fall                                 | Р   | Period         |

| н       | High                                 | R   | Rise           |

| I       | Invalid (High-impedance)             | V   | Valid          |

| L       | Low                                  | Z   | High-impedance |

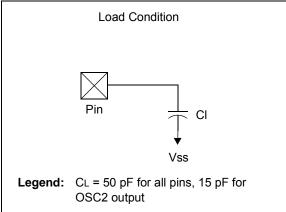

#### FIGURE 30-5: LOAD CONDITIONS

## TABLE 30-5:RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER, POWER-UP TIMER<br/>AND BROWN-OUT RESET PARAMETERS

| Standard Operating Conditions (unless otherwise stated)<br>Operating Temperature -40°C $\leq$ TA $\leq$ +125°C |                                                                  |                                                            |              |            |              |       |                                      |  |

|----------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|------------------------------------------------------------|--------------|------------|--------------|-------|--------------------------------------|--|

| Param<br>No.                                                                                                   | Sym Characteristic                                               |                                                            | Min.         | Тур†       | Max.         | Units | Conditions                           |  |

| 30                                                                                                             | TMCL                                                             | MCLR Pulse Width (low)                                     | 2            | _          | _            | μS    |                                      |  |

| 31                                                                                                             | TWDTLP                                                           | Low-Power Watchdog Timer<br>Time-out Period (No Prescaler) | 10           | 16         | 27           | ms    | VDD = 3.3V-5V<br>1:16 Prescaler used |  |

| 32                                                                                                             | Tost                                                             | Oscillator Start-up Timer Period <sup>(1),</sup> (2)       |              | 1024       |              | Tosc  | (Note 3)                             |  |

| 33*                                                                                                            | TPWRT                                                            | Power-up Timer Period, $\overline{PWRTE} = 0$              | 40           | 65         | 140          | ms    |                                      |  |

| 34*                                                                                                            | TIOZ I/O high-impedance from MCLR Low<br>or Watchdog Timer Reset |                                                            |              | —          | 2.0          | μS    |                                      |  |

| 35                                                                                                             | 35 VBOR Brown-out Reset Voltage                                  |                                                            | 2.38<br>1.80 | 2.5<br>1.9 | 2.73<br>2.11 | V     | BORV=2.5V<br>BORV=1.9V               |  |

| 36*                                                                                                            | VHYST                                                            | Brown-out Reset Hysteresis                                 | 0            | 25         | 50           | mV    | -40°C to +85°C                       |  |

| 37*                                                                                                            | 7* TBORDC Brown-out Reset DC Response<br>Time                    |                                                            |              | 3          | 35           | μS    | $V\text{DD} \leq V\text{BOR}$        |  |

These parameters are characterized but not tested.

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

- **Note 1:** Instruction cycle period (TCY) equals four times the input oscillator time base period. All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at "min" values with an external clock applied to the OSC1 pin. When an external clock input is used, the "max" cycle time limit is "DC" (no clock) for all devices.

- 2: By design.

- **3:** Period of the slower clock.

- 4: To ensure these voltage tolerances, VDD and Vss must be capacitively decoupled as close to the device as possible. 0.1  $\mu$ F and 0.01  $\mu$ F values in parallel are recommended.

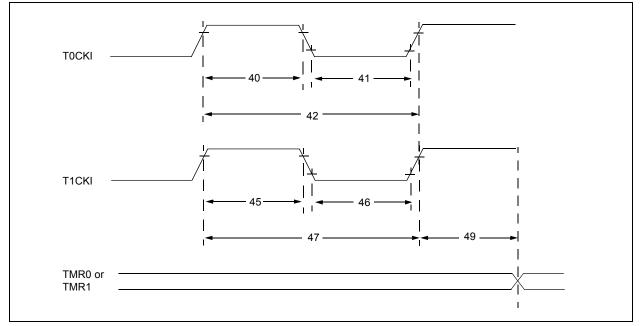

#### FIGURE 30-10: TIMER0 AND TIMER1 EXTERNAL CLOCK TIMINGS

## PIC16(L)F1826/27

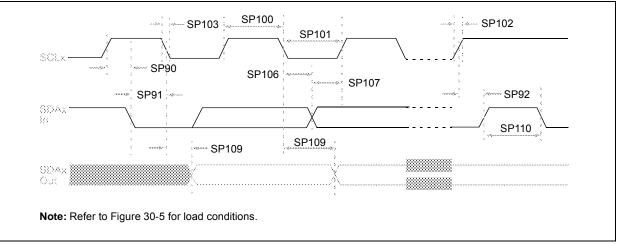

## FIGURE 30-21: I<sup>2</sup>C<sup>™</sup> BUS DATA TIMING

## TABLE 30-15: I<sup>2</sup>C<sup>™</sup> BUS START/STOP BITS REQUIREMENTS

| Param<br>No. | Symbol  | Characteristic  |              | Min. | Тур | Max. | Units | Conditions                   |

|--------------|---------|-----------------|--------------|------|-----|------|-------|------------------------------|

| SP90*        | Tsu:sta | Start condition | 100 kHz mode | 4700 |     | —    | ns    | Only relevant for Repeated   |

|              |         | Setup time      | 400 kHz mode | 600  | _   | —    |       | Start condition              |

| SP91*        | THD:STA | Start condition | 100 kHz mode | 4000 | —   | —    | ns    | After this period, the first |

|              |         | Hold time       | 400 kHz mode | 600  | _   | —    |       | clock pulse is generated     |

| SP92*        | Tsu:sto | Stop condition  | 100 kHz mode | 4700 | _   | —    | ns    |                              |

|              |         | Setup time      | 400 kHz mode | 600  | _   | —    |       |                              |

| SP93         | THD:STO | Stop condition  | 100 kHz mode | 4000 | _   | —    | ns    |                              |

|              |         | Hold time       | 400 kHz mode | 600  | _   |      |       |                              |

\* These parameters are characterized but not tested.

| Param.<br>No. | Symbol | Characteristic |        | Min. | Тур† | Max. | Units | Conditions |

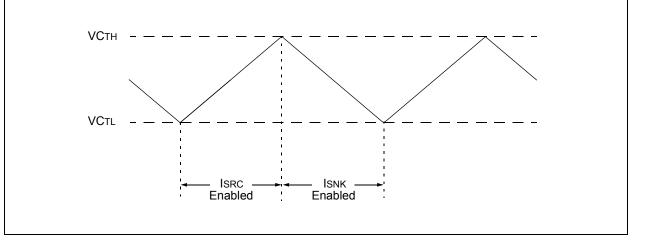

|---------------|--------|----------------|--------|------|------|------|-------|------------|

| CS01          | ISRC   | Current Source | High   | -3   | -8   | -15  | μA    |            |

|               |        |                | Medium | -0.8 | -1.5 | -3   | μA    |            |

|               |        |                | Low    | -0.1 | -0.3 | -0.4 | μA    |            |

| CS02          | Isnk   | Current Sink   | High   | 2.5  | 7.5  | 14   | μA    |            |

|               |        |                | Medium | 0.6  | 1.5  | 2.9  | μA    |            |

|               |        |                | Low    | 0.1  | 0.25 | 0.6  | μA    |            |

| CS03          | VСтн   | Cap Threshold  |        | _    | 0.8  | _    | mV    |            |

| CS04          | VCTL   | Cap Threshold  |        |      | 0.4  | _    | mV    |            |

| CS05          | VCHYST |                | High   | 350  | 525  | 725  | mV    |            |

|               |        | (VCTH - VCTL)  | Medium | 250  | 375  | 500  | mV    |            |

|               |        |                | Low    | 175  | 300  | 425  | mV    |            |

## TABLE 30-17: CAP SENSE OSCILLATOR SPECIFICATIONS

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

### FIGURE 30-22: CAP SENSE OSCILLATOR

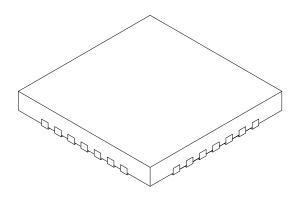

#### 28-Lead Plastic Ultra Thin Quad Flat, No Lead Package (MV) – 4x4x0.5 mm Body [UQFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                        | MILLIMETERS |           |      |      |  |  |

|------------------------|-------------|-----------|------|------|--|--|

| Dimension              | Limits      | MIN       | NOM  | MAX  |  |  |

| Number of Pins         | N           | 28        |      |      |  |  |

| Pitch                  | е           | 0.40 BSC  |      |      |  |  |

| Overall Height         | A           | 0.45      | 0.50 | 0.55 |  |  |

| Standoff               | A1          | 0.00      | 0.02 | 0.05 |  |  |

| Contact Thickness      | A3          | 0.127 REF |      |      |  |  |

| Overall Width          | E           | 4.00 BSC  |      |      |  |  |

| Exposed Pad Width      | E2          | 2.55      | 2.65 | 2.75 |  |  |

| Overall Length         | D           | 4.00 BSC  |      |      |  |  |

| Exposed Pad Length     | D2          | 2.55      | 2.65 | 2.75 |  |  |

| Contact Width          | b           | 0.15      | 0.20 | 0.25 |  |  |

| Contact Length         | L           | 0.30      | 0.40 | 0.50 |  |  |

| Contact-to-Exposed Pad | K           | 0.20      | -    | -    |  |  |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- Package is saw singulated.

- 3. Dimensioning and tolerancing per ASME Y14.5M.

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

- REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-152A Sheet 2 of 2