Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XF

| Product Status             | Active                                                                      |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 32MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                           |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 16                                                                          |

| Program Memory Size        | 3.5KB (2K x 14)                                                             |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 256 x 8                                                                     |

| RAM Size                   | 256 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 12x10b                                                                  |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 28-VQFN Exposed Pad                                                         |

| Supplier Device Package    | 28-QFN (6x6)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1826t-i-ml |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com** or fax the **Reader Response Form** in the back of this data sheet to (480) 792-4150. We welcome your feedback.

#### **Most Current Data Sheet**

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

# 1.0 DEVICE OVERVIEW

The PIC16(L)F1826/27 are described within this data sheet. They are available in 18/20/28-pin packages. Figure 1-1 shows a block diagram of the PIC16(L)F1826/27 devices. Table 1-2 shows the pinout descriptions.

Reference Table 1-1 for peripherals available per device.

TABLE 1-1:DEVICE PERIPHERALSUMMARY

| Peripheral               |             | PIC16F/LF1826 | PIC16(L)F1827 |

|--------------------------|-------------|---------------|---------------|

| ADC                      |             | ٠             | •             |

| Capacitive Sensing Mod   | dule        | ٠             | •             |

| Digital-to-Analog Conve  | rter (DAC)  | •             | •             |

| Digital Signal Modulator | (DSM)       | •             | •             |

| EUSART                   |             | ٠             | •             |

| Fixed Voltage Reference  | e (FVR)     | •             | •             |

| Reference Clock Module   | e           | •             | •             |

| SR Latch                 |             | •             | •             |

| Capture/Compare/PWM      | Modules     |               |               |

|                          | ECCP1       | •             | •             |

|                          | ECCP2       |               | •             |

|                          | CCP3        |               | •             |

|                          | CCP4        |               | •             |

| Comparators              |             |               |               |

|                          | C1          | •             | •             |

|                          | C2          | •             | •             |

| Master Synchronous Se    | erial Ports |               |               |

|                          | MSSP1       | •             | •             |

|                          | MSSP2       |               | •             |

| Timers                   |             |               |               |

|                          | Timer0      | •             | •             |

|                          | Timer1      | •             | •             |

|                          | Timer2      | •             | •             |

|                          | Timer4      |               | •             |

|                          | Timer6      |               |               |

# 7.1 Power-on Reset (POR)

The POR circuit holds the device in Reset until VDD has reached an acceptable level for minimum operation. Slow rising VDD, fast operating speeds or analog performance may require greater than minimum VDD. The PWRT, BOR or MCLR features can be used to extend the start-up period until all device operation conditions have been met.

## 7.1.1 POWER-UP TIMER (PWRT)

The Power-up Timer provides a nominal 64 ms timeout on POR or Brown-out Reset.

The device is held in Reset as long as PWRT is active. The PWRT delay allows additional time for the VDD to rise to an acceptable level. The Power-up Timer is enabled by clearing the PWRTE bit in Configuration Word 1.

The Power-up Timer starts after the release of the POR and BOR.

For additional information, refer to Application Note AN607, *"Power-up Trouble Shooting"* (DS00607).

# 7.2 Brown-Out Reset (BOR)

The BOR circuit holds the device in Reset when Vdd reaches a selectable minimum level. Between the POR and BOR, complete voltage range coverage for execution protection can be implemented.

The Brown-out Reset module has four operating modes controlled by the BOREN<1:0> bits in Configuration Word 1. The four operating modes are:

- · BOR is always on

- · BOR is off when in Sleep

- · BOR is controlled by software

- · BOR is always off

Refer to Table 7-1 for more information.

The Brown-out Reset voltage level is selectable by configuring the BORV bit in Configuration Word 2.

A VDD noise rejection filter prevents the BOR from triggering on small events. If VDD falls below VBOR for a duration greater than parameter TBORDC, the device will reset. See Figure 7-2 for more information.

| BOREN<1:0> | SBOREN | Device Mode | BOR Mode | Device Operation<br>upon release of POR  | Device Operation<br>upon wake- up from<br>Sleep |  |

|------------|--------|-------------|----------|------------------------------------------|-------------------------------------------------|--|

| 11         | Х      | Х           | Active   | Waits for BOR ready <sup>(1)</sup>       |                                                 |  |

| 1.0        |        | Awake       | Active   | Waite for BOD ready                      |                                                 |  |

| 10         | 10 X   |             | Disabled | Waits for BOR ready                      |                                                 |  |

| 0.1        | 1      | X           | Active   | Begins in                                | nmediately                                      |  |

| 01         | 0      | Х           | Disabled | Begins in                                | mediately                                       |  |

| 00         | Х      | х           | Disabled | Begins immediately                       |                                                 |  |

| 00         | -      | X           | Disabled | Begins immediately<br>Begins immediately |                                                 |  |

# TABLE 7-1:BOR OPERATING MODES

Note 1: Even though this case specifically waits for the BOR, the BOR is already operating, so there is no delay in start-up.

# 7.2.1 BOR IS ALWAYS ON

When the BOREN bits of Configuration Word 1 are set to '11', the BOR is always on. The device start-up will be delayed until the BOR is ready and VDD is higher than the BOR threshold.

BOR protection is active during Sleep. The BOR does not delay wake-up from Sleep.

# 7.2.2 BOR IS OFF IN SLEEP

When the BOREN bits of Configuration Word 1 are set to '10', the BOR is on, except in Sleep. The device start-up will be delayed until the BOR is ready and VDD is higher than the BOR threshold.

BOR protection is not active during Sleep. The device wake-up will be delayed until the BOR is ready.

# 7.2.3 BOR CONTROLLED BY SOFTWARE

When the BOREN bits of Configuration Word 1 are set to '01', the BOR is controlled by the SBOREN bit of the BORCON register. The device start-up is not delayed by the BOR ready condition or the VDD level.

BOR protection begins as soon as the BOR circuit is ready. The status of the BOR circuit is reflected in the BORRDY bit of the BORCON register.

BOR protection is unchanged by Sleep.

# EXAMPLE 11-2: DATA EEPROM WRITE

|                      | BANKSEL<br>MOVLW<br>MOVWF<br>MOVLW<br>MOVWF<br>BCF<br>BCF<br>BSF       | EECON1, EEPG<br>EECON1, WREN                                 | ;Data Memory Address to write<br>;                                                                        |

|----------------------|------------------------------------------------------------------------|--------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|

| Required<br>Sequence | MOVLW<br>MOVWF<br>MOVLW<br>MOVWF<br>BSF<br>BSF<br>BCF<br>BTFSC<br>GOTO | 55h<br>EECON2<br>OAAh<br>EECON2<br>EECON1, WR<br>INTCON, GIE | ;<br>;Write 55h<br>;<br>;Write AAh<br>;Set WR bit to begin write<br>;Enable Interrupts<br>;Disable writes |

# PIC16(L)F1826/27

| EXAM                 | PLE 11-4:                                             | ERASING ONI                                                                    | E ROW OF PROGRAM MEMORY -                                                                                                                                                                                                                                                                                                                       |

|----------------------|-------------------------------------------------------|--------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                      |                                                       | routine assumes                                                                | -                                                                                                                                                                                                                                                                                                                                               |

| ; 1. A               | valid addr                                            | ess within the                                                                 | erase block is loaded in ADDRH:ADDRL                                                                                                                                                                                                                                                                                                            |

| ; 2. AI              | DDRH and AD                                           | DRL are located                                                                | in shared data memory 0x70 - 0x7F (common RAM)                                                                                                                                                                                                                                                                                                  |

|                      | BCF<br>BANKSEL<br>MOVF<br>MOVWF<br>MOVF<br>BSF        | INTCON,GIE<br>EEADRL<br>ADDRL,W<br>EEADRL<br>ADDRH,W<br>EEADRH<br>EECON1,EEPGD | <ul> <li>; Disable ints so required sequences will execute properly</li> <li>; Load lower 8 bits of erase address boundary</li> <li>; Load upper 6 bits of erase address boundary</li> <li>; Point to program memory</li> </ul>                                                                                                                 |

|                      | BCF                                                   | EECON1, EEFGD                                                                  | ; Not configuration space                                                                                                                                                                                                                                                                                                                       |

|                      | BSF                                                   | EECON1, FREE                                                                   | ; Specify an erase operation                                                                                                                                                                                                                                                                                                                    |

|                      | BSF                                                   | EECON1, WREN                                                                   | ; Enable writes                                                                                                                                                                                                                                                                                                                                 |

| Required<br>Sequence | MOVLW<br>MOVWF<br>MOVLW<br>MOVWF<br>BSF<br>NOP<br>NOP | 55h<br>EECON2<br>0AAh<br>EECON2<br>EECON1,WR                                   | <pre>; Start of required sequence to initiate erase<br/>; Write 55h<br/>;<br/>; Write AAh<br/>; Set WR bit to begin erase<br/>; Any instructions here are ignored as processor<br/>; halts to begin erase sequence<br/>; Processor will stop here and wait for erase complete.<br/>; after erase processor continues with 3rd instruction</pre> |

|                      | BCF<br>BSF                                            | EECON1,WREN<br>INTCON,GIE                                                      | ; Disable writes<br>; Enable interrupts                                                                                                                                                                                                                                                                                                         |

| R/W-0/0          | R/W-0/0               | R/W-0/0                       | R/W/HC-0/0                           | R/W-x/q           | R/W-0/0         | R/S/HC-0/0               | R/S/HC-0/0      |

|------------------|-----------------------|-------------------------------|--------------------------------------|-------------------|-----------------|--------------------------|-----------------|

| EEPGD            | CFGS                  | LWLO                          | FREE                                 | WRERR             | WREN            | WR                       | RD              |

| bit 7            |                       |                               |                                      |                   |                 |                          | bit (           |

|                  |                       |                               |                                      |                   |                 |                          |                 |

| Legend:          | <b>b</b> :4           |                               | <b>b</b> :4                          |                   | nanted bit was  | d aa (0)                 |                 |

| R = Readable     |                       | W = Writable                  |                                      | •                 | nented bit, rea |                          | than Decete     |

| S = Bit can or   | 5                     | x = Bit is unk                |                                      |                   |                 | R/Value at all o         | iner Resets     |

| '1' = Bit is set |                       | '0' = Bit is cl€              | eared                                | HC = Bit is cl    | eared by hardv  | vare                     |                 |

| bit 7            | EEPGD: Flas           | sh Program/Da                 | ta EEPROM M                          | emory Select      | bit             |                          |                 |

|                  | 1 = Accesse           | s program spa                 | ce Flash memo                        | -                 |                 |                          |                 |

|                  |                       | s data EEPRC                  | -                                    |                   |                 |                          |                 |

| bit 6            |                       | -                             | EEPROM or C                          | -                 |                 |                          |                 |

|                  |                       |                               | n, User ID and I<br>Im or data EEP   |                   |                 |                          |                 |

| bit 5            |                       | Write Latches                 |                                      |                   |                 |                          |                 |

| bit 0            |                       |                               | <u>space)</u> OR <u>CFC</u>          | SS = 0 and $FF$   | PGD = 1 (proc   | oram Flash) <sup>.</sup> |                 |

|                  |                       | -                             |                                      |                   |                 | program memoi            | v latches are   |

|                  | upda                  | ated.                         |                                      |                   |                 | C                        | -               |

|                  |                       |                               |                                      |                   |                 | into program m           | emory latche    |

|                  | and                   | initiates a write             | e of all the data                    | stored in the     | program memo    | bry latches.             |                 |

|                  | <u> If CFGS = 0 a</u> | and EEPGD =                   | 0: (Accessing c                      | lata EEPROM       | 1)              |                          |                 |

|                  |                       |                               | WR command i                         |                   |                 | EPROM.                   |                 |

| bit 4            | FREE: Progr           | am Flash Eras                 | e Enable bit                         |                   |                 |                          |                 |

|                  |                       | -                             | <u>space)</u> OR <u>CFC</u>          |                   |                 | -                        |                 |

|                  |                       |                               | operation on the                     | he next WR co     | ommand (clear   | ed by hardware           | after comple    |

|                  |                       | of erase).<br>forms a write o | peration on the                      | next WR com       | mand            |                          |                 |

|                  | 0 - 1 Ch              |                               | peration on the                      |                   | inana.          |                          |                 |

|                  |                       |                               | 0: (Accessing c                      |                   |                 |                          |                 |

|                  | -                     |                               |                                      | will initiate bot | h a erase cycle | e and a write cyc        | de.             |

| bit 3            |                       | PROM Error F                  | •                                    |                   |                 |                          |                 |

|                  |                       |                               | improper prog<br>et attempt (write   |                   |                 | empt or termination      | tion (bit is se |

|                  |                       |                               | operation comp                       |                   |                 |                          |                 |

| bit 2            |                       | ram/Erase Ena                 | •                                    | j                 |                 |                          |                 |

|                  | -                     | rogram/erase o                |                                      |                   |                 |                          |                 |

|                  |                       |                               | rasing of progra                     | am Flash and      | data EEPROM     | l                        |                 |

| bit 1            | WR: Write Co          | ontrol bit                    |                                      |                   |                 |                          |                 |

|                  |                       |                               | sh or data EEPI                      |                   |                 |                          |                 |

|                  |                       |                               | ned and the bit<br>e set (not cleare |                   |                 | operation is co          | mplete.         |

|                  |                       | •                             | on to the Flash                      |                   |                 | e and inactive.          |                 |

| bit 0            | RD: Read Co           | -                             |                                      |                   |                 |                          |                 |

|                  |                       |                               | lash or data E                       | EPROM read        | d. Read takes   | one cycle. RD            | is cleared in   |

|                  |                       |                               |                                      |                   |                 | , <b>.</b>               |                 |

|                  | nardware              | e. The RD bit o               | an only be set                       | (not cleared) i   | n software.     |                          |                 |

# REGISTER 11-5: EECON1: EEPROM CONTROL 1 REGISTER

#### 12.2.3 PORTA FUNCTIONS AND OUTPUT PRIORITIES

Each PORTA pin is multiplexed with other functions. The pins, their combined functions and their output priorities are shown in Table 12-2.

When multiple outputs are enabled, the actual pin control goes to the peripheral with the highest priority.

Analog input functions, such as ADC, comparator and CapSense inputs, are not shown in the priority lists. These inputs are active when the I/O pin is set for Analog mode using the ANSELx registers. Digital output functions may control the pin when it is in Analog mode with the priority shown in Table 12-2.

| Pin Name | Function Priority <sup>(1)</sup>                                                                                     |

|----------|----------------------------------------------------------------------------------------------------------------------|

| RA0      | SDO2 (PIC16(L)F1827 only)<br>RA0                                                                                     |

| RA1      | SS2 (PIC16(L)F1827 only)<br>RA1                                                                                      |

| RA2      | DACOUT (DAC)<br>RA2                                                                                                  |

| RA3      | SRQ (SR latch)<br>CCP3 (PIC16(L)F1827 only)<br>C1OUT (Comparator)<br>RA3                                             |

| RA4      | SRNQ (SR latch)<br>CCP4 (PIC16(L)F1827 only)<br>T0CKI<br>C2OUT (Comparator)<br>RA4                                   |

| RA5      | Input only pin                                                                                                       |

| RA6      | OSC2 (enabled by Configura-<br>tion Word)<br>CLKOUT<br>CLKR<br>SDO1<br>P1D<br>P2B (PIC16(L)F1827 only)<br>RA6        |

| RA7      | OSC1/CLKIN (enabled by<br>Configuration Word)<br>P1C<br>CCP2 (PIC16(L)F1827 only)<br>P2A (PIC16(L)F1827 only)<br>RA7 |

TABLE 12-2: PORTA OUTPUT PRIORITY

**Note 1:** Priority listed from highest to lowest.

Each PORTA pin is multiplexed with other functions. The pins, their combined functions and their output priorities are briefly described here. For additional information, refer to the appropriate section in this data sheet.

When multiple outputs are enabled, the actual pin control goes to the peripheral with the lowest number in the following lists.

# 14.3 FVR Control Registers

#### REGISTER 14-1: FVRCON: FIXED VOLTAGE REFERENCE CONTROL REGISTER

| R/W-0/0         | R-q/q                                                      | R/W-0/0                                                                                                                                                                                                                                                                                                                                                                                                                                                   | R/W-0/0                                                             | R/W-0/0                                                                  | R/W-0/0                                              | R/W-0/0          | R/W-0/0      |  |

|-----------------|------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|--------------------------------------------------------------------------|------------------------------------------------------|------------------|--------------|--|

| FVREN           | FVRRDY <sup>(1)</sup>                                      | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Reserved                                                            | CDAF                                                                     | /R<1:0>                                              | ADFVI            | R<1:0>       |  |

| bit 7           |                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                     |                                                                          |                                                      |                  | bit 0        |  |

|                 |                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                     |                                                                          |                                                      |                  |              |  |

| Legend:         |                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                     |                                                                          |                                                      |                  |              |  |

| R = Readabl     | le bit                                                     | W = Writable                                                                                                                                                                                                                                                                                                                                                                                                                                              | bit                                                                 | U = Unimpler                                                             | nented bit, read                                     | l as '0'         |              |  |

| u = Bit is und  | changed                                                    | x = Bit is unkr                                                                                                                                                                                                                                                                                                                                                                                                                                           | nown                                                                | -n/n = Value a                                                           | at POR and BO                                        | R/Value at all o | other Resets |  |

| '1' = Bit is se | et                                                         | '0' = Bit is cle                                                                                                                                                                                                                                                                                                                                                                                                                                          | ared                                                                | q = Value de                                                             | pends on condit                                      | ion              |              |  |

| bit 7           | 0 = Fixed Vo<br>1 = Fixed Vo                               | d Voltage Refe<br>Itage Referenc<br>Itage Referenc                                                                                                                                                                                                                                                                                                                                                                                                        | e is disabled<br>e is enabled                                       |                                                                          |                                                      |                  |              |  |

| bit 6           | 0 = Fixed Vo                                               | ed Voltage Rei<br>Itage Referenc<br>Itage Referenc                                                                                                                                                                                                                                                                                                                                                                                                        | e output is no                                                      | t ready or not e                                                         | enabled                                              |                  |              |  |

| bit 5-4         |                                                            | <b>Reserved:</b> Read as '0'. Maintain these bits clear.                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                     |                                                                          |                                                      |                  |              |  |

| bit 3-2         | 00 = Compar<br>01 = Compar<br>10 = Compar                  | <b>CDAFVR&lt;1:0&gt;:</b> Comparator and DAC Fixed Voltage Reference Selection bit<br>00 = Comparator and DAC Fixed Voltage Reference Peripheral output is off.<br>01 = Comparator and DAC Fixed Voltage Reference Peripheral output is 1x (1.024V)<br>10 = Comparator and DAC Fixed Voltage Reference Peripheral output is 2x (2.048V) <sup>(2)</sup><br>11 = Comparator and DAC Fixed Voltage Reference Peripheral output is 4x (4.096V) <sup>(2)</sup> |                                                                     |                                                                          |                                                      |                  |              |  |

| bit 1-0         | ADFVR<1:0><br>00 = ADC Fix<br>01 = ADC Fix<br>10 = ADC Fix | : ADC Fixed V<br>ked Voltage Re<br>ked Voltage Re<br>ked Voltage Re<br>ked Voltage Re                                                                                                                                                                                                                                                                                                                                                                     | oltage Refere<br>ference Peripl<br>ference Peripl<br>ference Peripl | nce Selection I<br>heral output is<br>heral output is<br>heral output is | bit<br>off.<br>1x (1.024V)<br>2x (2.048V) <b>(2)</b> |                  |              |  |

|                 | FVRRDY is always '1' on devices with LDO (PIC16F1826/27).  |                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                     |                                                                          |                                                      |                  |              |  |

2: Fixed Voltage Reference output cannot exceed VDD.

# TABLE 14-1: SUMMARY OF REGISTERS ASSOCIATED WITH THE FVR MODULE

| Name   | Bit 7 | Bit 6  | Bit 5    | Bit 4    | Bit 3   | Bit 2   | Bit 1  | Bit 0  | Register<br>on page |

|--------|-------|--------|----------|----------|---------|---------|--------|--------|---------------------|

| FVRCON | FVREN | FVRRDY | Reserved | Reserved | CDAFVR1 | CDAFVR0 | ADFVR1 | ADFVR0 | 136                 |

Legend: Shaded cells are unused by the FVR module.

# PIC16(L)F1826/27

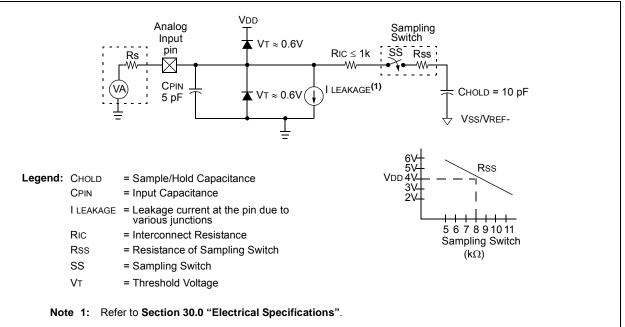

# FIGURE 16-4: ANALOG INPUT MODEL

# 19.2 Comparator Control

Each comparator has 2 control registers: CMxCON0 and CMxCON1.

The CMxCON0 registers (see Register 19-1) contain Control and Status bits for the following:

- Enable

- · Output selection

- Output polarity

- · Speed/Power selection

- · Hysteresis enable

- · Output synchronization

The CMxCON1 registers (see Register 19-2) contain Control bits for the following:

- · Interrupt enable

- · Interrupt edge polarity

- · Positive input channel selection

- Negative input channel selection

#### 19.2.1 COMPARATOR ENABLE

Setting the CxON bit of the CMxCON0 register enables the comparator for operation. Clearing the CxON bit disables the comparator resulting in minimum current consumption.

#### 19.2.2 COMPARATOR OUTPUT SELECTION

The output of the comparator can be monitored by reading either the CxOUT bit of the CMxCON0 register or the MCxOUT bit of the CMOUT register. In order to make the output available for an external connection, the following conditions must be true:

- · CxOE bit of the CMxCON0 register must be set

- · Corresponding TRIS bit must be cleared

- · CxON bit of the CMxCON0 register must be set

| Note 1: | The CxOE bit of the CMxCON0 register   |

|---------|----------------------------------------|

|         | overrides the PORT data latch. Setting |

|         | the CxON bit of the CMxCON0 register   |

|         | has no impact on the port override.    |

2: The internal output of the comparator is latched with each instruction cycle. Unless otherwise specified, external outputs are not latched.

#### 19.2.3 COMPARATOR OUTPUT POLARITY

Inverting the output of the comparator is functionally equivalent to swapping the comparator inputs. The polarity of the comparator output can be inverted by setting the CxPOL bit of the CMxCON0 register. Clearing the CxPOL bit results in a non-inverted output.

Table 19-1 shows the output state versus input conditions, including polarity control.

#### TABLE 19-1: COMPARATOR OUTPUT STATE VS. INPUT CONDITIONS

| Input Condition | CxPOL | CxOUT |

|-----------------|-------|-------|

| CxVN > CxVP     | 0     | 0     |

| CxVN < CxVP     | 0     | 1     |

| CxVN > CxVP     | 1     | 1     |

| CxVN < CxVP     | 1     | 0     |

## 19.2.4 COMPARATOR SPEED/POWER SELECTION

The trade-off between speed or power can be optimized during program execution with the CxSP control bit. The default state for this bit is '1' which selects the normal speed mode. Device power consumption can be optimized at the cost of slower comparator propagation delay by clearing the CxSP bit to '0'.

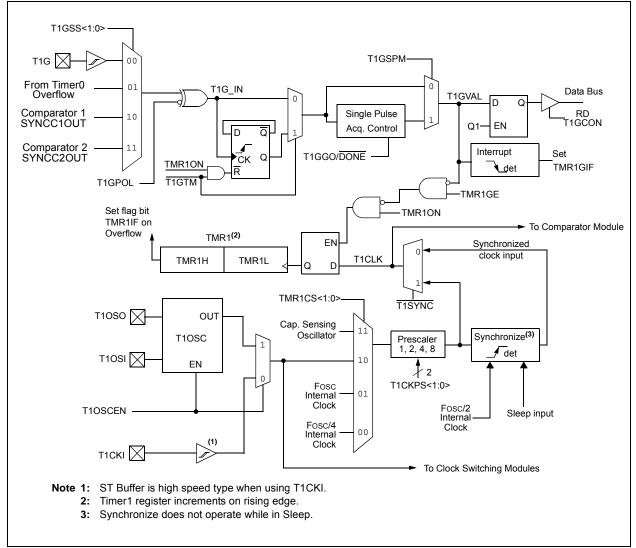

# 21.0 TIMER1 MODULE WITH GATE CONTROL

The Timer1 module is a 16-bit timer/counter with the following features:

- 16-bit timer/counter register pair (TMR1H:TMR1L)

- Programmable internal or external clock source

- 2-bit prescaler

- · Dedicated 32 kHz oscillator circuit

- · Optionally synchronized comparator out

- Multiple Timer1 gate (count enable) sources

- · Interrupt on overflow

- Wake-up on overflow (external clock, Asynchronous mode only)

- Time base for the Capture/Compare function

- Special Event Trigger (with CCP/ECCP)

- · Selectable Gate Source Polarity

- Gate Toggle mode

- Gate Single-pulse mode

- Gate Value Status

- Gate Event Interrupt

- Figure 21-1 is a block diagram of the Timer1 module.

# FIGURE 21-1: TIMER1 BLOCK DIAGRAM

# PIC16(L)F1826/27

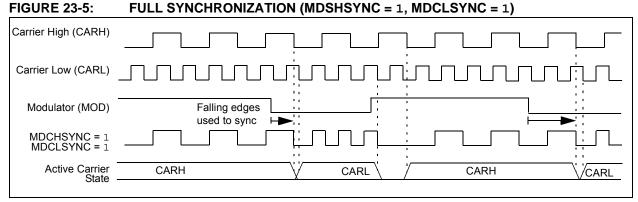

| FIGURE 23-4:                 | CARRIER LOW SYNCHRONIZATION (MDSHSYNC = 0, MDCLSYNC = 1) |

|------------------------------|----------------------------------------------------------|

| Carrier High (CARH)          |                                                          |

| Carrier Low (CARL)           |                                                          |

| Modulator (MOD)              |                                                          |

| MDCHSYNC = 0<br>MDCLSYNC = 1 |                                                          |

| Active Carrier<br>State      |                                                          |

|                              |                                                          |

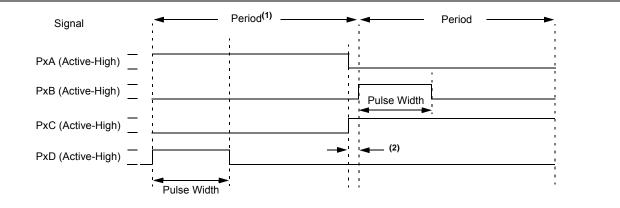

# 24.4.2.1 Direction Change in Full-Bridge Mode

In the Full-Bridge mode, the PxM1 bit in the CCPxCON register allows users to control the forward/reverse direction. When the application firmware changes this direction control bit, the module will change to the new direction on the next PWM cycle.

A direction change is initiated in software by changing the PxM1 bit of the CCPxCON register. The following sequence occurs four Timer cycles prior to the end of the current PWM period:

- The modulated outputs (PxB and PxD) are placed in their inactive state.

- The associated unmodulated outputs (PxA and PxC) are switched to drive in the opposite direction.

- PWM modulation resumes at the beginning of the next period.

See Figure 24-12 for an illustration of this sequence.

The Full-Bridge mode does not provide dead-band delay. As one output is modulated at a time, dead-band delay is generally not required. There is a situation where dead-band delay is required. This situation occurs when both of the following conditions are true:

- 1. The direction of the PWM output changes when the duty cycle of the output is at or near 100%.

- 2. The turn off time of the power switch, including the power device and driver circuit, is greater than the turn on time.

Figure 24-13 shows an example of the PWM direction changing from forward to reverse, at a near 100% duty cycle. In this example, at time t1, the output PxA and PxD become inactive, while output PxC becomes active. Since the turn off time of the power devices is longer than the turn on time, a shoot-through current will flow through power devices QC and QD (see Figure 24-10) for the duration of 't'. The same phenomenon will occur to power devices QA and QB for PWM direction change from reverse to forward.

If changing PWM direction at high duty cycle is required for an application, two possible solutions for eliminating the shoot-through current are:

- 1. Reduce PWM duty cycle for one PWM period before changing directions.

- 2. Use switch drivers that can drive the switches off faster than they can drive them on.

Other options to prevent shoot-through current may exist.

# FIGURE 24-12: EXAMPLE OF PWM DIRECTION CHANGE

**Note 1:** The direction bit PxM1 of the CCPxCON register is written any time during the PWM cycle.

2: When changing directions, the PxA and PxC signals switch before the end of the current PWM cycle. The modulated PxB and PxD signals are inactive at this time. The length of this time is four Timer counts.

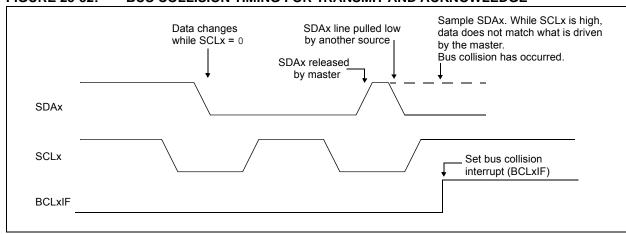

# FIGURE 25-32: BUS COLLISION TIMING FOR TRANSMIT AND ACKNOWLEDGE

## REGISTER 25-2: SSPxCON1: SSPx CONTROL REGISTER 1

| R/C/HS-0/0              | R/C/HS-0/0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | R/W-0/0                                                                                                                                                                      | R/W-0/0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | R/W-0/0                                                                                                 | R/W-0/0                                  | R/W-0/0                                            | R/W-0/0                                     |

|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|------------------------------------------|----------------------------------------------------|---------------------------------------------|

| WCOL                    | SSPxOV                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | SSPxEN                                                                                                                                                                       | CKP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                         | SSPx                                     | M<3:0>                                             |                                             |

| bit 7                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                         |                                          |                                                    | bit                                         |

|                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                         |                                          |                                                    |                                             |

| Legend:                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                         |                                          |                                                    |                                             |

| R = Readable bit        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | W = Writable bit                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | •                                                                                                       | ted bit, read as '0'                     |                                                    |                                             |

| u = Bit is unchang      | ged                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | x = Bit is unknow                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                         |                                          | e at all other Resets                              |                                             |