# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                      |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 32MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                           |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 16                                                                          |

| Program Memory Size        | 3.5KB (2K x 14)                                                             |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 256 x 8                                                                     |

| RAM Size                   | 256 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 12x10b                                                                  |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                                              |

| Supplier Device Package    | 20-SSOP                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1826t-i-ss |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

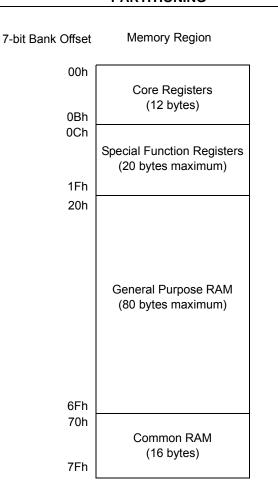

#### 3.2.2 SPECIAL FUNCTION REGISTER

The Special Function Registers are registers used by the application to control the desired operation of peripheral functions in the device. The Special Function Registers occupy the 20 bytes after the core registers of every data memory bank (addresses x0Ch/x8Ch through x1Fh/x9Fh). The registers associated with the operation of the peripherals are described in the appropriate peripheral chapter of this data sheet.

#### 3.2.3 GENERAL PURPOSE RAM

There are up to 80 bytes of GPR in each data memory bank. The Special Function Registers occupy the 20 bytes after the core registers of every data memory bank (addresses x0Ch/x8Ch through x1Fh/x9Fh).

#### 3.2.3.1 Linear Access to GPR

The general purpose RAM can be accessed in a non-banked method via the FSRs. This can simplify access to large memory structures. See **Section 3.5.2** "Linear Data Memory" for more information.

#### 3.2.4 COMMON RAM

There are 16 bytes of common RAM accessible from all banks.

#### FIGURE 3-3: BANKED MEMORY PARTITIONING

#### 3.2.5 DEVICE MEMORY MAPS

The memory maps for the device family are as shown in Table 3-3 and Table 3-4.

NOTES:

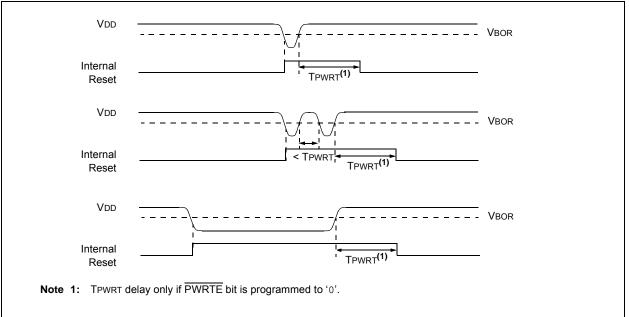

#### REGISTER 7-1: BORCON: BROWN-OUT RESET CONTROL REGISTER

| R/W-1/u | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | R-q/u  |

|---------|-----|-----|-----|-----|-----|-----|--------|

| SBOREN  | —   | —   | _   | —   | —   | —   | BORRDY |

| bit 7   | -   |     |     |     |     |     | bit 0  |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | q = Value depends on condition                        |

| bit 7   | SBOREN: Software Brown-out Reset Enable bit<br><u>If BOREN &lt;1:0&gt; in Configuration Word 1 ≠ 01</u> :<br>SBOREN is read/write, but has no effect on the BOR.<br><u>If BOREN &lt;1:0&gt; in Configuration Word 1 = 01</u> :<br>1 = BOR Enabled<br>0 = BOR Disabled |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6-1 | Unimplemented: Read as '0'                                                                                                                                                                                                                                            |

| bit 0   | BORRDY: Brown-out Reset Circuit Ready Status bit<br>1 = The Brown-out Reset circuit is active<br>0 = The Brown-out Reset circuit is inactive                                                                                                                          |

## 7.11 Power Control (PCON) Register

The Power Control (PCON) register contains flag bits to differentiate between a:

- Power-on Reset (POR)

- Brown-out Reset (BOR)

- Reset Instruction Reset (RI)

- MCLR Reset (RMCLR)

- Stack Underflow Reset (STKUNF)

- Stack Overflow Reset (STKOVF)

The PCON register bits are shown in Register 7-2.

#### REGISTER 7-2: PCON: POWER CONTROL REGISTER

| R/W/HS-0/q | R/W/HS-0/q | U-0 | U-0 | R/W/HC-1/q | R/W/HC-1/q | R/W/HC-q/u | R/W/HC-q/u |

|------------|------------|-----|-----|------------|------------|------------|------------|

| STKOVF     | STKUNF     | -   | —   | RMCLR      | RI         | POR        | BOR        |

| bit 7      |            |     |     |            |            |            | bit 0      |

| Legend:          |                                         |                            |                                                                  |  |  |  |

|------------------|-----------------------------------------|----------------------------|------------------------------------------------------------------|--|--|--|

| HC = Bit is cl   | eared by hardw                          | vare                       | HS = Bit is set by hardware                                      |  |  |  |

| R = Readable     | e bit                                   | W = Writable bit           | U = Unimplemented bit, read as '0'                               |  |  |  |

| u = Bit is unc   | hanged                                  | x = Bit is unknown         | -m/n = Value at POR and BOR/Value at all other Resets            |  |  |  |

| '1' = Bit is set | t i i i i i i i i i i i i i i i i i i i | '0' = Bit is cleared       | q = Value depends on condition                                   |  |  |  |

|                  |                                         |                            |                                                                  |  |  |  |

| bit 7            | STKOVF: St                              | tack Overflow Flag bit     |                                                                  |  |  |  |

|                  | 1 = A Stack                             | Overflow occurred          |                                                                  |  |  |  |

|                  | 0 = A Stack                             | Overflow has not occurred  | or set to '0' by firmware                                        |  |  |  |

| bit 6            | STKUNF: St                              | tack Underflow Flag bit    |                                                                  |  |  |  |

|                  |                                         | Underflow occurred         |                                                                  |  |  |  |

|                  | 0 = A Stack                             | Underflow has not occurre  | d or set to '0' by firmware                                      |  |  |  |

| bit 5-4          | Unimpleme                               | nted: Read as '0'          |                                                                  |  |  |  |

| bit 3            | RMCLR: MC                               | CLR Reset Flag bit         |                                                                  |  |  |  |

|                  |                                         | Reset has not occurred or  |                                                                  |  |  |  |

|                  | 0 = A MCLR                              | Reset has occurred (set to | o '0' in hardware when a MCLR Reset occurs)                      |  |  |  |

| bit 2            | RI: RESET I                             | nstruction Flag bit        |                                                                  |  |  |  |

|                  |                                         |                            | executed or set to '1' by firmware                               |  |  |  |

|                  |                                         |                            | Ited (set to '0' in hardware upon executing a RESET instruction) |  |  |  |

| bit 1            | POR: Power                              | r-on Reset Status bit      |                                                                  |  |  |  |

|                  |                                         | er-on Reset occurred       |                                                                  |  |  |  |

|                  |                                         |                            | be set in software after a Power-on Reset occurs)                |  |  |  |

| bit 0            | BOR: Brown                              | n-out Reset Status bit     |                                                                  |  |  |  |

|                  |                                         | n-out Reset occurred       |                                                                  |  |  |  |

|                  |                                         | -out Reset occurred (must  | be set in software after a Power-on Reset or Brown-out Reset     |  |  |  |

| occurs)          |                                         |                            |                                                                  |  |  |  |

|                  |                                         |                            |                                                                  |  |  |  |

#### TABLE 10-3: SUMMARY OF REGISTERS ASSOCIATED WITH WATCHDOG TIMER

| Name   | Bit 7 | Bit 6 | Bit 5       | Bit 4 | Bit 3 | Bit 2 | Bit 1    | Bit 0  | Register<br>on Page |

|--------|-------|-------|-------------|-------|-------|-------|----------|--------|---------------------|

| OSCCON | —     |       | IRCF<3:0>   |       |       |       | SCS<1:0> |        | 69                  |

| STATUS | —     | _     | —           | TO    | PD    | Z     | DC       | С      | 21                  |

| WDTCON | —     | _     | — WDTPS<4:( |       |       |       |          | SWDTEN | 99                  |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by Watchdog Timer.

#### TABLE 10-4: SUMMARY OF CONFIGURATION WORD WITH WATCHDOG TIMER

| Name    | Bits | Bit -/7 | Bit -/6 | Bit 13/5 | Bit 12/4  | Bit 11/3 | Bit 10/2   | Bit 9/1   | Bit 8/0 | Register<br>on Page |

|---------|------|---------|---------|----------|-----------|----------|------------|-----------|---------|---------------------|

| CONFIG1 | 13:8 | _       | _       | FCMEN    | IESO      | CLKOUTEN | BOREN<1:0> |           | CPD     | 44                  |

| CONFIGT | 7:0  | CP      | MCLRE   | PWRTE    | WDTE<1:0> |          |            | FOSC<2:0> |         | 44                  |

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used by Watchdog Timer.

#### 12.3.4 PORTB FUNCTIONS AND OUTPUT PRIORITIES

Each PORTB pin is multiplexed with other functions. The pins, their combined functions and their output priorities are shown in Table 12-5.

When multiple outputs are enabled, the actual pin control goes to the peripheral with the highest priority.

Analog input and some digital input functions are not included in the list below. These input functions can remain active when the pin is configured as an output. Certain digital input functions, such as the EUSART RX signal, override other port functions and are included in the priority list.

## TABLE 12-5: PORTB OUTPUT PRIORITY

| Pin Name | Function Priority <sup>(1)</sup>                                                                      |

|----------|-------------------------------------------------------------------------------------------------------|

| RB0      | P1A<br>RB0                                                                                            |

| RB1      | SDA1<br>RX/DT<br>RB1                                                                                  |

| RB2      | SDA2 (PIC16(L)F1827 only)<br>TX/CK<br>RX/DT<br>SDO1<br>RB2                                            |

| RB3      | MDOUT<br>CCP1/P1A<br>RB3                                                                              |

| RB4      | SCL1<br>SCK1<br>RB4                                                                                   |

| RB5      | SCL2 (PIC16(L)F1827 only)<br>TX/CK<br>SCK2 (PIC16(L)F1827 only)<br>P1B<br>RB5                         |

| RB6      | ICSPCLK (Programming)<br>T1OSI<br>P1C<br>CCP2 (PIC16(L)F1827 only)<br>P2A (PIC16(L)F1827 only)<br>RB6 |

| RB7      | ICSPDAT (Programming)<br>T1OSO<br>P1D<br>P2B (PIC16(L)F1827 only)<br>RB7                              |

Note 1: Priority listed from highest to lowest.

## 20.2 Option and Timer0 Control Register

### REGISTER 20-1: OPTION\_REG: OPTION REGISTER

| R/W-1/1                             | R/W-1/1  | <b>R/W-</b> 1                   | I/1 I                  | R/W-1/1     | R/W-1/1        | R/W-1/1        | R/W       | /-1/1      | R/W-1/1    |

|-------------------------------------|----------|---------------------------------|------------------------|-------------|----------------|----------------|-----------|------------|------------|

| WPUEN                               | INTEDG   | TMR0                            | CS 1                   | MR0SE       | PSA            |                | PS<2      | 2:0>       |            |

| bit 7                               |          |                                 |                        |             |                |                |           |            | bit (      |

| <u> </u>                            |          |                                 |                        |             |                |                |           |            |            |

| Legend:                             |          |                                 |                        |             |                |                |           |            |            |

| R = Readable                        |          | W = Wri                         |                        | -           | -              | emented bit, r |           |            |            |

| u = Bit is uncl<br>'1' = Bit is set | 0        |                                 | s unknow<br>is cleared |             | -n/n = value   | at POR and     | BOR/value | at all otr | ier Resets |

|                                     |          | 0 <b>–</b> Dil                  | is cleared             | 1           |                |                |           |            |            |

| bit 7                               | WPUEN: V | Veak Pull-up                    | Enable                 | bit         |                |                |           |            |            |

|                                     |          |                                 |                        |             | MCLR, if it is |                |           |            |            |

|                                     |          |                                 |                        |             | al WPUx latc   | h values       |           |            |            |

| bit 6                               |          | nterrupt Edg                    |                        |             |                |                |           |            |            |

|                                     |          | pt on rising e<br>pt on falling |                        |             |                |                |           |            |            |

| bit 5                               |          | Timer0 Cloc                     | •                      |             |                |                |           |            |            |

| DIL J                               |          | tion on TOCK                    |                        | Select bit  |                |                |           |            |            |

|                                     |          | al instruction                  |                        | ck (Fosc/4  | ł)             |                |           |            |            |

| bit 4                               | TMR0SE:  | Timer0 Sour                     | ce Edge                | Select bit  |                |                |           |            |            |

|                                     |          | ent on high-                    |                        |             |                |                |           |            |            |

| 1.11.0                              |          | ient on low-to                  |                        | insition on | TOCKI pin      |                |           |            |            |

| bit 3                               |          | caler Assign<br>aler is not as  |                        | the Timer   | 0 modulo       |                |           |            |            |

|                                     |          | aler is assign                  |                        |             |                |                |           |            |            |

| bit 2-0                             | PS<2:0>: | Prescaler Ra                    | ate Select             | t bits      |                |                |           |            |            |

|                                     | E        | Bit Value Ti                    | mer0 Rate              | e           |                |                |           |            |            |

|                                     | -        | 000                             | 1:2                    | _           |                |                |           |            |            |

|                                     |          | 001                             | 1:4                    |             |                |                |           |            |            |

|                                     |          | 010<br>011                      | 1:8<br>1:16            |             |                |                |           |            |            |

|                                     |          | 100                             | 1:32                   |             |                |                |           |            |            |

|                                     |          | 101                             | 1:64                   |             |                |                |           |            |            |

|                                     |          | 110                             | 1:128                  |             |                |                |           |            |            |

|                                     |          | 111                             | 1 : 256                |             |                |                |           |            |            |

| TABLE 20-1                          | : SUMMA  | RY OF RE                        | GISTER                 | S ASSO      | CIATED WI      | TH TIMER0      |           |            |            |

| Name                                | Bit 7    | Bit 6                           | Bit 5                  | Bit 4       | Bit 3          | Bit 2          | Bit 1     | Bit 0      | Register   |

| Name                        | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3   | Bit 2   | Bit 1  | Bit 0  | Register<br>on Page |

|-----------------------------|--------|--------|--------|--------|---------|---------|--------|--------|---------------------|

| CPSCON0                     | CPSON  | —      | —      | —      | CPSRNG1 | CPSRNG0 | CPSOUT | T0XCS  | 318                 |

| INTCON                      | GIE    | PEIE   | TMR0IE | INTE   | IOCIE   | TMR0IF  | INTF   | IOCIF  | 86                  |

| OPTION_REG                  | WPUEN  | INTEDG | TMR0CS | TMR0SE | PSA     | PS2     | PS1    | PS0    | 177                 |

| TMR0 Timer0 Module Register |        |        |        |        |         |         |        |        |                     |

| TRISA                       | TRISA7 | TRISA6 | TRISA5 | TRISA4 | TRISA3  | TRISA2  | TRISA1 | TRISA0 | 122                 |

**Legend:** — = Unimplemented locations, read as '0'. Shaded cells are not used by the Timer0 module.

\* Page provides register information.

#### 21.6.2 TIMER1 GATE SOURCE SELECTION

The Timer1 gate source can be selected from one of four different sources. Source selection is controlled by the T1GSS bits of the T1GCON register. The polarity for each available source is also selectable. Polarity selection is controlled by the T1GPOL bit of the T1GCON register.

TABLE 21-4: TIMER1 GATE SOURCES

| T1GSS | Timer1 Gate Source                                                       |

|-------|--------------------------------------------------------------------------|

| 00    | Timer1 Gate Pin                                                          |

| 01    | Overflow of Timer0<br>(TMR0 increments from FFh to 00h)                  |

| 10    | Comparator 1 Output SYNCC1OUT<br>(optionally Timer1 synchronized output) |

| 11    | Comparator 2 Output SYNCC2OUT<br>(optionally Timer1 synchronized output) |

#### 21.6.2.1 T1G Pin Gate Operation

The T1G pin is one source for Timer1 gate control. It can be used to supply an external source to the Timer1 gate circuitry.

#### 21.6.2.2 Timer0 Overflow Gate Operation

When Timer0 increments from FFh to 00h, a low-to-high pulse will automatically be generated and internally supplied to the Timer1 gate circuitry.

#### 21.6.2.3 Comparator C1 Gate Operation

The output resulting from a Comparator 1 operation can be selected as a source for Timer1 gate control. The Comparator 1 output (SYNCC1OUT) can be synchronized to the Timer1 clock or left asynchronous. For more information see **Section 19.4.1 "Comparator Output Synchronization**".

#### 21.6.2.4 Comparator C2 Gate Operation

The output resulting from a Comparator 2 operation can be selected as a source for Timer1 gate control. The Comparator 2 output (SYNCC2OUT) can be synchronized to the Timer1 clock or left asynchronous. For more information see **Section 19.4.1 "Comparator Output Synchronization"**.

## 21.6.3 TIMER1 GATE TOGGLE MODE

When Timer1 Gate Toggle mode is enabled, it is possible to measure the full-cycle length of a Timer1 gate signal, as opposed to the duration of a single level pulse.

The Timer1 gate source is routed through a flip-flop that changes state on every incrementing edge of the signal. See Figure 21-4 for timing details.

Timer1 Gate Toggle mode is enabled by setting the T1GTM bit of the T1GCON register. When the T1GTM bit is cleared, the flip-flop is cleared and held clear. This is necessary in order to control which edge is measured.

| Note: | Enabling Toggle mode at the same time       |  |  |  |

|-------|---------------------------------------------|--|--|--|

|       | as changing the gate polarity may result in |  |  |  |

|       | indeterminate operation.                    |  |  |  |

#### 21.6.4 TIMER1 GATE SINGLE-PULSE MODE

When Timer1 Gate Single-Pulse mode is enabled, it is possible to capture a single pulse gate event. Timer1 Gate Single-Pulse mode is first enabled by setting the T1GSPM bit in the T1GCON register. Next, the T1GGO/DONE bit in the T1GCON register must be set. The Timer1 will be fully enabled on the next incrementing edge. On the next trailing edge of the pulse, the T1GGO/DONE bit will automatically be cleared. No other gate events will be allowed to increment Timer1 until the T1GGO/DONE bit is once again set in software. See Figure 21-5 for timing details.

If the Single Pulse Gate mode is disabled by clearing the T1GSPM bit in the T1GCON register, the T1GGO/DONE bit should also be cleared.

Enabling the Toggle mode and the Single-Pulse mode simultaneously will permit both sections to work together. This allows the cycle times on the Timer1 gate source to be measured. See Figure 21-6 for timing details.

#### 21.6.5 TIMER1 GATE VALUE STATUS

When Timer1 Gate Value Status is utilized, it is possible to read the most current level of the gate control value. The value is stored in the T1GVAL bit in the T1GCON register. The T1GVAL bit is valid even when the Timer1 gate is not enabled (TMR1GE bit is cleared).

#### 21.6.6 TIMER1 GATE EVENT INTERRUPT

When Timer1 Gate Event Interrupt is enabled, it is possible to generate an interrupt upon the completion of a gate event. When the falling edge of T1GVAL occurs, the TMR1GIF flag bit in the PIR1 register will be set. If the TMR1GIE bit in the PIE1 register is set, then an interrupt will be recognized.

The TMR1GIF flag bit operates even when the Timer1 gate is not enabled (TMR1GE bit is cleared).

## 23.5 Carrier Source Polarity Select

The signal provided from any selected input source for the carrier high and carrier low signals can be inverted. Inverting the signal for the carrier high source is enabled by setting the MDCHPOL bit of the MDCARH register. Inverting the signal for the carrier low source is enabled by setting the MDCLPOL bit of the MDCARL register.

## 23.6 Carrier Source Pin Disable

Some peripherals assert control over their corresponding output pin when they are enabled. For example, when the CCP1 module is enabled, the output of CCP1 is connected to the CCP1 pin.

This default connection to a pin can be disabled by setting the MDCHODIS bit in the MDCARH register for the carrier high source and the MDCLODIS bit in the MDCARL register for the carrier low source.

## 23.7 Programmable Modulator Data

The MDBIT of the MDCON register can be selected as the source for the modulator signal. This gives the user the ability to program the value used for modulation.

## 23.8 Modulator Source Pin Disable

The modulator source default connection to a pin can be disabled by setting the MDMSODIS bit in the MDSRC register.

## 23.9 Modulated Output Polarity

The modulated output signal provided on the MDOUT pin can also be inverted. Inverting the modulated output signal is enabled by setting the MDOPOL bit of the MDCON register.

## 23.10 Slew Rate Control

The slew rate limitation on the output port pin can be disabled. The slew rate limitation can be removed by clearing the MDSLR bit in the MDCON register.

## 23.11 Operation in Sleep Mode

The DSM module is not affected by Sleep mode. The DSM can still operate during Sleep, if the Carrier and Modulator input sources are also still operable during Sleep.

## 23.12 Effects of a Reset

Upon any device Reset, the data signal modulator module is disabled. The user's firmware is responsible for initializing the module before enabling the output. The registers are reset to their default values.

#### 24.2.5 COMPARE DURING SLEEP

The Compare mode is dependent upon the system clock (Fosc) for proper operation. Since Fosc is shut down during Sleep mode, the Compare mode will not function properly during Sleep.

#### 24.2.6 ALTERNATE PIN LOCATIONS

This module incorporates I/O pins that can be moved to other locations with the use of the alternate pin function registers, APFCON0 and APFCON1. To determine which pins can be moved and what their default locations are upon a reset, see **Section 12.1 "Alternate Pin Function"** for more information.

| Name                | Bit 7                                                                       | Bit 6               | Bit 5        | Bit 4                 | Bit 3                  | Bit 2  | Bit 1  | Bit 0                 | Register<br>on Page |

|---------------------|-----------------------------------------------------------------------------|---------------------|--------------|-----------------------|------------------------|--------|--------|-----------------------|---------------------|

| APFCON0             | RXDTSEL                                                                     | SDO1SEL             | SS1SEL       | P2BSEL <sup>(2)</sup> | CCP2SEL <sup>(2)</sup> | P1DSEL | P1CSEL | CCP1SEL               | 119                 |

| CCPxCON             | PxM1 <sup>(1)</sup>                                                         | PxM0 <sup>(1)</sup> | DCxB1        | DCxB0                 | CCPxM3                 | CCPxM2 | CCPxM1 | CCPxM0                | 226                 |

| CCPRxL              | Capture/Cor                                                                 | mpare/PWM           | Register x L | ow Byte (LSE          | 3)                     |        |        |                       | 204*                |

| CCPRxH              | Capture/Cor                                                                 | mpare/PWM           | Register x H | igh Byte (MS          | B)                     |        |        |                       | 204*                |

| CM1CON0             | C10N                                                                        | C1OUT               | C10E         | C1POL                 | —                      | C1SP   | C1HYS  | C1SYNC                | 170                 |

| CM1CON1             | C1INTP                                                                      | C1INTN              | C1PCH1       | C1PCH0                | —                      | _      | C1NCH1 | C1NCH0                | 171                 |

| CM2CON0             | C2ON                                                                        | C2OUT               | C2OE         | C2POL                 | —                      | C2SP   | C2HYS  | C2SYNC                | 170                 |

| CM2CON1             | C2INTP                                                                      | C2INTN              | C2PCH1       | C2PCH0                | —                      | _      | C2NCH1 | C2NCH0                | 171                 |

| INTCON              | GIE                                                                         | PEIE                | TMR0IE       | INTE                  | IOCIE                  | TMR0IF | INTF   | IOCIF                 | 86                  |

| PIE1                | TMR1GIE                                                                     | ADIE                | RCIE         | TXIE                  | SSPIE                  | CCP1IE | TMR2IE | TMR1IE                | 87                  |

| PIE2                | OSFIE                                                                       | C2IE                | C1IE         | EEIE                  | BCL1IE                 | _      | _      | CCP2IE <sup>(2)</sup> | 88                  |

| PIE3 <sup>(2)</sup> | —                                                                           | _                   | CCP4IE       | CCP3IE                | TMR6IE                 |        | TMR4IE | —                     | 89                  |

| PIR1                | TMR1GIF                                                                     | ADIF                | RCIF         | TXIF                  | SSPIF                  | CCP1IF | TMR2IF | TMR1IF                | 91                  |

| PIR2                | OSFIF                                                                       | C2IF                | C1IF         | EEIF                  | BCLIF                  |        |        | CCP2IF <sup>(2)</sup> | 92                  |

| PIR3 <sup>(2)</sup> | _                                                                           | _                   | CCP4IF       | CCP3IF                | TMR6IF                 | _      | TMR4IF | _                     | 93                  |

| T1CON               | TMR1CS1                                                                     | TMR1CS0             | T1CKPS1      | T1CKPS0               | T1OSCEN                | T1SYNC | _      | TMR10N                | 185                 |

| T1GCON              | TMR1GE                                                                      | T1GPOL              | T1GTM        | T1GSPM                | T1GGO/DONE             | T1GVAL | T1GSS1 | T1GSS0                | 186                 |

| TMR1L               | Holding Register for the Least Significant Byte of the 16-bit TMR1 Register |                     |              |                       |                        |        | 177*   |                       |                     |

| TMR1H               | Holding Register for the Most Significant Byte of the 16-bit TMR1 Register  |                     |              |                       |                        |        | 177*   |                       |                     |

| TRISA               | TRISA7                                                                      | TRISA6              | TRISA5       | TRISA4                | TRISA3                 | TRISA2 | TRISA1 | TRISA0                | 122                 |

| TRISB               | TRISB7                                                                      | TRISB6              | TRISB5       | TRISB4                | TRISB3                 | TRISB2 | TRISB1 | TRISB0                | 127                 |

#### TABLE 24-4: SUMMARY OF REGISTERS ASSOCIATED WITH COMPARE

Legend: — = Unimplemented locations, read as '0'. Shaded cells are not used by Compare mode.

\* Page provides register information.

**Note 1:** Applies to ECCP modules only.

2: PIC16(L)F1827 only.

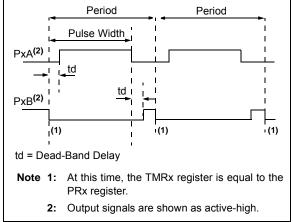

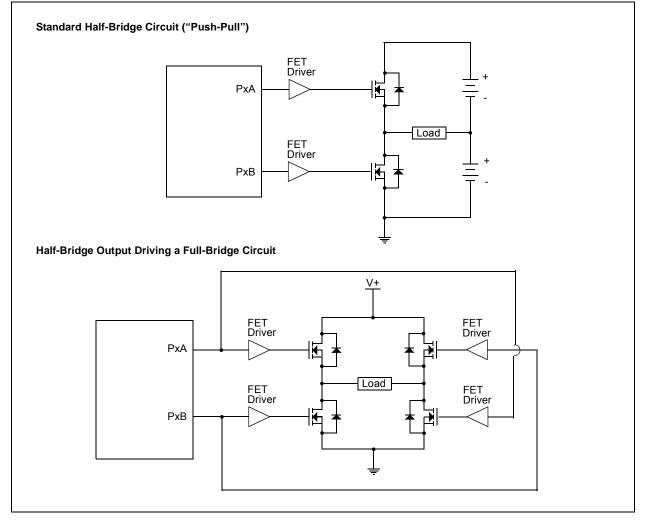

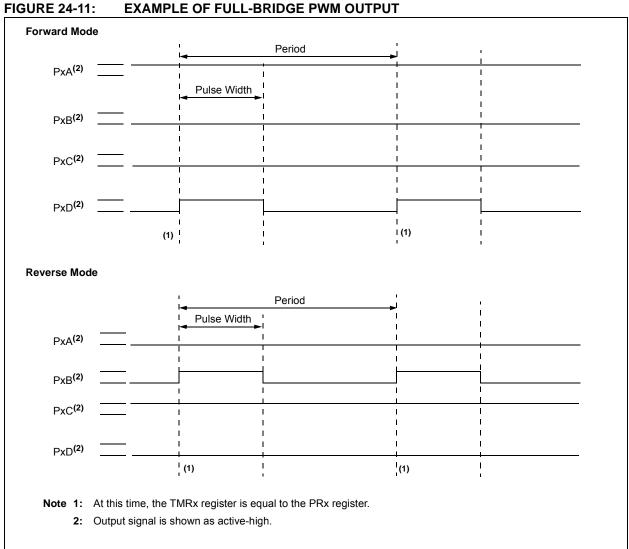

#### 24.4.1 HALF-BRIDGE MODE

In Half-Bridge mode, two pins are used as outputs to drive push-pull loads. The PWM output signal is output on the CCPx/PxA pin, while the complementary PWM output signal is output on the PxB pin (see Figure 24-9). This mode can be used for Half-Bridge applications, as shown in Figure 24-9, or for Full-Bridge applications, where four power switches are being modulated with two PWM signals.

In Half-Bridge mode, the programmable dead-band delay can be used to prevent shoot-through current in Half-Bridge power devices. The value of the PDC<6:0> bits of the PWMxCON register sets the number of instruction cycles before the output is driven active. If the value is greater than the duty cycle, the corresponding output remains inactive during the entire cycle. See **Section 24.4.5 "Programmable Dead-Band Delay Mode"** for more details of the dead-band delay operations. Since the PxA and PxB outputs are multiplexed with the PORT data latches, the associated TRIS bits must be cleared to configure PxA and PxB as outputs.

## FIGURE 24-8: EXAMPLE OF HALF-BRIDGE PWM OUTPUT

## FIGURE 24-9: EXAMPLE OF HALF-BRIDGE APPLICATIONS

FIGURE 24-11:

| R/W-0/0                                                                                       | R/W-0/0                                                                                         | R/W-0/0           | R/W-0/0       | R/W-0/0            | R/W-0/0              | R/W-0/0        | R/W-0/0      |

|-----------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|-------------------|---------------|--------------------|----------------------|----------------|--------------|

| PxRSEN                                                                                        | 1                                                                                               |                   |               | PxDC<6:0>          |                      |                |              |

| bit 7                                                                                         |                                                                                                 |                   |               |                    |                      |                | bit 0        |

|                                                                                               |                                                                                                 |                   |               |                    |                      |                |              |

| Legend:                                                                                       |                                                                                                 |                   |               |                    |                      |                |              |

| R = Readable bit W = Writable bit                                                             |                                                                                                 |                   | bit           | U = Unimplen       | nented bit, read     | d as '0'       |              |

| u = Bit is ur                                                                                 | nchanged                                                                                        | x = Bit is unkr   | nown          | -n/n = Value a     | t POR and BC         | R/Value at all | other Resets |

| '1' = Bit is s                                                                                | et                                                                                              | '0' = Bit is cle  | ared          |                    |                      |                |              |

|                                                                                               |                                                                                                 |                   |               |                    |                      |                |              |

| bit 7                                                                                         | PxRSEN: P                                                                                       | WM Restart Ena    | able bit      |                    |                      |                |              |

|                                                                                               | 1 = Upon auto-shutdown, the CCPxASE bit clears automatically once the shutdown event goes away; |                   |               |                    |                      |                |              |

|                                                                                               | the PWM restarts automatically                                                                  |                   |               |                    |                      |                |              |

|                                                                                               | 0 = Upon auto-shutdown, CCPxASE must be cleared in software to restart the PWM                  |                   |               |                    |                      |                |              |

| bit 6-0                                                                                       | PxDC<6:0>: PWM Delay Count bits                                                                 |                   |               |                    |                      |                |              |

| PxDCx =Number of Fosc/4 (4 * Tosc) cycles between the scheduled time when a PWM signal should |                                                                                                 |                   |               |                    | signal <b>should</b> |                |              |

|                                                                                               | tra                                                                                             | ansition active a | nd the actual | time it transition | s active             |                |              |

|                                                                                               |                                                                                                 |                   |               |                    |                      |                |              |

#### REGISTER 24-4: PWMxCON: ENHANCED PWM CONTROL REGISTER

**Note 1:** Bit resets to '0' with Two-Speed Start-up and LP, XT or HS selected as the Oscillator mode or Fail-Safe mode is enabled.

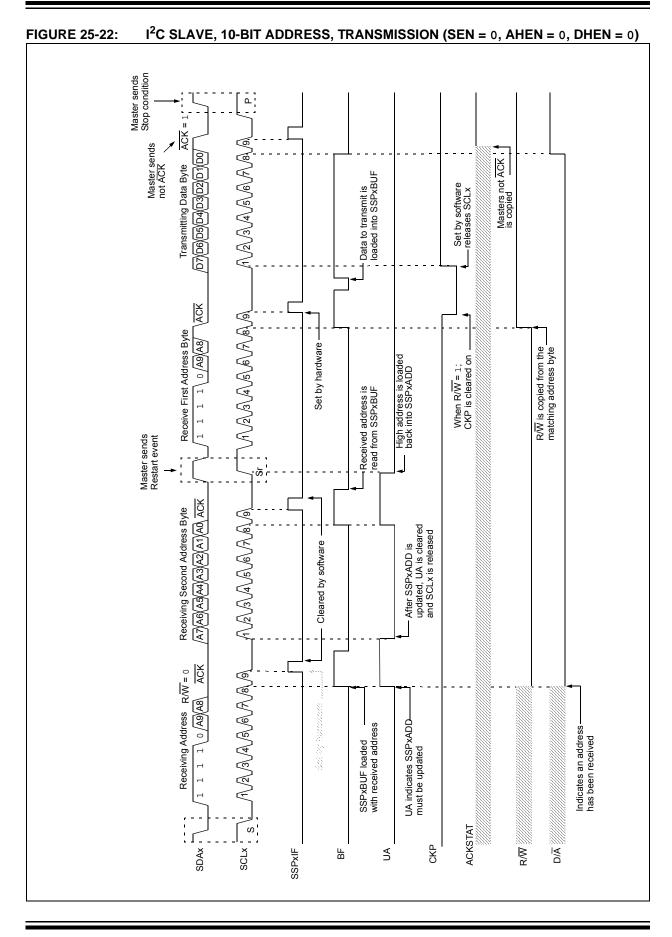

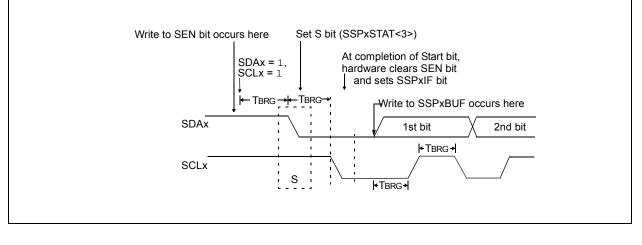

#### 25.6.4 I<sup>2</sup>C MASTER MODE START CONDITION TIMING

To initiate a Start condition, the user sets the Start Enable bit, SEN bit of the SSPxCON2 register. If the SDAx and SCLx pins are sampled high, the Baud Rate Generator is reloaded with the contents of SSPxADD<7:0> and starts its count. If SCLx and SDAx are both sampled high when the Baud Rate Generator times out (TBRG), the SDAx pin is driven low. The action of the SDAx being driven low while SCLx is high is the Start condition and causes the S bit of the SSPxSTAT1 register to be set. Following this, the Baud Rate Generator is reloaded with the contents of SSPxADD<7:0> and resumes its count. When the Baud Rate Generator times out (TBRG), the SEN bit of the SSPxCON2 register will be automatically cleared

#### FIGURE 25-26: FIRST START BIT TIMING

by hardware; the Baud Rate Generator is suspended, leaving the SDAx line held low and the Start condition is complete.

- Note 1: If at the beginning of the Start condition, the SDAx and SCLx pins are already sampled low, or if during the Start condition, the SCLx line is sampled low before the SDAx line is driven low, a bus collision occurs, the Bus Collision Interrupt Flag, BCLxIF, is set, the Start condition is aborted and the I<sup>2</sup>C module is reset into its Idle state.

- **2:** The Philips I<sup>2</sup>C Specification states that a bus collision cannot occur on a Start.

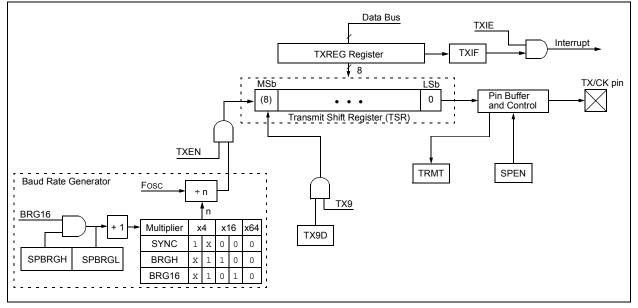

## 26.0 ENHANCED UNIVERSAL SYNCHRONOUS ASYNCHRONOUS RECEIVER TRANSMITTER (EUSART)

The Enhanced Universal Synchronous Asynchronous Receiver Transmitter (EUSART) module is a serial I/O communications peripheral. It contains all the clock generators, shift registers and data buffers necessary to perform an input or output serial data transfer independent of device program execution. The EUSART, also known as a Serial Communications Interface (SCI), can be configured as a full-duplex asynchronous system or half-duplex synchronous system. Full-Duplex mode is useful for communications with peripheral systems, such as CRT terminals and personal computers. Half-Duplex Synchronous mode is intended for communications with peripheral devices, such as A/D or D/A integrated circuits, serial EEPROMs or other microcontrollers. These devices typically do not have internal clocks for baud rate generation and require the external clock signal provided by a master synchronous device.

The EUSART module includes the following capabilities:

- · Full-duplex asynchronous transmit and receive

- Two-character input buffer

- One-character output buffer

- · Programmable 8-bit or 9-bit character length

- · Address detection in 9-bit mode

- · Input buffer overrun error detection

- Received character framing error detection

- Half-duplex synchronous master

- · Half-duplex synchronous slave

- Programmable clock polarity in synchronous modes

- Sleep operation

The EUSART module implements the following additional features, making it ideally suited for use in Local Interconnect Network (LIN) bus systems:

- · Automatic detection and calibration of the baud rate

- Wake-up on Break reception

- 13-bit Break character transmit

Block diagrams of the EUSART transmitter and receiver are shown in Figure 26-1 and Figure 26-2.

#### FIGURE 26-1: EUSART TRANSMIT BLOCK DIAGRAM

## 27.1 Analog MUX

The capacitive sensing module can monitor up to 12 inputs. The capacitive sensing inputs are defined as CPS<11:0>. To determine if a frequency change has occurred the user must:

- Select the appropriate CPS pin by setting the CPSCH<3:0> bits of the CPSCON1 register

- · Set the corresponding ANSEL bit

- · Set the corresponding TRIS bit

- · Run the software algorithm

Selection of the CPSx pin while the module is enabled will cause the capacitive sensing oscillator to be on the CPSx pin. Failure to set the corresponding ANSEL and TRIS bits can cause the capacitive sensing oscillator to stop, leading to false frequency readings.

## 27.2 Capacitive Sensing Oscillator

The capacitive sensing oscillator consists of a constant current source and a constant current sink, to produce a triangle waveform. The CPSOUT bit of the CPSCON0 register shows the status of the capacitive sensing oscillator, whether it is a sinking or sourcing current. The oscillator is designed to drive a capacitive load (single PCB pad) and at the same time, be a clock source to either Timer0 or Timer1. The oscillator has three different current settings as defined by CPSRNG<1:0> of the CPSCON0 register. The different current settings for the oscillator serve two purposes:

- Maximize the number of counts in a timer for a fixed time base

- Maximize the count differential in the timer during a change in frequency

#### 27.3 Timer resources

To measure the change in frequency of the capacitive sensing oscillator, a fixed time base is required. For the period of the fixed time base, the capacitive sensing oscillator is used to clock either Timer0 or Timer1. The frequency of the capacitive sensing oscillator is equal to the number of counts in the timer divided by the period of the fixed time base.

## 27.4 Fixed Time Base

To measure the frequency of the capacitive sensing oscillator, a fixed time base is required. Any timer resource or software loop can be used to establish the fixed time base. It is up to the end user to determine the method in which the fixed time base is generated.

**Note:** The fixed time base can not be generated by the timer resource that the capacitive sensing oscillator is clocking.

#### 27.4.1 TIMER0

To select Timer0 as the timer resource for the capacitive sensing module:

- Set the T0XCS bit of the CPSCON0 register

- · Clear the TMR0CS bit of the OPTION register

When Timer0 is chosen as the timer resource, the capacitive sensing oscillator will be the clock source for Timer0. Refer to **Section 20.0** "**Timer0 Module**" for additional information.

#### 27.4.2 TIMER1

To select Timer1 as the timer resource for the capacitive sensing module, set the TMR1CS<1:0> of the T1CON register to '11'. When Timer1 is chosen as the timer resource, the capacitive sensing oscillator will be the clock source for Timer1. Because the Timer1 module has a gate control, developing a time base for the frequency measurement can be simplified by using the Timer0 overflow flag.

It is recommend that the Timer0 overflow flag, in conjunction with the Toggle mode of the Timer1 gate, be used to develop the fixed time base required by the software portion of the capacitive sensing module. Refer to **Section 21.6.3 "Timer1 Gate Toggle Mode"** for additional information.

| TABLE 27-1: | TIMER1 ENABLE FUNCTION |

|-------------|------------------------|

|-------------|------------------------|

| TMR10N | TMR1GE | Timer1 Operation       |

|--------|--------|------------------------|

| 0      | 0      | Off                    |

| 0      | 1      | Off                    |

| 1      | 0      | On                     |

| 1      | 1      | Count Enabled by input |

### 28.2 Low-Voltage Programming Entry Mode

The Low-Voltage Programming Entry mode allows the PIC16(L)F1826/27 devices to be programmed using VDD only, without high voltage. When the LVP bit of Configuration Word 2 is set to '1', the low-voltage ICSP programming entry is enabled. To disable the Low-Voltage ICSP mode, the LVP bit must be programmed to '0'.

Entry into the Low-Voltage Programming Entry mode requires the following steps:

- 1.  $\overline{\text{MCLR}}$  is brought to VIL.

- 2. A 32-bit key sequence is presented on ICSPDAT, while clocking ICSPCLK.

Once the key sequence is complete,  $\overline{\text{MCLR}}$  must be held at VIL for as long as Program/Verify mode is to be maintained.

If low-voltage programming is enabled (LVP = 1), the  $\overline{\text{MCLR}}$  Reset function is automatically enabled and cannot be disabled. See **Section 7.3 "MCLR"** for more information.

The LVP bit can only be reprogrammed to '0' by using the High-Voltage Programming mode.

## 28.3 Common Programming Interfaces

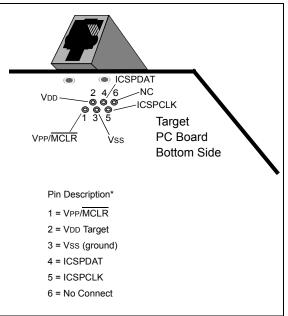

Connection to a target device is typically done through an ICSP<sup>™</sup> header. A commonly found connector on development tools is the RJ-11 in the 6P6C (6 pin, 6 connector) configuration. See Figure 28-2.

#### FIGURE 28-2: ICD RJ-11 STYLE CONNECTOR INTERFACE

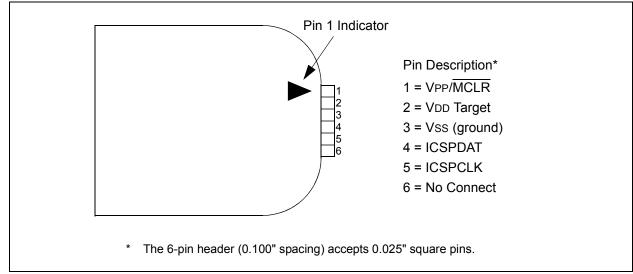

Another connector often found in use with the PICkit<sup>™</sup> programmers is a standard 6-pin header with 0.1 inch spacing. Refer to Figure 28-3.

#### FIGURE 28-3: PICkit<sup>™</sup> STYLE CONNECTOR INTERFACE

| SWAPF            | Swap Nibbles in f                                                                                                                                                                 |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:          | [ label ] SWAPF f,d                                                                                                                                                               |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                                 |  |  |  |

| Operation:       | $(f<3:0>) \rightarrow (destination<7:4>),$<br>$(f<7:4>) \rightarrow (destination<3:0>)$                                                                                           |  |  |  |

| Status Affected: | None                                                                                                                                                                              |  |  |  |

| Description:     | The upper and lower nibbles of regis-<br>ter 'f' are exchanged. If 'd' is '0', the<br>result is placed in the W register. If 'd'<br>is '1', the result is placed in register 'f'. |  |  |  |

| XORLW            | Exclusive OR literal with W                                                                                                |  |  |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [label] XORLW k                                                                                                            |  |  |  |  |

| Operands:        | $0 \le k \le 255$                                                                                                          |  |  |  |  |

| Operation:       | (W) .XOR. $k \rightarrow (W)$                                                                                              |  |  |  |  |

| Status Affected: | Z                                                                                                                          |  |  |  |  |

| Description:     | The contents of the W register are<br>XOR'ed with the eight-bit<br>literal 'k'. The result is placed in the<br>W register. |  |  |  |  |

| TRIS                    | Load TRIS Register with W                                                                                       | XORWF            | Exclusive OR W with f                                                                                                                                                           |

|-------------------------|-----------------------------------------------------------------------------------------------------------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:                 | [ label ] TRIS f                                                                                                | Syntax:          | [ <i>label</i> ] XORWF f,d                                                                                                                                                      |

| Operands:<br>Operation: | $5 \le f \le 7$<br>(W) $\rightarrow$ TRIS register 'f'                                                          | Operands:        | $0 \le f \le 127$<br>d $\in [0,1]$                                                                                                                                              |

| Status Affected:        | None $(W) \rightarrow TRIS register T$                                                                          | Operation:       | (W) .XOR. (f) $\rightarrow$ (destination)                                                                                                                                       |

| Description:            | Move data from W register to TRIS                                                                               | Status Affected: | Z                                                                                                                                                                               |

|                         | register.<br>When 'f' = 5, TRISA is loaded.<br>When 'f' = 6, TRISB is loaded.<br>When 'f' = 7, TRISC is loaded. | Description:     | Exclusive OR the contents of the W register with register 'f'. If 'd' is '0', the result is stored in the W register. If 'd' is '1', the result is stored back in register 'f'. |

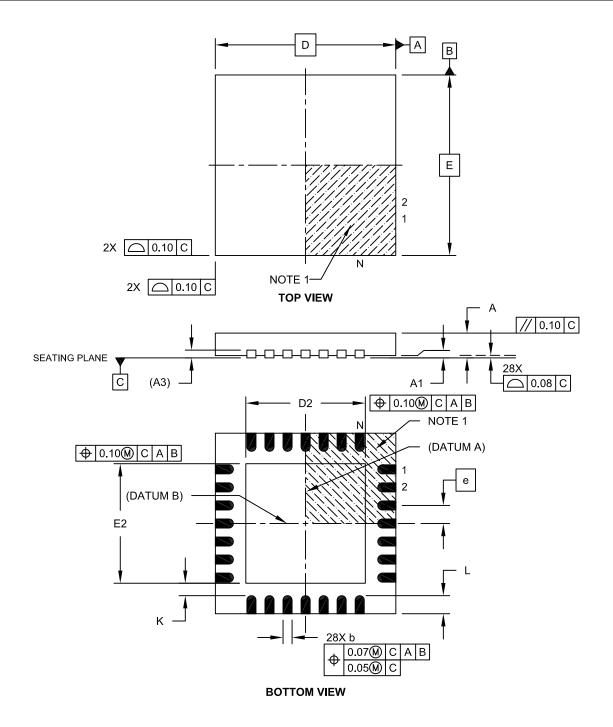

28-Lead Plastic Ultra Thin Quad Flat, No Lead Package (MV) – 4x4x0.5 mm Body [UQFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-152A Sheet 1 of 2