#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 32MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 16                                                                        |

| Program Memory Size        | 7KB (4K x 14)                                                             |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 256 x 8                                                                   |

| RAM Size                   | 384 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                               |

| Data Converters            | A/D 12x10b                                                                |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

| Mounting Type              | Through Hole                                                              |

| Package / Case             | 18-DIP (0.300", 7.62mm)                                                   |

| Supplier Device Package    | 18-PDIP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1827-e-p |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **TABLE 1-2:** PIC16(L)F1826/27 PINOUT DESCRIPTION (CONTINUED)

| Name                                                                                                      | Function | Input<br>Type     | Output<br>Type | Description                                                                                        |

|-----------------------------------------------------------------------------------------------------------|----------|-------------------|----------------|----------------------------------------------------------------------------------------------------|

| RA6/OSC2/CLKOUT/CLKR/                                                                                     | RA6      | TTL               | CMOS           | General purpose I/O.                                                                               |

| P1D <sup>(1)</sup> /P2B <sup>(1,2)</sup> /SDO1 <sup>(1)</sup>                                             | OSC2     | —                 | XTAL           | Crystal/Resonator (LP, XT, HS modes).                                                              |

|                                                                                                           | CLKOUT   | _                 | CMOS           | Fosc/4 output.                                                                                     |

|                                                                                                           | CLKR     | —                 | CMOS           | Clock Reference Output.                                                                            |

|                                                                                                           | P1D      | —                 | CMOS           | PWM output.                                                                                        |

|                                                                                                           | P2B      | —                 | CMOS           | PWM output.                                                                                        |

|                                                                                                           | SDO1     | —                 | CMOS           | SPI data output 1.                                                                                 |

| RA7/OSC1/CLKIN/P1C <sup>(1)</sup> /                                                                       | RA7      | TTL               | CMOS           | General purpose I/O.                                                                               |

| CCP2 <sup>(1,2)</sup> /P2A <sup>(1,2)</sup>                                                               | OSC1     | XTAL              | _              | Crystal/Resonator (LP, XT, HS modes).                                                              |

|                                                                                                           | CLKIN    | CMOS              | —              | External clock input (EC mode).                                                                    |

|                                                                                                           | P1C      | —                 | CMOS           | PWM output.                                                                                        |

|                                                                                                           | CCP2     | ST                | CMOS           | Capture/Compare/PWM2.                                                                              |

|                                                                                                           | P2A      | —                 | CMOS           | PWM output.                                                                                        |

| RB0/T1G/CCP1 <sup>(1)</sup> /P1A <sup>(1)</sup> /INT/<br>SRI/FLT0                                         | RB0      | TTL               | CMOS           | General purpose I/O. Individually controlled interrupt-on-change.<br>Individually enabled pull-up. |

|                                                                                                           | T1G      | ST                | _              | Timer1 Gate input.                                                                                 |

|                                                                                                           | CCP1     | ST                | CMOS           | Capture/Compare/PWM1.                                                                              |

|                                                                                                           | P1A      | _                 | CMOS           | PWM output.                                                                                        |

|                                                                                                           | INT      | ST                | —              | External interrupt.                                                                                |

|                                                                                                           | SRI      | ST                |                | SR latch input.                                                                                    |

|                                                                                                           | FLT0     | ST                |                | ECCP Auto-Shutdown Fault input.                                                                    |

| RB1/AN11/CPS11/RX <sup>(1,3)</sup> /<br>DT <sup>(1,3)</sup> /SDA1/SDI1                                    | RB1      | TTL               | CMOS           | General purpose I/O. Individually controlled interrupt-on-change.<br>Individually enabled pull-up. |

|                                                                                                           | AN11     | AN                |                | A/D Channel 11 input.                                                                              |

|                                                                                                           | CPS11    | AN                |                | Capacitive sensing input 11.                                                                       |

|                                                                                                           | RX       | ST                |                | USART asynchronous input.                                                                          |

|                                                                                                           | DT       | ST                | CMOS           | USART synchronous data.                                                                            |

|                                                                                                           | SDA1     | I <sup>2</sup> C™ | OD             | I <sup>2</sup> C™ data input/output 1.                                                             |

|                                                                                                           | SDI1     | CMOS              |                | SPI data input 1.                                                                                  |

| RB2/AN10/CPS10/MDMIN/<br>TX <sup>(1,3)</sup> /CK <sup>(1,3)</sup> /RX <sup>(1)</sup> /DT <sup>(1)</sup> / | RB2      | TTL               | CMOS           | General purpose I/O. Individually controlled interrupt-on-change.<br>Individually enabled pull-up. |

| SDA2 <sup>(2)</sup> /SDI2 <sup>(2)</sup> /SDO1 <sup>(1,3)</sup>                                           | AN10     | AN                |                | A/D Channel 10 input.                                                                              |

|                                                                                                           | CPS10    | AN                |                | Capacitive sensing input 10.                                                                       |

|                                                                                                           | MDMIN    | _                 | CMOS           | Modulator source input.                                                                            |

|                                                                                                           | TX       | _                 | CMOS           | USART asynchronous transmit.                                                                       |

|                                                                                                           | СК       | ST                | CMOS           | USART synchronous clock.                                                                           |

|                                                                                                           | RX       | ST                | —              | USART asynchronous input.                                                                          |

|                                                                                                           | DT       | ST                | CMOS           | USART synchronous data.                                                                            |

|                                                                                                           | SDA2     | I <sup>2</sup> C™ | OD             | I <sup>2</sup> C™ data input/output 2.                                                             |

|                                                                                                           |          |                   |                |                                                                                                    |

|                                                                                                           | SDI2     | ST                | _              | SPI data input 2.                                                                                  |

Legend: AN = Analog input or output CMOS = CMOS compatible input or output

OD = Open Drain

TTL = TTL compatible input ST = Schmitt Trigger input with CMOS levels  $I^2C^{TM}$  = Schmitt Trigger input with  $I^2C$ HV = High Voltage XTAL = Crystal

levels

Note 1: Pin functions can be moved using the APFCON0 or APFCON1 register.

2: Functions are only available on the PIC16(L)F1827.

3: Default function location.

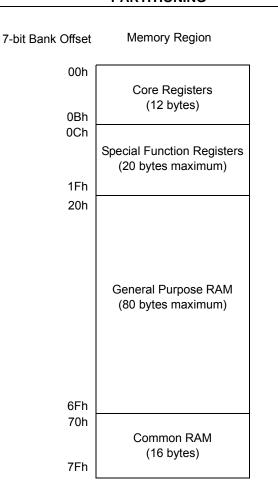

#### 3.2.2 SPECIAL FUNCTION REGISTER

The Special Function Registers are registers used by the application to control the desired operation of peripheral functions in the device. The Special Function Registers occupy the 20 bytes after the core registers of every data memory bank (addresses x0Ch/x8Ch through x1Fh/x9Fh). The registers associated with the operation of the peripherals are described in the appropriate peripheral chapter of this data sheet.

#### 3.2.3 GENERAL PURPOSE RAM

There are up to 80 bytes of GPR in each data memory bank. The Special Function Registers occupy the 20 bytes after the core registers of every data memory bank (addresses x0Ch/x8Ch through x1Fh/x9Fh).

#### 3.2.3.1 Linear Access to GPR

The general purpose RAM can be accessed in a non-banked method via the FSRs. This can simplify access to large memory structures. See **Section 3.5.2** "Linear Data Memory" for more information.

#### 3.2.4 COMMON RAM

There are 16 bytes of common RAM accessible from all banks.

#### FIGURE 3-3: BANKED MEMORY PARTITIONING

#### 3.2.5 DEVICE MEMORY MAPS

The memory maps for the device family are as shown in Table 3-3 and Table 3-4.

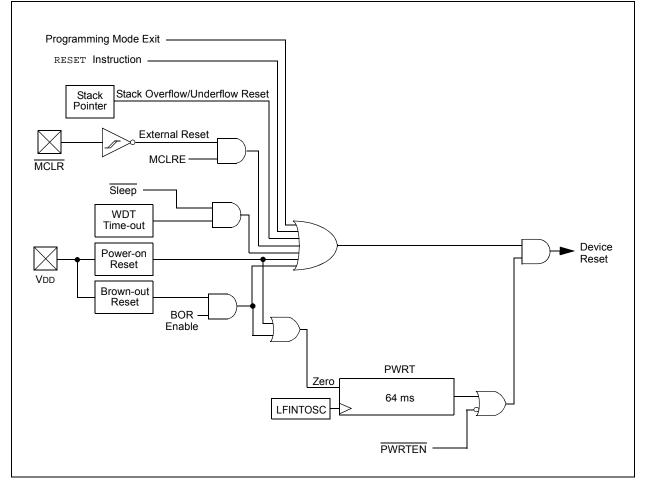

### 7.0 RESETS

There are multiple ways to reset this device:

- Power-on Reset (POR)

- Brown-out Reset (BOR)

- MCLR Reset

- WDT Reset

- RESET instruction

- Stack Overflow

- Stack Underflow

- Programming mode exit

To allow VDD to stabilize, an optional power-up timer can be enabled to extend the Reset time after a BOR or POR event.

A simplified block diagram of the On-Chip Reset Circuit is shown in Figure 7-1.

#### FIGURE 7-1: SIMPLIFIED BLOCK DIAGRAM OF ON-CHIP RESET CIRCUIT

#### 8.6.7 PIR2 REGISTER

The PIR2 register contains the interrupt flag bits, as shown in Register 8-7.

Note: Interrupt flag bits are set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the Global Enable bit, GIE, of the INTCON register. User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

#### REGISTER 8-7: PIR2: PERIPHERAL INTERRUPT REQUEST REGISTER 2

| <b>B</b> # 4 / 6 / 6 | <b>B</b> 4 4 4 6 4 5 | B 8 4 / 6 / 5             | B 4 4 4 6 15         | B 4 4 4 4      |                  |                | <b>B</b> 444 6 / 5    |

|----------------------|----------------------|---------------------------|----------------------|----------------|------------------|----------------|-----------------------|

| R/W-0/0              | R/W-0/0              | R/W-0/0                   | R/W-0/0              | R/W-0/0        | U-0              | U-0            | R/W-0/0               |

| OSFIF                | C2IF                 | C1IF                      | EEIF                 | BCL1IF         | —                | <u> </u>       | CCP2IF <sup>(1)</sup> |

| bit 7                |                      |                           |                      |                |                  |                | bit C                 |

|                      |                      |                           |                      |                |                  |                |                       |

| Legend:              |                      |                           |                      |                |                  |                |                       |

| R = Readable         | bit                  | W = Writable              | bit                  | U = Unimpler   | mented bit, read | as '0'         |                       |

| u = Bit is unch      | anged                | x = Bit is unkr           | nown                 | -n/n = Value a | at POR and BO    | R/Value at all | other Resets          |

| '1' = Bit is set     |                      | '0' = Bit is cle          | ared                 |                |                  |                |                       |

|                      |                      |                           |                      |                |                  |                |                       |

| bit 7                | <b>OSFIF:</b> Oscil  | llator Fail Interru       | upt Flag bit         |                |                  |                |                       |

|                      | 1 = Interrupt        | 1 0                       |                      |                |                  |                |                       |

|                      | 0 = Interrupt        | is not pending            |                      |                |                  |                |                       |

| bit 6                | C2IF: Compa          | arator C2 Interru         | upt Flag bit         |                |                  |                |                       |

|                      | 1 = Interrupt        |                           |                      |                |                  |                |                       |

|                      | -                    | is not pending            |                      |                |                  |                |                       |

| bit 5                |                      | arator C1 Interru         | upt Flag bit         |                |                  |                |                       |

|                      | 1 = Interrupt        | is penaing is not pending |                      |                |                  |                |                       |

| bit 4                |                      | OM Write Com              | letion Interru       | nt Flag bit    |                  |                |                       |

|                      | 1 = Interrupt        |                           |                      | pt i lag bit   |                  |                |                       |

|                      |                      | is not pending            |                      |                |                  |                |                       |

| bit 3                | BCL1IF: MS           | SP1 Bus Collisi           | on Interrupt F       | lag bit        |                  |                |                       |

|                      | 1 = Interrupt        | is pending                |                      | •              |                  |                |                       |

|                      | 0 = Interrupt        | is not pending            |                      |                |                  |                |                       |

| bit 2-1              | Unimplemer           | nted: Read as '           | 0'                   |                |                  |                |                       |

| bit 0                | CCP2IF: CC           | P2 Interrupt Fla          | g bit <sup>(1)</sup> |                |                  |                |                       |

|                      | 1 = Interrupt        |                           |                      |                |                  |                |                       |

|                      | 0 = Interrupt        | is not pending            |                      |                |                  |                |                       |

Note 1: PIC16(L)F1827 only.

NOTES:

NOTES:

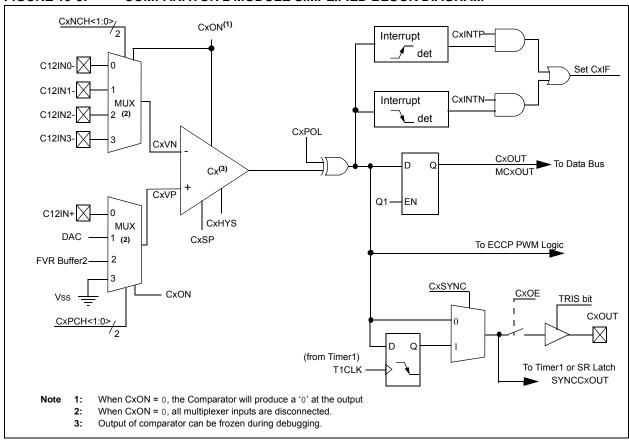

#### FIGURE 19-3: COMPARATOR 2 MODULE SIMPLIFIED BLOCK DIAGRAM

| Name    | Bit 7  | Bit 6  | Bit 5    | Bit 4    | Bit 3   | Bit 2   | Bit 1  | Bit 0                 | Register<br>on Page |

|---------|--------|--------|----------|----------|---------|---------|--------|-----------------------|---------------------|

| ANSELA  | _      | _      | —        | ANSA4    | ANSA3   | ANSA2   | ANSA1  | ANSA0                 | 123                 |

| CMxCON0 | CxON   | CxOUT  | CxOE     | CxPOL    | _       | CxSP    | CxHYS  | CxSYNC                | 170                 |

| CMxCON1 | CxNTP  | CxINTN | CxPCH1   | CxPCH0   | —       | —       | CxNCH1 | CxNCH0                | 171                 |

| CMOUT   | _      | _      | _        | —        | —       | —       | MC2OUT | MC10UT                | 171                 |

| DACCON0 | DACEN  | DACLPS | DACOE    | _        | DACPSS1 | DACPSS0 | _      | DACNSS                | 156                 |

| DACCON1 | _      | —      | _        | DACR4    | DACR3   | DACR2   | DACR1  | DACR0                 | 156                 |

| FVRCON  | FVREN  | FVRRDY | Reserved | Reserved | CDAFVR1 | CDAFVR0 | ADFVR1 | ADFVR0                | 136                 |

| INTCON  | GIE    | PEIE   | TMR0IE   | INTE     | IOCIE   | TMR0IF  | INTF   | IOCIF                 | 86                  |

| LATA    | LATA7  | LATA6  | _        | LATA4    | LATA3   | LATA2   | LATA1  | LATA0                 | 122                 |

| PIE2    | OSFIE  | C2IE   | C1IE     | EEIE     | BCL1IE  | —       | _      | CCP2IE <sup>(1)</sup> | 88                  |

| PIR2    | OSFIF  | C2IF   | C1IF     | EEIF     | BCL1IF  | —       | _      | CCP2IF <sup>(1)</sup> | 92                  |

| PORTA   | RA7    | RA6    | RA5      | RA4      | RA3     | RA2     | RA1    | RA0                   | 122                 |

| TRISA   | TRISA7 | TRISA6 | TRISA5   | TRISA4   | TRISA3  | TRISA2  | TRISA1 | TRISA0                | 122                 |

#### TABLE 19-2: SUMMARY OF REGISTERS ASSOCIATED WITH COMPARATOR MODULE

Legend: — = unimplemented, read as '0'. Shaded cells are unused by the comparator module.

Note 1: PIC16(L)F1827 only.

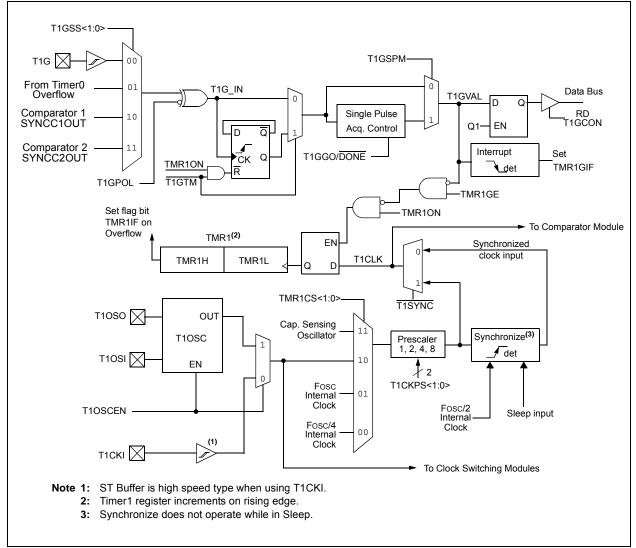

#### 21.0 TIMER1 MODULE WITH GATE CONTROL

The Timer1 module is a 16-bit timer/counter with the following features:

- 16-bit timer/counter register pair (TMR1H:TMR1L)

- Programmable internal or external clock source

- 2-bit prescaler

- · Dedicated 32 kHz oscillator circuit

- · Optionally synchronized comparator out

- Multiple Timer1 gate (count enable) sources

- · Interrupt on overflow

- Wake-up on overflow (external clock, Asynchronous mode only)

- Time base for the Capture/Compare function

- Special Event Trigger (with CCP/ECCP)

- · Selectable Gate Source Polarity

- Gate Toggle mode

- Gate Single-pulse mode

- Gate Value Status

- Gate Event Interrupt

- Figure 21-1 is a block diagram of the Timer1 module.

#### FIGURE 21-1: TIMER1 BLOCK DIAGRAM

#### 24.3.2 SETUP FOR PWM OPERATION

The following steps should be taken when configuring the CCP module for standard PWM operation:

- 1. Disable the CCPx pin output driver by setting the associated TRIS bit.

- 2. Load the PRx register with the PWM period value.

- Configure the CCP module for the PWM mode by loading the CCPxCON register with the appropriate values.

- Load the CCPRxL register and the DCxBx bits of the CCPxCON register, with the PWM duty cycle value.

- 5. Configure and start Timer2/4/6:

- •Select the Timer2/4/6 resource to be used for PWM generation by setting the CxTSEL<1:0> bits in the CCPTMRS register.

- •Clear the TMRxIF interrupt flag bit of the PIRx register. See Note below.

- •Configure the TxCKPS bits of the TxCON register with the Timer prescale value.

- •Enable the Timer by setting the TMRxON bit of the TxCON register.

- 6. Enable PWM output pin:

- •Wait until the Timer overflows and the TMRxIF bit of the PIRx register is set. See Note below.

- •Enable the CCPx pin output driver by clearing the associated TRIS bit.

- **Note:** In order to send a complete duty cycle and period on the first PWM output, the above steps must be included in the setup sequence. If it is not critical to start with a complete PWM signal on the first output, then step 6 may be ignored.

#### 24.3.3 TIMER2/4/6 TIMER RESOURCE

The PWM standard mode makes use of one of the 8-bit Timer2/4/6 timer resources to specify the PWM period.

Configuring the CxTSEL<1:0> bits in the CCPTMRS register selects which Timer2/4/6 timer is used.

#### 24.3.4 PWM PERIOD

The PWM period is specified by the PRx register of Timer2/4/6. The PWM period can be calculated using the formula of Equation 24-1.

#### EQUATION 24-1: PWM PERIOD

$PWM Period = [(PRx) + 1] \bullet 4 \bullet TOSC \bullet$ (TMRx Prescale Value)

**Note 1:** Tosc = 1/Fosc

When TMRx is equal to PRx, the following three events occur on the next increment cycle:

- TMRx is cleared

- The CCPx pin is set. (Exception: If the PWM duty cycle = 0%, the pin will not be set.)

- The PWM duty cycle is latched from CCPRxL into CCPRxH.

Note: The Timer postscaler (see Section 22.1 "Timer2/4/6 Operation") is not used in the determination of the PWM frequency.

#### 24.3.5 PWM DUTY CYCLE

The PWM duty cycle is specified by writing a 10-bit value to multiple registers: CCPRxL register and DCxB<1:0> bits of the CCPxCON register. The CCPRxL contains the eight MSbs and the DCxB<1:0> bits of the CCPxCON register contain the two LSbs. CCPRxL and DCxB<1:0> bits of the CCPxCON register can be written to at any time. The duty cycle value is not latched into CCPRxH until after the period completes (i.e., a match between PRx and TMRx registers occurs). While using the PWM, the CCPRxH register is read-only.

Equation 24-2 is used to calculate the PWM pulse width.

Equation 24-3 is used to calculate the PWM duty cycle ratio.

#### EQUATION 24-2: PULSE WIDTH

Pulse Width = (CCPRxL:CCPxCON < 5:4>) •

TOSC • (TMRx Prescale Value)

#### EQUATION 24-3: DUTY CYCLE RATIO

Duty Cycle Ratio =  $\frac{(CCPRxL:CCPxCON < 5:4>)}{4(PRx+1)}$

The CCPRxH register and a 2-bit internal latch are used to double buffer the PWM duty cycle. This double buffering is essential for glitchless PWM operation.

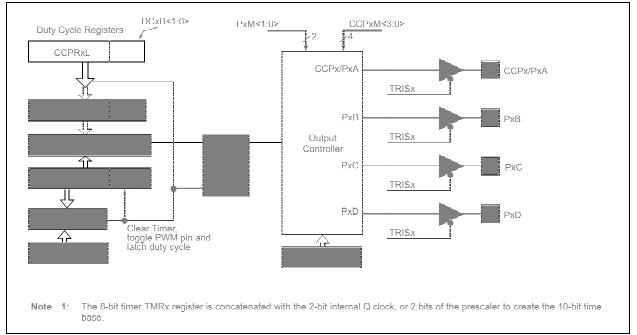

The 8-bit timer TMRx register is concatenated with either the 2-bit internal system clock (FOSC), or 2 bits of the prescaler, to create the 10-bit time base. The system clock is used if the Timer2/4/6 prescaler is set to 1:1.

When the 10-bit time base matches the CCPRxH and 2-bit latch, then the CCPx pin is cleared (see Figure 24-4).

#### 24.4 PWM (Enhanced Mode)

The enhanced PWM function described in this section is available for CCP modules ECCP1 and ECCP2, with any differences between modules noted.

The enhanced PWM mode generates a Pulse-Width Modulation (PWM) signal on up to four different output pins with up to 10 bits of resolution. The period, duty cycle, and resolution are controlled by the following registers:

- PRx registers

- TxCON registers

- · CCPRxL registers

- CCPxCON registers

The ECCP modules have the following additional PWM registers which control Auto-shutdown, Auto-restart, Dead-band Delay and PWM Steering modes:

- · CCPxAS registers

- PSTRxCON registers

- PWMxCON registers

The enhanced PWM module can generate the following five PWM Output modes:

- Single PWM

- Half-Bridge PWM

- Full-Bridge PWM, Forward Mode

- Full-Bridge PWM, Reverse Mode

- · Single PWM with PWM Steering Mode

To select an Enhanced PWM Output mode, the PxM bits of the CCPxCON register must be configured appropriately.

The PWM outputs are multiplexed with I/O pins and are designated PxA, PxB, PxC and PxD. The polarity of the PWM pins is configurable and is selected by setting the CCPxM bits in the CCPxCON register appropriately.

Figure 24-5 shows an example of a simplified block diagram of the Enhanced PWM module.

Figure 24-9 shows the pin assignments for various Enhanced PWM modes.

- Note 1: The corresponding TRIS bit must be cleared to enable the PWM output on the CCPx pin.

- 2: Clearing the CCPxCON register will relinquish control of the CCPx pin.

- **3:** Any pin not used in the enhanced PWM mode is available for alternate pin functions, if applicable.

- 4: To prevent the generation of an incomplete waveform when the PWM is first enabled, the ECCP module waits until the start of a new PWM period before generating a PWM signal.

#### FIGURE 24-5: EXAMPLE SIMPLIFIED BLOCK DIAGRAM OF THE ENHANCED PWM MODE

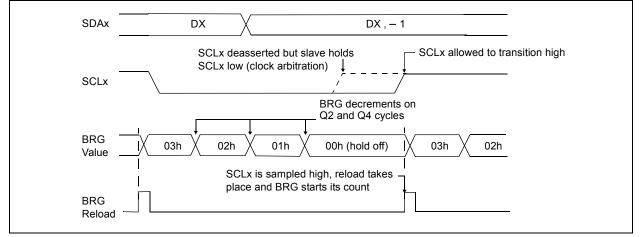

#### 25.6.2 CLOCK ARBITRATION

Clock arbitration occurs when the master, during any receive, transmit or Repeated Start/Stop condition, releases the SCLx pin (SCLx allowed to float high). When the SCLx pin is allowed to float high, the Baud Rate Generator (BRG) is suspended from counting until the SCLx pin is actually sampled high. When the SCLx pin is sampled high, the Baud Rate Generator is reloaded with the contents of SSPxADD<7:0> and begins counting. This ensures that the SCLx high time will always be at least one BRG rollover count in the event that the clock is held low by an external device (Figure 25-25).

#### 25.6.3 WCOL STATUS FLAG

If the user writes the SSPxBUF when a Start, Restart, Stop, Receive or Transmit sequence is in progress, the WCOL is set and the contents of the buffer are unchanged (the write does not occur). Any time the WCOL bit is set it indicates that an action on SSPxBUF was attempted while the module was not Idle.

| Note: | Because queueing of events is not       |

|-------|-----------------------------------------|

|       | allowed, writing to the lower 5 bits of |

|       | SSPxCON2 is disabled until the Start    |

|       | condition is complete.                  |

#### 26.4 EUSART Synchronous Mode

Synchronous serial communications are typically used in systems with a single master and one or more slaves. The master device contains the necessary circuitry for baud rate generation and supplies the clock for all devices in the system. Slave devices can take advantage of the master clock by eliminating the internal clock generation circuitry.

There are two signal lines in Synchronous mode: a bidirectional data line and a clock line. Slaves use the external clock supplied by the master to shift the serial data into and out of their respective receive and transmit shift registers. Since the data line is bidirectional, synchronous operation is half-duplex only. Half-duplex refers to the fact that master and slave devices can receive and transmit data but not both simultaneously. The EUSART can operate as either a master or slave device.

Start and Stop bits are not used in synchronous transmissions.

#### 26.4.1 SYNCHRONOUS MASTER MODE

The following bits are used to configure the EUSART for Synchronous Master operation:

- SYNC = 1

- CSRC = 1

- SREN = 0 (for transmit); SREN = 1 (for receive)

- CREN = 0 (for transmit); CREN = 1 (for receive)

- SPEN = 1

Setting the SYNC bit of the TXSTA register configures the device for synchronous operation. Setting the CSRC bit of the TXSTA register configures the device as a master. Clearing the SREN and CREN bits of the RCSTA register ensures that the device is in the Transmit mode, otherwise the device will be configured to receive. Setting the SPEN bit of the RCSTA register enables the EUSART.

#### 26.4.1.1 Master Clock

Synchronous data transfers use a separate clock line, which is synchronous with the data. A device configured as a master transmits the clock on the TX/CK line. The TX/CK pin output driver is automatically enabled when the EUSART is configured for synchronous transmit or receive operation. Serial data bits change on the leading edge to ensure they are valid at the trailing edge of each clock. One clock cycle is generated for each data bit. Only as many clock cycles are generated as there are data bits.

#### 26.4.1.2 Clock Polarity

A clock polarity option is provided for Microwire compatibility. Clock polarity is selected with the SCKP bit of the BAUDCON register. Setting the SCKP bit sets the clock Idle state as high. When the SCKP bit is set, the data changes on the falling edge of each clock. Clearing the SCKP bit sets the Idle state as low. When the SCKP bit is cleared, the data changes on the rising edge of each clock.

#### 26.4.1.3 Synchronous Master Transmission

Data is transferred out of the device on the RX/DT pin. The RX/DT and TX/CK pin output drivers are automatically enabled when the EUSART is configured for synchronous master transmit operation.

A transmission is initiated by writing a character to the TXREG register. If the TSR still contains all or part of a previous character the new character data is held in the TXREG until the last bit of the previous character has been transmitted. If this is the first character, or the previous character has been completely flushed from the TSR, the data in the TXREG is immediately transferred to the TSR. The transmission of the character commences immediately following the transfer of the data to the TSR from the TXREG.

Each data bit changes on the leading edge of the master clock and remains valid until the subsequent leading clock edge.

| Note: | The TSR register is not mapped in data      |

|-------|---------------------------------------------|

|       | memory, so it is not available to the user. |

- 26.4.1.4 Synchronous Master Transmission Set-up:

- Initialize the SPBRGH, SPBRGL register pair and the BRGH and BRG16 bits to achieve the desired baud rate (see Section 26.3 "EUSART Baud Rate Generator (BRG)").

- 2. Enable the synchronous master serial port by setting bits SYNC, SPEN and CSRC.

- 3. Disable Receive mode by clearing bits SREN and CREN.

- 4. Enable Transmit mode by setting the TXEN bit.

- 5. If 9-bit transmission is desired, set the TX9 bit.

- 6. If interrupts are desired, set the TXIE bit of the PIE1 register and the GIE and PEIE bits of the INTCON register.

- 7. If 9-bit transmission is selected, the ninth bit should be loaded in the TX9D bit.

- 8. Start transmission by loading data to the TXREG register.

#### 26.4.2 SYNCHRONOUS SLAVE MODE

The following bits are used to configure the EUSART for Synchronous slave operation:

- SYNC = 1

- CSRC = 0

- SREN = 0 (for transmit); SREN = 1 (for receive)

- CREN = 0 (for transmit); CREN = 1 (for receive)

- SPEN = 1

Setting the SYNC bit of the TXSTA register configures the device for synchronous operation. Clearing the CSRC bit of the TXSTA register configures the device as a slave. Clearing the SREN and CREN bits of the RCSTA register ensures that the device is in the Transmit mode, otherwise the device will be configured to receive. Setting the SPEN bit of the RCSTA register enables the EUSART.

#### 26.4.2.1 EUSART Synchronous Slave Transmit

The operation of the Synchronous Master and Slave modes are identical (see **Section 26.4.1.3 "Synchronous Master Transmission")**, except in the case of the Sleep mode. If two words are written to the TXREG and then the SLEEP instruction is executed, the following will occur:

- 1. The first character will immediately transfer to the TSR register and transmit.

- 2. The second word will remain in TXREG register.

- 3. The TXIF bit will not be set.

- After the first character has been shifted out of TSR, the TXREG register will transfer the second character to the TSR and the TXIF bit will now be set.

- 5. If the PEIE and TXIE bits are set, the interrupt will wake the device from Sleep and execute the next instruction. If the GIE bit is also set, the program will call the Interrupt Service Routine.

- 26.4.2.2 Synchronous Slave Transmission Set-up:

- 1. Set the SYNC and SPEN bits and clear the CSRC bit.

- 2. Clear the ANSEL bit for the CK pin (if applicable).

- 3. Clear the CREN and SREN bits.

- If interrupts are desired, set the TXIE bit of the PIE1 register and the GIE and PEIE bits of the INTCON register.

- 5. If 9-bit transmission is desired, set the TX9 bit.

- 6. Enable transmission by setting the TXEN bit.

- 7. If 9-bit transmission is selected, insert the Most Significant bit into the TX9D bit.

- 8. Start transmission by writing the Least Significant 8 bits to the TXREG register.

### TABLE 26-9:SUMMARY OF REGISTERS ASSOCIATED WITH SYNCHRONOUS SLAVE<br/>TRANSMISSION

| Name    | Bit 7                         | Bit 6   | Bit 5  | Bit 4                 | Bit 3                  | Bit 2  | Bit 1  | Bit 0   | Register<br>on Page |

|---------|-------------------------------|---------|--------|-----------------------|------------------------|--------|--------|---------|---------------------|

| APFCON0 | RXDTSEL                       | SDO1SEL | SS1SEL | P2BSEL <sup>(1)</sup> | CCP2SEL <sup>(1)</sup> | P1DSEL | P1CSEL | CCP1SEL | 119                 |

| APFCON1 | _                             | _       | _      | _                     | _                      | _      | _      | TXCKSEL | 119                 |

| BAUDCON | ABDOVF                        | RCIDL   | —      | SCKP                  | BRG16                  | —      | WUE    | ABDEN   | 296                 |

| INTCON  | GIE                           | PEIE    | TMR0IE | INTE                  | IOCIE                  | TMR0IF | INTF   | IOCIF   | 86                  |

| PIE1    | TMR1GIE                       | ADIE    | RCIE   | TXIE                  | SSPIE                  | CCP1IE | TMR2IE | TMR1IE  | 87                  |

| PIR1    | TMR1GIF                       | ADIF    | RCIF   | TXIF                  | SSPIF                  | CCP1IF | TMR2IF | TMR1IF  | 91                  |

| RCSTA   | SPEN                          | RX9     | SREN   | CREN                  | ADDEN                  | FERR   | OERR   | RX9D    | 295                 |

| TRISB   | TRISB7                        | TRISB6  | TRISB5 | TRISB4                | TRISB3                 | TRISB2 | TRISB1 | TRISB0  | 127                 |

| TXREG   | EUSART Transmit Data Register |         |        |                       |                        |        |        |         | 287*                |

| TXSTA   | CSRC                          | TX9     | TXEN   | SYNC                  | SENDB                  | BRGH   | TRMT   | TX9D    | 294                 |

|         |                               |         |        |                       |                        |        |        |         |                     |

Legend: — = unimplemented location, read as '0'. Shaded cells are not used for Synchronous Slave Transmission. \* Page provides register information.

Note 1: PIC16(L)F1827 only.

#### REGISTER 27-2: CPSCON1: CAPACITIVE SENSING CONTROL REGISTER 1

| U-0              | U-0          | U-0                           | U-0            | R/W-0/0        | R/W-0/0            | R/W-0/0           | R/W-0/0   |

|------------------|--------------|-------------------------------|----------------|----------------|--------------------|-------------------|-----------|

| 0-0              | 0-0          | 0-0                           | 0-0            |                |                    |                   | 1         |

|                  | _            | _                             | _              | CPSCH3         | CPSCH2             | CPSCH1            | CPSCH0    |

| bit 7            |              |                               |                |                |                    |                   | bit (     |

|                  |              |                               |                |                |                    |                   |           |

| Legend:          |              |                               |                |                |                    |                   |           |

| R = Readable I   | bit          | W = Writable b                | it             | U = Unimplem   | nented bit, read a | as '0'            |           |

| u = Bit is uncha | anged        | x = Bit is unkno              | own            | -n/n = Value a | t POR and BOR      | /Value at all oth | er Resets |

| '1' = Bit is set | -            | '0' = Bit is clea             | red            |                |                    |                   |           |

|                  |              |                               |                |                |                    |                   |           |

| bit 7-4          | Unimplemen   | ted: Read as '0'              |                |                |                    |                   |           |

|                  | •            |                               |                |                |                    |                   |           |

| bit 3-0          | If CPSON = 0 | Capacitive Sen                | sing Channel   | Select Dits    |                    |                   |           |

|                  |              | <u>.</u><br>ts are ignored. N | o channel is s | elected        |                    |                   |           |

|                  | If CPSON = 1 | -                             |                | selected.      |                    |                   |           |

|                  |              | channel 0, (CPS               | 50)            |                |                    |                   |           |

|                  |              | channel 1, (CPS               | ,              |                |                    |                   |           |

|                  |              | channel 2, (CPS               | ,              |                |                    |                   |           |

|                  | 0011 =       | channel 3, (CPS               | S3)            |                |                    |                   |           |

|                  | 0100 =       | channel 4, (CPS               | 64)            |                |                    |                   |           |

|                  | 0101 =       | channel 5, (CPS               | 65)            |                |                    |                   |           |

|                  | 0110 =       | channel 6, (CPS               | 56)            |                |                    |                   |           |

|                  |              | channel 7, (CPS               | ,              |                |                    |                   |           |

|                  |              | channel 8, (CPS               | ,              |                |                    |                   |           |

|                  |              | channel 9, (CPS               | ,              |                |                    |                   |           |

|                  |              | channel 10, (CF               | ,              |                |                    |                   |           |

|                  |              | channel 11, (CF               | ,              |                |                    |                   |           |

|                  |              | Reserved. Do n                |                |                |                    |                   |           |

|                  |              | Reserved. Do n                |                |                |                    |                   |           |

|                  |              | Reserved. Do n                |                |                |                    |                   |           |

|                  | 1111 =       | Reserved. Do n                | ot use.        |                |                    |                   |           |

#### TABLE 27-2: SUMMARY OF REGISTERS ASSOCIATED WITH CAPACITIVE SENSING

| Name       | Bit 7   | Bit 6    | Bit 5    | Bit 4    | Bit 3    | Bit 2   | Bit 1   | Bit 0   | Register<br>on Page |

|------------|---------|----------|----------|----------|----------|---------|---------|---------|---------------------|

| ANSELA     | -       | —        | —        | ANSA4    | ANSA3    | ANSA2   | ANSA1   | ANSA0   | 123                 |

| ANSELB     | ANSB7   | ANSB6    | ANSB5    | ANSB4    | ANSB3    | ANSB2   | ANSB1   | _       | 128                 |

| CPSCON0    | CPSON   | —        | _        |          | CPSRNG1  | CPSRNG0 | CPSOUT  | T0XCS   | 318                 |

| CPSCON1    |         | —        | _        |          | CPSCH3   | CPSCH2  | CPSCH1  | CPSCH0  | 319                 |

| INTCON     | GIE     | PEIE     | TMR0IE   | INTE     | IOCIE    | TMR0IF  | INTF    | IOCIF   | 86                  |

| OPTION_REG | WPUEN   | INTEDG   | TMR0CS   | TMR0SE   | PSA      | PS2     | PS1     | PS0     | 176                 |

| PIE1       | TMR1GIE | ADIE     | RCIE     | TXIE     | SSP1IE   | CCP1IE  | TMR2IE  | TMR1IE  | 87                  |

| PIR1       | TMR1GIF | ADIF     | RCIF     | TXIF     | SSP1IF   | CCP1IF  | TMR2IF  | TMR1IF  | 91                  |

| T1CON      | TMR1CS1 | TMR1CS0  | T1CKPS1  | T1CKPS0  | T1OSCEN  | T1SYNC  |         | TMR10N  | 185                 |

| TxCON      | _       | TxOUTPS3 | TxOUTPS2 | TxOUTPS1 | TxOUTPS0 | TMRxON  | TxCKPS1 | TxCKPS0 | 185                 |

| TRISA      | TRISA7  | TRISA6   | TRISA5   | TRISA4   | TRISA3   | TRISA2  | TRISA1  | TRISA0  | 122                 |

| TRISB      | TRISB7  | TRISB6   | TRISB5   | TRISB4   | TRISB3   | TRISB2  | TRISB1  | TRISB0  | 127                 |

Legend: — = Unimplemented locations, read as '0'. Shaded cells are not used by the capacitive sensing module.

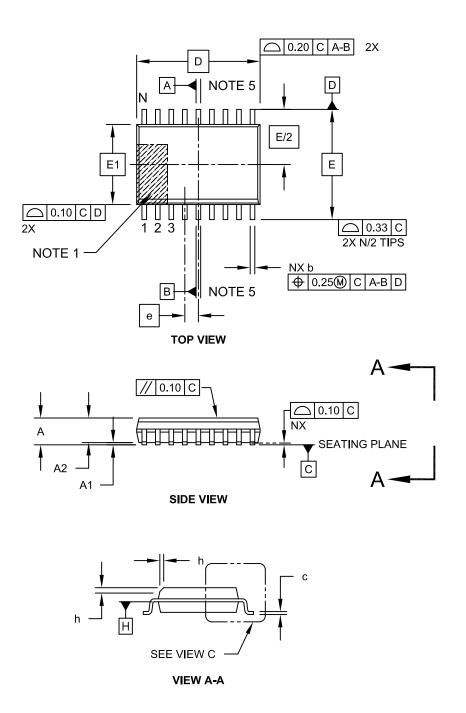

#### 18-Lead Plastic Small Outline (SO) - Wide, 7.50 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-051C Sheet 1 of 2

| TRISB                         | 125     |

|-------------------------------|---------|

| TRISB Register                | 28, 127 |

| Two-Speed Clock Start-up Mode | 61      |

| TXCON (Timer2/4/6) Register   |         |

| TXREG                         |         |

| TXREG Register                |         |

| TXSTA Register                |         |

| BRGH Bit                      |         |

### U

#### USART

| Synchronous Master Mode                   |     |

|-------------------------------------------|-----|

| Requirements, Synchronous Receive         | 364 |

| Requirements, Synchronous Transmission    | 364 |

| Timing Diagram, Synchronous Receive       | 364 |

| Timing Diagram, Synchronous Transmission. | 364 |

#### ۷

VREF. SEE ADC Reference Voltage

#### W

| Wake-up on Break     Wake-up Using Interrupts     Watchdog Timer (WDT)     Associated Registers     Configuration Word w/ Watchdog Timer     Modes     Specifications     WCOL   263, 266, 266     WCOL Status Flag   263, 266, 266     WDTCON Register   123     Write Protection   123 |           |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

|                                                                                                                                                                                                                                                                                          | 47<br>403 |

|                                                                                                                                                                                                                                                                                          |           |

#### **READER RESPONSE**

It is our intention to provide you with the best documentation possible to ensure successful use of your Microchip product. If you wish to provide your comments on organization, clarity, subject matter, and ways in which our documentation can better serve you, please FAX your comments to the Technical Publications Manager at (480) 792-4150.

Please list the following information, and use this outline to provide us with your comments about this document.

|                                                        | Total Pages Sent                         |

|--------------------------------------------------------|------------------------------------------|

|                                                        |                                          |

|                                                        |                                          |

|                                                        |                                          |

|                                                        |                                          |

| Telephone: ()                                          | FAX: ()                                  |

| plication (optional):                                  |                                          |

| ould you like a reply?YN                               |                                          |

| vice: PIC16(L)F1826/27                                 | Literature Number: DS41391D              |

| estions:                                               |                                          |

| What are the best features of this document?           |                                          |

|                                                        |                                          |

| How does this document meet your hardware and so       | oftware development needs?               |

|                                                        |                                          |

| Do you find the organization of this document easy t   | o follow? If not, why?                   |

|                                                        |                                          |

|                                                        |                                          |

| What additions to the document do you think would o    | enhance the structure and subject?       |

|                                                        |                                          |

| What deletions from the document could be made w       | ithout affecting the overall usefulness? |

|                                                        |                                          |

| Is there any incorrect or misleading information (what | it and where)?                           |

|                                                        |                                          |

| How would you improve this document?                   |                                          |

| How would you improve this document?                   |                                          |

|                                                        | Reader Response  Name                    |