Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 16                                                                         |

| Program Memory Size        | 7KB (4K x 14)                                                              |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 384 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                |

| Data Converters            | A/D 12x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 18-SOIC (0.295", 7.50mm Width)                                             |

| Supplier Device Package    | 18-SOIC                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1827-e-so |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# PIC16(L)F1826/27

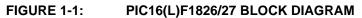

#### 2.0 ENHANCED MID-RANGE CPU

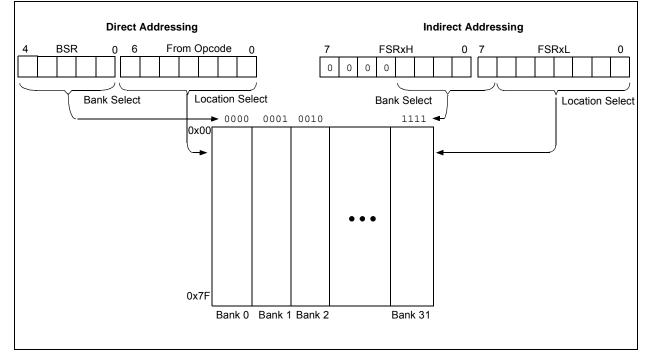

This family of devices contain an enhanced mid-range 8-bit CPU core. The CPU has 49 instructions. Interrupt capability includes automatic context saving. The hardware stack is 16 levels deep and has Overflow and Underflow Reset capability. Direct, Indirect, and Relative addressing modes are available. Two File Select Registers (FSRs) provide the ability to read program and data memory.

- Automatic Interrupt Context Saving

- 16-level Stack with Overflow and Underflow

- File Select Registers

- Instruction Set

#### 2.1 Automatic Interrupt Context Saving

During interrupts, certain registers are automatically saved in shadow registers and restored when returning from the interrupt. This saves stack space and user code. See **Section 8.5 "Automatic Context Saving"**, for more information.

#### 2.2 16-level Stack with Overflow and Underflow

These devices have an external stack memory 15 bits wide and 16 words deep. A Stack Overflow or Underflow will set the appropriate bit (STKOVF or STKUNF) in the PCON register, and if enabled will cause a software Reset. See section **Section 3.4 "Stack"** for more details.

#### 2.3 File Select Registers

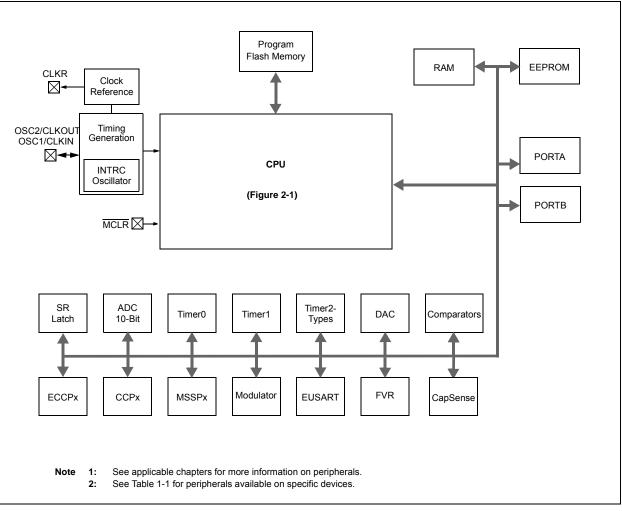

There are two 16-bit File Select Registers (FSR). FSRs can access all file registers and program memory, which allows one Data Pointer for all memory. When an FSR points to program memory, there is one additional instruction cycle in instructions using INDF to allow the data to be fetched. General purpose memory can now also be addressed linearly, providing the ability to access contiguous data larger than 80 bytes. There are also new instructions to support the FSRs. See **Section 3.4 "Stack**"for more details.

#### 2.4 Instruction Set

There are 49 instructions for the enhanced mid-range CPU to support the features of the CPU. See **Section 29.0** "Instruction Set Summary" for more details.

#### TABLE 3-3: PIC16(L)F1826/27 MEMORY MAP (CONTINUED)

|      | BANK 8                        |      | BANK 9                        |      | BANK 10                       |      | BANK 11                       |      | BANK 12                       |      | BANK 13                       |      | BANK 14                       |      | BANK 15                       |

|------|-------------------------------|------|-------------------------------|------|-------------------------------|------|-------------------------------|------|-------------------------------|------|-------------------------------|------|-------------------------------|------|-------------------------------|

| 400h | Core Registers<br>(Table 3-2) | 480h | Core Registers<br>(Table 3-2) | 500h | Core Registers<br>(Table 3-2) | 580h | Core Registers<br>(Table 3-2) | 600h | Core Registers<br>(Table 3-2) | 680h | Core Registers<br>(Table 3-2) | 700h | Core Registers<br>(Table 3-2) | 780h | Core Registers<br>(Table 3-2) |

| 40Bh |                               | 48Bh |                               | 50Bh |                               | 58Bh |                               | 60Bh |                               | 68Bh |                               | 70Bh |                               | 78Bh |                               |

| 40Ch | —                             | 48Ch | —                             | 50Ch | —                             | 58Ch |                               | 60Ch | —                             | 68Ch | —                             | 70Ch | —                             | 78Ch | —                             |

| 40Dh | —                             | 48Dh | —                             | 50Dh | —                             | 58Dh | —                             | 60Dh | —                             | 68Dh | —                             | 70Dh | —                             | 78Dh | —                             |

| 40Eh | _                             | 48Eh | —                             | 50Eh | _                             | 58Eh | _                             | 60Eh | _                             | 68Eh | _                             | 70Eh | _                             | 78Eh | _                             |

| 40Fh | —                             | 48Fh | —                             | 50Fh | _                             | 58Fh |                               | 60Fh | —                             | 68Fh | —                             | 70Fh | —                             | 78Fh | —                             |

| 410h | —                             | 490h | —                             | 510h | _                             | 590h | —                             | 610h | _                             | 690h | _                             | 710h | _                             | 790h | _                             |

| 411h | —                             | 491h | _                             | 511h | _                             | 591h | _                             | 611h | —                             | 691h | —                             | 711h | —                             | 791h | _                             |

| 412h | —                             | 492h | _                             | 512h | —                             | 592h | —                             | 612h | —                             | 692h | —                             | 712h | —                             | 792h | _                             |

| 413h | —                             | 493h | _                             | 513h | —                             | 593h | —                             | 613h | —                             | 693h | —                             | 713h | —                             | 793h | _                             |

| 414h | -                             | 494h | —                             | 514h | —                             | 594h | —                             | 614h | —                             | 694h | —                             | 714h | —                             | 794h | —                             |

| 415h | TMR4 <sup>(1)</sup>           | 495h | —                             | 515h | —                             | 595h | —                             | 615h | —                             | 695h | —                             | 715h | —                             | 795h | —                             |

| 416h | PR4 <sup>(1)</sup>            | 496h | _                             | 516h | _                             | 596h |                               | 616h | —                             | 696h | —                             | 716h | —                             | 796h | _                             |

| 417h | T4CON <sup>(1)</sup>          | 497h | —                             | 517h | —                             | 597h | —                             | 617h | —                             | 697h | —                             | 717h | —                             | 797h | —                             |

| 418h | —                             | 498h | —                             | 518h | —                             | 598h | —                             | 618h | —                             | 698h | —                             | 718h | —                             | 798h | —                             |

| 419h | —                             | 499h | —                             | 519h | —                             | 599h | _                             | 619h | —                             | 699h | —                             | 719h | —                             | 799h | _                             |

| 41Ah | —                             | 49Ah | —                             | 51Ah | _                             | 59Ah | _                             | 61Ah | —                             | 69Ah | —                             | 71Ah | —                             | 79Ah | _                             |

| 41Bh | —                             | 49Bh | —                             | 51Bh | —                             | 59Bh | _                             | 61Bh | —                             | 69Bh | —                             | 71Bh | —                             | 79Bh | _                             |

| 41Ch | TMR6 <sup>(1)</sup>           | 49Ch | _                             | 51Ch | _                             | 59Ch |                               | 61Ch | _                             | 69Ch | _                             | 71Ch | _                             | 79Ch | —                             |

| 41Dh | PR6 <sup>(1)</sup>            | 49Dh | —                             | 51Dh | —                             | 59Dh | —                             | 61Dh | —                             | 69Dh | —                             | 71Dh | —                             | 79Dh | —                             |

| 41Eh | T6CON <sup>(1)</sup>          | 49Eh | _                             | 51Eh | —                             | 59Eh | —                             | 61Eh | —                             | 69Eh | —                             | 71Eh | —                             | 79Eh | —                             |

| 41Fh | —                             | 49Fh | _                             | 51Fh | —                             | 59Fh | _                             | 61Fh | —                             | 69Fh | —                             | 71Fh | —                             | 79Fh | _                             |

| 420h |                               | 4A0h |                               | 520h |                               | 5A0h |                               | 620h |                               | 6A0h |                               | 720h |                               | 7A0h |                               |

|      | Unimplemented<br>Read as '0'  |

| 46Fh |                               | 4EFh |                               | 56Fh |                               | 5EFh |                               | 66Fh |                               | 6EFh |                               | 76Fh |                               | 7EFh |                               |

| 470h |                               | 4F0h |                               | 570h |                               | 5F0h |                               | 670h |                               | 6F0h |                               | 770h |                               | 7F0h |                               |

|      | Accesses<br>70h – 7Fh         |

| 47Fh |                               | 4FFh |                               | 57Fh |                               | 5FFh |                               | 67Fh |                               | 6FFh |                               | 77Fh |                               | 7FFh |                               |

Legend: = Unimplemented data memory locations, read as '0'

# PIC16(L)F1826/27

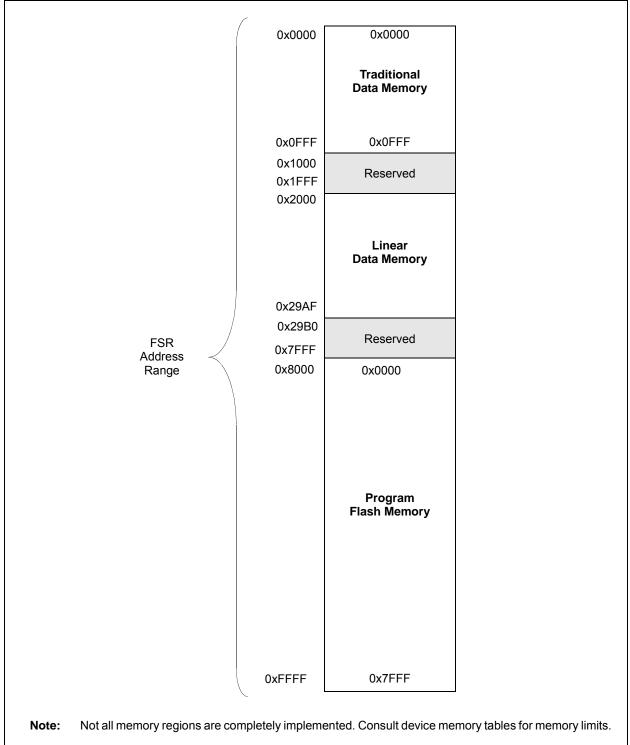

#### 3.5.1 TRADITIONAL DATA MEMORY

The traditional data memory is a region from FSR address 0x000 to FSR address 0xFFF. The addresses correspond to the absolute addresses of all SFR, GPR and common registers.

| R-1/q           | R-0/q                                                                                                                                                                       | R-q/q                                                       | R-0/q          | R-0/q         | R-q/q            | R-0/0          | R-0/q        |

|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|----------------|---------------|------------------|----------------|--------------|

| T10SCR          | PLLR                                                                                                                                                                        | OSTS                                                        | HFIOFR         | HFIOFL        | MFIOFR           | LFIOFR         | HFIOFS       |

| bit 7           |                                                                                                                                                                             |                                                             |                |               |                  |                | bit 0        |

|                 |                                                                                                                                                                             |                                                             |                |               |                  |                |              |

| Legend:         |                                                                                                                                                                             |                                                             |                |               |                  |                |              |

| R = Readable    |                                                                                                                                                                             | W = Writable                                                |                | -             | mented bit, read |                |              |

| u = Bit is unc  | 0                                                                                                                                                                           | x = Bit is unk                                              |                |               | at POR and BO    | R/Value at all | other Resets |

| '1' = Bit is se | t                                                                                                                                                                           | '0' = Bit is cle                                            | ared           | q = Condition | nal              |                |              |

| bit 7           | <u>If T1OSCEN</u><br>1 = Timer1<br>0 = Timer1<br><u>If T1OSCEN</u>                                                                                                          | oscillator is rea<br>oscillator is not                      | dy<br>ready    |               |                  |                |              |

| bit 6           | <b>PLLR</b> 4x PL<br>1 = 4x PLL                                                                                                                                             | L Ready bit                                                 |                |               |                  |                |              |

| bit 5           | 1 = Runnin                                                                                                                                                                  | llator Start-up T<br>ig from the clocl<br>ig from an interr | defined by the | e FOSC<2:0>   |                  | guration Word  | 1            |

| bit 4           | 1 = HFINTC                                                                                                                                                                  | gh Frequency Ir<br>DSC is ready<br>DSC is not ready         |                | or Ready bit  |                  |                |              |

| bit 3           | <ul> <li><b>HFIOFL:</b> High Frequency Internal Oscillator Locked bit</li> <li>1 = HFINTOSC is at least 2% accurate</li> <li>0 = HFINTOSC is not 2% accurate</li> </ul>     |                                                             |                |               |                  |                |              |

| bit 2           | MFIOFR: Medium Frequency Internal Oscillator Ready bit<br>1 = MFINTOSC is ready<br>0 = MFINTOSC is not ready                                                                |                                                             |                |               |                  |                |              |

| bit 1           | LFIOFR: Low Frequency Internal Oscillator Ready bit<br>1 = LFINTOSC is ready<br>0 = LFINTOSC is not ready                                                                   |                                                             |                |               |                  |                |              |

| bit 0           | <ul> <li><b>HFIOFS:</b> High Frequency Internal Oscillator Stable bit</li> <li>1 = HFINTOSC is at least 0.5% accurate</li> <li>0 = HFINTOSC is not 0.5% accurate</li> </ul> |                                                             |                |               |                  |                |              |

#### REGISTER 5-2: OSCSTAT: OSCILLATOR STATUS REGISTER

| Name   | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Register<br>on Page |

|--------|--------|--------|--------|--------|--------|--------|--------|--------|---------------------|

| BORCON | SBOREN |        |        |        |        |        | _      | BORRDY | 75                  |

| PCON   | STKOVF | STKUNF | _      | _      | RMCLR  | RI     | POR    | BOR    | 79                  |

| STATUS | _      | _      |        | TO     | PD     | Z      | DC     | С      | 21                  |

| WDTCON | _      | _      | WDTPS4 | WDTPS3 | WDTPS2 | WDTPS1 | WDTPS0 | SWDTEN | 99                  |

#### TABLE 7-5: SUMMARY OF REGISTERS ASSOCIATED WITH RESETS

**Legend:** — = unimplemented bit, reads as '0'. Shaded cells are not used by Resets.

**Note 1:** Other (non Power-up) Resets include MCLR Reset and Watchdog Timer Reset during normal operation.

#### 8.6 Interrupt Control Registers

#### 8.6.1 INTCON REGISTER

The INTCON register is a readable and writable register, that contains the various enable and flag bits for TMR0 register overflow, interrupt-on-change and external INT pin interrupts.

Note: Interrupt flag bits are set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the Global Enable bit, GIE, of the INTCON register. User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

#### REGISTER 8-1: INTCON: INTERRUPT CONTROL REGISTER

| R/W-0/0 | R-0/0                |

|---------|---------|---------|---------|---------|---------|---------|----------------------|

| GIE     | PEIE    | TMR0IE  | INTE    | IOCIE   | TMR0IF  | INTF    | IOCIF <sup>(1)</sup> |

| bit 7   |         |         |         |         |         |         | bit 0                |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7 | GIE: Global Interrupt Enable bit                                                                                                                                                                                                  |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <ul><li>1 = Enables all active interrupts</li><li>0 = Disables all interrupts</li></ul>                                                                                                                                           |

| bit 6 | <b>PEIE:</b> Peripheral Interrupt Enable bit<br>1 = Enables all active peripheral interrupts<br>0 = Disables all peripheral interrupts                                                                                            |

| bit 5 | <b>TMROIE:</b> Timer0 Overflow Interrupt Enable bit<br>1 = Enables the Timer0 interrupt<br>0 = Disables the Timer0 interrupt                                                                                                      |

| bit 4 | INTE: INT External Interrupt Enable bit<br>1 = Enables the INT external interrupt<br>0 = Disables the INT external interrupt                                                                                                      |

| bit 3 | IOCIE: Interrupt-on-Change Enable bit<br>1 = Enables the interrupt-on-change<br>0 = Disables the interrupt-on-change                                                                                                              |

| bit 2 | <b>TMR0IF:</b> Timer0 Overflow Interrupt Flag bit<br>1 = TMR0 register has overflowed<br>0 = TMR0 register did not overflow                                                                                                       |

| bit 1 | INTF: INT External Interrupt Flag bit<br>1 = The INT external interrupt occurred<br>0 = The INT external interrupt did not occur                                                                                                  |

| bit 0 | <ul> <li>IOCIF: Interrupt-on-Change Interrupt Flag bit<sup>(1)</sup></li> <li>1 = When at least one of the interrupt-on-change pins changed state</li> <li>0 = None of the interrupt-on-change pins have changed state</li> </ul> |

|       |                                                                                                                                                                                                                                   |

**Note 1:** The IOCIF Flag bit is read-only and cleared when all the Interrupt-on-Change flags in the IOCBF register have been cleared by software.

#### 17.0 DIGITAL-TO-ANALOG CONVERTER (DAC) MODULE

The Digital-to-Analog Converter supplies a variable voltage reference, ratiometric with the input source, with 32 selectable output levels.

The input of the DAC can be connected to:

- External VREF pins

- VDD supply voltage

- FVR (Fixed Voltage Reference)

The output of the DAC can be configured to supply a reference voltage to the following:

- Comparator positive input

- ADC input channel

- DACOUT pin

- Capacitive Sensing module (CSM)

The Digital-to-Analog Converter (DAC) can be enabled by setting the DACEN bit of the DACCON0 register.

#### EQUATION 17-1: DAC OUTPUT VOLTAGE

### <u>**IF DACEN = 1**</u> $VOUT = \left( (VSOURCE - VSOURCE -) \times \frac{DACR[4:0]}{2^5} \right) + VSOURCE - VSOURCE -$

IF DACEN = 0 and DACLPS = 1 and DACR[4:0] = 11111

VOUT = VSOURCE +

#### IF DACEN = 0 and DACLPS = 0 and DACR[4:0] = 00000

VOUT = VSOURCE -

VSOURCE+ = VDD, VREF, or FVR BUFFER 2

VSOURCE- = VSS

#### 17.2 Ratiometric Output Level

The DAC output value is derived using a resistor ladder with each end of the ladder tied to a positive and negative voltage reference input source. If the voltage of either input source fluctuates, a similar fluctuation will result in the DAC output value.

The value of the individual resistors within the ladder can be found in **Section 29.0** "**Electrical Specifications**".

#### 17.1 Output Voltage Selection

The DAC has 32 voltage level ranges. The 32 levels are set with the DACR<4:0> bits of the DACCON1 register.

The DAC output voltage is determined by the equations in Equation 17-1.

#### 17.3 DAC Voltage Reference Output

The DAC can be output to the DACOUT pin by setting the DACOE bit of the DACCON0 register to '1'. Selecting the DAC reference voltage for output on the DACOUT pin automatically overrides the digital output buffer and digital input threshold detector functions of that pin. Reading the DACOUT pin when it has been configured for DAC reference voltage output will always return a '0'.

Due to the limited current drive capability, a buffer must be used on the DAC voltage reference output for external connections to DACOUT. Figure 17-2 shows an example buffering technique.

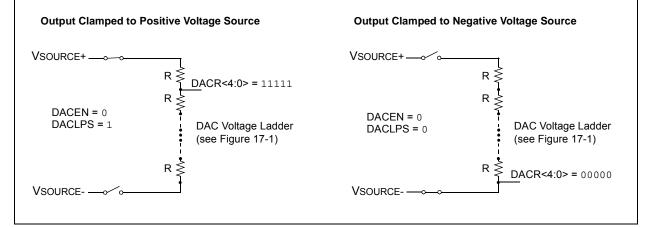

#### 17.4 Low-Power Voltage State

In order for the DAC module to consume the least amount of power, one of the two voltage reference input sources to the resistor ladder must be disconnected. Either the positive voltage source, (VSOURCE+), or the negative voltage source, (VSOURCE-) can be disabled.

The negative voltage source is disabled by setting the DACLPS bit in the DACCON0 register. Clearing the DACLPS bit in the DACCON0 register disables the positive voltage source.

#### 17.4.1 OUTPUT CLAMPED TO POSITIVE VOLTAGE SOURCE

The DAC output voltage can be set to VSOURCE+ with the least amount of power consumption by performing the following:

- · Clearing the DACEN bit in the DACCON0 register.

- Setting the DACLPS bit in the DACCON0 register.

- Configuring the DACPSS bits to the proper positive source.

- Configuring the DACR<4:0> bits to '11111' in the DACCON1 register.

This is also the method used to output the voltage level from the FVR to an output pin. See **Section 17.5** "**Operation During Sleep**" for more information.

Reference Figure 17-3 for output clamping examples.

### 17.4.2 OUTPUT CLAMPED TO NEGATIVE VOLTAGE SOURCE

The DAC output voltage can be set to VSOURCE- with the least amount of power consumption by performing the following:

- · Clearing the DACEN bit in the DACCON0 register.

- Clearing the DACLPS bit in the DACCON0 register.

- Configuring the DACNSS bits to the proper negative source.

- Configuring the DACR<4:0> bits to '00000' in the DACCON1 register.

This allows the comparator to detect a zero-crossing while not consuming additional current through the DAC module.

Reference Figure 17-3 for output clamping examples.

#### FIGURE 17-3: OUTPUT VOLTAGE CLAMPING EXAMPLES

#### 17.5 Operation During Sleep

When the device wakes up from Sleep through an interrupt or a Watchdog Timer time-out, the contents of the DACCON0 register are not affected. To minimize current consumption in Sleep mode, the voltage reference should be disabled.

#### 17.6 Effects of a Reset

A device Reset affects the following:

- DAC is disabled.

- DAC output voltage is removed from the DACOUT pin.

- The DACR<4:0> range select bits are cleared.

- © 2011 Microchip Technology Inc.

#### 19.0 COMPARATOR MODULE

Comparators are used to interface analog circuits to a digital circuit by comparing two analog voltages and providing a digital indication of their relative magnitudes. Comparators are very useful mixed signal building blocks because they provide analog functionality independent of program execution. The analog comparator module includes the following features:

- · Independent comparator control

- Programmable input selection

- · Comparator output is available internally/externally

- Programmable output polarity

- Interrupt-on-change

- · Wake-up from Sleep

- Programmable Speed/Power optimization

- · PWM shutdown

- · Programmable and fixed voltage reference

#### 19.1 Comparator Overview

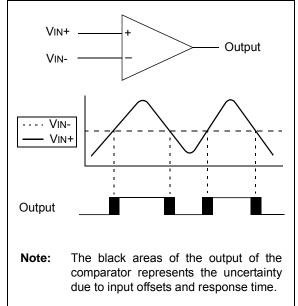

A single comparator is shown in Figure 19-1 along with the relationship between the analog input levels and the digital output. When the analog voltage at VIN+ is less than the analog voltage at VIN-, the output of the comparator is a digital low level. When the analog voltage at VIN+ is greater than the analog voltage at VIN-, the output of the comparator is a digital high level.

#### FIGURE 19-1:

#### SINGLE COMPARATOR

## 19.7 Comparator Negative Input Selection

The CxNCH<1:0> bits of the CMxCON0 register direct one of four analog pins to the comparator inverting input.

| Note: | To use CxIN+ and CxINx- pins as analog     |

|-------|--------------------------------------------|

|       | input, the appropriate bits must be set in |

|       | the ANSEL register and the correspond-     |

|       | ing TRIS bits must also be set to disable  |

|       | the output drivers.                        |

#### 19.8 Comparator Response Time

The comparator output is indeterminate for a period of time after the change of an input source or the selection of a new reference voltage. This period is referred to as the response time. The response time of the comparator differs from the settling time of the voltage reference. Therefore, both of these times must be considered when determining the total response time to a comparator input change. See the Comparator and Voltage Reference Specifications in **Section 29.0 "Electrical Specifications"** for more details.

#### 19.9 Interaction with ECCP Logic

The C1 and C2 comparators can be used as general purpose comparators. Their outputs can be brought out to the C1OUT and C2OUT pins. When the ECCP Auto-Shutdown is active it can use one or both comparator signals. If auto-restart is also enabled, the comparators can be configured as a closed loop analog feedback to the ECCP, thereby, creating an analog controlled PWM.

**Note:** When the comparator module is first initialized the output state is unknown. Upon initialization, the user should verify the output state of the comparator prior to relying on the result, primarily when using the result in connection with other peripheral features, such as the ECCP Auto-Shutdown mode.

#### 19.10 Analog Input Connection Considerations

A simplified circuit for an analog input is shown in Figure 19-4. Since the analog input pins share their connection with a digital input, they have reverse biased ESD protection diodes to VDD and VSS. The analog input, therefore, must be between VSS and VDD. If the input voltage deviates from this range by more than 0.6V in either direction, one of the diodes is forward biased and a latch-up may occur.

A maximum source impedance of  $10 \text{ k}\Omega$  is recommended for the analog sources. Also, any external component connected to an analog input pin, such as a capacitor or a Zener diode, should have very little leakage current to minimize inaccuracies introduced.

Note 1: When reading a PORT register, all pins configured as analog inputs will read as a '0'. Pins configured as digital inputs will convert as an analog input, according to the input specification.

> Analog levels on any pin defined as a digital input, may cause the input buffer to consume more current than is specified.

#### 21.1 Timer1 Operation

The Timer1 module is a 16-bit incrementing counter which is accessed through the TMR1H:TMR1L register pair. Writes to TMR1H or TMR1L directly update the counter.

When used with an internal clock source, the module is a timer and increments on every instruction cycle. When used with an external clock source, the module can be used as either a timer or counter and increments on every selected edge of the external source.

Timer1 is enabled by configuring the TMR1ON and TMR1GE bits in the T1CON and T1GCON registers, respectively. Table 21-1 displays the Timer1 enable selections.

| TABLE 21-1: | TIMER1 ENABLE |

|-------------|---------------|

|             | SELECTIONS    |

| TMR10N | TMR1GE | Timer1<br>Operation |

|--------|--------|---------------------|

| 0      | 0      | Off                 |

| 0      | 1      | Off                 |

| 1      | 0      | Always On           |

| 1      | 1      | Count Enabled       |

#### 21.2 Clock Source Selection

The TMR1CS<1:0> and T1OSCEN bits of the T1CON register are used to select the clock source for Timer1. Table 21-2 displays the clock source selections.

#### 21.2.1 INTERNAL CLOCK SOURCE

When the internal clock source is selected the TMR1H:TMR1L register pair will increment on multiples of Fosc as determined by the Timer1 prescaler.

When the Fosc internal clock source is selected, the Timer1 register value will increment by four counts every instruction clock cycle. Due to this condition, a 2 LSB error in resolution will occur when reading the Timer1 value. To utilize the full resolution of Timer1, an asynchronous input signal must be used to gate the Timer1 clock input.

The following asynchronous sources may be used:

- Asynchronous event on the T1G pin to Timer1 gate

- C1 or C2 comparator input to Timer1 gate

#### 21.2.2 EXTERNAL CLOCK SOURCE

When the external clock source is selected, the Timer1 module may work as a timer or a counter.

When enabled to count, Timer1 is incremented on the rising edge of the external clock input T1CKI or the capacitive sensing oscillator signal. Either of these external clock sources can be synchronized to the microcontroller system clock or they can run asynchronously.

When used as a timer with a clock oscillator, an external 32.768 kHz crystal can be used in conjunction with the dedicated internal oscillator circuit.

- **Note:** In Counter mode, a falling edge must be registered by the counter prior to the first incrementing rising edge after any one or more of the following conditions:

- Timer1 enabled after POR

- Write to TMR1H or TMR1L

- Timer1 is disabled

- Timer1 is disabled (TMR1ON = 0) when T1CKI is high then Timer1 is enabled (TMR1ON=1) when T1CKI is low.

| TMR1CS1 | TMR1CS0 | T10SCEN | Clock Source                   |  |

|---------|---------|---------|--------------------------------|--|

| 0       | 0       | x       | Instruction Clock (Fosc/4)     |  |

| 0       | 1       | x       | System Clock (Fosc)            |  |

| 1       | 0       | 0       | External Clocking on T1CKI Pin |  |

| 1       | 0       | 0       | External Clocking on T1CKI Pin |  |

| 1       | 1       | x       | Capacitive Sensing Oscillator  |  |

#### TABLE 21-2: CLOCK SOURCE SELECTIONS

#### 21.6.2 TIMER1 GATE SOURCE SELECTION

The Timer1 gate source can be selected from one of four different sources. Source selection is controlled by the T1GSS bits of the T1GCON register. The polarity for each available source is also selectable. Polarity selection is controlled by the T1GPOL bit of the T1GCON register.

TABLE 21-4: TIMER1 GATE SOURCES

| T1GSS | Timer1 Gate Source                                                       |

|-------|--------------------------------------------------------------------------|

| 00    | Timer1 Gate Pin                                                          |

| 01    | Overflow of Timer0<br>(TMR0 increments from FFh to 00h)                  |

| 10    | Comparator 1 Output SYNCC1OUT<br>(optionally Timer1 synchronized output) |

| 11    | Comparator 2 Output SYNCC2OUT<br>(optionally Timer1 synchronized output) |

#### 21.6.2.1 T1G Pin Gate Operation

The T1G pin is one source for Timer1 gate control. It can be used to supply an external source to the Timer1 gate circuitry.

#### 21.6.2.2 Timer0 Overflow Gate Operation

When Timer0 increments from FFh to 00h, a low-to-high pulse will automatically be generated and internally supplied to the Timer1 gate circuitry.

#### 21.6.2.3 Comparator C1 Gate Operation

The output resulting from a Comparator 1 operation can be selected as a source for Timer1 gate control. The Comparator 1 output (SYNCC1OUT) can be synchronized to the Timer1 clock or left asynchronous. For more information see **Section 19.4.1 "Comparator Output Synchronization**".

#### 21.6.2.4 Comparator C2 Gate Operation

The output resulting from a Comparator 2 operation can be selected as a source for Timer1 gate control. The Comparator 2 output (SYNCC2OUT) can be synchronized to the Timer1 clock or left asynchronous. For more information see **Section 19.4.1 "Comparator Output Synchronization"**.

#### 21.6.3 TIMER1 GATE TOGGLE MODE

When Timer1 Gate Toggle mode is enabled, it is possible to measure the full-cycle length of a Timer1 gate signal, as opposed to the duration of a single level pulse.

The Timer1 gate source is routed through a flip-flop that changes state on every incrementing edge of the signal. See Figure 21-4 for timing details.

Timer1 Gate Toggle mode is enabled by setting the T1GTM bit of the T1GCON register. When the T1GTM bit is cleared, the flip-flop is cleared and held clear. This is necessary in order to control which edge is measured.

| Note: | Enabling Toggle mode at the same time       |  |  |  |  |  |

|-------|---------------------------------------------|--|--|--|--|--|

|       | as changing the gate polarity may result in |  |  |  |  |  |

|       | indeterminate operation.                    |  |  |  |  |  |

#### 21.6.4 TIMER1 GATE SINGLE-PULSE MODE

When Timer1 Gate Single-Pulse mode is enabled, it is possible to capture a single pulse gate event. Timer1 Gate Single-Pulse mode is first enabled by setting the T1GSPM bit in the T1GCON register. Next, the T1GGO/DONE bit in the T1GCON register must be set. The Timer1 will be fully enabled on the next incrementing edge. On the next trailing edge of the pulse, the T1GGO/DONE bit will automatically be cleared. No other gate events will be allowed to increment Timer1 until the T1GGO/DONE bit is once again set in software. See Figure 21-5 for timing details.

If the Single Pulse Gate mode is disabled by clearing the T1GSPM bit in the T1GCON register, the T1GGO/DONE bit should also be cleared.

Enabling the Toggle mode and the Single-Pulse mode simultaneously will permit both sections to work together. This allows the cycle times on the Timer1 gate source to be measured. See Figure 21-6 for timing details.

#### 21.6.5 TIMER1 GATE VALUE STATUS

When Timer1 Gate Value Status is utilized, it is possible to read the most current level of the gate control value. The value is stored in the T1GVAL bit in the T1GCON register. The T1GVAL bit is valid even when the Timer1 gate is not enabled (TMR1GE bit is cleared).

#### 21.6.6 TIMER1 GATE EVENT INTERRUPT

When Timer1 Gate Event Interrupt is enabled, it is possible to generate an interrupt upon the completion of a gate event. When the falling edge of T1GVAL occurs, the TMR1GIF flag bit in the PIR1 register will be set. If the TMR1GIE bit in the PIE1 register is set, then an interrupt will be recognized.

The TMR1GIF flag bit operates even when the Timer1 gate is not enabled (TMR1GE bit is cleared).

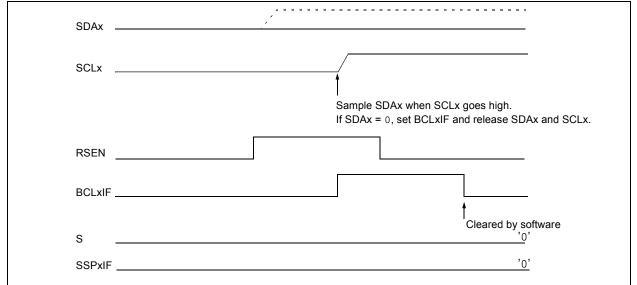

#### 25.4.9 ACKNOWLEDGE SEQUENCE

The 9th SCLx pulse for any transferred byte in  $I^2C$  is dedicated as an Acknowledge. It allows receiving devices to respond back to the transmitter by pulling the SDAx line low. The transmitter must release control of the line during this time to shift in the response. The Acknowledge (ACK) is an active-low signal, pulling the SDAx line low indicated to the transmitter that the device has received the transmitted data and is ready to receive more.

The result of an  $\overline{ACK}$  is placed in the ACKSTAT bit of the SSPxCON2 register.

Slave software, when the AHEN and DHEN bits are set, allow the user to set the ACK value sent back to the transmitter. The ACKDT bit of the SSPxCON2 register is set/cleared to determine the response.

Slave hardware will generate an ACK response if the AHEN and DHEN bits of the SSPxCON3 register are clear.

There are certain conditions where an  $\overline{ACK}$  will not be sent by the slave. If the BF bit of the SSPxSTAT register or the SSPxOV bit of the SSPxCON1 register are set when a byte is received.

When the module is addressed, after the 8th falling edge of SCLx on the bus, the ACKTIM bit of the SSPxCON3 register is set. The ACKTIM bit indicates the acknowledge time of the active bus. The ACKTIM Status bit is only active when the AHEN bit or DHEN bit is enabled.

#### 25.5 I<sup>2</sup>C SLAVE MODE OPERATION

The MSSPx Slave mode operates in one of four modes selected in the SSPxM bits of SSPxCON1 register. The modes can be divided into 7-bit and 10-bit Addressing mode. 10-bit Addressing modes operate the same as 7-bit with some additional overhead for handling the larger addresses.

Modes with Start and Stop bit interrupts operated the same as the other modes with SSPxIF additionally getting set upon detection of a Start, Restart, or Stop condition.

#### 25.5.1 SLAVE MODE ADDRESSES

The SSPxADD register (Register 25-6) contains the Slave mode address. The first byte received after a Start or Restart condition is compared against the value stored in this register. If the byte matches, the value is loaded into the SSPxBUF register and an interrupt is generated. If the value does not match, the module goes Idle and no indication is given to the software that anything happened.

The SSPx Mask register (Register 25-5) affects the address matching process. See **Section 25.5.9 "SSPx Mask Register**" for more information.

25.5.1.1 I<sup>2</sup>C Slave 7-bit Addressing Mode

In 7-bit Addressing mode, the LSb of the received data byte is ignored when determining if there is an address match.

25.5.1.2 I<sup>2</sup>C Slave 10-bit Addressing Mode

In 10-bit Addressing mode, the first received byte is compared to the binary value of '1 1 1 1 0 A9 A8 0'. A9 and A8 are the two MSb of the 10-bit address and stored in bits 2 and 1 of the SSPxADD register.

After the acknowledge of the high byte the UA bit is set and SCLx is held low until the user updates SSPxADD with the low address. The low address byte is clocked in and all 8 bits are compared to the low address value in SSPxADD. Even if there is not an address match; SSPxIF and UA are set, and SCLx is held low until SSPxADD is updated to receive a high byte again. When SSPxADD is updated the UA bit is cleared. This ensures the module is ready to receive the high address byte on the next communication.

A high and low address match as a write request is required at the start of all 10-bit addressing communication. A transmission can be initiated by issuing a Restart once the slave is addressed, and clocking in the high address with the R/W bit set. The slave hardware will then acknowledge the read request and prepare to clock out data. This is only valid for a slave after it has received a complete high and low address byte match.

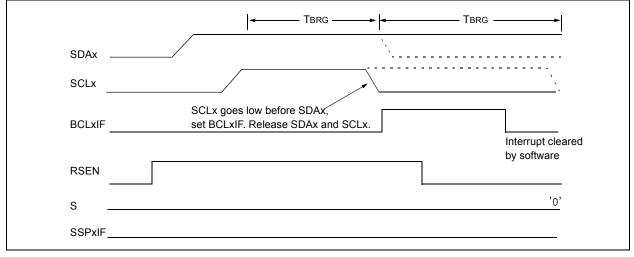

### 25.6.13.2 Bus Collision During a Repeated Start Condition

During a Repeated Start condition, a bus collision occurs if:

- a) A low level is sampled on SDAx when SCLx goes from low level to high level.

- SCLx goes low before SDAx is asserted low, indicating that another master is attempting to transmit a data '1'.

When the user releases SDAx and the pin is allowed to float high, the BRG is loaded with SSPxADD and counts down to zero. The SCLx pin is then deasserted and when sampled high, the SDAx pin is sampled. If SDAx is low, a bus collision has occurred (i.e., another master is attempting to transmit a data '0', Figure 25-35). If SDAx is sampled high, the BRG is reloaded and begins counting. If SDAx goes from high-to-low before the BRG times out, no bus collision occurs because no two masters can assert SDAx at exactly the same time.

If SCLx goes from high-to-low before the BRG times out and SDAx has not already been asserted, a bus collision occurs. In this case, another master is attempting to transmit a data '1' during the Repeated Start condition, see Figure 25-36.

If, at the end of the BRG time-out, both SCLx and SDAx are still high, the SDAx pin is driven low and the BRG is reloaded and begins counting. At the end of the count, regardless of the status of the SCLx pin, the SCLx pin is driven low and the Repeated Start condition is complete.

FIGURE 25-36: BUS COLLISION DURING A REPEATED START CONDITION (CASE 1)

#### 28.2 Low-Voltage Programming Entry Mode

The Low-Voltage Programming Entry mode allows the PIC16(L)F1826/27 devices to be programmed using VDD only, without high voltage. When the LVP bit of Configuration Word 2 is set to '1', the low-voltage ICSP programming entry is enabled. To disable the Low-Voltage ICSP mode, the LVP bit must be programmed to '0'.

Entry into the Low-Voltage Programming Entry mode requires the following steps:

- 1.  $\overline{\text{MCLR}}$  is brought to VIL.

- 2. A 32-bit key sequence is presented on ICSPDAT, while clocking ICSPCLK.

Once the key sequence is complete,  $\overline{\text{MCLR}}$  must be held at VIL for as long as Program/Verify mode is to be maintained.

If low-voltage programming is enabled (LVP = 1), the  $\overline{\text{MCLR}}$  Reset function is automatically enabled and cannot be disabled. See **Section 7.3 "MCLR"** for more information.

The LVP bit can only be reprogrammed to '0' by using the High-Voltage Programming mode.

#### 28.3 Common Programming Interfaces

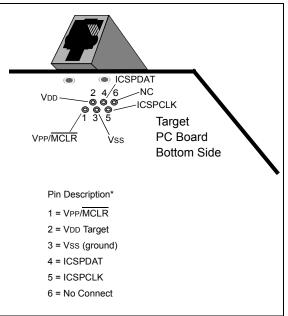

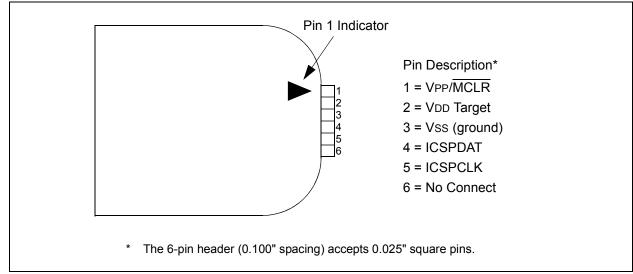

Connection to a target device is typically done through an ICSP<sup>™</sup> header. A commonly found connector on development tools is the RJ-11 in the 6P6C (6 pin, 6 connector) configuration. See Figure 28-2.

#### FIGURE 28-2: ICD RJ-11 STYLE CONNECTOR INTERFACE

Another connector often found in use with the PICkit<sup>™</sup> programmers is a standard 6-pin header with 0.1 inch spacing. Refer to Figure 28-3.

#### FIGURE 28-3: PICkit<sup>™</sup> STYLE CONNECTOR INTERFACE

| Operating Conditions: 1.8V < VDD < 5.5V, -40°C < TA < +125°C (unless otherwise stated). |         |                                           |      |      |      |       |                 |  |

|-----------------------------------------------------------------------------------------|---------|-------------------------------------------|------|------|------|-------|-----------------|--|

| Param<br>No.                                                                            | Sym.    | Characteristics                           | Min. | Тур. | Max. | Units | Comments        |  |

| CM01                                                                                    | Vioff   | Input Offset Voltage                      | —    | ±7.5 | ±60  | mV    | High Power Mode |  |

| CM02                                                                                    | Vicm    | Input Common Mode Voltage                 | 0    | _    | Vdd  | V     |                 |  |

| CM03*                                                                                   | CMRR    | Common Mode Rejection Ratio               |      | 50   |      | dB    |                 |  |

| CM04A                                                                                   |         | Response Time Rising Edge                 | —    | 400  | 800  | ns    | High Power Mode |  |

| CM04B                                                                                   | Troop   | Response Time Falling Edge                |      | 200  | 400  | ns    | High Power Mode |  |

| CM04C                                                                                   | Tresp   | Response Time Rising Edge                 | —    | 1200 |      | ns    | Low Power Mode  |  |

| CM04D                                                                                   |         | Response Time Falling Edge                | —    | 550  | _    | ns    |                 |  |

| CM05*                                                                                   | Tmc2ov  | Comparator Mode Change to<br>Output Valid | —    | —    | 10   | μS    |                 |  |

| CM06                                                                                    | Chyster | Comparator Hysteresis                     |      | 65   |      | mV    | Hysteresis ON   |  |

#### **TABLE 30-10: COMPARATOR SPECIFICATIONS**

\* These parameters are characterized but not tested.

#### TABLE 30-11: DIGITAL-TO-ANALOG CONVERTER (DAC) SPECIFICATIONS

| <b>Operating Conditions:</b> $1.8V < VDD < 5.5V$ , $-40^{\circ}C < TA < +125^{\circ}C$ (unless otherwise stated). |      |                              |      |        |       |       |          |

|-------------------------------------------------------------------------------------------------------------------|------|------------------------------|------|--------|-------|-------|----------|

| Param<br>No.                                                                                                      | Sym. | Characteristics              | Min. | Тур.   | Max.  | Units | Comments |

| DAC01*                                                                                                            | CLSB | Step Size                    | —    | VDD/32 |       | V     |          |

| DAC02*                                                                                                            | CACC | Absolute Accuracy            | —    | —      | ± 1/2 | LSb   |          |

| DAC03*                                                                                                            | CR   | Unit Resistor Value (R)      | —    | 5000   | _     | Ω     |          |

| DAC04*                                                                                                            | CST  | Settling Time <sup>(1)</sup> | _    | _      | 10    | μS    |          |

| * These parameters are characterized but not tested                                                               |      |                              |      |        |       |       |          |

These parameters are characterized but not tested.

Note 1: Settling time measured while DACR<4:0> transitions from '0000' to '1111'.

# PIC16(L)F1826/27

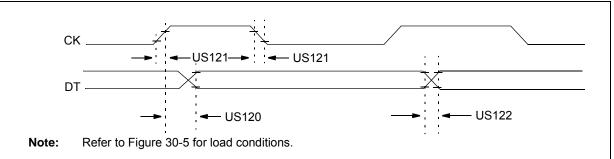

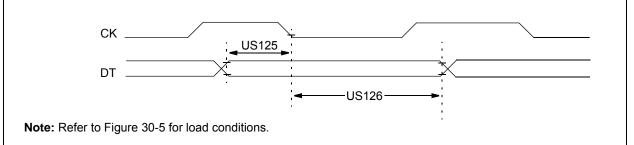

#### FIGURE 30-14: USART SYNCHRONOUS TRANSMISSION (MASTER/SLAVE) TIMING

#### TABLE 30-12: USART SYNCHRONOUS TRANSMISSION REQUIREMENTS

| Standard Operating Conditions (unless otherwise stated)Operating Temperature $-40^{\circ}C \le TA \le +125^{\circ}C$ |                              |                                         |          |      |       |            |  |  |

|----------------------------------------------------------------------------------------------------------------------|------------------------------|-----------------------------------------|----------|------|-------|------------|--|--|

| Param.<br>No.                                                                                                        | Symbol                       | Characteristic                          | Min.     | Max. | Units | Conditions |  |  |

| US120                                                                                                                | US120 TCKH2DTV               | V SYNC XMIT (Master and Slave)          | 3.0-5.5V | —    | 80    | ns         |  |  |

|                                                                                                                      | Clock high to data-out valid | 1.8-5.5V                                | —        | 100  | ns    |            |  |  |

| US121                                                                                                                | JS121 TCKRF                  | TCKRF Clock out rise time and fall time | 3.0-5.5V | —    | 45    | ns         |  |  |

|                                                                                                                      | (Master mode)                | 1.8-5.5V                                | —        | 50   | ns    |            |  |  |

| US122                                                                                                                | TDTRF                        | Data-out rise time and fall time        | 3.0-5.5V | —    | 45    | ns         |  |  |

|                                                                                                                      |                              |                                         | 1.8-5.5V | _    | 50    | ns         |  |  |

#### FIGURE 30-15: USART SYNCHRONOUS RECEIVE (MASTER/SLAVE) TIMING

#### TABLE 30-13: USART SYNCHRONOUS RECEIVE REQUIREMENTS

| Standard Operating Conditions (unless otherwise stated)Operating Temperature $-40^{\circ}C \le TA \le +125^{\circ}C$ |          |                                                                                |    |  |    |            |  |

|----------------------------------------------------------------------------------------------------------------------|----------|--------------------------------------------------------------------------------|----|--|----|------------|--|

| Param.<br>No.SymbolCharacteristicMin.Max.UnitsConditions                                                             |          |                                                                                |    |  |    | Conditions |  |

| US125                                                                                                                | TDTV2CKL | SYNC RCV (Master and Slave)<br>Data-hold before CK $\downarrow$ (DT hold time) | 10 |  | ns |            |  |

| US126                                                                                                                | TCKL2DTL | Data-hold after CK $\downarrow$ (DT hold time)                                 | 15 |  | ns |            |  |

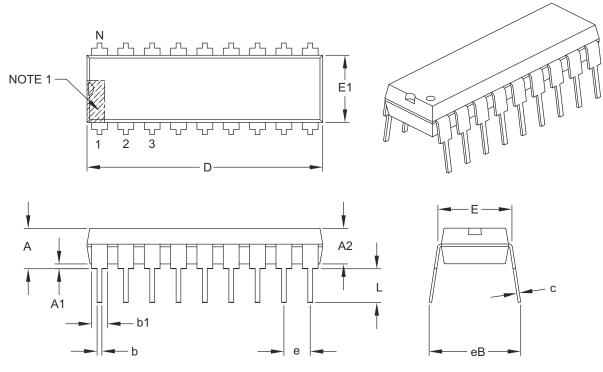

#### 33.2 Package Details

The following sections give the technical details of the packages.

#### 18-Lead Plastic Dual In-Line (P) – 300 mil Body [PDIP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | Units            | INCHES |          |      |  |

|----------------------------|------------------|--------|----------|------|--|

|                            | Dimension Limits | MIN    | NOM      | MAX  |  |

| Number of Pins             | N                | 18     |          |      |  |

| Pitch                      | e                |        | .100 BSC |      |  |

| Top to Seating Plane       | A                | -      | _        | .210 |  |

| Molded Package Thickness   | A2               | .115   | .130     | .195 |  |

| Base to Seating Plane      | A1               | .015   | _        | -    |  |

| Shoulder to Shoulder Width | E                | .300   | .310     | .325 |  |

| Molded Package Width       | E1               | .240   | .250     | .280 |  |

| Overall Length             | D                | .880   | .900     | .920 |  |

| Tip to Seating Plane       | L                | .115   | .130     | .150 |  |

| Lead Thickness             | С                | .008   | .010     | .014 |  |

| Upper Lead Width           | b1               | .045   | .060     | .070 |  |

| Lower Lead Width           | b                | .014   | .018     | .022 |  |

| Overall Row Spacing §      | eB               | -      | _        | .430 |  |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. § Significant Characteristic.

- 3. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing C04-007B