Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 16                                                                         |

| Program Memory Size        | 7KB (4K x 14)                                                              |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 384 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                |

| Data Converters            | A/D 12x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 18-SOIC (0.295", 7.50mm Width)                                             |

| Supplier Device Package    | 18-SOIC                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1827-i-so |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### PIC16(L)F1826/27 Family Types

|             | Program<br>Memory | -               | ata<br>nory            |                      | (ch)         | (ch)       | rs        | -bit)          |        |              | idge)              | idge)              |     |          |

|-------------|-------------------|-----------------|------------------------|----------------------|--------------|------------|-----------|----------------|--------|--------------|--------------------|--------------------|-----|----------|

| Device      | Words             | SRAM<br>(bytes) | Data EEPROM<br>(bytes) | 1/O's <sup>(1)</sup> | 10-bit ADC ( | CapSense ( | Comparato | Timers (8/16-l | EUSART | <b>dss</b> W | ECCP (Full-Bridge) | ECCP (Half-Bridge) | doo | SR Latch |

| PIC16LF1826 | 2K                | 256             | 256                    | 16                   | 12           | 12         | 2         | 2/1            | 1      | 1            | 1                  | _                  | _   | Yes      |

| PIC16F1826  | 2K                | 256             | 256                    | 16                   | 12           | 12         | 2         | 2/1            | 1      | 1            | 1                  | _                  | _   | Yes      |

| PIC16LF1827 | 4K                | 384             | 256                    | 16                   | 12           | 12         | 2         | 4/1            | 1      | 2            | 1                  | 1                  | 2   | Yes      |

| PIC16F1827  | 4K                | 384             | 256                    | 16                   | 12           | 12         | 2         | 4/1            | 1      | 2            | 1                  | 1                  | 2   | Yes      |

Note 1: One pin is input only.

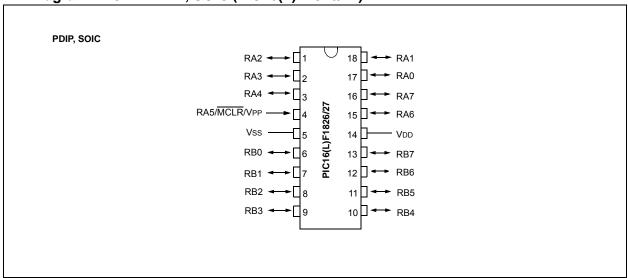

### Pin Diagram - 18-Pin PDIP, SOIC (PIC16(L)F1826/27)

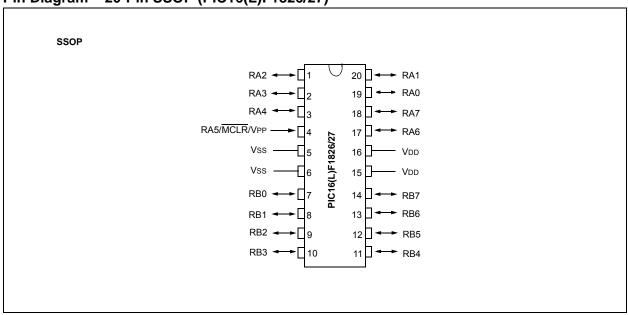

### Pin Diagram - 20-Pin SSOP (PIC16(L)F1826/27)

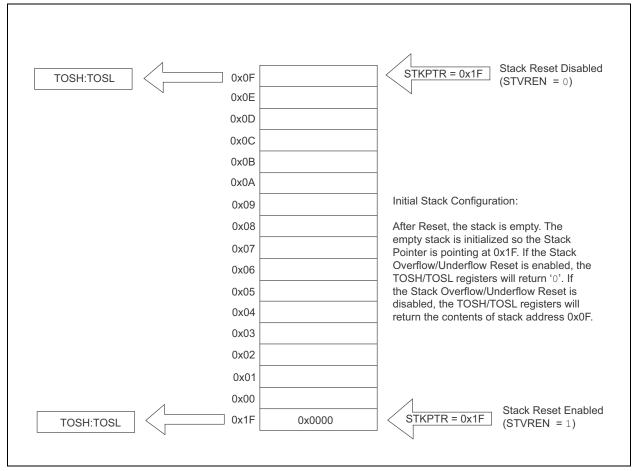

#### 3.4 Stack

All devices have a 16-level x 15-bit wide hardware stack (refer to Figures 3-5 through 3-8). The stack space is not part of either program or data space. The PC is PUSHed onto the stack when CALL or CALLW instructions are executed or an interrupt causes a branch. The stack is POPed in the event of a RETURN, RETLW or a RETFIE instruction execution. PCLATH is not affected by a PUSH or POP operation.

The stack operates as a circular buffer if the STVREN bit is programmed to '0' (Configuration Word 2). This means that after the stack has been PUSHed sixteen times, the seventeenth PUSH overwrites the value that was stored from the first PUSH. The eighteenth PUSH overwrites the second PUSH (and so on). The STKOVF and STKUNF flag bits will be set on an Overflow/Underflow, regardless of whether the Reset is enabled.

Note 1: There are no instructions/mnemonics called PUSH or POP. These are actions that occur from the execution of the CALL, CALLW, RETURN, RETLW and RETFIE instructions or the vectoring to an interrupt address.

#### 3.4.1 ACCESSING THE STACK

The stack is available through the TOSH, TOSL and STKPTR registers. STKPTR is the current value of the Stack Pointer. TOSH:TOSL register pair points to the TOP of the stack. Both registers are read/writable. TOS is split into TOSH and TOSL due to the 15-bit size of the PC. To access the stack, adjust the value of STKPTR, which will position TOSH:TOSL, then read/write to TOSH:TOSL. STKPTR is 5 bits to allow detection of overflow and underflow.

**Note:** Care should be taken when modifying the STKPTR while interrupts are enabled.

During normal program operation, CALL, CALLW and Interrupts will increment STKPTR while RETLW, RETURN, and RETFIE will decrement STKPTR. At any time STKPTR can be inspected to see how much stack is left. The STKPTR always points at the currently used place on the stack. Therefore, a CALL or CALLW will increment the STKPTR and then write the PC, and a return will unload the PC and then decrement STKPTR.

Reference Figure 3-5 through Figure 3-8 for examples of accessing the stack.

FIGURE 3-5: ACCESSING THE STACK EXAMPLE 1

#### REGISTER 4-1: CONFIGURATION WORD 1 (CONTINUED)

- bit 2-0 FOSC<2:0>: Oscillator Selection bits

- 111 = ECH: External Clock, High-Power mode (4-20 MHz): device clock supplied to CLKIN pin

- 110 = ECM: External Clock, Medium-Power mode (0.5-4 MHz): device clock supplied to CLKIN pin

- 101 = ECL: External Clock, Low-Power mode (0-0.5 MHz): device clock supplied to CLKIN pin

- 100 = INTOSC oscillator: I/O function on CLKIN pin

- 011 = EXTRC oscillator: External RC circuit connected to CLKIN pin

- 010 = HS oscillator: High-speed crystal/resonator connected between OSC1 and OSC2 pins

- 001 = XT oscillator: Crystal/resonator connected between OSC1 and OSC2 pins

- 000 = LP oscillator: Low-power crystal connected between OSC1 and OSC2 pins

NOTES:

#### 16.1 ADC Configuration

When configuring and using the ADC the following functions must be considered:

- · Port configuration

- · Channel selection

- · ADC voltage reference selection

- · ADC conversion clock source

- · Interrupt control

- · Result formatting

#### 16.1.1 PORT CONFIGURATION

The ADC can be used to convert both analog and digital signals. When converting analog signals, the I/O pin should be configured for analog by setting the associated TRIS and ANSEL bits. Refer to **Section 12.0 "I/O Ports"** for more information.

**Note:** Analog voltages on any pin that is defined as a digital input may cause the input buffer to conduct excess current.

#### 16.1.2 CHANNEL SELECTION

There are up to 15 channel selections available:

- AN<11:0> pins

- · Temperature Indicator

- DAC Output

- · FVR (Fixed Voltage Reference) Output

Refer to Section 14.0 "Fixed Voltage Reference (FVR)" and Section 15.0 "Temperature Indicator Module" for more information on these channel selections.

The CHS bits of the ADCON0 register determine which channel is connected to the sample and hold circuit.

When changing channels, a delay is required before starting the next conversion. Refer to **Section 16.2** "**ADC Operation**" for more information.

#### 16.1.3 ADC VOLTAGE REFERENCE

The ADPREF bits of the ADCON1 register provides control of the positive voltage reference. The positive voltage reference can be:

- VREF+ pin

- VDD

- FVR 2.048V

- FVR 4.096V (Not available on LF devices)

The ADNREF bits of the ADCON1 register provides control of the negative voltage reference. The negative voltage reference can be:

- VREF- pin

- Vss

See Section 14.0 "Fixed Voltage Reference (FVR)" for more details on the fixed voltage reference.

#### 16.1.4 CONVERSION CLOCK

The source of the conversion clock is software selectable via the ADCS bits of the ADCON1 register. There are seven possible clock options:

- Fosc/2

- Fosc/4

- Fosc/8

- Fosc/16

- Fosc/32

- Fosc/64

- · FRC (dedicated internal oscillator)

The time to complete one bit conversion is defined as TAD. One full 10-bit conversion requires 11.5 TAD periods as shown in Figure 16-2.

For correct conversion, the appropriate TAD specification must be met. Refer to the A/D conversion requirements in **Section 30.0** "**Electrical Specifications**" for more information. Table 16-1 gives examples of appropriate ADC clock selections.

Note: Unless using the FRC, any changes in the system clock frequency will change the ADC clock frequency, which may adversely affect the ADC result.

#### REGISTER 16-2: ADCON1: A/D CONTROL REGISTER 1

| R/W-0/0 | R/W-0/0   | R/W-0/0 | R/W-0/0 | U-0 | R/W-0/0 | R/W-0/0     | R/W-0/0 |  |

|---------|-----------|---------|---------|-----|---------|-------------|---------|--|

| ADFM    | ADCS<2:0> |         |         | _   | ADNREF  | ADPREF<1:0> |         |  |

| bit 7   |           |         |         |     |         |             | bit 0   |  |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7 ADFM: A/D Result Format Select bit

1 = Right justified. Six Most Significant bits of ADRESH are set to '0' when the conversion result is loaded.

0 = Left justified. Six Least Significant bits of ADRESL are set to '0' when the conversion result is loaded.

bit 6-4 ADCS<2:0>: A/D Conversion Clock Select bits

000 = Fosc/2

001 = Fosc/8

010 = Fosc/32

011 = FRC (clock supplied from a dedicated RC oscillator)

100 = Fosc/4

101 = Fosc/16

110 = Fosc/64

111 = FRC (clock supplied from a dedicated RC oscillator)

bit 3 **Unimplemented:** Read as '0'

bit 2 ADNREF: A/D Negative Voltage Reference Configuration bit

0 = VREF- is connected to VSS

1 = VREF- is connected to external VREF- pin<sup>(1)</sup>

bit 1-0 ADPREF<1:0>: A/D Positive Voltage Reference Configuration bits

00 = VREF+ is connected to VDD

01 = Reserved

10 = VREF+ is connected to external VREF+ pin<sup>(1)</sup>

11 = VREF+ is connected to internal Fixed Voltage Reference (FVR) module<sup>(1)</sup>

**Note 1:** When selecting the FVR or the VREF+ pin as the source of the positive reference, be aware that a minimum voltage specification exists. See **Section 30.0 "Electrical Specifications"** for details.

#### REGISTER 16-3: ADRESH: ADC RESULT REGISTER HIGH (ADRESH) ADFM = 0

| R/W-x/u    | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u |  |

|------------|---------|---------|---------|---------|---------|---------|---------|--|

| ADRES<9:2> |         |         |         |         |         |         |         |  |

| bit 7      |         |         |         |         |         |         | bit 0   |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

bit 7-0 **ADRES<9:2>**: ADC Result Register bits Upper 8 bits of 10-bit conversion result

#### REGISTER 16-4: ADRESL: ADC RESULT REGISTER LOW (ADRESL) ADFM = 0

| R/W-x/u    | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u |

|------------|---------|---------|---------|---------|---------|---------|---------|

| ADRES<1:0> |         | _       | _       | _       | _       | _       | _       |

| bit 7      |         |         |         |         |         |         | bit 0   |

Legend:R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'u = Bit is unchangedx = Bit is unknown-n/n = Value at POR and BOR/Value at all other Resets'1' = Bit is set'0' = Bit is cleared

bit 7-6 ADRES<1:0>: ADC Result Register bits

Lower 2 bits of 10-bit conversion result

bit 5-0 **Reserved**: Do not use.

#### 16.4 A/D Acquisition Requirements

For the ADC to meet its specified accuracy, the charge holding capacitor (Chold) must be allowed to fully charge to the input channel voltage level. The Analog Input model is shown in Figure 16-4. The source impedance (Rs) and the internal sampling switch (Rss) impedance directly affect the time required to charge the capacitor Chold. The sampling switch (Rss) impedance varies over the device voltage (VDD), refer to Figure 16-4. The maximum recommended impedance for analog sources is  $10~\mathrm{k}\Omega$ . As the

source impedance is decreased, the acquisition time may be decreased. After the analog input channel is selected (or changed), an A/D acquisition must be done before the conversion can be started. To calculate the minimum acquisition time, Equation 16-1 may be used. This equation assumes that 1/2 LSb error is used (1,024 steps for the ADC). The 1/2 LSb error is the maximum error allowed for the ADC to meet its specified resolution.

#### **EQUATION 16-1: ACQUISITION TIME EXAMPLE**

Assumptions: Temperature =  $50^{\circ}$ C and external impedance of  $10k\Omega 5.0V VDD$

$$TACQ = Amplifier Settling Time + Hold Capacitor Charging Time + Temperature Coefficient$$

=  $TAMP + TC + TCOFF$

=  $2\mu s + TC + [(Temperature - 25°C)(0.05\mu s/°C)]$

The value for TC can be approximated with the following equations:

$$V_{APPLIED}\left(1 - \frac{1}{(2^{n+1}) - 1}\right) = V_{CHOLD}$$

;[1] VCHOLD charged to within 1/2 lsb

$$V_{APPLIED}\left(1-e^{\frac{-Tc}{RC}}\right) = V_{CHOLD}$$

;[2] VCHOLD charge response to VAPPLIED

$$V_{APPLIED}\left(1 - e^{\frac{-Tc}{RC}}\right) = V_{APPLIED}\left(1 - \frac{1}{(2^{n+1}) - 1}\right) \quad ; combining [1] \ and [2]$$

*Note:* Where n = number of bits of the ADC.

Solving for TC:

$$TC = -C_{HOLD}(RIC + RSS + RS) \ln(1/511)$$

$$= -10pF(1k\Omega + 7k\Omega + 10k\Omega) \ln(0.001957)$$

$$= 1.12\mu s$$

Therefore:

$$TACQ = 2\mu s + 1.12\mu s + [(50^{\circ}C - 25^{\circ}C)(0.05\mu s/^{\circ}C)]$$

= 4.42\mu s

- Note 1: The reference voltage (VREF) has no effect on the equation, since it cancels itself out.

- 2: The charge holding capacitor (CHOLD) is not discharged after each conversion.

- **3:** The maximum recommended impedance for analog sources is 10 kΩ. This is required to meet the pin leakage specification.

NOTES:

TABLE 21-5: SUMMARY OF REGISTERS ASSOCIATED WITH TIMER1

| Name    | Bit 7       | Bit 6          | Bit 5      | Bit 4         | Bit 3          | Bit 2     | Bit 1  | Bit 0  | Register on Page |

|---------|-------------|----------------|------------|---------------|----------------|-----------|--------|--------|------------------|

| ANSELB  | ANSB7       | ANSB6          | ANSB5      | ANSB4         | ANSB3          | ANSB2     | ANSB1  | _      | 128              |

| CCP1CON | PxM1        | PxM0           | DCxB1      | DCxB0         | CCPxM3         | CCPxM2    | CCPxM1 | CCPxM0 | 226              |

| INTCON  | GIE         | PEIE           | TMR0IE     | INTE          | IOCIE          | TMR0IF    | INTF   | IOCIF  | 86               |

| PIE1    | TMR1GIE     | ADIE           | RCIE       | TXIE          | SSP1IE         | CCP1IE    | TMR2IE | TMR1IE | 87               |

| PIR1    | TMR1GIF     | ADIF           | RCIF       | TXIF          | SSP1IF         | CCP1IF    | TMR2IF | TMR1IF | 91               |

| PORTB   | RB7         | RB6            | RB5        | RB4           | RB3            | RB2       | RB1    | RB0    | 127              |

| TMR1H   | Holding Reg | gister for the | Most Signi | ficant Byte o | of the 16-bit  | TMR1 Regi | ster   |        | 177*             |

| TMR1L   | Holding Reg | gister for the | Least Sign | ificant Byte  | of the 16-bit  | TMR1 Reg  | ister  |        | 177*             |

| TRISB   | TRISB7      | TRISB6         | TRISB5     | TRISB4        | TRISB3         | TRISB2    | TRISB1 | TRISB0 | 127              |

| T1CON   | TMR1CS1     | TMR1CS0        | T1CKPS1    | T1CKPS0       | T10SCEN        | T1SYNC    | _      | TMR10N | 185              |

| T1GCON  | TMR1GE      | T1GPOL         | T1GTM      | T1GSPM        | T1GGO/<br>DONE | T1GVAL    | T1GSS1 | T1GSS0 | 186              |

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used by the Timer1 module.

<sup>\*</sup> Page provides register information.

TABLE 22-1: SUMMARY OF REGISTERS ASSOCIATED WITH TIMER2/4/6

| Name                | Bit 7                                                        | Bit 6           | Bit 5         | Bit 4                  | Bit 3    | Bit 2  | Bit 1   | Bit 0   | Register on Page |

|---------------------|--------------------------------------------------------------|-----------------|---------------|------------------------|----------|--------|---------|---------|------------------|

| INTCON              | GIE                                                          | PEIE            | TMR0IE        | INTE                   | IOCIE    | TMR0IF | INTF    | IOCIF   | 91               |

| PIE1                | TMR1GIE                                                      | ADIE            | RCIE          | TXIE                   | SSP1IE   | CCP1IE | TMR2IE  | TMR1IE  | 92               |

| PIR1                | TMR1GIF                                                      | ADIF            | RCIF          | TXIF                   | SSP1IF   | CCP1IF | TMR2IF  | TMR1IF  | 96               |

| PIE3 <sup>(1)</sup> | _                                                            | _               | CCP4IE        | CCP3IE                 | TMR6IE   | _      | TMR4IE  | _       | 94               |

| PIR3 <sup>(1)</sup> | _                                                            | _               | CCP4IF        | CCP3IF                 | TMR6IF   | _      | TMR4IF  | _       | 98               |

| PR2                 | Timer2 Module Period Register                                |                 |               |                        |          |        |         |         |                  |

| PR4                 | Timer4 Module Period Register                                |                 |               |                        |          |        |         |         | 189*             |

| PR6                 | Timer6 Mode                                                  | ule Period Re   | gister        |                        |          |        |         |         | 189*             |

| T2CON               | _                                                            | T2OUTPS3        | T2OUTPS2      | T2OUTPS1               | T2OUTPS0 | TMR2ON | T2CKPS1 | T2CKPS0 | 191              |

| T4CON               | _                                                            | T4OUTPS3        | T4OUTPS2      | T4OUTPS1               | T4OUTPS0 | TMR4ON | T4CKPS1 | T4CKPS0 | 191              |

| T6CON               | _                                                            | T6OUTPS3        | T6OUTPS2      | T6OUTPS1               | T6OUTPS0 | TMR6ON | T6CKPS1 | T6CKPS0 | 191              |

| TMR2                | Holding Register for the 8-bit TMR2 Time Base                |                 |               |                        |          |        |         |         | 189*             |

| TMR4                | Holding Register for the 8-bit TMR4 Time Base <sup>(1)</sup> |                 |               |                        |          |        |         |         | 189*             |

| TMR6                | Holding Reg                                                  | ister for the 8 | -bit TMR6 Tin | ne Base <sup>(1)</sup> |          |        |         |         | 189*             |

**Legend:** — = unimplemented read as '0'. Shaded cells are not used for Timer2 module.

Note 1: PIC16(L)F1827 only.

<sup>\*</sup> Page provides register information.

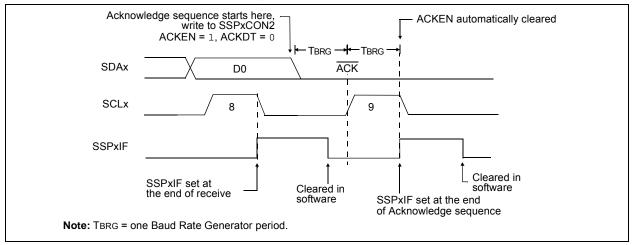

### 25.6.8 ACKNOWLEDGE SEQUENCE TIMING

An Acknowledge sequence is enabled by setting the Acknowledge Sequence Enable bit, ACKEN bit of the SSPxCON2 register. When this bit is set, the SCLx pin is pulled low and the contents of the Acknowledge data bit are presented on the SDAx pin. If the user wishes to generate an Acknowledge, then the ACKDT bit should be cleared. If not, the user should set the ACKDT bit before starting an Acknowledge sequence. The Baud Rate Generator then counts for one rollover period (TBRG) and the SCLx pin is deasserted (pulled high). When the SCLx pin is sampled high (clock arbitration), the Baud Rate Generator counts for TBRG. The SCLx pin is then pulled low. Following this, the ACKEN bit is automatically cleared, the Baud Rate Generator is turned off and the MSSPx module then goes into Idle mode (Figure 25-29).

#### 25.6.8.1 WCOL Status Flag

If the user writes the SSPxBUF when an Acknowledge sequence is in progress, then WCOL is set and the contents of the buffer are unchanged (the write does not occur).

#### 25.6.9 STOP CONDITION TIMING

A Stop bit is asserted on the SDAx pin at the end of a receive/transmit by setting the Stop Sequence Enable bit, PEN bit of the SSPxCON2 register. At the end of a receive/transmit, the SCLx line is held low after the falling edge of the ninth clock. When the PEN bit is set, the master will assert the SDAx line low. When the SDAx line is sampled low, the Baud Rate Generator is reloaded and counts down to '0'. When the Baud Rate Generator times out, the SCLx pin will be brought high and one TBRG (Baud Rate Generator rollover count) later, the SDAx pin will be deasserted. When the SDAx pin is sampled high while SCLx is high, the P bit of the SSPxSTAT register is set. A TBRG later, the PEN bit is cleared and the SSPxIF bit is set (Figure 25-30).

#### 25.6.9.1 WCOL Status Flag

If the user writes the SSPxBUF when a Stop sequence is in progress, then the WCOL bit is set and the contents of the buffer are unchanged (the write does not occur).

FIGURE 25-30: ACKNOWLEDGE SEQUENCE WAVEFORM

## 26.3 EUSART Baud Rate Generator (BRG)

The Baud Rate Generator (BRG) is an 8-bit or 16-bit timer that is dedicated to the support of both the asynchronous and synchronous EUSART operation. By default, the BRG operates in 8-bit mode. Setting the BRG16 bit of the BAUDCON register selects 16-bit mode.

The SPBRGH, SPBRGL register pair determines the period of the free running baud rate timer. In Asynchronous mode the multiplier of the baud rate period is determined by both the BRGH bit of the TXSTA register and the BRG16 bit of the BAUDCON register. In Synchronous mode, the BRGH bit is ignored.

Table 26-3 contains the formulas for determining the baud rate. Example 26-1 provides a sample calculation for determining the baud rate and baud rate error.

Typical baud rates and error values for various asynchronous modes have been computed for your convenience and are shown in Table 26-3. It may be advantageous to use the high baud rate (BRGH = 1), or the 16-bit BRG (BRG16 = 1) to reduce the baud rate error. The 16-bit BRG mode is used to achieve slow baud rates for fast oscillator frequencies.

Writing a new value to the SPBRGH, SPBRGL register pair causes the BRG timer to be reset (or cleared). This ensures that the BRG does not wait for a timer overflow before outputting the new baud rate.

If the system clock is changed during an active receive operation, a receive error or data loss may result. To avoid this problem, check the status of the RCIDL bit to make sure that the receive operation is Idle before changing the system clock.

### EXAMPLE 26-1: CALCULATING BAUD RATE ERROR

For a device with Fosc of 16 MHz, desired baud rate of 9600, Asynchronous mode, 8-bit BRG:

$$Desired \ Baud \ Rate = \frac{FOSC}{64([SPBRGH:SPBRGL] + 1)}$$

Solving for SPBRGH:SPBRGL:

$$X = \frac{Fosc}{\frac{Desired Baud Rate}{64}} - 1$$

$$= \frac{\frac{16000000}{9600}}{\frac{9600}{64}} - 1$$

$$= [25.042] = 25$$

$$Calculated Baud Rate = \frac{16000000}{64(25+1)}$$

$$= 9615$$

$$Error = \frac{Calc. Baud Rate - Desired Baud Rate}{Desired Baud Rate}$$

$$= \frac{(9615 - 9600)}{9600} = 0.16\%$$

#### FIGURE 26-7: AUTO-WAKE-UP BIT (WUE) TIMING DURING NORMAL OPERATION

#### FIGURE 26-8: AUTO-WAKE-UP BIT (WUE) TIMINGS DURING SLEEP

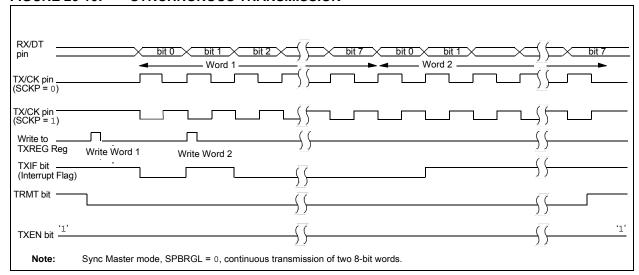

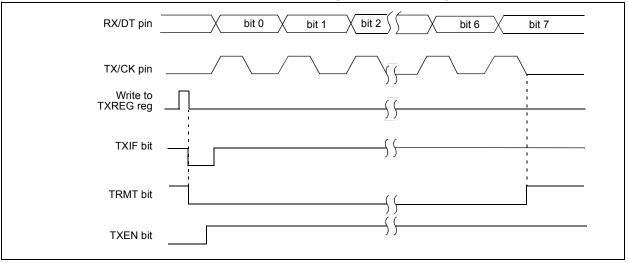

#### FIGURE 26-10: SYNCHRONOUS TRANSMISSION

#### FIGURE 26-11: SYNCHRONOUS TRANSMISSION (THROUGH TXEN)

## 26.4.2.3 EUSART Synchronous Slave Reception

The operation of the Synchronous Master and Slave modes is identical (Section 26.4.1.5 "Synchronous Master Reception"), with the following exceptions:

- Sleep

- CREN bit is always set, therefore the receiver is never Idle

- · SREN bit, which is a "don't care" in Slave mode

A character may be received while in Sleep mode by setting the CREN bit prior to entering Sleep. Once the word is received, the RSR register will transfer the data to the RCREG register. If the RCIE enable bit is set, the interrupt generated will wake the device from Sleep and execute the next instruction. If the GIE bit is also set, the program will branch to the interrupt vector.

### 26.4.2.4 Synchronous Slave Reception Set-up:

- Set the SYNC and SPEN bits and clear the CSRC bit.

- Clear the ANSEL bit for both the CK and DT pins (if applicable).

- If interrupts are desired, set the RCIE bit of the PIE1 register and the GIE and PEIE bits of the INTCON register.

- 4. If 9-bit reception is desired, set the RX9 bit.

- 5. Set the CREN bit to enable reception.

- The RCIF bit will be set when reception is complete. An interrupt will be generated if the RCIE bit was set.

- If 9-bit mode is enabled, retrieve the Most Significant bit from the RX9D bit of the RCSTA register.

- 8. Retrieve the 8 Least Significant bits from the receive FIFO by reading the RCREG register.

- If an overrun error occurs, clear the error by either clearing the CREN bit of the RCSTA register or by clearing the SPEN bit which resets the EUSART.

TABLE 26-10: SUMMARY OF REGISTERS ASSOCIATED WITH SYNCHRONOUS SLAVE RECEPTION

| Name    | Bit 7   | Bit 6   | Bit 5  | Bit 4                 | Bit 3                  | Bit 2  | Bit 1  | Bit 0   | Register<br>on Page |

|---------|---------|---------|--------|-----------------------|------------------------|--------|--------|---------|---------------------|

| APFCON0 | RXDTSEL | SDO1SEL | SS1SEL | P2BSEL <sup>(1)</sup> | CCP2SEL <sup>(1)</sup> | P1DSEL | P1CSEL | CCP1SEL | 119                 |

| APFCON1 | 1       |         | 1      | _                     | _                      | _      |        | TXCKSEL | 119                 |

| BAUDCON | ABDOVF  | RCIDL   | 1      | SCKP                  | BRG16                  | _      | WUE    | ABDEN   | 296                 |

| INTCON  | GIE     | PEIE    | TMR0IE | INTE                  | IOCIE                  | TMR0IF | INTF   | IOCIF   | 86                  |

| PIE1    | TMR1GIE | ADIE    | RCIE   | TXIE                  | SSPIE                  | CCP1IE | TMR2IE | TMR1IE  | 87                  |

| PIR1    | TMR1GIF | ADIF    | RCIF   | TXIF                  | SSPIF                  | CCP1IF | TMR2IF | TMR1IF  | 91                  |

| RCREG   |         |         | EU     | SART Recei            | ve Data Regis          | ter    |        |         | 290*                |

| RCSTA   | SPEN    | RX9     | SREN   | CREN                  | ADDEN                  | FERR   | OERR   | RX9D    | 295                 |

| TRISB   | TRISB7  | TRISB6  | TRISB5 | TRISB4                | TRISB3                 | TRISB2 | TRISB1 | TRISB0  | 127                 |

| TXSTA   | CSRC    | TX9     | TXEN   | SYNC                  | SENDB                  | BRGH   | TRMT   | TX9D    | 294                 |

Legend: — = unimplemented location, read as '0'. Shaded cells are not used for Synchronous Slave Reception.

Note 1: PIC16(L)F1827 only.

<sup>\*</sup> Page provides register information.

#### 27.1 Analog MUX

The capacitive sensing module can monitor up to 12 inputs. The capacitive sensing inputs are defined as CPS<11:0>. To determine if a frequency change has occurred the user must:

- Select the appropriate CPS pin by setting the CPSCH<3:0> bits of the CPSCON1 register

- · Set the corresponding ANSEL bit

- · Set the corresponding TRIS bit

- · Run the software algorithm

Selection of the CPSx pin while the module is enabled will cause the capacitive sensing oscillator to be on the CPSx pin. Failure to set the corresponding ANSEL and TRIS bits can cause the capacitive sensing oscillator to stop, leading to false frequency readings.

#### 27.2 Capacitive Sensing Oscillator

The capacitive sensing oscillator consists of a constant current source and a constant current sink, to produce a triangle waveform. The CPSOUT bit of the CPSCON0 register shows the status of the capacitive sensing oscillator, whether it is a sinking or sourcing current. The oscillator is designed to drive a capacitive load (single PCB pad) and at the same time, be a clock source to either Timer0 or Timer1. The oscillator has three different current settings as defined by CPSRNG<1:0> of the CPSCON0 register. The different current settings for the oscillator serve two purposes:

- Maximize the number of counts in a timer for a fixed time base

- Maximize the count differential in the timer during a change in frequency

#### 27.3 Timer resources

To measure the change in frequency of the capacitive sensing oscillator, a fixed time base is required. For the period of the fixed time base, the capacitive sensing oscillator is used to clock either Timer0 or Timer1. The frequency of the capacitive sensing oscillator is equal to the number of counts in the timer divided by the period of the fixed time base.

#### 27.4 Fixed Time Base

To measure the frequency of the capacitive sensing oscillator, a fixed time base is required. Any timer resource or software loop can be used to establish the fixed time base. It is up to the end user to determine the method in which the fixed time base is generated.

**Note:** The fixed time base can not be generated by the timer resource that the capacitive sensing oscillator is clocking.

#### 27.4.1 TIMER0

To select Timer0 as the timer resource for the capacitive sensing module:

- · Set the T0XCS bit of the CPSCON0 register

- · Clear the TMR0CS bit of the OPTION register

When Timer0 is chosen as the timer resource, the capacitive sensing oscillator will be the clock source for Timer0. Refer to **Section 20.0 "Timer0 Module"** for additional information.

#### 27.4.2 TIMER1

To select Timer1 as the timer resource for the capacitive sensing module, set the TMR1CS<1:0> of the T1CON register to '11'. When Timer1 is chosen as the timer resource, the capacitive sensing oscillator will be the clock source for Timer1. Because the Timer1 module has a gate control, developing a time base for the frequency measurement can be simplified by using the Timer0 overflow flag.

It is recommend that the Timer0 overflow flag, in conjunction with the Toggle mode of the Timer1 gate, be used to develop the fixed time base required by the software portion of the capacitive sensing module. Refer to **Section 21.6.3 "Timer1 Gate Toggle Mode"** for additional information.

TABLE 27-1: TIMER1 ENABLE FUNCTION

| TMR10N | TMR1GE | Timer1 Operation       |

|--------|--------|------------------------|

| 0      | 0      | Off                    |

| 0      | 1      | Off                    |

| 1      | 0      | On                     |

| 1      | 1      | Count Enabled by input |

### 30.1 DC Characteristics: PIC16(L)F1826/27-I/E (Industrial, Extended)

| PIC16LF       | 1826/27 |                                                           | Standard Operating Conditions (unless otherwise stated)  Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for industrial $-40^{\circ}\text{C} \le \text{TA} \le +125^{\circ}\text{C}$ for extended |                                                                                                                                                                                                                                     |             |       |                                                                |  |  |

|---------------|---------|-----------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-------|----------------------------------------------------------------|--|--|

| PIC16F1       | 1826/27 |                                                           |                                                                                                                                                                                                                                     | Standard Operating Conditions (unless otherwise stated)  Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for industrial $-40^{\circ}\text{C} \le \text{TA} \le +125^{\circ}\text{C}$ for extended |             |       |                                                                |  |  |

| Param.<br>No. | Sym.    | Characteristic                                            | Min.                                                                                                                                                                                                                                | Тур†                                                                                                                                                                                                                                | Max.        | Units | Conditions                                                     |  |  |

| D001          | VDD     | Supply Voltage                                            |                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                     |             |       |                                                                |  |  |

|               |         | PIC16LF1826/27                                            | 1.8<br>2.5                                                                                                                                                                                                                          | 1 1                                                                                                                                                                                                                                 | 3.6<br>3.6  | V     | Fosc ≤ 16 MHz:<br>Fosc ≤ 32 MHz ( <b>NOTE 2</b> )              |  |  |

| D001          |         | PIC16F1826/27                                             | 1.8<br>2.5                                                                                                                                                                                                                          |                                                                                                                                                                                                                                     | 5.5<br>5.5  | V     | Fosc ≤ 16 MHz:<br>Fosc ≤ 32 MHz ( <b>NOTE 2</b> )              |  |  |

| D002*         | VDR     | RAM Data Retention Voltage <sup>(1)</sup>                 |                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                     |             |       |                                                                |  |  |

|               |         | PIC16LF1826/27                                            | 1.5                                                                                                                                                                                                                                 | -                                                                                                                                                                                                                                   | _           | V     | Device in Sleep mode                                           |  |  |

| D002*         |         | PIC16F1826/27                                             | 1.7                                                                                                                                                                                                                                 | _                                                                                                                                                                                                                                   | _           | V     | Device in Sleep mode                                           |  |  |

|               | VPOR*   | Power-on Reset Release Voltage                            | _                                                                                                                                                                                                                                   | 1.6                                                                                                                                                                                                                                 | _           | V     |                                                                |  |  |

|               | VPORR*  | Power-on Reset Rearm Voltage                              |                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                     |             |       |                                                                |  |  |

|               |         | PIC16LF1826/27                                            | _                                                                                                                                                                                                                                   | 8.0                                                                                                                                                                                                                                 | _           | V     | Device in Sleep mode                                           |  |  |

|               |         | PIC16F1826/27                                             |                                                                                                                                                                                                                                     | 1.7                                                                                                                                                                                                                                 | _           | V     | Device in Sleep mode                                           |  |  |

| D003          | VADFVR  | Fixed Voltage Reference Voltage for ADC                   | -8<br>-8<br>-8                                                                                                                                                                                                                      | _<br>_<br>_                                                                                                                                                                                                                         | 6<br>6<br>6 | %     | 1.024V, VDD ≥ 2.5V<br>2.048V, VDD ≥ 2.5V<br>4.096V, VDD ≥ 4.75 |  |  |

| D003A         | VCDAFVR | Fixed Voltage Reference Voltage for Comparator and DAC    | -11<br>-11<br>-11                                                                                                                                                                                                                   | _<br>_<br>_                                                                                                                                                                                                                         | 7<br>7<br>7 | %     | 1.024V, VDD ≥ 2.5V<br>2.048V, VDD ≥ 2.5V<br>4.096V, VDD ≥ 4.75 |  |  |

| D004*         | SVDD    | VDD Rise Rate to ensure internal<br>Power-on Reset signal | 0.05                                                                                                                                                                                                                                | ı                                                                                                                                                                                                                                   | _           | V/ms  | See Section 7.1 "Power-on Reset (POR)" for details.            |  |  |

<sup>\*</sup> These parameters are characterized but not tested.

Note 1: This is the limit to which VDD can be lowered in Sleep mode without losing RAM data.

<sup>†</sup> Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

<sup>2:</sup> PLL required for 32 MHz operation.

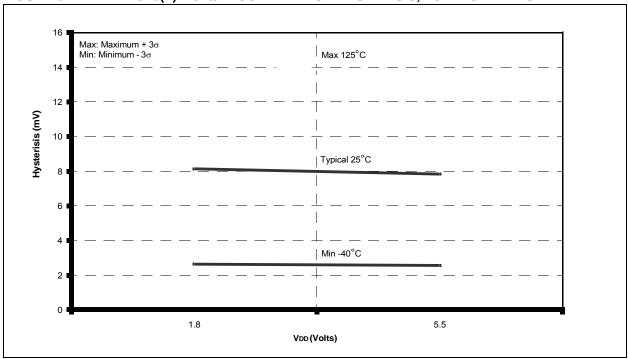

FIGURE 31-11: PIC16(L)F1826/27 COMPARATOR HYSTERISIS, LOW-POWER MODE

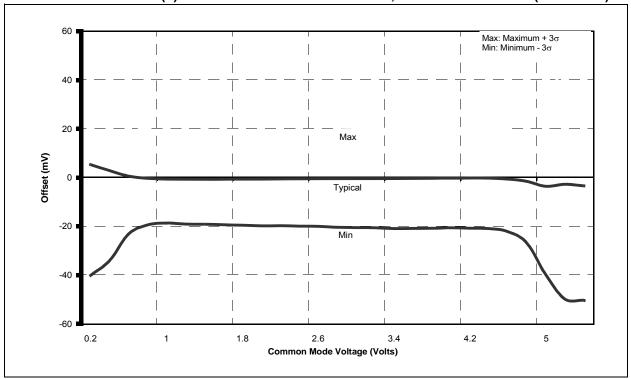

FIGURE 31-12: PIC16(L)F1826/27 COMPARATOR OFFSET, HIGH-POWER MODE (VDD = 5.5V)

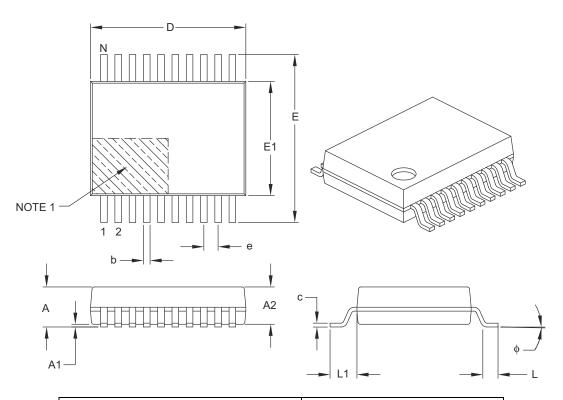

### 20-Lead Plastic Shrink Small Outline (SS) - 5.30 mm Body [SSOP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units    |          | MILLIMETERS | 3    |  |  |

|--------------------------|----------|----------|-------------|------|--|--|

| Dimension                | n Limits | MIN      | NOM         | MAX  |  |  |

| Number of Pins           | N        | 20       |             |      |  |  |

| Pitch                    | е        | 0.65 BSC |             |      |  |  |

| Overall Height           | Α        | _        | _           | 2.00 |  |  |

| Molded Package Thickness | A2       | 1.65     | 1.75        | 1.85 |  |  |

| Standoff                 | A1       | 0.05     | _           | _    |  |  |

| Overall Width            | Е        | 7.40     | 7.80        | 8.20 |  |  |

| Molded Package Width     | E1       | 5.00     | 5.30        | 5.60 |  |  |

| Overall Length           | D        | 6.90     | 7.20        | 7.50 |  |  |

| Foot Length              | L        | 0.55     | 0.75        | 0.95 |  |  |

| Footprint                | L1       | 1.25 REF |             |      |  |  |

| Lead Thickness           | С        | 0.09     | _           | 0.25 |  |  |

| Foot Angle               | ф        | 0°       | 4°          | 8°   |  |  |

| Lead Width               | b        | 0.22     | _           | 0.38 |  |  |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.20 mm per side.

- 3. Dimensioning and tolerancing per ASME Y14.5M.

- ${\tt BSC: Basic \ Dimension. \ Theoretically \ exact \ value \ shown \ without \ tolerances.}$

- REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-072B