Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XF

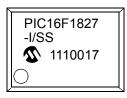

| Product Status             | Active                                                                      |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 32MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                           |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 16                                                                          |

| Program Memory Size        | 7KB (4K x 14)                                                               |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 256 x 8                                                                     |

| RAM Size                   | 384 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 12x10b                                                                  |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 28-UFQFN Exposed Pad                                                        |

| Supplier Device Package    | 28-UQFN (4x4)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1827t-i-mv |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### REGISTER 4-1: CONFIGURATION WORD 1

|                |                                                                                                                                                                                                                                                                                                                                                                 | R/P-1                                                                             | R/P-1                   | R/P-1          | R/P-1           | R/P-1         | R/P-1/1 |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|-------------------------|----------------|-----------------|---------------|---------|

|                |                                                                                                                                                                                                                                                                                                                                                                 | FCMEN                                                                             | IESO                    | CLKOUTEN       | BORE            | N<1:0>        | CPD     |

|                |                                                                                                                                                                                                                                                                                                                                                                 | bit 13                                                                            |                         | 1 1            |                 |               | bit 8   |

|                |                                                                                                                                                                                                                                                                                                                                                                 |                                                                                   |                         |                |                 |               |         |

| R/P-1          | R/P-1                                                                                                                                                                                                                                                                                                                                                           | R/P-1                                                                             | R/P-1                   | R/P-1          | R/P-1           | R/P-1         | R/P-1   |

| CP             | MCLRE                                                                                                                                                                                                                                                                                                                                                           | PWRTE                                                                             | WDT                     | E<1:0>         |                 | FOSC<2:0>     |         |

| bit 7          |                                                                                                                                                                                                                                                                                                                                                                 |                                                                                   |                         |                |                 |               | bit C   |

|                |                                                                                                                                                                                                                                                                                                                                                                 |                                                                                   |                         |                |                 |               |         |

| Legend:        |                                                                                                                                                                                                                                                                                                                                                                 |                                                                                   |                         |                |                 |               |         |

| R = Readab     | ole bit                                                                                                                                                                                                                                                                                                                                                         | P = Programn                                                                      | nable bit               | U = Unimplem   | ented bit, read | d as '1'      |         |

| '0' = Bit is c | leared                                                                                                                                                                                                                                                                                                                                                          | '1' = Bit is set                                                                  |                         | -n = Value whe | en blank or aft | er Bulk Erase |         |

| bit 13         | 1 = Fail-Safe<br>0 = Fail-Safe                                                                                                                                                                                                                                                                                                                                  | -Safe Clock Mo<br>Clock Monitor i<br>Clock Monitor i                              | s enabled<br>s disabled | bit            |                 |               |         |

| bit 12         | 1 = Internal/E                                                                                                                                                                                                                                                                                                                                                  | al External Swite<br>External Switche<br>External Switche                         | ver mode is e           |                |                 |               |         |

| bit 11         | CLKOUTEN: Clock Out Enable bit         If FOSC configuration bits are set to LP, XT, HS modes:         This bit is ignored, CLKOUT function is disabled. Oscillator function on the CLKOUT pin.         All other FOSC modes:         1 = CLKOUT function is disabled. I/O function on the CLKOUT pin.         0 = CLKOUT function is enabled on the CLKOUT pin |                                                                                   |                         |                |                 | pin.          |         |

| bit 10-9       | BOREN<1:0>: Brown-out Reset Enable bits<br>11 = BOR enabled<br>10 = BOR enabled during operation and disabled in Sleep<br>01 = BOR controlled by SBOREN bit of the BORCON register<br>00 = BOR disabled                                                                                                                                                         |                                                                                   |                         |                |                 |               |         |

| bit 8          | 1 = Data mer                                                                                                                                                                                                                                                                                                                                                    | ode Protection<br>nory code prote<br>nory code prote                              | ction is disab          |                |                 |               |         |

| bit 7          |                                                                                                                                                                                                                                                                                                                                                                 | otection bit<br>memory code p<br>memory code p                                    |                         |                |                 |               |         |

| bit 6          | <pre>MCLRE: MCLR/VPP Pin Function Select bit If LVP bit = 1: This bit is ignored. If LVP bit = 0: 1 = MCLR/VPP pin function is MCLR; Weak pull-up enabled. 0 = MCLR/VPP pin function is digital input; MCLR internally disabled; Weak pull-up under control of WPUE3 bit.</pre>                                                                                 |                                                                                   |                         |                |                 |               |         |

| bit 5          | 1 = PWRT di                                                                                                                                                                                                                                                                                                                                                     | <b>PWRTE</b> : Power-up Timer Enable bit<br>1 = PWRT disabled<br>0 = PWRT enabled |                         |                |                 |               |         |

| bit 4-3        |                                                                                                                                                                                                                                                                                                                                                                 |                                                                                   |                         |                |                 |               |         |

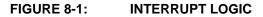

## 8.0 INTERRUPTS

The interrupt feature allows certain events to preempt normal program flow. Firmware is used to determine the source of the interrupt and act accordingly. Some interrupts can be configured to wake the MCU from Sleep mode.

This chapter contains the following information for Interrupts:

- Operation

- Interrupt Latency

- Interrupts During Sleep

- INT Pin

- · Automatic Context Saving

Many peripherals produce Interrupts. Refer to the corresponding chapters for details.

A block diagram of the interrupt logic is shown in Figure 8-1.

#### **REGISTER 12-3: PORTA: PORTA REGISTER**

| R/W-x/x                                 | R/W-x/x | R-x/x             | R/W-x/x | R/W-x/x                                               | R/W-x/x            | R/W-x/x | R/W-x/x |  |

|-----------------------------------------|---------|-------------------|---------|-------------------------------------------------------|--------------------|---------|---------|--|

| RA7                                     | RA6     | RA5               | RA4     | RA3                                                   | RA2                | RA1     | RA0     |  |

| bit 7                                   |         |                   |         |                                                       |                    |         | bit 0   |  |

|                                         |         |                   |         |                                                       |                    |         |         |  |

| Legend:                                 |         |                   |         |                                                       |                    |         |         |  |

| R = Readable bi                         | it      | W = Writable b    | oit     | U = Unimpleme                                         | ented bit, read as | '0'     |         |  |

| u = Bit is unchanged x = Bit is unknown |         |                   | own     | -n/n = Value at POR and BOR/Value at all other Resets |                    |         |         |  |

| '1' = Bit is set                        |         | '0' = Bit is clea | red     |                                                       |                    |         |         |  |

bit 7-0 RA<7:0>: PORTA I/O Value bits<sup>(1)</sup> 1 = Port pin is > VIH 0 = Port pin is < VIL

Note 1: Writes to PORTA are actually written to corresponding LATA register. Reads from PORTA register is return of actual I/O pin values.

#### REGISTER 12-4: TRISA: PORTA TRI-STATE REGISTER

| R/W-1/1 | R/W-1/1 | R-1/1  | R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 |

|---------|---------|--------|---------|---------|---------|---------|---------|

| TRISA7  | TRISA6  | TRISA5 | TRISA4  | TRISA3  | TRISA2  | TRISA1  | TRISA0  |

| bit 7   |         |        |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7-6 | <b>TRISA&lt;7:6&gt;:</b> PORTA Tri-State Control bit<br>1 = PORTA pin configured as an input (tri-stated)<br>0 = PORTA pin configured as an output |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 5   | <b>TRISA5:</b> RA5 Port Tri-State Control bit<br>This bit is always '1' as RA5 is an input only                                                    |

| bit 4-0 | <b>TRISA&lt;4:0&gt;:</b> PORTA Tri-State Control bit<br>1 = PORTA pin configured as an input (tri-stated)<br>0 = PORTA pin configured as an output |

#### REGISTER 12-5: LATA: PORTA DATA LATCH REGISTER

| R/W-x/u | R/W-x/u | U-0 | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u |

|---------|---------|-----|---------|---------|---------|---------|---------|

| LATA7   | LATA6   | —   | LATA4   | LATA3   | LATA2   | LATA1   | LATA0   |

| bit 7   |         |     |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7-6 | LATA<7:6>: RA<7:6> Output Latch Value bits <sup>(1)</sup> |

|---------|-----------------------------------------------------------|

|---------|-----------------------------------------------------------|

bit 5 Unimplemented: Read as '0

bit 4-0 LATA<4:0>: RA<4:0> Output Latch Value bits<sup>(1)</sup>

Note 1: Writes to PORTA are actually written to corresponding LATA register. Reads from PORTA register is return of actual I/O pin values.

## 12.3 PORTB and TRISB Registers

PORTB is an 8-bit wide, bidirectional port. The corresponding data direction register is TRISB (Register 12-9). Setting a TRISB bit (= 1) will make the corresponding PORTB pin an input (i.e., put the corresponding output driver in a High-Impedance mode). Clearing a TRISB bit (= 0) will make the corresponding PORTB pin an output (i.e., enable the output driver and put the contents of the output latch on the selected pin). Example 12-1 shows how to initialize an I/O port.

Reading the PORTB register (Register 12-8) reads the status of the pins, whereas writing to it will write to the PORT latch. All write operations are read-modify-write operations. Therefore, a write to a port implies that the port pins are read, this value is modified and then written to the PORT data latch.

The TRISB register (Register 12-9) controls the PORTB pin output drivers, even when they are being used as analog inputs. The user should ensure the bits in the TRISB register are maintained set when using them as analog inputs. I/O pins configured as analog input always read '0'.

#### 12.3.1 INTERRUPT-ON-CHANGE

All of the PORTB pins are individually configurable as an interrupt-on-change pin. Control bits IOCB<7:0> enable or disable the interrupt function for each pin. The interrupt-on-change feature is disabled on a Power-on Reset. Reference **Section 13.0 "Interrupt-On-Change"** for more information.

#### 12.3.2 WEAK PULL-UPS

Each of the PORTB pins has an individually configurable internal weak pull-up. Control bits WPUB<7:0> enable or disable each pull-up (see Register 12-11). Each weak pull-up is automatically turned off when the port pin is configured as an output. All pull-ups are disabled on a Power-on Reset by the WPUEN bit of the OPTION register.

#### 12.3.3 ANSELB REGISTER

The ANSELB register (Register 12-12) is used to configure the Input mode of an I/O pin to analog. Setting the appropriate ANSELB bit high will cause all digital reads on the pin to be read as '0' and allow analog functions on the pin to operate correctly.

The state of the ANSELB bits has no affect on digital output functions. A pin with TRIS clear and ANSELB set will still operate as a digital output, but the Input mode will be analog. This can cause unexpected behavior when executing read-modify-write instructions on the affected port.

The TRISB register (Register 12-9) controls the PORTB pin output drivers, even when they are being used as analog inputs. The user should ensure the bits in the TRISB register are maintained set when using them as analog inputs. I/O pins configured as analog input always read '0'.

Note: The ANSELB register must be initialized to configure an analog channel as a digital input. Pins configured as analog inputs will read '0'.

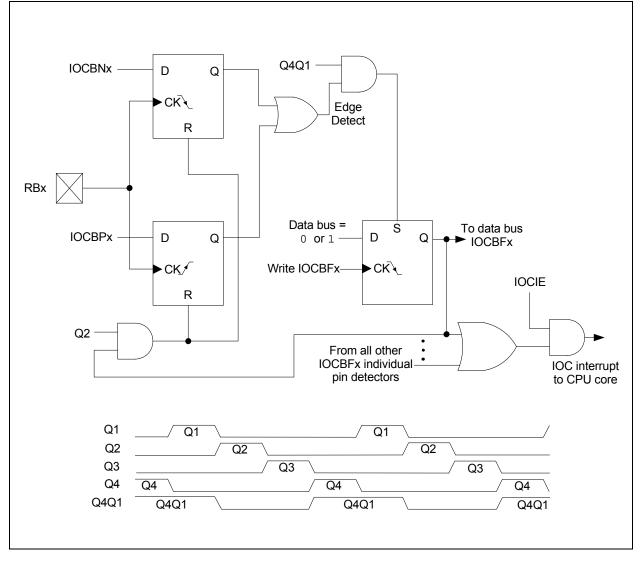

## 13.0 INTERRUPT-ON-CHANGE

The PORTB pins can be configured to operate as Interrupt-On-Change (IOC) pins. An interrupt can be generated by detecting a signal that has either a rising edge or a falling edge. Any individual PORTB pin can be configured to generate an interrupt. The interrupt-on-change module has the following features:

- Interrupt-on-Change enable (Master Switch)

- Individual pin configuration

- Rising and falling edge detection

- Individual pin interrupt flags

Figure 13-1 is a block diagram of the IOC module.

### 13.1 Enabling the Module

To allow individual port pins to generate an interrupt, the IOCIE bit of the INTCON register must be set. If the IOCIE bit is disabled, the edge detection on the pin will still occur, but an interrupt will not be generated.

#### 13.2 Individual Pin Configuration

For each port pin, a rising edge detector and a falling edge detector are present. To enable a pin to detect a rising edge, the associated IOCBPx bit of the IOCBP register is set. To enable a pin to detect a falling edge, the associated IOCBNx bit of the IOCBN register is set.

A pin can be configured to detect rising and falling edges simultaneously by setting both the IOCBPx bit and the IOCBNx bit of the IOCBP and IOCBN registers, respectively.

## 13.3 Interrupt Flags

The IOCBFx bits located in the IOCBF register are status flags that correspond to the Interrupt-on-change pins of the port. If an expected edge is detected on an appropriately enabled pin, then the status flag for that pin will be set, and an interrupt will be generated if the IOCIE bit is set. The IOCIF bit of the INTCON register reflects the status of all IOCBFx bits.

## 13.4 Clearing Interrupt Flags

The individual status flags, (IOCBFx bits), can be cleared by resetting them to zero. If another edge is detected during this clearing operation, the associated status flag will be set at the end of the sequence, regardless of the value actually being written.

In order to ensure that no detected edge is lost while clearing flags, only AND operations masking out known changed bits should be performed. The following sequence is an example of what should be performed.

#### EXAMPLE 13-1:

```

MOVLW 0xff

XORWF IOCBF, W

ANDWF IOCBF, F

```

### 13.5 Operation in Sleep

The interrupt-on-change interrupt sequence will wake the device from Sleep mode, if the IOCIE bit is set.

If an edge is detected while in Sleep mode, the IOCBF register will be updated prior to the first instruction executed out of Sleep.

FIGURE 13-1: INTERRUPT-ON-CHANGE BLOCK DIAGRAM

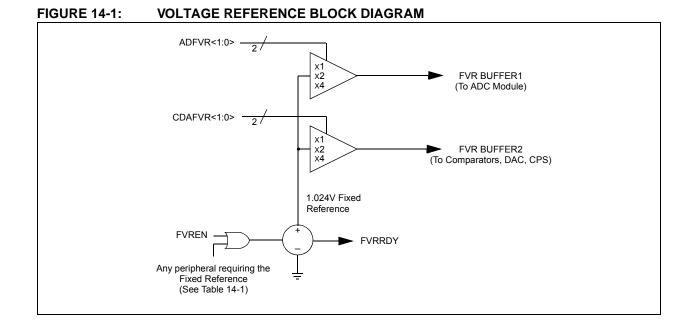

## 14.0 FIXED VOLTAGE REFERENCE (FVR)

The Fixed Voltage Reference, or FVR, is a stable voltage reference, independent of VDD, with 1.024V, 2.048V or 4.096V selectable output levels. The output of the FVR can be configured to supply a reference voltage to the following:

- · ADC input channel

- · ADC positive reference

- · Comparator positive input

- Digital-to-Analog Converter (DAC)

- Capacitive Sensing (CPS) module

The FVR can be enabled by setting the FVREN bit of the FVRCON register.

#### 14.1 Independent Gain Amplifiers

The output of the FVR supplied to the ADC, Comparators, and DAC and CPS is routed through two independent programmable gain amplifiers. Each amplifier can be configured to amplify the reference voltage by 1x, 2x or 4x, to produce the three possible voltage levels.

The ADFVR<1:0> bits of the FVRCON register are used to enable and configure the gain amplifier settings for the reference supplied to the ADC module. Reference **Section 16.0** "**Analog-to-Digital Converter** (**ADC**) **Module**" for additional information.

The CDAFVR<1:0> bits of the FVRCON register are used to enable and configure the gain amplifier settings for the reference supplied to the DAC and comparator module. Reference Section 16.0 "Digital-to-Analog Converter (DAC) Module" and Section 18.0 "Comparator Module" and Section 27.0 "Capacitive Sensing Module" for additional information.

### 14.2 FVR Stabilization Period

When the Fixed Voltage Reference module is enabled, it requires time for the reference and amplifier circuits to stabilize. Once the circuits stabilize and are ready for use, the FVRRDY bit of the FVRCON register will be set. See **Section 30.0** "**Electrical Specifications**" for the minimum delay requirement.

# PIC16(L)F1826/27

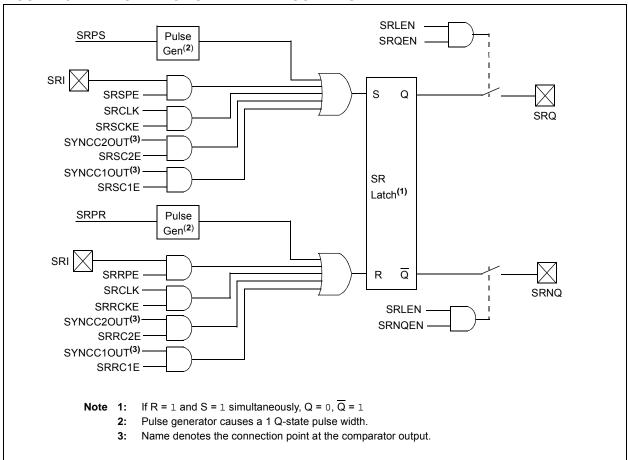

#### FIGURE 18-1: SR LATCH SIMPLIFIED BLOCK DIAGRAM

## 24.0 CAPTURE/COMPARE/PWM MODULES

The Capture/Compare/PWM module is a peripheral which allows the user to time and control different events, and to generate Pulse-Width Modulation (PWM) signals. In Capture mode, the peripheral allows the timing of the duration of an event. The Compare mode allows the user to trigger an external event when a predetermined amount of time has expired. The PWM mode can generate Pulse-Width Modulated signals of varying frequency and duty cycle.

This family of devices contains two Enhanced Capture/Compare/PWM modules (ECCP1 and ECCP2) and two standard Capture/Compare/PWM modules (CCP3 and CCP4).

The Capture and Compare functions are identical for all four CCP modules (ECCP1, ECCP2, CCP3 and CCP4). The only differences between CCP modules are in the Pulse-Width Modulation (PWM) function. The standard PWM function is identical in modules, CCP3 and CCP4. In CCP modules ECCP1 and ECCP2, the Enhanced PWM function has slight variations from one another. Full-Bridge ECCP modules have four available I/O pins while Half-Bridge ECCP modules only have two available I/O pins. See Table 24-1 for more information.

- Note 1: In devices with more than one CCP module, it is very important to pay close attention to the register names used. A number placed after the module acronym is used to distinguish between separate modules. For example, the CCP1CON and CCP2CON control the same operational aspects of two completely different CCP modules.

- 2: Throughout this section, generic references to a CCP module in any of its operating modes may be interpreted as being equally applicable to ECCP1, ECCP2, CCP3 and CCP4. Register names, module signals, I/O pins, and bit names may use the generic designator 'x' to indicate the use of a numeral to distinguish a particular module, when required.

#### TABLE 24-1:PWM RESOURCES

| Device Name   | ECCP1                       | ECCP2                       | CCP3          | CCP4          |

|---------------|-----------------------------|-----------------------------|---------------|---------------|

| PIC16(L)F1826 | Enhanced PWM<br>Full-Bridge | Not Available               | Not Available | Not Available |

| PIC16(L)F1827 | Enhanced PWM<br>Full-Bridge | Enhanced PWM<br>Half-Bridge | Standard PWM  | Standard PWM  |

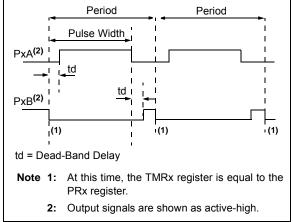

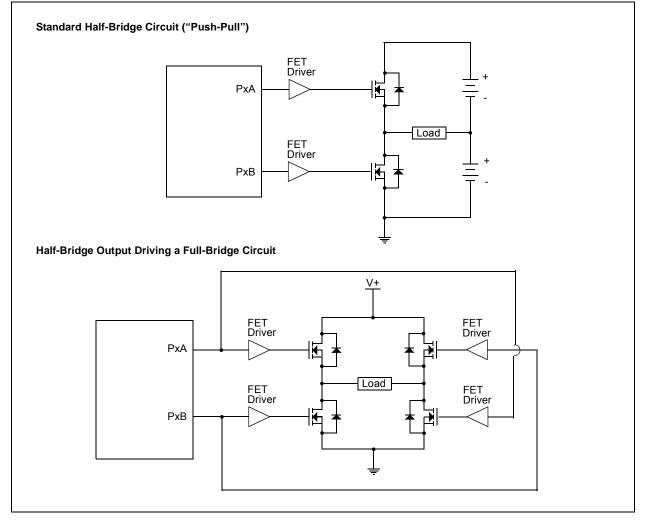

#### 24.4.1 HALF-BRIDGE MODE

In Half-Bridge mode, two pins are used as outputs to drive push-pull loads. The PWM output signal is output on the CCPx/PxA pin, while the complementary PWM output signal is output on the PxB pin (see Figure 24-9). This mode can be used for Half-Bridge applications, as shown in Figure 24-9, or for Full-Bridge applications, where four power switches are being modulated with two PWM signals.

In Half-Bridge mode, the programmable dead-band delay can be used to prevent shoot-through current in Half-Bridge power devices. The value of the PDC<6:0> bits of the PWMxCON register sets the number of instruction cycles before the output is driven active. If the value is greater than the duty cycle, the corresponding output remains inactive during the entire cycle. See **Section 24.4.5 "Programmable Dead-Band Delay Mode"** for more details of the dead-band delay operations. Since the PxA and PxB outputs are multiplexed with the PORT data latches, the associated TRIS bits must be cleared to configure PxA and PxB as outputs.

#### FIGURE 24-8: EXAMPLE OF HALF-BRIDGE PWM OUTPUT

## FIGURE 24-9: EXAMPLE OF HALF-BRIDGE APPLICATIONS

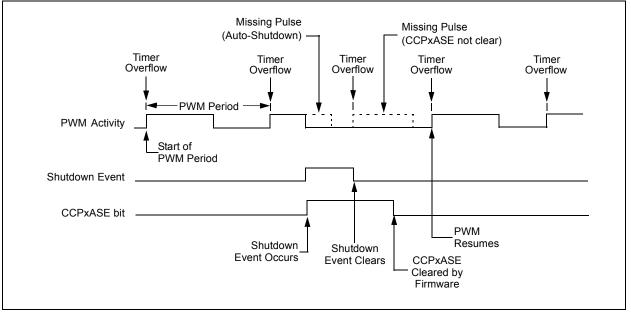

#### 24.4.3 ENHANCED PWM AUTO-SHUTDOWN MODE

The PWM mode supports an Auto-Shutdown mode that will disable the PWM outputs when an external shutdown event occurs. Auto-Shutdown mode places the PWM output pins into a predetermined state. This mode is used to help prevent the PWM from damaging the application.

The auto-shutdown sources are selected using the CCPxAS<2:0> bits of the CCPxAS register. A shutdown event may be generated by:

- A logic '0' on the INT pin

- A logic '1' on a Comparator (Cx) output

A shutdown condition is indicated by the CCPxASE (Auto-Shutdown Event Status) bit of the CCPxAS register. If the bit is a '0', the PWM pins are operating normally. If the bit is a '1', the PWM outputs are in the shutdown state.

When a shutdown event occurs, two things happen:

The CCPxASE bit is set to '1'. The CCPxASE will remain set until cleared in firmware or an auto-restart occurs (see Section 24.4.4 "Auto-Restart Mode").

The enabled PWM pins are asynchronously placed in their shutdown states. The PWM output pins are grouped into pairs [PxA/PxC] and [PxB/PxD]. The state of each pin pair is determined by the PSSxAC and PSSxBD bits of the CCPxAS register. Each pin pair may be placed into one of three states:

- Drive logic '1'

- Drive logic '0'

- Tri-state (high-impedance)

- Note 1: The auto-shutdown condition is a level-based signal, not an edge-based signal. As long as the level is present, the auto-shutdown will persist.

- Writing to the CCPxASE bit of the CCPxAS register is disabled while an auto-shutdown condition persists.

- 3: Once the auto-shutdown condition has been removed and the PWM restarted (either through firmware or auto-restart) the PWM signal will always restart at the beginning of the next PWM period.

- 4: Prior to an auto-shutdown event caused by a comparator output or INT pin event, a software shutdown can be triggered in firmware by setting the CCPxASE bit of the CCPxAS register to '1'. The Auto-Restart feature tracks the active status of a shutdown caused by a comparator output or INT pin event only. If it is enabled at this time, it will immediately clear this bit and restart the ECCP module at the beginning of the next PWM period.

#### FIGURE 24-14: PWM AUTO-SHUTDOWN WITH FIRMWARE RESTART (PXRSEN = 0)

| R/W-0/0        | R/W-0/0                                                                                       | R/W-0/0                                                                        | R/W-0/0        | R/W-0/0            | R/W-0/0          | R/W-0/0        | R/W-0/0              |

|----------------|-----------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|----------------|--------------------|------------------|----------------|----------------------|

| PxRSEN         | 1                                                                                             |                                                                                |                | PxDC<6:0>          |                  |                |                      |

| bit 7          |                                                                                               |                                                                                |                |                    |                  |                | bit 0                |

|                |                                                                                               |                                                                                |                |                    |                  |                |                      |

| Legend:        |                                                                                               |                                                                                |                |                    |                  |                |                      |

| R = Reada      | ble bit                                                                                       | W = Writable                                                                   | bit            | U = Unimplen       | nented bit, read | d as '0'       |                      |

| u = Bit is u   | nchanged                                                                                      | x = Bit is unkr                                                                | nown           | -n/n = Value a     | at POR and BC    | R/Value at all | other Resets         |

| '1' = Bit is s | et                                                                                            | '0' = Bit is cle                                                               | ared           |                    |                  |                |                      |

|                |                                                                                               |                                                                                |                |                    |                  |                |                      |

| bit 7          | PxRSEN: P                                                                                     | WM Restart Ena                                                                 | able bit       |                    |                  |                |                      |

|                | 1 = Upon auto-shutdown, the CCPxASE bit clears automatically once the shutdown event goes awa |                                                                                |                |                    |                  |                | ent goes away;       |

|                |                                                                                               | the PWM restarts automatically                                                 |                |                    |                  |                |                      |

|                | 0 = Upon a                                                                                    | 0 = Upon auto-shutdown, CCPxASE must be cleared in software to restart the PWM |                |                    |                  |                |                      |

| bit 6-0        | PxDC<6:0>                                                                                     | PxDC<6:0>: PWM Delay Count bits                                                |                |                    |                  |                |                      |

|                | PxDCx =Nu                                                                                     | mber of Fosc/4 (                                                               | (4 * Tosc) cyc | les between the    | scheduled time   | e when a PWM   | signal <b>should</b> |

|                | tra                                                                                           | ansition active a                                                              | nd the actual  | time it transition | s active         |                |                      |

|                |                                                                                               |                                                                                |                |                    |                  |                |                      |

#### REGISTER 24-4: PWMxCON: ENHANCED PWM CONTROL REGISTER

**Note 1:** Bit resets to '0' with Two-Speed Start-up and LP, XT or HS selected as the Oscillator mode or Fail-Safe mode is enabled.

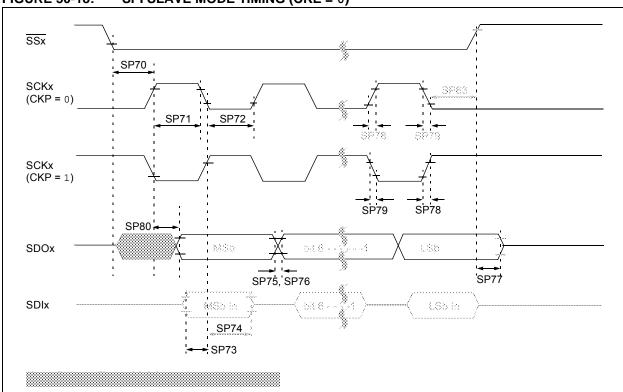

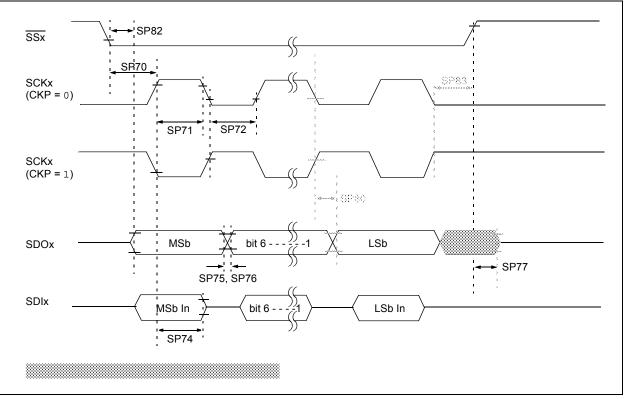

#### 25.2.4 SPI SLAVE MODE

In Slave mode, the data is transmitted and received as external clock pulses appear on SCKx. When the last bit is latched, the SSPxIF interrupt flag bit is set.

Before enabling the module in SPI Slave mode, the clock line must match the proper Idle state. The clock line can be observed by reading the SCKx pin. The Idle state is determined by the CKP bit of the SSPxCON1 register.

While in Slave mode, the external clock is supplied by the external clock source on the SCKx pin. This external clock must meet the minimum high and low times as specified in the electrical specifications.

While in Sleep mode, the slave can transmit/receive data. The shift register is clocked from the SCKx pin input and when a byte is received, the device will generate an interrupt. If enabled, the device will wake-up from Sleep.

25.2.4.1 Daisy-Chain Configuration

The SPI bus can sometimes be connected in a daisy-chain configuration. The first slave output is connected to the second slave input, the second slave output is connected to the third slave input, and so on. The final slave output is connected to the master input. Each slave sends out, during a second group of clock pulses, an exact copy of what was received during the first group of clock pulses. The whole chain acts as one large communication shift register. The daisy-chain feature only requires a single Slave Select line from the master device.

Figure 25-7 shows the block diagram of a typical daisy-chain connection when operating in SPI Mode.

In a daisy-chain configuration, only the most recent byte on the bus is required by the slave. Setting the BOEN bit of the SSPxCON3 register will enable writes to the SSPxBUF register, even if the previous byte has not been read. This allows the software to ignore data that may not apply to it.

### 25.2.5 SLAVE SELECT SYNCHRONIZATION

The Slave Select can also be used to synchronize communication. The Slave Select line is held high until the master device is ready to communicate. When the Slave Select line is pulled low, the slave knows that a new transmission is starting.

If the slave fails to receive the communication properly, it will be reset at the end of the transmission, when the Slave Select line returns to a high state. The slave is then ready to receive a new transmission when the Slave Select line is pulled low again. If the Slave Select line is not used, there is a risk that the slave will eventually become out of sync with the master. If the slave misses a bit, it will always be one bit off in future transmissions. Use of the Slave Select line allows the slave and master to align themselves at the beginning of each transmission.

The  $\overline{SSx}$  pin allows a Synchronous Slave mode. The SPI must be in Slave mode with  $\overline{SSx}$  pin control enabled (SSPxCON1<3:0> = 0100).

When the  $\overline{SSx}$  pin is low, transmission and reception are enabled and the SDOx pin is driven.

When the  $\overline{\text{SSx}}$  pin goes high, the SDOx pin is no longer driven, even if in the middle of a transmitted byte and becomes a floating output. External pull-up/pull-down resistors may be desirable depending on the application.

| Note 1: | When the SPI is in Slave mode with $\overline{SSx}$ pin control enabled (SSPxCON1<3:0> = 0100), the SPI module will reset if the $\overline{SSx}$ pin is set to VDD. |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2:      | When the SPI is used in Slave mode with CKE set; the user must enable $\overline{SSx}$ pin control.                                                                  |

| 3:      | While operated in SPI Slave mode the SMP bit of the SSPxSTAT register must remain clear.                                                                             |

When the SPI module resets, the bit counter is forced to '0'. This can be done by either forcing the SSx pin to a high level or clearing the SSPxEN bit.

| Name    | Bit 7                         | Bit 6   | Bit 5  | Bit 4                 | Bit 3                  | Bit 2  | Bit 1  | Bit 0   | Register on<br>Page |

|---------|-------------------------------|---------|--------|-----------------------|------------------------|--------|--------|---------|---------------------|

| APFCON0 | RXDTSEL                       | SDO1SEL | SS1SEL | P2BSEL <sup>(1)</sup> | CCP2SEL <sup>(1)</sup> | P1DSEL | P1CSEL | CCP1SEL | 119                 |

| APFCON1 | _                             | —       | —      | _                     | _                      | _      | —      | TXCKSEL | 119                 |

| BAUDCON | ABDOVF                        | RCIDL   |        | SCKP                  | BRG16                  | _      | WUE    | ABDEN   | 296                 |

| INTCON  | GIE                           | PEIE    | TMR0IE | INTE                  | IOCIE                  | TMR0IF | INTF   | IOCIF   | 86                  |

| PIE1    | TMR1GIE                       | ADIE    | RCIE   | TXIE                  | SSPIE                  | CCP1IE | TMR2IE | TMR1IE  | 87                  |

| PIR1    | TMR1GIF                       | ADIF    | RCIF   | TXIF                  | SSPIF                  | CCP1IF | TMR2IF | TMR1IF  | 91                  |

| RCSTA   | SPEN                          | RX9     | SREN   | CREN                  | ADDEN                  | FERR   | OERR   | RX9D    | 295                 |

| SPBRGL  | BRG<7:0>                      |         |        |                       | 297*                   |        |        |         |                     |

| SPBRGH  |                               |         |        | BRG<                  | <15:8>                 |        |        |         | 297*                |

| TRISB   | TRISB7                        | TRISB6  | TRISB5 | TRISB4                | TRISB3                 | TRISB2 | TRISB1 | TRISB0  | 127                 |

| TXREG   | EUSART Transmit Data Register |         |        |                       |                        |        | 287*   |         |                     |

| TXSTA   | CSRC                          | TX9     | TXEN   | SYNC                  | SENDB                  | BRGH   | TRMT   | TX9D    | 294                 |

#### **TABLE 26-1:** SUMMARY OF REGISTERS ASSOCIATED WITH ASYNCHRONOUS TRANSMISSION

— = unimplemented location, read as '0'. Shaded cells are not used for Asynchronous Transmission.

Page provides register information.

PIC16(L)F1827 only. Legend:

Note 1:

## 30.2 DC Characteristics: PIC16(L)F1826/27-I/E (Industrial, Extended)

| PIC16LF | 1826/27                             | $ \begin{array}{l} \mbox{Standard Operating Conditions (unless otherwise stated)} \\ \mbox{Operating temperature} & -40^\circ C \leq TA \leq +85^\circ C \mbox{ for industrial} \\ -40^\circ C \leq TA \leq +125^\circ C \mbox{ for extended} \end{array} $ |      |      |       |                                                                                                    |                                                               |

|---------|-------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|-------|----------------------------------------------------------------------------------------------------|---------------------------------------------------------------|

| PIC16F1 | 826/27                              | 1 0 1                                                                                                                                                                                                                                                       |      |      |       | ess otherwise stated)<br>$a \le +85^{\circ}C$ for industrial<br>$a \le +125^{\circ}C$ for extended |                                                               |

| Param   | Device                              | Min.                                                                                                                                                                                                                                                        | Typ† | Max. | Units | Conditions                                                                                         |                                                               |

| No.     | Characteristics                     | IVIIII.                                                                                                                                                                                                                                                     | IJPI | Wax. |       | Vdd                                                                                                | Note                                                          |

|         | Supply Current (IDD) <sup>(1,</sup> | 2)                                                                                                                                                                                                                                                          |      |      |       |                                                                                                    |                                                               |

| D010    |                                     | —                                                                                                                                                                                                                                                           | 7.0  | 13   | μΑ    | 1.8                                                                                                | Fosc = 32 kHz                                                 |

|         |                                     | _                                                                                                                                                                                                                                                           | 9.0  | 16   | μΑ    | 3.0                                                                                                | LP Oscillator mode, $-40^{\circ}C \le TA \le +85^{\circ}C$    |

|         |                                     | _                                                                                                                                                                                                                                                           | 7.0  | 17   | μΑ    | 1.8                                                                                                | Fosc = 32 kHz                                                 |

|         |                                     | —                                                                                                                                                                                                                                                           | 9.0  | 18   | μΑ    | 3.0                                                                                                | LP Oscillator mode, $-40^{\circ}C \le TA \le +125^{\circ}C$   |

| D010    |                                     | _                                                                                                                                                                                                                                                           | 24   | 40   | μΑ    | 1.8                                                                                                | Fosc = 32 kHz                                                 |

|         |                                     | —                                                                                                                                                                                                                                                           | 30   | 48   | μΑ    | 3.0                                                                                                | LP Oscillator mode<br>-40°C $\leq$ TA $\leq$ +85°C            |

|         |                                     | —                                                                                                                                                                                                                                                           | 32   | 55   | μΑ    | 5.0                                                                                                | $-40.0 \leq 14 \leq +05.0$                                    |

|         |                                     | —                                                                                                                                                                                                                                                           | 24   | 43   | μA    | 1.8                                                                                                | Fosc = 32 kHz                                                 |

|         |                                     | —                                                                                                                                                                                                                                                           | 30   | 50   | μΑ    | 3.0                                                                                                | LP Oscillator mode<br>$-40^{\circ}C \le TA \le +125^{\circ}C$ |

|         |                                     | —                                                                                                                                                                                                                                                           | 32   | 60   | μΑ    | 5.0                                                                                                | $-40.0 \leq 14 \leq +125.0$                                   |

| D011    |                                     | —                                                                                                                                                                                                                                                           | 110  | 200  | μA    | 1.8                                                                                                | Fosc = 1 MHz                                                  |

|         |                                     | —                                                                                                                                                                                                                                                           | 200  | 400  | μA    | 3.0                                                                                                | XT Oscillator mode                                            |

| D011    |                                     | —                                                                                                                                                                                                                                                           | 160  | 210  | μΑ    | 1.8                                                                                                | Fosc = 1 MHz                                                  |

|         |                                     | _                                                                                                                                                                                                                                                           | 210  | 400  | μΑ    | 3.0                                                                                                | XT Oscillator mode                                            |

|         |                                     | —                                                                                                                                                                                                                                                           | 250  | 450  | μΑ    | 5.0                                                                                                |                                                               |

| D012    |                                     | _                                                                                                                                                                                                                                                           | 290  | 475  | μΑ    | 1.8                                                                                                | Fosc = 4 MHz                                                  |

|         |                                     | _                                                                                                                                                                                                                                                           | 600  | 900  | μΑ    | 3.0                                                                                                | XT Oscillator mode                                            |

| D012    |                                     |                                                                                                                                                                                                                                                             | 380  | 570  | μA    | 1.8                                                                                                | Fosc = 4 MHz                                                  |

|         |                                     |                                                                                                                                                                                                                                                             | 650  | 880  | μΑ    | 3.0                                                                                                | XT Oscillator mode                                            |

|         |                                     | —                                                                                                                                                                                                                                                           | 680  | 1100 | μΑ    | 5.0                                                                                                |                                                               |

| D013    |                                     | _                                                                                                                                                                                                                                                           | 40   | 80   | μA    | 1.8                                                                                                | Fosc = 500 kHz                                                |

|         |                                     | _                                                                                                                                                                                                                                                           | 70   | 120  | μΑ    | 3.0                                                                                                | EC Oscillator mode, Low-power mode                            |

| D013    |                                     | _                                                                                                                                                                                                                                                           | 60   | 120  | μΑ    | 1.8                                                                                                | Fosc = 500 kHz                                                |

|         |                                     | —                                                                                                                                                                                                                                                           | 80   | 180  | μΑ    | 3.0                                                                                                | EC Oscillator mode<br>Low-power mode                          |

|         |                                     |                                                                                                                                                                                                                                                             | 93   | 200  | μA    | 5.0                                                                                                |                                                               |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** The test conditions for all IDD measurements in active operation mode are: OSC1 = external square wave, from rail-to-rail; all I/O pins as inputs, pulled to VDD; MCLR = VDD; WDT disabled.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors, such as I/O pin loading and switching rate, oscillator type, internal code execution pattern and temperature, also have an impact on the current consumption.

- 3: 8 MHz internal RC oscillator with 4x PLL enabled.

- 4: 8 MHz crystal oscillator with 4x PLL enabled.

5: For RC oscillator configurations, current through REXT is not included. The current through the resistor can be extended by the formula IR = VDD/2REXT (mA) with REXT in k $\Omega$ .

## 30.3 DC Characteristics: PIC16(L)F1826/27-I/E (Power-Down)

| PIC16LF1826/27 |                         |                      |                | rd Operating temper |         | ditions (unless otherwise stated)<br>-40°C $\leq$ TA $\leq$ +85°C for industrial<br>-40°C $\leq$ TA $\leq$ +125°C for extended |     |                                    |  |

|----------------|-------------------------|----------------------|----------------|---------------------|---------|--------------------------------------------------------------------------------------------------------------------------------|-----|------------------------------------|--|

| PIC16F1826/27  |                         |                      |                | rd Operating temper |         | ditions (unless otherwise stated)<br>-40°C $\leq$ TA $\leq$ +85°C for industrial<br>-40°C $\leq$ TA $\leq$ +125°C for extended |     |                                    |  |

| Param          | Davias Characteristics  | Min.                 | Tunt Max. Max. |                     | L Inite | Conditions                                                                                                                     |     |                                    |  |

| No.            | Device Characteristics  | win.                 | Тур†           | +85°C               | +125°C  | Units                                                                                                                          | Vdd | Note                               |  |

|                | Power-down Base Current | (IPD) <sup>(2)</sup> |                | -                   |         |                                                                                                                                |     |                                    |  |

| D022           |                         | _                    | 0.02           | 1.0                 | 4.0     | μA                                                                                                                             | 1.8 | WDT, BOR, FVR, and T1OSC           |  |

|                |                         | —                    | 0.03           | 1.1                 | 7.0     | μA                                                                                                                             | 3.0 | disabled, all Peripherals Inactive |  |

| D022           |                         |                      | 15             | 35                  | 50      | μA                                                                                                                             | 1.8 | WDT, BOR, FVR, and T1OSC           |  |

|                |                         |                      | 18             | 40                  | 60      | μA                                                                                                                             | 3.0 | disabled, all Peripherals Inactive |  |

|                |                         | —                    | 19             | 45                  | 70      | μA                                                                                                                             | 5.0 |                                    |  |

| D023           |                         |                      | 0.5            | 1.1                 | 5.0     | μA                                                                                                                             | 1.8 | LPWDT Current (Note 1)             |  |

|                |                         |                      | 0.8            | 2.0                 | 8.0     | μA                                                                                                                             | 3.0 |                                    |  |

| D023           |                         |                      | 16             | 35                  | 50      | μA                                                                                                                             | 1.8 | LPWDT Current (Note 1)             |  |

|                |                         |                      | 19             | 40                  | 60      | μA                                                                                                                             | 3.0 | _                                  |  |

|                |                         | —                    | 20             | 45                  | 70      | μA                                                                                                                             | 5.0 |                                    |  |

| D023A          |                         |                      | 8.5            | 23                  | 32      | μA                                                                                                                             | 1.8 | FVR current (Note 1)               |  |

|                |                         | —                    | 8.5            | 26                  | 40      | μA                                                                                                                             | 3.0 |                                    |  |

| D023A          |                         |                      | 32             | 62                  | 66      | μA                                                                                                                             | 1.8 | FVR current (Note 1)               |  |

|                |                         |                      | 39             | 70                  | 80      | μA                                                                                                                             | 3.0 | _                                  |  |

|                |                         | —                    | 70             | 110                 | 120     | μA                                                                                                                             | 5.0 |                                    |  |

| D024           |                         | —                    | 8.1            | 14                  | 20      | μA                                                                                                                             | 3.0 | BOR Current (Note 1)               |  |

| D024           |                         |                      | 34             | 57                  | 70      | μA                                                                                                                             | 3.0 | BOR Current (Note 1)               |  |

|                |                         | —                    | 67             | 100                 | 115     | μA                                                                                                                             | 5.0 |                                    |  |

| D025           |                         |                      | 0.6            | 1.5                 | 5.0     | μA                                                                                                                             | 1.8 | T1OSC Current (Note 1)             |  |

|                |                         |                      | 0.8            | 2.5                 | 8.0     | μΑ                                                                                                                             | 3.0 |                                    |  |

| D025           |                         | _                    | 16             | 35                  | 50      | μA                                                                                                                             | 1.8 | T1OSC Current (Note 1)             |  |

|                |                         | _                    | 21             | 40                  | 60      | μA                                                                                                                             | 3.0 | _                                  |  |

|                |                         | —                    | 25             | 45                  | 70      | μA                                                                                                                             | 5.0 |                                    |  |

| D026           |                         |                      | 0.1            | 1.1                 | 5.0     | μA                                                                                                                             | 1.8 | A/D Current (Note 1, Note 3), no   |  |

|                |                         | -                    | 0.1            | 2.0                 | 8.0     | μΑ                                                                                                                             | 3.0 | conversion in progress             |  |

| D026           |                         | _                    | 16             | 35                  | 50      | μA                                                                                                                             | 1.8 | A/D Current (Note 1, Note 3), no   |  |

|                |                         | _                    | 21             | 40                  | 60      | μΑ                                                                                                                             | 3.0 | conversion in progress             |  |

|                |                         | —                    | 25             | 45                  | 70      | μA                                                                                                                             | 5.0 |                                    |  |

These parameters are characterized but not tested.

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: The peripheral current is the sum of the base IDD or IPD and the additional current consumed when this peripheral is enabled. The peripheral △ current can be determined by subtracting the base IDD or IPD current from this limit. Max values should be used when calculating total current consumption.

2: The power-down current in Sleep mode does not depend on the oscillator type. Power-down current is measured with the part in Sleep mode, with all I/O pins set to inputs state and tied to VDD.

**3:** A/D oscillator source is FRC.

# PIC16(L)F1826/27

#### FIGURE 30-18: SPI SLAVE MODE TIMING (CKE = 0)

## 33.0 PACKAGING INFORMATION

## 33.1 Package Marking Information

#### 18-Lead PDIP

#### 18-Lead SOIC (.300")

#### 20-Lead SSOP

#### 28-Lead QFN/UQFN

### Example

### Example

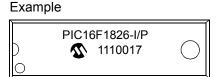

#### Example

| Legend | : XXX<br>Y<br>YY<br>WW<br>NNN<br>@3<br>* | Customer-specific information<br>Year code (last digit of calendar year)<br>Year code (last 2 digits of calendar year)<br>Week code (week of January 1 is week '01')<br>Alphanumeric traceability code<br>Pb-free JEDEC designator for Matte Tin (Sn)<br>This package is Pb-free. The Pb-free JEDEC designator ((e3))<br>can be found on the outer packaging for this package. |

|--------|------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Note:  | be carried                               | nt the full Microchip part number cannot be marked on one line, it will<br>d over to the next line, thus limiting the number of available<br>s for customer-specific information.                                                                                                                                                                                              |

\* Standard PICmicro<sup>®</sup> device marking consists of Microchip part number, year code, week code and traceability code. For PICmicro device marking beyond this, certain price adders apply. Please check with your Microchip Sales Office. For QTP devices, any special marking adders are included in QTP price.

## INDEX

| Α                                        |           |

|------------------------------------------|-----------|

| A/D                                      |           |

| Specifications                           |           |

| Absolute Maximum Ratings                 |           |

| AC Characteristics                       |           |

| Industrial and Extended                  | 354       |

| Load Conditions                          | 353       |

| ACKSTAT                                  | 266       |

| ACKSTAT Status Flag                      | 266       |

| ADC                                      |           |

| Acquisition Requirements                 | 149       |

| Associated registers                     | 151       |

| Block Diagram                            |           |

| Calculating Acquisition Time             |           |

| Channel Selection                        |           |

| Configuration                            |           |

| Configuring Interrupt                    | 144       |

| Conversion Clock                         | 140       |

| Conversion Procedure                     |           |

| Internal Sampling Switch (Rss) IMPEDANCE | 149       |

| Interrupts                               |           |

| Operation                                | 143       |

| Operation During Sleep                   | 143       |

| Port Configuration                       | 140       |

| Reference Voltage (VREF)                 | 140       |

| Source Impedance                         | 149       |

| Special Event Trigger                    | 143       |

| Starting an A/D Conversion               | 142       |

| ADCON0 Register                          | . 28, 145 |

| ADCON1 Register                          | . 28, 146 |

| ADDFSR                                   | 329       |

| ADDWFC                                   | 329       |

| ADRESH Register                          |           |

| ADRESH Register (ADFM = 0)               |           |

| ADRESH Register (ADFM = 1)               | 148       |

| ADRESL Register (ADFM = 0)               | 147       |

| ADRESL Register (ADFM = 1)               |           |

| Alternate Pin Function                   | 118       |

| Analog-to-Digital Converter. See ADC     |           |

| ANSELA Register                          | 123       |

| ANSELB Register                          | 128       |

| APFCON0 Register                         | 119       |

| APFCON1 Register                         | 119       |

| Assembler                                |           |

| MPASM Assembler                          |           |

| Automatic Context Saving                 | 85        |

## В

| -       |       |

|---------|-------|

| Bank 10 |       |

| Bank 11 |       |

| Bank 12 |       |

| Bank 13 |       |

| Bank 14 |       |

| Bank 15 |       |

| Bank 16 |       |

| Bank 17 | ••••• |

| Bank 18 |       |

| Bank 19 |       |

| Bank 20 |       |

| Bank 21 |       |

| Bank 22 |       |

| Bank 23 |       |

| Bank 31 |       |

|         |       |

| Bank 6                                        | 31    |

|-----------------------------------------------|-------|

| Bank 7                                        | 31    |

| Bank 8                                        | 32    |

| Bank 9                                        |       |

| BAUDCON Register                              | . 296 |

| BF                                            | ,     |

| BF Status Flag 266                            | , 268 |

| Block Diagram                                 |       |

| Capacitive Sensing                            | . 315 |

| Block Diagrams                                |       |

| (CCP) Capture Mode Operation                  |       |

| ADC                                           |       |

| ADC Transfer Function                         |       |

| Analog Input Model 150                        |       |

| CCP PWM                                       |       |