Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XF

| Detuns                     |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 32MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                           |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 16                                                                          |

| Program Memory Size        | 7KB (4K x 14)                                                               |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 256 x 8                                                                     |

| RAM Size                   | 384 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 12x10b                                                                  |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 18-SOIC (0.295", 7.50mm Width)                                              |

| Supplier Device Package    | 18-SOIC                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1827t-i-so |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 2.0 ENHANCED MID-RANGE CPU

This family of devices contain an enhanced mid-range 8-bit CPU core. The CPU has 49 instructions. Interrupt capability includes automatic context saving. The hardware stack is 16 levels deep and has Overflow and Underflow Reset capability. Direct, Indirect, and Relative addressing modes are available. Two File Select Registers (FSRs) provide the ability to read program and data memory.

- Automatic Interrupt Context Saving

- 16-level Stack with Overflow and Underflow

- File Select Registers

- Instruction Set

# 2.1 Automatic Interrupt Context Saving

During interrupts, certain registers are automatically saved in shadow registers and restored when returning from the interrupt. This saves stack space and user code. See **Section 8.5 "Automatic Context Saving"**, for more information.

### 2.2 16-level Stack with Overflow and Underflow

These devices have an external stack memory 15 bits wide and 16 words deep. A Stack Overflow or Underflow will set the appropriate bit (STKOVF or STKUNF) in the PCON register, and if enabled will cause a software Reset. See section **Section 3.4 "Stack"** for more details.

# 2.3 File Select Registers

There are two 16-bit File Select Registers (FSR). FSRs can access all file registers and program memory, which allows one Data Pointer for all memory. When an FSR points to program memory, there is one additional instruction cycle in instructions using INDF to allow the data to be fetched. General purpose memory can now also be addressed linearly, providing the ability to access contiguous data larger than 80 bytes. There are also new instructions to support the FSRs. See **Section 3.4 "Stack**"for more details.

# 2.4 Instruction Set

There are 49 instructions for the enhanced mid-range CPU to support the features of the CPU. See **Section 29.0** "Instruction Set Summary" for more details.

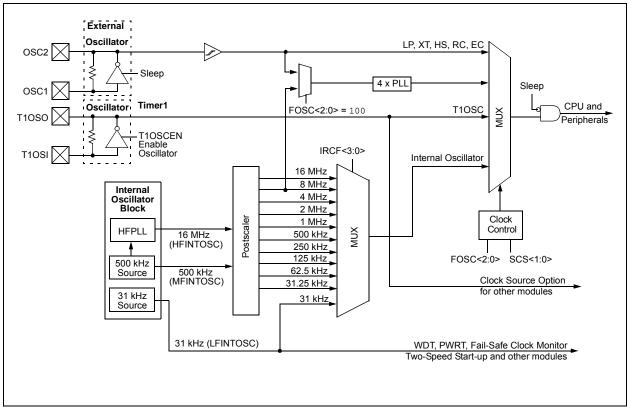

#### FIGURE 5-1: SIMPLIFIED PIC<sup>®</sup> MCU CLOCK SOURCE BLOCK DIAGRAM

#### 5.2.2.3 Internal Oscillator Frequency Adjustment

The 500 kHz internal oscillator is factory calibrated. This internal oscillator can be adjusted in software by writing to the OSCTUNE register (Register 5-3). Since the HFINTOSC and MFINTOSC clock sources are derived from the 500 kHz internal oscillator a change in the OSCTUNE register value will apply to both.

The default value of the OSCTUNE register is '0'. The value is a 6-bit two's complement number. A value of 1Fh will provide an adjustment to the maximum frequency. A value of 20h will provide an adjustment to the minimum frequency.

When the OSCTUNE register is modified, the oscillator frequency will begin shifting to the new frequency. Code execution continues during this shift. There is no indication that the shift has occurred.

OSCTUNE does not affect the LFINTOSC frequency. Operation of features that depend on the LFINTOSC clock source frequency, such as the Power-up Timer (PWRT), Watchdog Timer (WDT), Fail-Safe Clock Monitor (FSCM) and peripherals, are *not* affected by the change in frequency.

# 5.2.2.4 LFINTOSC

The Low-Frequency Internal Oscillator (LFINTOSC) is an uncalibrated 31 kHz internal clock source.

The output of the LFINTOSC connects to a postscaler and multiplexer (see Figure 5-1). Select 31 kHz, via software, using the IRCF<3:0> bits of the OSCCON register. See **Section 5.2.2.7** "Internal Oscillator **Clock Switch Timing**" for more information. The LFINTOSC is also the frequency for the Power-up Timer (PWRT), Watchdog Timer (WDT) and Fail-Safe Clock Monitor (FSCM).

The LFINTOSC is enabled by selecting 31 kHz (IRCF<3:0> bits of the OSCCON register = 000) as the system clock source (SCS bits of the OSCCON register = 1x), or when any of the following are enabled:

- Configure the IRCF<3:0> bits of the OSCCON register for the desired LF frequency, and

- FOSC<2:0> = 100, or

- Set the System Clock Source (SCS) bits of the OSCCON register to '1x'

Peripherals that use the LFINTOSC are:

- Power-up Timer (PWRT)

- Watchdog Timer (WDT)

- Fail-Safe Clock Monitor (FSCM)

The Low Frequency Internal Oscillator Ready bit (LFIOFR) of the OSCSTAT register indicates when the LFINTOSC is running and can be utilized.

#### 5.2.2.5 Internal Oscillator Frequency Selection

The system clock speed can be selected via software using the Internal Oscillator Frequency Select bits IRCF<3:0> of the OSCCON register.

The output of the 16 MHz HFINTOSC and 31 kHz LFINTOSC connects to a postscaler and multiplexer (see Figure 5-1). The Internal Oscillator Frequency Select bits IRCF<3:0> of the OSCCON register select the frequency output of the internal oscillators. One of the following frequencies can be selected via software:

- 32 MHz (requires 4X PLL)

- 16 MHz

- 8 MHz

- 4 MHz

- 2 MHz

- 1 MHz

- 500 kHz (Default after Reset)

- 250 kHz

- 125 kHz

- 62.5 kHz

- 31.25 kHz

- 31 kHz (LFINTOSC)

| Note: | Following any Reset, the IRCF<3:0> bits  |

|-------|------------------------------------------|

|       | of the OSCCON register are set to '0111' |

|       | and the frequency selection is set to    |

|       | 500 kHz. The user can modify the IRCF    |

|       | bits to select a different frequency.    |

The IRCF<3:0> bits of the OSCCON register allow duplicate selections for some frequencies. These duplicate choices can offer system design trade-offs. Lower power consumption can be obtained when changing oscillator sources for a given frequency. Faster transition times can be obtained between frequency changes that use the same oscillator source.

# EXAMPLE 11-2: DATA EEPROM WRITE

|                      | BANKSEL<br>MOVLW<br>MOVWF<br>MOVLW<br>MOVWF<br>BCF<br>BCF<br>BSF       | EECON1, EEPG<br>EECON1, WREN                                 | ;Data Memory Address to write<br>;                                                                        |

|----------------------|------------------------------------------------------------------------|--------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|

| Required<br>Sequence | MOVLW<br>MOVWF<br>MOVLW<br>MOVWF<br>BSF<br>BSF<br>BCF<br>BTFSC<br>GOTO | 55h<br>EECON2<br>OAAh<br>EECON2<br>EECON1, WR<br>INTCON, GIE | ;<br>;Write 55h<br>;<br>;Write AAh<br>;Set WR bit to begin write<br>;Enable Interrupts<br>;Disable writes |

#### 12.3.4 PORTB FUNCTIONS AND OUTPUT PRIORITIES

Each PORTB pin is multiplexed with other functions. The pins, their combined functions and their output priorities are shown in Table 12-5.

When multiple outputs are enabled, the actual pin control goes to the peripheral with the highest priority.

Analog input and some digital input functions are not included in the list below. These input functions can remain active when the pin is configured as an output. Certain digital input functions, such as the EUSART RX signal, override other port functions and are included in the priority list.

# TABLE 12-5: PORTB OUTPUT PRIORITY

| Pin Name | Function Priority <sup>(1)</sup>                                                                      |

|----------|-------------------------------------------------------------------------------------------------------|

| RB0      | P1A<br>RB0                                                                                            |

| RB1      | SDA1<br>RX/DT<br>RB1                                                                                  |

| RB2      | SDA2 (PIC16(L)F1827 only)<br>TX/CK<br>RX/DT<br>SDO1<br>RB2                                            |

| RB3      | MDOUT<br>CCP1/P1A<br>RB3                                                                              |

| RB4      | SCL1<br>SCK1<br>RB4                                                                                   |

| RB5      | SCL2 (PIC16(L)F1827 only)<br>TX/CK<br>SCK2 (PIC16(L)F1827 only)<br>P1B<br>RB5                         |

| RB6      | ICSPCLK (Programming)<br>T1OSI<br>P1C<br>CCP2 (PIC16(L)F1827 only)<br>P2A (PIC16(L)F1827 only)<br>RB6 |

| RB7      | ICSPDAT (Programming)<br>T1OSO<br>P1D<br>P2B (PIC16(L)F1827 only)<br>RB7                              |

Note 1: Priority listed from highest to lowest.

| Name    | Bit 7                   | Bit 6                   | Bit 5    | Bit 4    | Bit 3   | Bit 2   | Bit 1   | Bit 0    | Register<br>on Page |

|---------|-------------------------|-------------------------|----------|----------|---------|---------|---------|----------|---------------------|

| ADCON0  | _                       | CHS4                    | CHS3     | CHS2     | CHS1    | CHS0    | GO/DONE | ADON     | 145                 |

| ADCON1  | ADFM                    | ADCS2                   | ADCS1    | ADCS0    | —       | ADNREF  | ADPREF1 | ADPREF0  | 146                 |

| ADRESH  | A/D Result I            | VD Result Register High |          |          |         |         |         |          | 147, 148            |

| ADRESL  | A/D Result Register Low |                         |          |          |         |         |         | 147, 148 |                     |

| ANSELA  | —                       | —                       | —        | ANSA4    | ANSA3   | ANSA2   | ANSA1   | ANSA0    | 123                 |

| ANSELB  | ANSB7                   | ANSB6                   | ANSB5    | ANSB4    | ANSB3   | ANSB2   | ANSB1   | _        | 123                 |

| CCPxCON | PxM1                    | PxM0                    | DCxB1    | DCxB0    | CCPxM3  | CCPxM2  | CCPxM1  | CCPxM0   | 226                 |

| INTCON  | GIE                     | PEIE                    | TMR0IE   | INTE     | IOCE    | TMR0IF  | INTF    | IOCF     | 86                  |

| PIE1    | TMR1GIE                 | ADIE                    | RCIE     | TXIE     | SSP1IE  | CCP1IE  | TMR2IE  | TMR1IE   | 87                  |

| PIR1    | TMR1GIF                 | ADIF                    | RCIF     | TXIF     | SSP1IF  | CCP1IF  | TMR2IF  | TMR1IF   | 91                  |

| TRISA   | TRISA7                  | TRISA6                  | TRISA5   | TRISA4   | TRISA3  | TRISA2  | TRISA1  | TRISA0   | 123                 |

| TRISB   | TRISB7                  | TRISB6                  | TRISB5   | TRISB4   | TRISB3  | TRISB2  | TRISB1  | TRISB0   | 123                 |

| FVRCON  | FVREN                   | FVRRDY                  | Reserved | Reserved | CDAFVR1 | CDAFVR0 | ADFVR1  | ADFVR0   | 136                 |

| DACCON0 | DACEN                   | DACLPS                  | DACOE    | —        | DACPSS1 | DACPSS0 | —       | DACNSS   | 156                 |

| DACCON1 | —                       | _                       | —        | DACR4    | DACR3   | DACR2   | DACR1   | DACR0    | 156                 |

TABLE 16-3: SUMMARY OF REGISTERS ASSOCIATED WITH ADC

**Legend:** — = unimplemented read as '0'. Shaded cells are not used for ADC module.

# 21.1 Timer1 Operation

The Timer1 module is a 16-bit incrementing counter which is accessed through the TMR1H:TMR1L register pair. Writes to TMR1H or TMR1L directly update the counter.

When used with an internal clock source, the module is a timer and increments on every instruction cycle. When used with an external clock source, the module can be used as either a timer or counter and increments on every selected edge of the external source.

Timer1 is enabled by configuring the TMR1ON and TMR1GE bits in the T1CON and T1GCON registers, respectively. Table 21-1 displays the Timer1 enable selections.

| TABLE 21-1: | TIMER1 ENABLE |

|-------------|---------------|

|             | SELECTIONS    |

| TMR10N | TMR1GE Timer1<br>Operation |               |

|--------|----------------------------|---------------|

| 0      | 0                          | Off           |

| 0      | 1                          | Off           |

| 1      | 0                          | Always On     |

| 1      | 1                          | Count Enabled |

# 21.2 Clock Source Selection

The TMR1CS<1:0> and T1OSCEN bits of the T1CON register are used to select the clock source for Timer1. Table 21-2 displays the clock source selections.

#### 21.2.1 INTERNAL CLOCK SOURCE

When the internal clock source is selected the TMR1H:TMR1L register pair will increment on multiples of Fosc as determined by the Timer1 prescaler.

When the Fosc internal clock source is selected, the Timer1 register value will increment by four counts every instruction clock cycle. Due to this condition, a 2 LSB error in resolution will occur when reading the Timer1 value. To utilize the full resolution of Timer1, an asynchronous input signal must be used to gate the Timer1 clock input.

The following asynchronous sources may be used:

- Asynchronous event on the T1G pin to Timer1 gate

- C1 or C2 comparator input to Timer1 gate

#### 21.2.2 EXTERNAL CLOCK SOURCE

When the external clock source is selected, the Timer1 module may work as a timer or a counter.

When enabled to count, Timer1 is incremented on the rising edge of the external clock input T1CKI or the capacitive sensing oscillator signal. Either of these external clock sources can be synchronized to the microcontroller system clock or they can run asynchronously.

When used as a timer with a clock oscillator, an external 32.768 kHz crystal can be used in conjunction with the dedicated internal oscillator circuit.

- **Note:** In Counter mode, a falling edge must be registered by the counter prior to the first incrementing rising edge after any one or more of the following conditions:

- Timer1 enabled after POR

- Write to TMR1H or TMR1L

- Timer1 is disabled

- Timer1 is disabled (TMR1ON = 0) when T1CKI is high then Timer1 is enabled (TMR1ON=1) when T1CKI is low.

| TMR1CS1 | TMR1CS0 | T1OSCEN | Clock Source                   |

|---------|---------|---------|--------------------------------|

| 0       | 0       | x       | Instruction Clock (Fosc/4)     |

| 0       | 1       | x       | System Clock (FOSC)            |

| 1       | 0       | 0       | External Clocking on T1CKI Pin |

| 1       | 0       | 0       | External Clocking on T1CKI Pin |

| 1       | 1       | x       | Capacitive Sensing Oscillator  |

#### TABLE 21-2: CLOCK SOURCE SELECTIONS

#### 24.1.5 CAPTURE DURING SLEEP

Capture mode depends upon the Timer1 module for proper operation. There are two options for driving the Timer1 module in Capture mode. It can be driven by the instruction clock (FOSC/4), or by an external clock source.

When Timer1 is clocked by Fosc/4, Timer1 will not increment during Sleep. When the device wakes from Sleep, Timer1 will continue from its previous state.

Capture mode will operate during Sleep when Timer1 is clocked by an external clock source.

#### 24.1.6 ALTERNATE PIN LOCATIONS

This module incorporates I/O pins that can be moved to other locations with the use of the alternate pin function registers, APFCON0 and APFCON1. To determine which pins can be moved and what their default locations are upon a reset, see **Section 12.1 "Alternate Pin Function"** for more information.

| Name                                                 | Bit 7                                                                          | Bit 6                                     | Bit 5         | Bit 4                 | Bit 3                  | Bit 2    | Bit 1  | Bit 0                 | Register<br>on Page |

|------------------------------------------------------|--------------------------------------------------------------------------------|-------------------------------------------|---------------|-----------------------|------------------------|----------|--------|-----------------------|---------------------|

| APFCON0                                              | RXDTSEL                                                                        | SDO1SEL                                   | SS1SEL        | P2BSEL <sup>(2)</sup> | CCP2SEL <sup>(2)</sup> | P1DSEL   | P1CSEL | CCP1SEL               | 119                 |

| CCPxCON                                              | PxM1 <sup>(1)</sup>                                                            | PxM0 <sup>(1)</sup>                       | DCxB1         | DCxB0                 | CCPxM3                 | CCPxM2   | CCPxM1 | CCPxM0                | 226                 |

| CCPRxL Capture/Compare/PWM Register x Low Byte (LSB) |                                                                                |                                           |               |                       |                        |          |        |                       | 204*                |

| CCPRxH                                               | Capture/Cor                                                                    | mpare/PWM                                 | Register x H  | igh Byte (MS          | B)                     |          |        |                       | 204*                |

| CM1CON0                                              | C10N                                                                           | C10N C10UT C10E C1POL — C1SP C1HYS C1SYNC |               |                       |                        |          |        | 170                   |                     |

| CM1CON1                                              | C1INTP                                                                         | C1INTN                                    | C1PCH1        | C1PCH0                | —                      | _        | C1NCH1 | C1NCH0                | 171                 |

| CM2CON0                                              | C2ON                                                                           | C2OUT                                     | C2OE          | C2POL                 | —                      | C2SP     | C2HYS  | C2SYNC                | 170                 |

| CM2CON1                                              | C2INTP                                                                         | C2INTN                                    | C2PCH1        | C2PCH0                | —                      | _        | C2NCH1 | C2NCH0                | 171                 |

| INTCON                                               | GIE                                                                            | PEIE                                      | TMR0IE        | INTE                  | IOCIE                  | TMR0IF   | INTF   | IOCIF                 | 86                  |

| PIE1                                                 | TMR1GIE                                                                        | ADIE                                      | RCIE          | TXIE                  | SSP1IE                 | CCP1IE   | TMR2IE | TMR1IE                | 87                  |

| PIE2                                                 | OSFIE                                                                          | C2IE                                      | C1IE          | EEIE                  | BCL1IE                 | _        | _      | CCP2IE <sup>(2)</sup> | 88                  |

| PIE3 <sup>(2)</sup>                                  | _                                                                              | _                                         | CCP4IE        | CCP3IE                | TMR6IE                 | _        | TMR4IE | _                     | 89                  |

| PIR1                                                 | TMR1GIF                                                                        | ADIF                                      | RCIF          | TXIF                  | SSP1IF                 | CCP1IF   | TMR2IF | TMR1IF                | 91                  |

| PIR2                                                 | OSFIF                                                                          | C2IF                                      | C1IF          | EEIF                  | BCL1IF                 | _        | _      | CCP2IF <sup>(2)</sup> | 92                  |

| PIR3 <sup>(2)</sup>                                  | _                                                                              | _                                         | CCP4IF        | CCP3IF                | TMR6IF                 |          | TMR4IF | _                     | 93                  |

| T1CON                                                | TMR1CS1                                                                        | TMR1CS0                                   | T1CKPS1       | T1CKPS0               | T1OSCEN                | T1SYNC   | _      | TMR10N                | 185                 |

| T1GCON                                               | TMR1GE                                                                         | T1GPOL                                    | T1GTM         | T1GSPM                | T1GGO/DONE             | T1GVAL   | T1GSS1 | T1GSS0                | 186                 |

| TMR1L                                                | IL Holding Register for the Least Significant Byte of the 16-bit TMR1 Register |                                           |               |                       |                        |          |        |                       | 177*                |

| TMR1H                                                | Holding Reg                                                                    | ister for the                             | Most Signific | ant Byte of th        | ne 16-bit TMR1 R       | legister |        |                       | 177*                |

| TRISA                                                | TRISA7                                                                         | TRISA6                                    | TRISA5        | TRISA4                | TRISA3                 | TRISA2   | TRISA1 | TRISA0                | 122                 |

| TRISB                                                | TRISB7                                                                         | TRISB6                                    | TRISB5        | TRISB4                | TRISB3                 | TRISB2   | TRISB1 | TRISB0                | 127                 |

#### TABLE 24-2: SUMMARY OF REGISTERS ASSOCIATED WITH CAPTURE

Legend: - = Unimplemented locations, read as '0'. Shaded cells are not used by Capture mode.

\* Page provides register information.

**Note 1:** Applies to ECCP modules only.

2: PIC16(L)F1827 only.

When one device is transmitting a logical one, or letting the line float, and a second device is transmitting a logical zero, or holding the line low, the first device can detect that the line is not a logical one. This detection, when used on the SCLx line, is called clock stretching. Clock stretching gives slave devices a mechanism to control the flow of data. When this detection is used on the SDAx line, it is called arbitration. Arbitration ensures that there is only one master device communicating at any single time.

# 25.3.1 CLOCK STRETCHING

When a slave device has not completed processing data, it can delay the transfer of more data through the process of Clock Stretching. An addressed slave device may hold the SCLx clock line low after receiving or sending a bit, indicating that it is not yet ready to continue. The master that is communicating with the slave will attempt to raise the SCLx line in order to transfer the next bit, but will detect that the clock line has not yet been released. Because the SCLx connection is open-drain, the slave has the ability to hold that line low until it is ready to continue communicating.

Clock stretching allows receivers that cannot keep up with a transmitter to control the flow of incoming data.

# 25.3.2 ARBITRATION

Each master device must monitor the bus for Start and Stop bits. If the device detects that the bus is busy, it cannot begin a new message until the bus returns to an Idle state.

However, two master devices may try to initiate a transmission on or about the same time. When this occurs, the process of arbitration begins. Each transmitter checks the level of the SDAx data line and compares it to the level that it expects to find. The first transmitter to observe that the two levels don't match, loses arbitration, and must stop transmitting on the SDAx line.

For example, if one transmitter holds the SDAx line to a logical one (lets it float) and a second transmitter holds it to a logical zero (pulls it low), the result is that the SDAx line will be low. The first transmitter then observes that the level of the line is different than expected and concludes that another transmitter is communicating.

The first transmitter to notice this difference is the one that loses arbitration and must stop driving the SDAx line. If this transmitter is also a master device, it also must stop driving the SCLx line. It then can monitor the lines for a Stop condition before trying to reissue its transmission. In the meantime, the other device that has not noticed any difference between the expected and actual levels on the SDAx line continues with it's original transmission. It can do so without any complications, because so far, the transmission appears exactly as expected with no other transmitter disturbing the message.

Slave Transmit mode can also be arbitrated, when a master addresses multiple slaves, but this is less common.

If two master devices are sending a message to two different slave devices at the address stage, the master sending the lower slave address always wins arbitration. When two master devices send messages to the same slave address, and addresses can sometimes refer to multiple slaves, the arbitration process must continue into the data stage.

Arbitration usually occurs very rarely, but it is a necessary process for proper multi-master support.

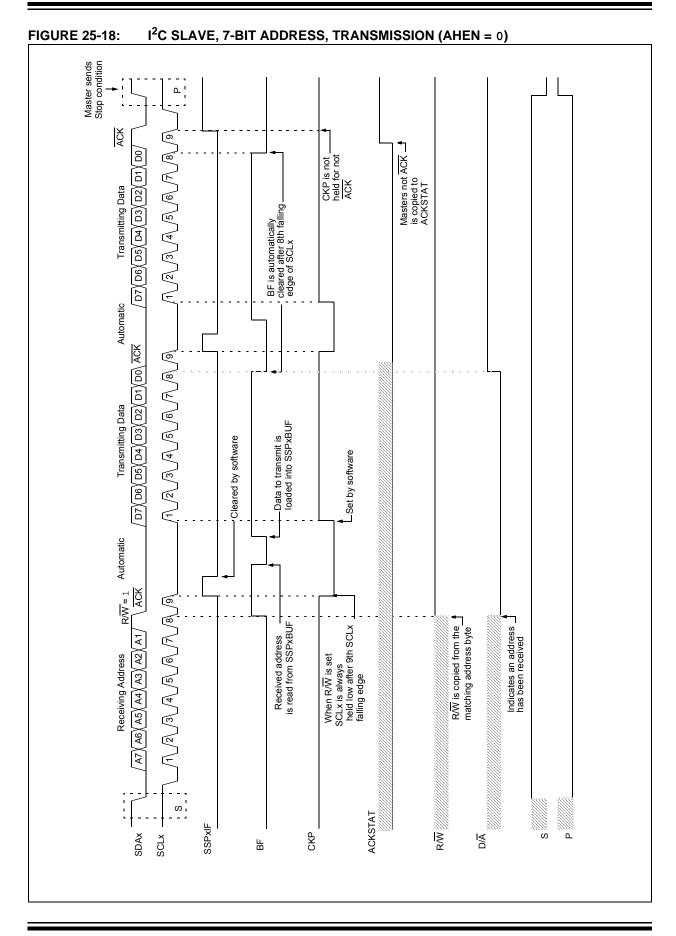

### 25.5.3 SLAVE TRANSMISSION

When the R/W bit of the incoming address byte is set and an address match occurs, the R/W bit of the SSPxSTAT register is set. The received address is loaded into the SSPxBUF register, and an ACK pulse is sent by the slave on the ninth bit.

Following the ACK, slave hardware clears the CKP bit and the SCLx pin is held low (see **Section 25.5.6 "Clock Stretching"** for more detail). By stretching the clock, the master will be unable to assert another clock pulse until the slave is done preparing the transmit data.

The transmit data must be loaded into the SSPxBUF register which also loads the SSPxSR register. Then the SCLx pin should be released by setting the CKP bit of the SSPxCON1 register. The eight data bits are shifted out on the falling edge of the SCLx input. This ensures that the SDAx signal is valid during the SCLx high time.

The ACK pulse from the master-receiver is latched on the rising edge of the ninth SCLx input pulse. This ACK value is copied to the ACKSTAT bit of the SSPxCON2 register. If ACKSTAT is set (not ACK), then the data transfer is complete. In this case, when the not ACK is latched by the slave, the slave goes Idle and waits for another occurrence of the Start bit. If the SDAx line was low (ACK), the next transmit data must be loaded into the SSPxBUF register. Again, the SCLx pin must be released by setting bit CKP.

An MSSPx interrupt is generated for each data transfer byte. The SSPxIF bit must be cleared by software and the SSPxSTAT register is used to determine the status of the byte. The SSPxIF bit is set on the falling edge of the ninth clock pulse.

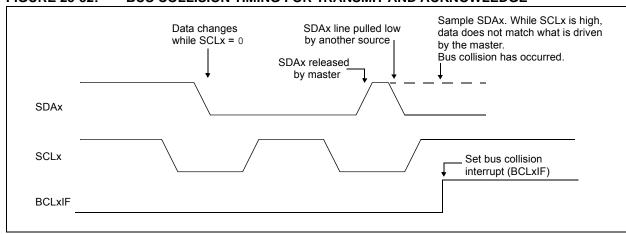

#### 25.5.3.1 Slave Mode Bus Collision

A slave receives a Read request and begins shifting data out on the SDAx line. If a bus collision is detected and the SBCDE bit of the SSPxCON3 register is set, the BCLxIF bit of the PIRx register is set. Once a bus collision is detected, the slave goes Idle and waits to be addressed again. User software can use the BCLxIF bit to handle a slave bus collision.

#### 25.5.3.2 7-bit Transmission

A master device can transmit a read request to a slave, and then clock data out of the slave. The list below outlines what software for a slave will need to do to accomplish a standard transmission. Figure 25-17 can be used as a reference to this list.

- 1. Master sends a Start condition on SDAx and SCLx.

- 2. S bit of SSPxSTAT is set; SSPxIF is set if interrupt on Start detect is enabled.

- Matching address with R/W bit set is received by the Slave setting SSPxIF bit.

- 4. Slave hardware generates an ACK and sets SSPxIF.

- 5. SSPxIF bit is cleared by user.

- 6. Software reads the received address from SSPxBUF, clearing BF.

- 7.  $R/\overline{W}$  is set so CKP was automatically cleared after the ACK.

- 8. The slave software loads the transmit data into SSPxBUF.

- 9. CKP bit is set releasing SCLx, allowing the master to clock the data out of the slave.

- 10. SSPxIF is set after the ACK response from the master is loaded into the ACKSTAT register.

- 11. SSPxIF bit is cleared.

- 12. The slave software checks the ACKSTAT bit to see if the master wants to clock out more data.

- **Note 1:** If the master ACKs the clock will be stretched.

- ACKSTAT is the only bit updated on the rising edge of SCLx (9th) rather than the falling.

- 13. Steps 9-13 are repeated for each transmitted byte.

- 14. If the master sends a not ACK; the clock is not held, but SSPxIF is still set.

- 15. The master sends a Restart condition or a Stop.

- 16. The slave is no longer addressed.

© 2011 Microchip Technology Inc.

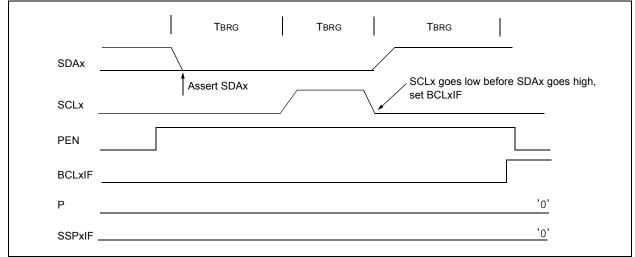

#### FIGURE 25-32: BUS COLLISION TIMING FOR TRANSMIT AND ACKNOWLEDGE

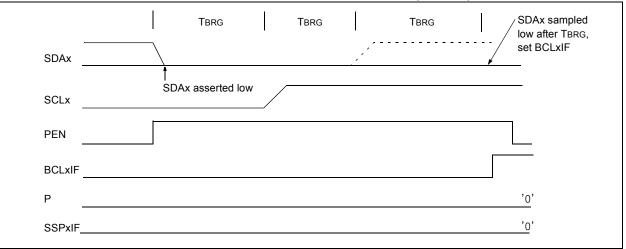

#### 25.6.13.3 Bus Collision During a Stop Condition

Bus collision occurs during a Stop condition if:

- a) After the SDAx pin has been deasserted and allowed to float high, SDAx is sampled low after the BRG has timed out.

- b) After the SCLx pin is deasserted, SCLx is sampled low before SDAx goes high.

The Stop condition begins with SDAx asserted low. When SDAx is sampled low, the SCLx pin is allowed to float. When the pin is sampled high (clock arbitration), the Baud Rate Generator is loaded with SSPxADD and counts down to 0. After the BRG times out, SDAx is sampled. If SDAx is sampled low, a bus collision has occurred. This is due to another master attempting to drive a data '0' (Figure 25-37). If the SCLx pin is sampled low before SDAx is allowed to float high, a bus collision occurs. This is another case of another master attempting to drive a data '0' (Figure 25-38).

#### FIGURE 25-38: BUS COLLISION DURING A STOP CONDITION (CASE 1)

#### FIGURE 25-39: BUS COLLISION DURING A STOP CONDITION (CASE 2)

#### REGISTER 25-1: SSPxSTAT: SSPx STATUS REGISTER

| R/W-0/0          | R/W-0/0                                   | R-0/0                              | R-0/0                                 | R-0/0                               | R-0/0                  | R-0/0               | R-0/0        |

|------------------|-------------------------------------------|------------------------------------|---------------------------------------|-------------------------------------|------------------------|---------------------|--------------|

| SMP              | CKE                                       | D/A                                | Р                                     | S                                   | R/W                    | UA                  | BF           |

| bit 7            | •                                         |                                    |                                       | •                                   |                        |                     | bit          |

|                  |                                           |                                    |                                       |                                     |                        |                     |              |

| Legend:          |                                           |                                    |                                       |                                     |                        |                     |              |

| R = Readable b   | bit                                       | W = Writable b                     | it                                    | U = Unimplem                        | ented bit, read as     | '0'                 |              |

| u = Bit is uncha | nged                                      | x = Bit is unkno                   | own                                   | -n/n = Value at                     | POR and BOR/Va         | alue at all other F | Resets       |

| '1' = Bit is set |                                           | '0' = Bit is clear                 | red                                   |                                     |                        |                     |              |

|                  |                                           |                                    |                                       |                                     |                        |                     |              |

| bit 7            |                                           | Input Sample bi                    | t                                     |                                     |                        |                     |              |

|                  | SPI Master mo                             | <u>de:</u><br>sampled at end c     | of data output ti                     | mo                                  |                        |                     |              |

|                  | •                                         | sampled at middl                   | •                                     |                                     |                        |                     |              |

|                  | SPI Slave mod                             |                                    |                                       |                                     |                        |                     |              |

|                  |                                           | leared when SP                     | l is used in Slav                     | ve mode                             |                        |                     |              |

|                  | In I <sup>2</sup> C Master o              |                                    |                                       |                                     |                        |                     |              |

|                  |                                           |                                    | •                                     | eed mode (100 k                     | Hz and 1 MHz)          |                     |              |

| h it 0           |                                           | control enabled f                  |                                       |                                     |                        |                     |              |

| bit 6            |                                           | k Edge Select bi                   | t (SPI mode oni                       | y)                                  |                        |                     |              |

|                  | <u>In SPI Master o</u><br>1 = Transmit or | curs on transitio                  | n from active to                      | ldle clock state                    |                        |                     |              |

|                  |                                           | ccurs on transitio                 |                                       |                                     |                        |                     |              |

|                  | <u>In I<sup>2</sup>C™ mode</u>            |                                    |                                       |                                     |                        |                     |              |

|                  |                                           | •                                  |                                       | ompliant with SM                    | bus™ specificatio      | on                  |              |

|                  |                                           | l bus™ specific i                  | •                                     |                                     |                        |                     |              |

| bit 5            |                                           | ress bit (I <sup>2</sup> C mod     |                                       |                                     |                        |                     |              |

|                  |                                           | •                                  |                                       | smitted was data<br>smitted was add |                        |                     |              |

| h:+ 1            | P: Stop bit                               | iat the last byte i                | eceived of train                      | sinilleu was auu                    | 635                    |                     |              |

| bit 4            | •                                         | This hit is clear                  | od whon the M                         |                                     | disabled, SSPxEN       | is closered )       |              |

|                  |                                           |                                    |                                       | last (this bit is '0                |                        | is cleared.)        |              |

|                  |                                           | s not detected la                  |                                       |                                     | on Reset               |                     |              |

| bit 3            | S: Start bit                              |                                    |                                       |                                     |                        |                     |              |

|                  | (I <sup>2</sup> C mode only               | This bit is clear                  | ed when the MS                        | SSPx module is o                    | disabled, SSPxEN       | is cleared.)        |              |

|                  |                                           |                                    |                                       | last (this bit is '0                |                        |                     |              |

|                  | 0 = Start bit wa                          | s not detected la                  | st                                    |                                     |                        |                     |              |

| bit 2            | R/W: Read/Wri                             | te bit information                 | ı (I <sup>2</sup> C mode onl          | y)                                  |                        |                     |              |

|                  | 4 - 41                                    | 4 h 14 Offerer h 14 offerer        | A A A A A A A A A A A A A A A A A A A | he last address r                   | natch. This bit is o   | nly valid from the  | address matc |

|                  | In I <sup>2</sup> C Slave mo              | t bit, Stop bit, or<br>ode:        | HOLACK DIL                            |                                     |                        |                     |              |

|                  | 1 = Read                                  | <u></u>                            |                                       |                                     |                        |                     |              |

|                  | 0 = Write                                 |                                    |                                       |                                     |                        |                     |              |

|                  | In I <sup>2</sup> C Master n              |                                    |                                       |                                     |                        |                     |              |

|                  | 1 = Transmit i                            | s in progress<br>s not in progress |                                       |                                     |                        |                     |              |

|                  |                                           |                                    |                                       | CEN or ACKEN                        | will indicate if the I | MSSPx is in Idle    | mode.        |

| bit 1            | -                                         | dress bit (10-bit                  |                                       |                                     |                        |                     |              |

|                  |                                           |                                    |                                       |                                     | SPxADD register        |                     |              |

|                  |                                           | es not need to b                   | •                                     |                                     | Ū                      |                     |              |

| bit 0            | BF: Buffer Full                           | Status bit                         |                                       |                                     |                        |                     |              |

|                  | <u>Receive (SPI a</u>                     |                                    |                                       |                                     |                        |                     |              |

|                  |                                           | mplete, SSPxBL                     |                                       |                                     |                        |                     |              |

|                  |                                           | t complete, SSP                    | xBUF is empty                         |                                     |                        |                     |              |

|                  | <u>Transmit (<math>I^2Cn</math></u>       |                                    | loes not include                      | the ACK and St                      | op bits), SSPxBUI      | = ie full           |              |

|                  |                                           |                                    |                                       |                                     |                        |                     |              |

#### REGISTER 25-2: SSPxCON1: SSPx CONTROL REGISTER 1

| R/C/HS-0/0              | R/C/HS-0/0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | R/W-0/0                                                                                                                                                                    | R/W-0/0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | R/W-0/0                                                                                                 | R/W-0/0                                    | R/W-0/0                                            | R/W-0/0                                     |

|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|--------------------------------------------|----------------------------------------------------|---------------------------------------------|

| WCOL                    | SSPxOV                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | SSPxEN                                                                                                                                                                     | CKP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                         | SSPx                                       | M<3:0>                                             |                                             |

| bit 7                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                         |                                            |                                                    | bit                                         |

|                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                         |                                            |                                                    |                                             |

| Legend:                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                         |                                            |                                                    |                                             |