# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Detuns                     |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 32MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                           |

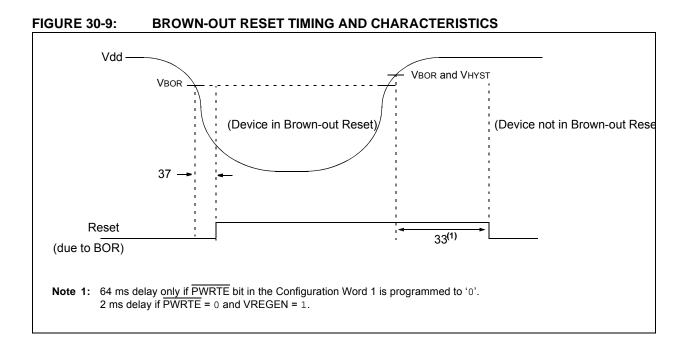

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 16                                                                          |

| Program Memory Size        | 7KB (4K x 14)                                                               |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 256 x 8                                                                     |

| RAM Size                   | 384 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 12x10b                                                                  |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                                              |

| Supplier Device Package    | 20-SSOP                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1827t-i-ss |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

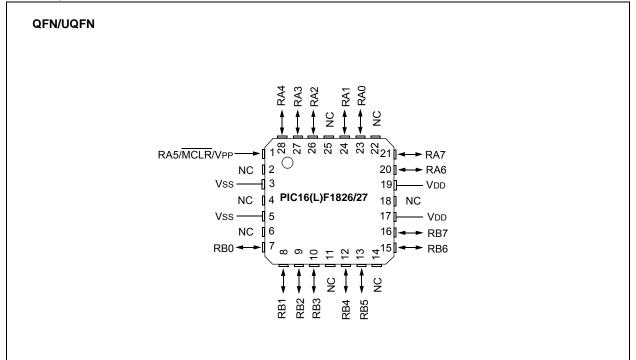

# Pin Diagram – 28-Pin QFN/UQFN (PIC16(L)F1826/27)

#### 3.1.1.2 Indirect Read with FSR

The program memory can be accessed as data by setting bit 7 of the FSRxH register and reading the matching INDFx register. The MOVIW instruction will place the lower 8 bits of the addressed word in the W register. Writes to the program memory cannot be performed via the INDF registers. Instructions that access the program memory via the FSR require one extra instruction cycle to complete. Example 3-2 demonstrates accessing the program memory via an FSR.

The HIGH directive will set bit<7> if a label points to a location in program memory.

#### EXAMPLE 3-2: ACCESSING PROGRAM MEMORY VIA FSR

| constants |          |        |         |      |  |

|-----------|----------|--------|---------|------|--|

| RETLW     | DATA0    |        | ;Index0 | data |  |

| RETLW     | DATA1    |        | ;Index1 | data |  |

| RETLW     | DATA2    |        |         |      |  |

| RETLW     | data3    |        |         |      |  |

| my_functi | on       |        |         |      |  |

| ;… LOI    | TS OF CO | DE     |         |      |  |

| MOVLW     | LOW cc   | nstant | LS      |      |  |

| MOVWF     | FSR1L    |        |         |      |  |

| MOVLW     | HIGH c   | onstar | nts     |      |  |

| MOVWF     | FSR1H    |        |         |      |  |

| MOVIW     | 0[FSR1]  |        |         |      |  |

| ;THE PROG | RAM MEMO | RY IS  | IN W    |      |  |

|           |          |        |         |      |  |

# 3.2 Data Memory Organization

The data memory is partitioned in 32 memory banks with 128 bytes in a bank. Each bank consists of (Figure 3-3):

- 12 core registers

- · 20 Special Function Registers (SFR)

- Up to 80 bytes of General Purpose RAM (GPR)

- · 16 bytes of common RAM

The active bank is selected by writing the bank number into the Bank Select Register (BSR). Unimplemented memory will read as '0'. All data memory can be accessed either directly (via instructions that use the file registers) or indirectly via the two File Select Registers (FSR). See **Section 3.5** "Indirect Addressing" for more information.

Data Memory uses a 12-bit address. The upper 7-bit of the address define the Bank address and the lower 5-bits select the registers/RAM in that bank.

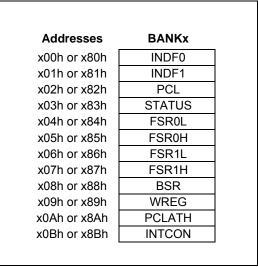

### 3.2.1 CORE REGISTERS

The core registers contain the registers that directly affect the basic operation. The core registers occupy the first 12 addresses of every data memory bank (addresses x00h/x08h through x0Bh/x8Bh). These registers are listed below in Table 3-2. For for detailed information, see Table 3-5.

| Address   | Name       | Bit 7             | Bit 6           | Bit 5         | Bit 4           | Bit 3        | Bit 2        | ,<br>Bit 1 | Bit 0 | Value on<br>POR, BOR | Value on all<br>other<br>Resets |

|-----------|------------|-------------------|-----------------|---------------|-----------------|--------------|--------------|------------|-------|----------------------|---------------------------------|

| Bank 9    |            |                   |                 |               |                 |              |              |            |       |                      |                                 |

| 48Ch      | —          | Unimplement       | ed              |               |                 |              |              |            |       | —                    | -                               |

| 49Fh      |            |                   |                 |               |                 |              |              |            |       |                      |                                 |

| Bank 10   | 0          |                   |                 |               |                 |              |              |            |       |                      |                                 |

| 50Ch      | —          | Unimplement       | ed              |               |                 |              |              |            |       | —                    | -                               |

| 51Fh      |            |                   |                 |               |                 |              |              |            |       |                      |                                 |

| Bank 11   | 1          |                   |                 |               |                 |              |              |            |       | -                    |                                 |

| 58Ch<br>  | —          | Unimplement       | ed              |               |                 |              |              |            |       | —                    | -                               |

| 59Fh      |            |                   |                 |               |                 |              |              |            |       |                      |                                 |

| Bank 12   | 2          |                   |                 |               |                 |              |              |            |       | -                    |                                 |

| 60Ch      | —          | Unimplement       | ed              |               |                 |              |              |            |       | —                    | -                               |

| 61Fh      |            |                   |                 |               |                 |              |              |            |       |                      |                                 |

| Bank 1:   | 3          |                   |                 |               |                 |              |              |            |       |                      |                                 |

| 68Ch<br>— | —          | Unimplement       | ed              |               |                 |              |              |            |       | —                    | _                               |

| 69Fh      |            |                   |                 |               |                 |              |              |            |       |                      |                                 |

| Bank 14   |            |                   |                 |               |                 |              |              |            |       |                      |                                 |

| 70Ch      | —          | Unimplement       | ed              |               |                 |              |              |            |       | —                    | _                               |

| 71Fh      |            |                   |                 |               |                 |              |              |            |       |                      |                                 |

| Bank 1    | 5          |                   |                 |               |                 |              |              |            |       |                      |                                 |

| 78Ch      | —          | Unimplement       | ed              |               |                 |              |              |            |       | —                    | _                               |

| 79Fh      |            |                   |                 |               |                 |              |              |            |       |                      |                                 |

| Bank 16   | 6          |                   |                 |               |                 |              |              |            |       |                      |                                 |

| 80Ch      | —          | Unimplement       | ed              |               |                 |              |              |            |       | —                    | _                               |

| 86Fh      |            |                   |                 |               |                 |              |              |            |       |                      |                                 |

| Bank 17   | 7          |                   |                 |               |                 |              |              |            |       |                      |                                 |

| 88Ch<br>— | —          | Unimplement       | ed              |               |                 |              |              |            |       | —                    | _                               |

| 8EFh      |            |                   |                 |               |                 |              |              |            |       |                      |                                 |

| Bank 18   |            |                   |                 |               |                 |              |              |            |       |                      |                                 |

| 90Ch      | —          | Unimplement       | ed              |               |                 |              |              |            |       | —                    | _                               |

| 96Fh      |            |                   |                 |               |                 |              |              |            |       |                      |                                 |

| Bank 19   | 9          |                   |                 |               |                 |              |              |            |       |                      |                                 |

| 98Ch<br>— | —          | Unimplement       | ed              |               |                 |              |              |            |       | —                    | _                               |

| 9EFh      |            |                   |                 |               |                 |              |              |            |       |                      |                                 |

| Bank 20   | 0          |                   |                 |               |                 |              |              |            |       |                      |                                 |

| A0Ch      | _          | Unimplement       | ed              |               |                 |              |              |            |       | _                    | -                               |

| A6Fh      | -          |                   |                 |               |                 |              |              |            |       |                      |                                 |

| Bank 2    | 1          | Linimalana        | ad              |               |                 |              |              |            |       |                      |                                 |

| A8Ch<br>— | _          | Unimplement       | ed              |               |                 |              |              |            |       | _                    | _                               |

| AEFh      | _          |                   |                 |               |                 |              |              |            |       |                      |                                 |

| Bank 22   |            | I I minus I and a |                 |               |                 |              |              |            |       |                      |                                 |

| B0Ch      | _          | Unimplement       | ed              |               |                 |              |              |            |       | —                    | _                               |

| B6Fh      |            |                   |                 |               |                 |              |              |            |       |                      |                                 |

| Legend:   | x = unknov | vn, u = unchange  | ed, q = value o | depends on co | ndition, - = un | implemented, | r = reserved | 1.         |       |                      |                                 |

**TABLE 3-6:** SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)

Legend:

x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, r = reserved. Shaded locations are unimplemented, read as '0'.

Note

1:

PIC16(L)F1827 only.

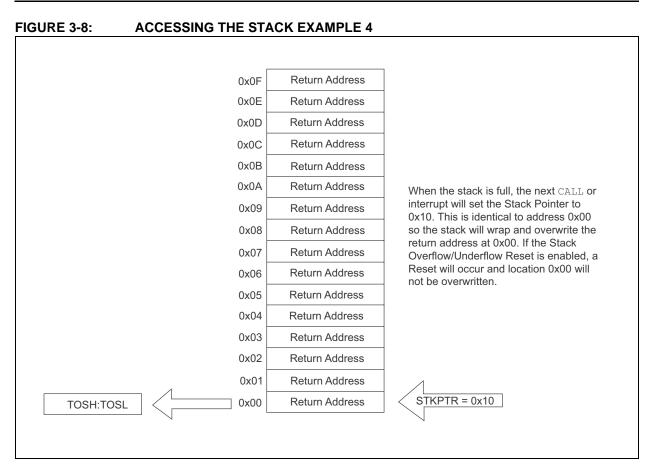

# 3.4.2 OVERFLOW/UNDERFLOW RESET

If the STVREN bit in Configuration Word 2 is programmed to '1', the device will be reset if the stack is PUSHed beyond the sixteenth level or POPed beyond the first level, setting the appropriate bits (STKOVF or STKUNF, respectively) in the PCON register.

#### 3.5 Indirect Addressing

The INDFn registers are not physical registers. Any instruction that accesses an INDFn register actually accesses the register at the address specified by the File Select Registers (FSR). If the FSRn address specifies one of the two INDFn registers, the read will return '0' and the write will not occur (though Status bits may be affected). The FSRn register value is created by the pair FSRnH and FSRnL.

The FSR registers form a 16-bit address that allows an addressing space with 65536 locations. These locations are divided into three memory regions:

- Traditional Data Memory

- Linear Data Memory

- Program Flash Memory

#### 5.2.2.6 32 MHz Internal Oscillator Frequency Selection

The Internal Oscillator Block can be used with the 4X PLL associated with the External Oscillator Block to produce a 32 MHz internal system clock source. The following settings are required to use the 32 MHz internal clock source:

- The FOSC bits in Configuration Word 1 must be set to use the INTOSC source as the device system clock (FOSC<2:0> = 100).

- The SCS bits in the OSCCON register must be cleared to use the clock determined by FOSC<2:0> in Configuration Word 1 (SCS<1:0> = 00).

- The IRCF bits in the OSCCON register must be set to the 8 MHz HFINTOSC set to use (IRCF<3:0> = 1110).

- The SPLLEN bit in the OSCCON register must be set to enable the 4xPLL, or the PLLEN bit of the Configuration Word 2 must be programmed to a '1'.

- Note: When using the PLLEN bit of the Configuration Word 2, the 4xPLL cannot be disabled by software and the 8 MHz HFINTOSC option will no longer be available.

The 4xPLL is not available for use with the internal oscillator when the SCS bits of the OSCCON register are set to '1x'. The SCS bits must be set to '00' to use the 4xPLL with the internal oscillator.

### 5.2.2.7 Internal Oscillator Clock Switch Timing

When switching between the HFINTOSC, MFINTOSC and the LFINTOSC, the new oscillator may already be shut down to save power (see Figure 5-7). If this is the case, there is a delay after the IRCF<3:0> bits of the OSCCON register are modified before the frequency selection takes place. The OSCSTAT register will reflect the current active status of the HFINTOSC, MFINTOSC and LFINTOSC oscillators. The sequence of a frequency selection is as follows:

- 1. IRCF<3:0> bits of the OSCCON register are modified.

- 2. If the new clock is shut down, a clock start-up delay is started.

- 3. Clock switch circuitry waits for a falling edge of the current clock.

- 4. The current clock is held low and the clock switch circuitry waits for a rising edge in the new clock.

- 5. The new clock is now active.

- 6. The OSCSTAT register is updated as required.

- 7. Clock switch is complete.

See Figure 5-7 for more details.

If the internal oscillator speed is switched between two clocks of the same source, there is no start-up delay before the new frequency is selected. Clock switching time delays are shown in Table 5-1.

Start-up delay specifications are located in the oscillator tables of **Section 30.0** "**Electrical Specifications**".

# 8.3 Interrupts During Sleep

Some interrupts can be used to wake from Sleep. To wake from Sleep, the peripheral must be able to operate without the system clock. The interrupt source must have the appropriate Interrupt Enable bit(s) set prior to entering Sleep.

On waking from Sleep, if the GIE bit is also set, the processor will branch to the interrupt vector. Otherwise, the processor will continue executing instructions after the SLEEP instruction. The instruction directly after the SLEEP instruction will always be executed before branching to the ISR. Refer to **Section 9.0 "Power-Down Mode (Sleep)"** for more details.

## 8.4 INT Pin

The INT pin can be used to generate an asynchronous edge-triggered interrupt. This interrupt is enabled by setting the INTE bit of the INTCON register. The INTEDG bit of the OPTION\_REG register determines on which edge the interrupt will occur. When the INTEDG bit is set, the rising edge will cause the interrupt. When the INTEDG bit is clear, the falling edge will cause the interrupt. The INTF bit of the INTCON register will be set when a valid edge appears on the INT pin. If the GIE and INTE bits are also set, the processor will redirect program execution to the interrupt vector.

# 8.5 Automatic Context Saving

Upon entering an interrupt, the return PC address is saved on the stack. Additionally, the following registers are automatically saved in the Shadow registers:

- W register

- STATUS register (except for TO and PD)

- BSR register

- FSR registers

- PCLATH register

Upon exiting the Interrupt Service Routine, these registers are automatically restored. Any modifications to these registers during the ISR will be lost. If modifications to any of these registers are desired, the corresponding Shadow register should be modified and the value will be restored when exiting the ISR. The Shadow registers are available in Bank 31 and are readable and writable. Depending on the user's application, other registers may also need to be saved.

# 11.0 DATA EEPROM AND FLASH PROGRAM MEMORY CONTROL

The Data EEPROM and Flash program memory are readable and writable during normal operation (full VDD range). These memories are not directly mapped in the register file space. Instead, they are indirectly addressed through the Special Function Registers (SFRs). There are six SFRs used to access these memories:

- EECON1

- EECON2

- EEDATL

- EEDATH

- EEADRL

- EEADRH

When interfacing the data memory block, EEDATL holds the 8-bit data for read/write, and EEADRL holds the address of the EEDATL location being accessed. These devices have 256 bytes of data EEPROM with an address range from 0h to 0FFh.

When accessing the program memory block, the EED-ATH:EEDATL register pair forms a 2-byte word that holds the 14-bit data for read/write, and the EEADRL and EEADRH registers form a 2-byte word that holds the 15-bit address of the program memory location being read.

The EEPROM data memory allows byte read and write. An EEPROM byte write automatically erases the location and writes the new data (erase before write).

The write time is controlled by an on-chip timer. The write/erase voltages are generated by an on-chip charge pump rated to operate over the voltage range of the device for byte or word operations.

Depending on the setting of the Flash Program Memory Self Write Enable bits WRT<1:0> of the Configuration Word 2, the device may or may not be able to write certain blocks of the program memory. However, reads from the program memory are always allowed.

When the device is code-protected, the device programmer can no longer access data or program memory. When code-protected, the CPU may continue to read and write the data EEPROM memory and Flash program memory.

### 11.1 EEADRL and EEADRH Registers

The EEADRH:EEADRL register pair can address up to a maximum of 256 bytes of data EEPROM or up to a maximum of 32K words of program memory.

When selecting a program address value, the MSB of the address is written to the EEADRH register and the LSB is written to the EEADRL register. When selecting a EEPROM address value, only the LSB of the address is written to the EEADRL register.

#### 11.1.1 EECON1 AND EECON2 REGISTERS

EECON1 is the control register for EE memory accesses.

Control bit EEPGD determines if the access will be a program or data memory access. When clear, any subsequent operations will operate on the EEPROM memory. When set, any subsequent operations will operate on the program memory. On Reset, EEPROM is selected by default.

Control bits RD and WR initiate read and write, respectively. These bits cannot be cleared, only set, in software. They are cleared in hardware at completion of the read or write operation. The inability to clear the WR bit in software prevents the accidental, premature termination of a write operation.

The WREN bit, when set, will allow a write operation to occur. On power-up, the WREN bit is clear. The WRERR bit is set when a write operation is interrupted by a Reset during normal operation. In these situations, following Reset, the user can check the WRERR bit and execute the appropriate error handling routine.

Interrupt flag bit EEIF of the PIR2 register is set when write is complete. It must be cleared in the software.

Reading EECON2 will read all '0's. The EECON2 register is used exclusively in the data EEPROM write sequence. To enable writes, a specific pattern must be written to EECON2.

# 11.6 Write Verify

Depending on the application, good programming practice may dictate that the value written to the data EEPROM or program memory should be verified (see Example 11-6) to the desired value to be written. Example 11-6 shows how to verify a write to EEPROM.

#### EXAMPLE 11-6: EEPROM WRITE VERIFY

| BANKSEI | LEEDATL    | ;                    |

|---------|------------|----------------------|

| MOVF    | EEDATL, W  | ;EEDATL not changed  |

|         |            | ;from previous write |

| BSF     | EECON1, RD | ;YES, Read the       |

|         |            | ;value written       |

| XORWF   | EEDATL, W  | ;                    |

| BTFSS   | STATUS, Z  | ;Is data the same    |

| GOTO    | WRITE_ERR  | ;No, handle error    |

| :       |            | ;Yes, continue       |

| 1       |            |                      |

| SRCLK | Divider | Fosc = 32 MHz | Fosc = 20 MHz | Fosc = 16 MHz | Fosc = 4 MHz | Fosc = 1 MHz |

|-------|---------|---------------|---------------|---------------|--------------|--------------|

| 111   | 512     | 62.5 kHz      | 39.0 kHz      | 31.3 kHz      | 7.81 kHz     | 1.95 kHz     |

| 110   | 256     | 125 kHz       | 78.1 kHz      | 62.5 kHz      | 15.6 kHz     | 3.90 kHz     |

| 101   | 128     | 250 kHz       | 156 kHz       | 125 kHz       | 31.25 kHz    | 7.81 kHz     |

| 100   | 64      | 500 kHz       | 313 kHz       | 250 kHz       | 62.5 kHz     | 15.6 kHz     |

| 011   | 32      | 1 MHz         | 625 kHz       | 500 kHz       | 125 kHz      | 31.3 kHz     |

| 010   | 16      | 2 MHz         | 1.25 MHz      | 1 MHz         | 250 kHz      | 62.5 kHz     |

| 001   | 8       | 4 MHz         | 2.5 MHz       | 2 MHz         | 500 kHz      | 125 kHz      |

| 000   | 4       | 8 MHz         | 5 MHz         | 4 MHz         | 1 MHz        | 250 kHz      |

### TABLE 18-1: SRCLK FREQUENCY TABLE

## REGISTER 18-1: SRCON0: SR LATCH CONTROL 0 REGISTER

| R/W-0/0 | R/W-0/0 | R/W-0/0    | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/S-0/0 | R/S-0/0 |

|---------|---------|------------|---------|---------|---------|---------|---------|

| SRLEN   |         | SRCLK<2:0> |         | SRQEN   | SRNQEN  | SRPS    | SRPR    |

| bit 7   |         |            |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | S = Bit is set only                                   |

| bit 7      | SRLEN: SR Latch Enable bit<br>1 = SR Latch is enabled<br>0 = SR Latch is disabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6-4    | <b>SRCLK&lt;2:0&gt;:</b> SR Latch Clock Divider bits<br>000 = Generates a 1 Fosc wide pulse every 4th Fosc cycle clock<br>001 = Generates a 1 Fosc wide pulse every 8th Fosc cycle clock<br>010 = Generates a 1 Fosc wide pulse every 16th Fosc cycle clock<br>011 = Generates a 1 Fosc wide pulse every 32nd Fosc cycle clock<br>100 = Generates a 1 Fosc wide pulse every 64th Fosc cycle clock<br>101 = Generates a 1 Fosc wide pulse every 128th Fosc cycle clock<br>110 = Generates a 1 Fosc wide pulse every 256th Fosc cycle clock<br>111 = Generates a 1 Fosc wide pulse every 512th Fosc cycle clock |

| bit 3      | SRQEN: SR Latch Q Output Enable bit<br><u>If SRLEN = 1</u> :<br>1 = Q is present on the SRQ pin<br>0 = External Q output is disabled<br><u>If SRLEN = 0</u> :<br>SR Latch is disabled                                                                                                                                                                                                                                                                                                                                                                                                                         |

| bit 2      | SRNQEN: SR Latch Q Output Enable bit<br><u>If SRLEN = 1</u> :<br>1 = Q is present on the SRnQ pin<br>0 = External Q output is disabled<br><u>If SRLEN = 0</u> :<br>SR Latch is disabled                                                                                                                                                                                                                                                                                                                                                                                                                       |

| bit 1      | <ul> <li>SRPS: Pulse Set Input of the SR Latch bit<sup>(1)</sup></li> <li>1 = Pulse set input for 1 Q-clock period</li> <li>0 = No effect on set input.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| bit 0      | <ul> <li>SRPR: Pulse Reset Input of the SR Latch bit<sup>(1)</sup></li> <li>1 = Pulse reset input for 1 Q-clock period</li> <li>0 = No effect on reset input.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Note 1: Se | t only, always reads back '0'.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

NOTES:

| Name                | Bit 7                                                        | Bit 6           | Bit 5         | Bit 4                  | Bit 3    | Bit 2  | Bit 1   | Bit 0   | Register<br>on Page |  |

|---------------------|--------------------------------------------------------------|-----------------|---------------|------------------------|----------|--------|---------|---------|---------------------|--|

| INTCON              | GIE                                                          | PEIE            | TMR0IE        | INTE                   | IOCIE    | TMR0IF | INTF    | IOCIF   | 91                  |  |

| PIE1                | TMR1GIE                                                      | ADIE            | RCIE          | TXIE                   | SSP1IE   | CCP1IE | TMR2IE  | TMR1IE  | 92                  |  |

| PIR1                | TMR1GIF                                                      | ADIF            | RCIF          | TXIF                   | SSP1IF   | CCP1IF | TMR2IF  | TMR1IF  | 96                  |  |

| PIE3 <sup>(1)</sup> | —                                                            | _               | CCP4IE        | CCP3IE                 | TMR6IE   |        | TMR4IE  | _       | 94                  |  |

| PIR3 <sup>(1)</sup> | —                                                            | _               | CCP4IF        | CCP3IF                 | TMR6IF   | _      | TMR4IF  | —       | 98                  |  |

| PR2                 | Timer2 Mod                                                   | ule Period Re   | gister        |                        |          |        |         |         | 189*                |  |

| PR4                 | Timer4 Mod                                                   | ule Period Re   | gister        |                        |          |        |         |         | 189*                |  |

| PR6                 | Timer6 Mod                                                   | ule Period Re   | gister        |                        |          |        |         |         | 189*                |  |

| T2CON               | —                                                            | T2OUTPS3        | T2OUTPS2      | T2OUTPS1               | T2OUTPS0 | TMR2ON | T2CKPS1 | T2CKPS0 | 191                 |  |

| T4CON               | —                                                            | T4OUTPS3        | T4OUTPS2      | T4OUTPS1               | T4OUTPS0 | TMR4ON | T4CKPS1 | T4CKPS0 | 191                 |  |

| T6CON               | —                                                            | T6OUTPS3        | T6OUTPS2      | T6OUTPS1               | T6OUTPS0 | TMR6ON | T6CKPS1 | T6CKPS0 | 191                 |  |

| TMR2                | Holding Register for the 8-bit TMR2 Time Base                |                 |               |                        |          |        |         |         |                     |  |

| TMR4                | Holding Register for the 8-bit TMR4 Time Base <sup>(1)</sup> |                 |               |                        |          |        |         |         |                     |  |

| TMR6                | Holding Reg                                                  | ister for the 8 | -bit TMR6 Tin | ne Base <sup>(1)</sup> |          |        |         |         | 189*                |  |

#### TABLE 22-1: SUMMARY OF REGISTERS ASSOCIATED WITH TIMER2/4/6

Legend: — = unimplemented read as '0'. Shaded cells are not used for Timer2 module.

\* Page provides register information.

Note 1: PIC16(L)F1827 only.

#### 24.1.5 CAPTURE DURING SLEEP

Capture mode depends upon the Timer1 module for proper operation. There are two options for driving the Timer1 module in Capture mode. It can be driven by the instruction clock (FOSC/4), or by an external clock source.

When Timer1 is clocked by Fosc/4, Timer1 will not increment during Sleep. When the device wakes from Sleep, Timer1 will continue from its previous state.

Capture mode will operate during Sleep when Timer1 is clocked by an external clock source.

#### 24.1.6 ALTERNATE PIN LOCATIONS

This module incorporates I/O pins that can be moved to other locations with the use of the alternate pin function registers, APFCON0 and APFCON1. To determine which pins can be moved and what their default locations are upon a reset, see **Section 12.1 "Alternate Pin Function"** for more information.

| Name                | Bit 7               | Bit 6               | Bit 5         | Bit 4                 | Bit 3                  | Bit 2    | Bit 1  | Bit 0                 | Register<br>on Page |

|---------------------|---------------------|---------------------|---------------|-----------------------|------------------------|----------|--------|-----------------------|---------------------|

| APFCON0             | RXDTSEL             | SDO1SEL             | SS1SEL        | P2BSEL <sup>(2)</sup> | CCP2SEL <sup>(2)</sup> | P1DSEL   | P1CSEL | CCP1SEL               | 119                 |

| CCPxCON             | PxM1 <sup>(1)</sup> | PxM0 <sup>(1)</sup> | DCxB1         | DCxB0                 | CCPxM3                 | CCPxM2   | CCPxM1 | CCPxM0                | 226                 |

| CCPRxL              | Capture/Cor         | mpare/PWM           | Register x L  | ow Byte (LSE          | 3)                     |          |        |                       | 204*                |

| CCPRxH              | Capture/Cor         | mpare/PWM           | Register x H  | igh Byte (MS          | B)                     |          |        |                       | 204*                |

| CM1CON0             | C10N                | C10UT               | C10E          | C1POL                 | _                      | C1SP     | C1HYS  | C1SYNC                | 170                 |

| CM1CON1             | C1INTP              | C1INTN              | C1PCH1        | C1PCH0                | _                      | _        | C1NCH1 | C1NCH0                | 171                 |

| CM2CON0             | C2ON                | C2OUT               | C2OE          | C2POL                 | _                      | C2SP     | C2HYS  | C2SYNC                | 170                 |

| CM2CON1             | C2INTP              | C2INTN              | C2PCH1        | C2PCH0                | _                      |          | C2NCH1 | C2NCH0                | 171                 |

| INTCON              | GIE                 | PEIE                | TMR0IE        | INTE                  | IOCIE                  | TMR0IF   | INTF   | IOCIF                 | 86                  |

| PIE1                | TMR1GIE             | ADIE                | RCIE          | TXIE                  | SSP1IE                 | CCP1IE   | TMR2IE | TMR1IE                | 87                  |

| PIE2                | OSFIE               | C2IE                | C1IE          | EEIE                  | BCL1IE                 |          |        | CCP2IE <sup>(2)</sup> | 88                  |

| PIE3 <sup>(2)</sup> | —                   | _                   | CCP4IE        | CCP3IE                | TMR6IE                 |          | TMR4IE | _                     | 89                  |

| PIR1                | TMR1GIF             | ADIF                | RCIF          | TXIF                  | SSP1IF                 | CCP1IF   | TMR2IF | TMR1IF                | 91                  |

| PIR2                | OSFIF               | C2IF                | C1IF          | EEIF                  | BCL1IF                 |          |        | CCP2IF <sup>(2)</sup> | 92                  |

| PIR3 <sup>(2)</sup> | —                   | _                   | CCP4IF        | CCP3IF                | TMR6IF                 | _        | TMR4IF | _                     | 93                  |

| T1CON               | TMR1CS1             | TMR1CS0             | T1CKPS1       | T1CKPS0               | T1OSCEN                | T1SYNC   | _      | TMR10N                | 185                 |

| T1GCON              | TMR1GE              | T1GPOL              | T1GTM         | T1GSPM                | T1GGO/DONE             | T1GVAL   | T1GSS1 | T1GSS0                | 186                 |

| TMR1L               | Holding Reg         | gister for the      | Least Signifi | cant Byte of t        | he 16-bit TMR1 F       | Register |        |                       | 177*                |

| TMR1H               | Holding Reg         | gister for the      | Most Signific | ant Byte of th        | ne 16-bit TMR1 R       | legister |        |                       | 177*                |

| TRISA               | TRISA7              | TRISA6              | TRISA5        | TRISA4                | TRISA3                 | TRISA2   | TRISA1 | TRISA0                | 122                 |

| TRISB               | TRISB7              | TRISB6              | TRISB5        | TRISB4                | TRISB3                 | TRISB2   | TRISB1 | TRISB0                | 127                 |

#### TABLE 24-2: SUMMARY OF REGISTERS ASSOCIATED WITH CAPTURE

Legend: — = Unimplemented locations, read as '0'. Shaded cells are not used by Capture mode.

\* Page provides register information.

Note 1: Applies to ECCP modules only.

2: PIC16(L)F1827 only.

#### 24.3.7 OPERATION IN SLEEP MODE

In Sleep mode, the TMRx register will not increment and the state of the module will not change. If the CCPx pin is driving a value, it will continue to drive that value. When the device wakes up, TMRx will continue from its previous state.

#### 24.3.8 CHANGES IN SYSTEM CLOCK FREQUENCY

The PWM frequency is derived from the system clock frequency. Any changes in the system clock frequency will result in changes to the PWM frequency. See Section 5.0 "Oscillator Module (With Fail-Safe Clock Monitor)" for additional details.

#### 24.3.9 EFFECTS OF RESET

Any Reset will force all ports to Input mode and the CCP registers to their Reset states.

#### 24.3.10 ALTERNATE PIN LOCATIONS

This module incorporates I/O pins that can be moved to other locations with the use of the alternate pin function registers, APFCON0 and APFCON1. To determine which pins can be moved and what their default locations are upon a reset, see **Section 12.1 "Alternate Pin Function"** for more information.

| Name     | Bit 7                                                        | Bit 6               | Bit 5         | Bit 4                  | Bit 3                  | Bit 2   | Bit 1   | Bit 0   | Register<br>on Page |

|----------|--------------------------------------------------------------|---------------------|---------------|------------------------|------------------------|---------|---------|---------|---------------------|

| APFCON0  | RXDTSEL                                                      | SDO1SEL             | SS1SEL        | P2BSEL <sup>(2)</sup>  | CCP2SEL <sup>(2)</sup> | P1DSEL  | P1CSEL  | CCP1SEL | 119                 |

| CCPxCON  | PxM1 <sup>(1)</sup>                                          | PxM0 <sup>(1)</sup> | DCxB1         | DCxB0                  | CCPxM3                 | CCPxM2  | CCPxM1  | CCPxM0  | 226                 |

| CCPxAS   | CCPxASE                                                      | CCPxAS2             | CCPxAS1       | CCPxAS0                | PSSxAC1                | PSSxAC0 | PSSxBD1 | PSSxBD0 | 228                 |

| CCPTMRS  | C4TSEL1                                                      | C4TSEL0             | C3TSEL1       | C3TSEL0                | C2TSEL1                | C2TSEL0 | C1TSEL1 | C1TSEL0 | 227                 |

| INTCON   | GIE                                                          | PEIE                | TMR0IE        | INTE                   | IOCIE                  | TMR0IF  | INTF    | IOCIF   | 86                  |

| PR2      | Timer2 Peric                                                 | od Register         |               |                        |                        |         |         |         | 189*                |

| PR4      | Timer4 Modu                                                  | ule Period Re       | gister        |                        |                        |         |         |         | 189*                |

| PR6      | Timer6 Modu                                                  | ule Period Re       | gister        |                        |                        |         |         |         | 189*                |

| PSTRxCON | _                                                            | —                   | _             | STRxSYNC               | STRxD                  | STRxC   | STRxB   | STRxA   | 230                 |

| PWMxCON  | PxRSEN                                                       | PxDC6               | PxDC5         | PxDC4                  | PxDC3                  | PxDC2   | PxDC1   | PxDC0   | 229                 |

| T2CON    | —                                                            | T2OUTPS3            | T2OUTPS2      | T2OUTPS1               | T2OUTPS0               | TMR2ON  | T2CKPS1 | T2CKPS0 | 191                 |

| T4CON    | —                                                            | T4OUTPS3            | T4OUTPS2      | T4OUTPS1               | T4OUTPS0               | TMR4ON  | T4CKPS1 | T4CKPS0 | 191                 |

| T6CON    | —                                                            | T6OUTPS3            | T6OUTPS2      | T6OUTPS1               | T6OUTPS0               | TMR6ON  | T6CKPS1 | T6CKPS0 | 191                 |

| TMR2     | Holding Reg                                                  | ister for the 8-    | -bit TMR2 Tin | ne Base                |                        |         |         |         | 189*                |

| TMR4     | Holding Register for the 8-bit TMR4 Time Base <sup>(1)</sup> |                     |               |                        |                        |         |         |         |                     |

| TMR6     | Holding Reg                                                  | ister for the 8-    | -bit TMR6 Tin | ne Base <sup>(1)</sup> |                        |         |         |         | 189*                |

| TRISB    | TRISB7                                                       | TRISB6              | TRISB5        | TRISB4                 | TRISB3                 | TRISB2  | TRISB1  | TRISB0  | 127                 |

#### TABLE 24-8: SUMMARY OF REGISTERS ASSOCIATED WITH STANDARD PWM

**Legend:** — = Unimplemented locations, read as '0'. Shaded cells are not used by the PWM.

\* Page provides register information.

Note 1: Applies to ECCP modules only.

**2:** PIC16(L)F1827 only.

#### 25.5.4 SLAVE MODE 10-BIT ADDRESS RECEPTION

This section describes a standard sequence of events for the MSSPx module configured as an  $I^2C$  Slave in 10-bit Addressing mode.

Figure 25-19 is used as a visual reference for this description.

This is a step by step process of what must be done by slave software to accomplish I<sup>2</sup>C communication.

- 1. Bus starts Idle.

- Master sends Start condition; S bit of SSPxSTAT is set; SSPxIF is set if interrupt on Start detect is enabled.

- Master sends matching high address with R/W bit clear; UA bit of the SSPxSTAT register is set.

- 4. Slave sends ACK and SSPxIF is set.

- 5. Software clears the SSPxIF bit.

- 6. Software reads received address from SSPx-BUF clearing the BF flag.

- 7. Slave loads low address into SSPxADD, releasing SCLx.

- 8. Master sends matching low address byte to the Slave; UA bit is set.

**Note:** Updates to the SSPxADD register are not allowed until after the ACK sequence.

- 9. Slave sends ACK and SSPxIF is set.

- Note: If the low address does not match, SSPxIF and UA are still set so that the slave software can set SSPxADD back to the high address. BF is not set because there is no match. CKP is unaffected.

- 10. Slave clears SSPxIF.

- 11. Slave reads the received matching address from SSPxBUF clearing BF.

- 12. Slave loads high address into SSPxADD.

- 13. Master clocks a data <u>byte</u> to the slave and clocks out the slaves ACK on the 9th SCLx pulse; SSPxIF is set.

- 14. If SEN bit of SSPxCON2 is set, CKP is cleared by hardware and the clock is stretched.

- 15. Slave clears SSPxIF.

- 16. Slave reads the received byte from SSPxBUF clearing BF.

- 17. If SEN is set the slave sets CKP to release the SCLx.

- 18. Steps 13-17 repeat for each received byte.

- 19. Master sends Stop to end the transmission.

# 25.5.5 10-BIT ADDRESSING WITH ADDRESS OR DATA HOLD

Reception using 10-bit addressing with AHEN or DHEN set is the same as with 7-bit modes. The only difference is the need to update the SSPxADD register using the UA bit. All functionality, specifically when the CKP bit is cleared and SCLx line is held low are the same. Figure 25-20 can be used as a reference of a slave in 10-bit addressing with AHEN set.

Figure 25-21 shows a standard waveform for a slave transmitter in 10-bit Addressing mode.

| R/W-0/0          | R-0/0                                                                                                                                                                                                                                                                                                                                                                                                                                     | R/W-0/0              | R/S/HS-0/0 | R/S/HS-0/0                            | R/S/HS-0/0        | R/S/HS-0/0     | R/W/HS-0/0   |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|------------|---------------------------------------|-------------------|----------------|--------------|--|

| GCEN             | ACKSTAT                                                                                                                                                                                                                                                                                                                                                                                                                                   | ACKDT                | ACKEN      | RCEN                                  | PEN               | RSEN           | SEN          |  |

| bit 7            |                                                                                                                                                                                                                                                                                                                                                                                                                                           |                      |            |                                       |                   |                | bit C        |  |

|                  |                                                                                                                                                                                                                                                                                                                                                                                                                                           |                      |            |                                       |                   |                |              |  |

| Legend:          |                                                                                                                                                                                                                                                                                                                                                                                                                                           |                      |            |                                       |                   |                |              |  |

| R = Readable     |                                                                                                                                                                                                                                                                                                                                                                                                                                           | W = Writable bit     |            | •                                     | mented bit, read  |                |              |  |

| u = Bit is unch  | nanged                                                                                                                                                                                                                                                                                                                                                                                                                                    | x = Bit is unknown   |            |                                       | at POR and BO     |                | other Resets |  |

| '1' = Bit is set |                                                                                                                                                                                                                                                                                                                                                                                                                                           | '0' = Bit is cleared |            | HC = Cleared by hardware S = User set |                   |                |              |  |

| bit 7            | 1 = Enable in                                                                                                                                                                                                                                                                                                                                                                                                                             |                      | •          | .,                                    | or 00h) is receiv | ed in the SSPx | SR           |  |

| bit 6            | ACKSTAT: Acknowledge Status bit (in I <sup>2</sup> C mode only)<br>1 = Acknowledge was not received<br>0 = Acknowledge was received                                                                                                                                                                                                                                                                                                       |                      |            |                                       |                   |                |              |  |

| bit 5            | ACKDT: Acknowledge Data bit (in I <sup>2</sup> C mode only)<br><u>In Receive mode:</u><br>Value transmitted when the user initiates an Acknowledge sequence at the end of a receive<br>1 = Not Acknowledge<br>0 = Acknowledge                                                                                                                                                                                                             |                      |            |                                       |                   |                |              |  |

| bit 4            | <ul> <li>ACKEN: Acknowledge Sequence Enable bit (in I<sup>2</sup>C Master mode only)</li> <li><u>In Master Receive mode:</u></li> <li>1 = Initiate Acknowledge sequence on SDAx and SCLx pins, and transmit ACKDT data b Automatically cleared by hardware.</li> <li>0 = Acknowledge sequence Idle</li> </ul>                                                                                                                             |                      |            |                                       |                   | KDT data bit   |              |  |

| bit 3            | <b>RCEN:</b> Receive Enable bit (in I <sup>2</sup> C Master mode only)<br>1 = Enables Receive mode for I <sup>2</sup> C<br>0 = Receive Idle                                                                                                                                                                                                                                                                                               |                      |            |                                       |                   |                |              |  |

| bit 2            | <ul> <li>PEN: Stop Condition Enable bit (in I<sup>2</sup>C Master mode only)</li> <li><u>SCKx Release Control:</u></li> <li>1 = Initiate Stop condition on SDAx and SCLx pins. Automatically cleared by hardware.</li> <li>0 = Stop condition Idle</li> </ul>                                                                                                                                                                             |                      |            |                                       |                   |                |              |  |

| bit 1            | <ul> <li>RSEN: Repeated Start Condition Enabled bit (in I<sup>2</sup>C Master mode only)</li> <li>1 = Initiate Repeated Start condition on SDAx and SCLx pins. Automatically cleared by hardware</li> <li>0 = Repeated Start condition Idle</li> </ul>                                                                                                                                                                                    |                      |            |                                       |                   | y hardware.    |              |  |

| bit 0            | <ul> <li>SEN: Start Condition Enabled bit (in I<sup>2</sup>C Master mode only)</li> <li><u>In Master mode:</u></li> <li>1 = Initiate Start condition on SDAx and SCLx pins. Automatically cleared by hardware.</li> <li>0 = Start condition Idle</li> <li><u>In Slave mode:</u></li> <li>1 = Clock stretching is enabled for both slave transmit and slave receive (stretch enabled)</li> <li>0 = Clock stretching is disabled</li> </ul> |                      |            |                                       |                   |                |              |  |

# REGISTER 25-3: SSPxCON2: SSPx CONTROL REGISTER 2

**Note 1:** For bits ACKEN, RCEN, PEN, RSEN, SEN: If the I<sup>2</sup>C module is not in the Idle mode, this bit may not be set (no spooling) and the SSPxBUF may not be written (or writes to the SSPxBUF are disabled).

#### 26.4.2 SYNCHRONOUS SLAVE MODE

The following bits are used to configure the EUSART for Synchronous slave operation:

- SYNC = 1

- CSRC = 0

- SREN = 0 (for transmit); SREN = 1 (for receive)

- CREN = 0 (for transmit); CREN = 1 (for receive)

- SPEN = 1

Setting the SYNC bit of the TXSTA register configures the device for synchronous operation. Clearing the CSRC bit of the TXSTA register configures the device as a slave. Clearing the SREN and CREN bits of the RCSTA register ensures that the device is in the Transmit mode, otherwise the device will be configured to receive. Setting the SPEN bit of the RCSTA register enables the EUSART.

#### 26.4.2.1 EUSART Synchronous Slave Transmit

The operation of the Synchronous Master and Slave modes are identical (see **Section 26.4.1.3 "Synchronous Master Transmission")**, except in the case of the Sleep mode. If two words are written to the TXREG and then the SLEEP instruction is executed, the following will occur:

- 1. The first character will immediately transfer to the TSR register and transmit.

- 2. The second word will remain in TXREG register.

- 3. The TXIF bit will not be set.

- After the first character has been shifted out of TSR, the TXREG register will transfer the second character to the TSR and the TXIF bit will now be set.

- 5. If the PEIE and TXIE bits are set, the interrupt will wake the device from Sleep and execute the next instruction. If the GIE bit is also set, the program will call the Interrupt Service Routine.

- 26.4.2.2 Synchronous Slave Transmission Set-up:

- 1. Set the SYNC and SPEN bits and clear the CSRC bit.

- 2. Clear the ANSEL bit for the CK pin (if applicable).

- 3. Clear the CREN and SREN bits.

- If interrupts are desired, set the TXIE bit of the PIE1 register and the GIE and PEIE bits of the INTCON register.

- 5. If 9-bit transmission is desired, set the TX9 bit.

- 6. Enable transmission by setting the TXEN bit.

- 7. If 9-bit transmission is selected, insert the Most Significant bit into the TX9D bit.

- 8. Start transmission by writing the Least Significant 8 bits to the TXREG register.

# TABLE 26-9:SUMMARY OF REGISTERS ASSOCIATED WITH SYNCHRONOUS SLAVE<br/>TRANSMISSION

| Name    | Bit 7                         | Bit 6   | Bit 5  | Bit 4                 | Bit 3                  | Bit 2  | Bit 1  | Bit 0   | Register<br>on Page |

|---------|-------------------------------|---------|--------|-----------------------|------------------------|--------|--------|---------|---------------------|

| APFCON0 | RXDTSEL                       | SDO1SEL | SS1SEL | P2BSEL <sup>(1)</sup> | CCP2SEL <sup>(1)</sup> | P1DSEL | P1CSEL | CCP1SEL | 119                 |

| APFCON1 | _                             | _       | _      | _                     | _                      | _      | _      | TXCKSEL | 119                 |

| BAUDCON | ABDOVF                        | RCIDL   | —      | SCKP                  | BRG16                  | _      | WUE    | ABDEN   | 296                 |

| INTCON  | GIE                           | PEIE    | TMR0IE | INTE                  | IOCIE                  | TMR0IF | INTF   | IOCIF   | 86                  |

| PIE1    | TMR1GIE                       | ADIE    | RCIE   | TXIE                  | SSPIE                  | CCP1IE | TMR2IE | TMR1IE  | 87                  |

| PIR1    | TMR1GIF                       | ADIF    | RCIF   | TXIF                  | SSPIF                  | CCP1IF | TMR2IF | TMR1IF  | 91                  |

| RCSTA   | SPEN                          | RX9     | SREN   | CREN                  | ADDEN                  | FERR   | OERR   | RX9D    | 295                 |

| TRISB   | TRISB7                        | TRISB6  | TRISB5 | TRISB4                | TRISB3                 | TRISB2 | TRISB1 | TRISB0  | 127                 |

| TXREG   | EUSART Transmit Data Register |         |        |                       |                        | 287*   |        |         |                     |

| TXSTA   | CSRC                          | TX9     | TXEN   | SYNC                  | SENDB                  | BRGH   | TRMT   | TX9D    | 294                 |

|         |                               |         |        |                       |                        |        |        |         |                     |

Legend: — = unimplemented location, read as '0'. Shaded cells are not used for Synchronous Slave Transmission. \* Page provides register information.

Note 1: PIC16(L)F1827 only.

| SWAPF            | Swap Nibbles in f                                                                                                                                                                 |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] SWAPF f,d                                                                                                                                                               |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                                 |

| Operation:       | $(f<3:0>) \rightarrow (destination<7:4>),$<br>$(f<7:4>) \rightarrow (destination<3:0>)$                                                                                           |

| Status Affected: | None                                                                                                                                                                              |

| Description:     | The upper and lower nibbles of regis-<br>ter 'f' are exchanged. If 'd' is '0', the<br>result is placed in the W register. If 'd'<br>is '1', the result is placed in register 'f'. |

| XORLW            | Exclusive OR literal with W                                                                                                |

|------------------|----------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] XORLW k                                                                                                            |

| Operands:        | $0 \leq k \leq 255$                                                                                                        |

| Operation:       | (W) .XOR. $k \rightarrow (W)$                                                                                              |

| Status Affected: | Z                                                                                                                          |

| Description:     | The contents of the W register are<br>XOR'ed with the eight-bit<br>literal 'k'. The result is placed in the<br>W register. |

| TRIS                    | Load TRIS Register with W                                                                                       | XORWF            | Exclusive OR W with f                                                                                                                                                           |  |

|-------------------------|-----------------------------------------------------------------------------------------------------------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Syntax:                 | [ label ] TRIS f                                                                                                | Syntax:          | [ <i>label</i> ] XORWF f,d                                                                                                                                                      |  |

| Operands:<br>Operation: | $5 \le f \le 7$<br>(W) $\rightarrow$ TRIS register 'f'                                                          | Operands:        | $0 \le f \le 127$<br>d $\in [0,1]$                                                                                                                                              |  |

| Status Affected:        | None $(W) \rightarrow TRIS register T$                                                                          | Operation:       | (W) .XOR. (f) $\rightarrow$ (destination)                                                                                                                                       |  |

| Description:            | Move data from W register to TRIS                                                                               | Status Affected: | Z                                                                                                                                                                               |  |

|                         | register.<br>When 'f' = 5, TRISA is loaded.<br>When 'f' = 6, TRISB is loaded.<br>When 'f' = 7, TRISC is loaded. | Description:     | Exclusive OR the contents of the W register with register 'f'. If 'd' is '0', the result is stored in the W register. If 'd' is '1', the result is stored back in register 'f'. |  |

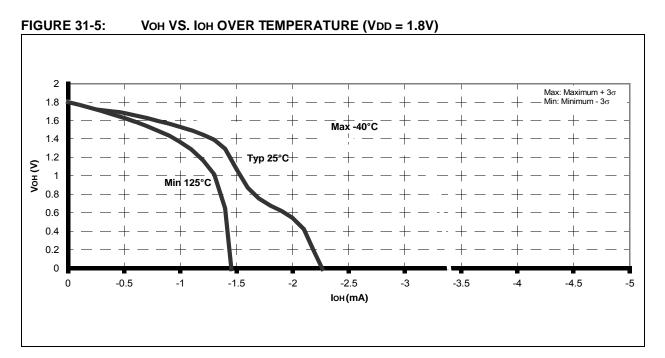

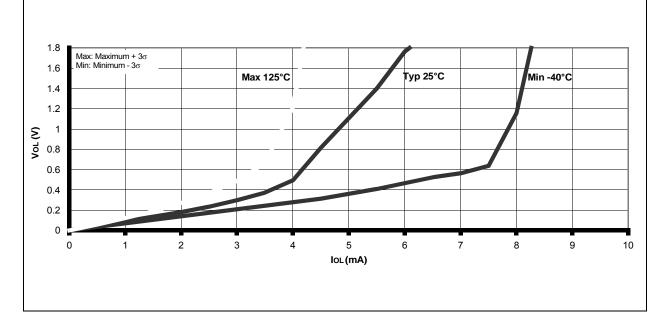

FIGURE 31-6: Vol VS. IoL OVER TEMPERATURE (VDD = 1.8V)

# 33.0 PACKAGING INFORMATION

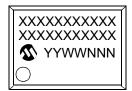

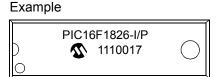

# 33.1 Package Marking Information

#### 18-Lead PDIP

#### 18-Lead SOIC (.300")

#### 20-Lead SSOP

#### 28-Lead QFN/UQFN

# Example

## Example

#### Example

| Legend | : XXX<br>Y<br>YY<br>WW<br>NNN<br>@3<br>* | Customer-specific information<br>Year code (last digit of calendar year)<br>Year code (last 2 digits of calendar year)<br>Week code (week of January 1 is week '01')<br>Alphanumeric traceability code<br>Pb-free JEDEC designator for Matte Tin (Sn)<br>This package is Pb-free. The Pb-free JEDEC designator ((e3))<br>can be found on the outer packaging for this package. |

|--------|------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Note:  | be carried                               | nt the full Microchip part number cannot be marked on one line, it will<br>d over to the next line, thus limiting the number of available<br>s for customer-specific information.                                                                                                                                                                                              |

\* Standard PICmicro<sup>®</sup> device marking consists of Microchip part number, year code, week code and traceability code. For PICmicro device marking beyond this, certain price adders apply. Please check with your Microchip Sales Office. For QTP devices, any special marking adders are included in QTP price.