# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                              |

|----------------------------|------------------------------------------------------------------------------|

| Product Status             | Active                                                                       |

| Core Processor             | M8C                                                                          |

| Core Size                  | 8-Bit                                                                        |

| Speed                      | 24MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                            |

| Peripherals                | POR, PWM, WDT                                                                |

| Number of I/O              | 16                                                                           |

| Program Memory Size        | 4KB (4K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | -                                                                            |

| RAM Size                   | 256 x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 2.4V ~ 5.25V                                                                 |

| Data Converters            | A/D 8x14b; D/A 2x9b                                                          |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                                               |

| Supplier Device Package    | 20-SSOP                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/cy8c24223a-24pvxi |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Contents

| PSoC Functional Overview          | 3  |

|-----------------------------------|----|

| PSoC Core                         | 3  |

| Digital System                    | 3  |

| Analog System                     | 4  |

| Additional System Resources       | 5  |

| PSoC Device Characteristics       | 5  |

| Getting Started                   | 6  |

| Application Notes                 |    |

| Development Kits                  | 6  |

| Training                          | 6  |

| CYPros Consultants                | 6  |

| Solutions Library                 | 6  |

| Technical Support                 | 6  |

| Development Tools                 |    |

| PSoC Designer Software Subsystems | 7  |

| Designing with PSoC Designer      | 8  |

| Select User Modules               | 8  |

| Configure User Modules            | 8  |

| Organize and Connect              | 8  |

| Generate, Verify, and Debug       | 8  |

| Pinouts                           |    |

| 8-Pin Part Pinout                 | 9  |

| 20-Pin Part Pinout                | 10 |

| 28-Pin Part Pinout                | 11 |

| 32-Pin Part Pinout                | 12 |

| 56-Pin Part Pinout                | 13 |

| Register Reference                |    |

| Register Conventions              | 14 |

| Register Mapping Tables           |    |

| Electrical Specifications         |    |

| Absolute Maximum Ratings          | 17 |

| Operating Temperature             | 18 |

| DC Electrical Characteristics     | 18 |

|                                   |    |

| AC Electrical Characteristics           |    |

|-----------------------------------------|----|

| Packaging Information                   | 50 |

| Packaging Dimensions                    | 50 |

| Thermal Impedances                      |    |

| Capacitance on Crystal Pins             | 56 |

| Solder Reflow Specifications            |    |

| Development Tool Selection              | 57 |

| Software                                |    |

| Development Kits                        | 57 |

| Evaluation Tools                        | 57 |

| Device Programmers                      | 58 |

| Accessories (Emulation and Programming) | 58 |

| Ordering Information                    | 59 |

| Ordering Code Definitions               | 59 |

| Acronyms                                | 60 |

| Acronyms Used                           |    |

| Reference Documents                     |    |

| Document Conventions                    | 61 |

| Units of Measure                        | 61 |

| Numeric Conventions                     | 61 |

| Glossary                                | 61 |

| Errata                                  |    |

| Part Numbers Affected                   |    |

| CY8C24123A Qualification Status         |    |

| CY8C24123A Errata Summary               |    |

| Document History Page                   |    |

| Sales, Solutions, and Legal Information |    |

| Worldwide Sales and Design Support      | 70 |

| Products                                |    |

| PSoC® Solutions                         |    |

| Cypress Developer Community             |    |

| Technical Support                       | 70 |

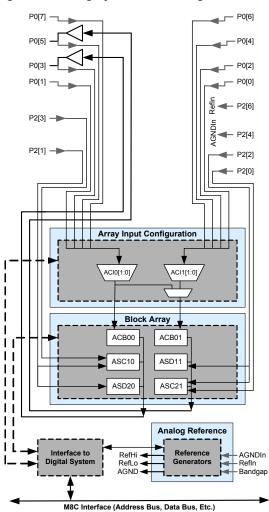

#### Analog System

The analog system consists of six configurable blocks, each consisting of an opamp circuit that allows the creation of complex analog signal flows. Analog peripherals are very flexible and can be customized to support specific application requirements. Some of the more common PSoC analog functions (most available as user modules) are:

- ADCs (up to two, with 6- to 14-bit resolution, selectable as incremental, delta sigma, and SAR)

- Filters (two and four pole band-pass, low-pass, and notch)

- Amplifiers (up to two, with selectable gain to 48x)

- Instrumentation amplifiers (one with selectable gain to 93x)

- Comparators (up to two, with 16 selectable thresholds)

- DACs (up to two, with 6 to 9-bit resolution)

- Multiplying DACs (up to two, with 6 to 9-bit resolution)

- High current output drivers (two with 30 mA drive as a PSoC Core resource)

- 1.3 V reference (as a system resource)

- DTMF dialer

- Modulators

- Correlators

- Peak detectors

- Many other topologies possible

Analog blocks are arranged in a column of three, which includes one continuous time (CT) and two switched capacitor (SC) blocks, as shown in Figure 3

#### Figure 3. Analog System Block Diagram

#### Additional System Resources

System resources, some of which are listed in the previous sections, provide additional capability useful to complete systems. Additional resources include a multiplier, decimator, switch-mode pump, low-voltage detection, and power-on-reset (POR). Statements describing the merits of each system resource follow:

- Digital clock dividers provide three customizable clock frequencies for use in applications. The clocks can be routed to both the digital and analog systems. Additional clocks may be generated using digital PSoC blocks as clock dividers.

- A multiply accumulate (MAC) provides a fast 8-bit multiplier with 32-bit accumulate, to assist in both general math and digital filters.

- The decimator provides a custom hardware filter for digital signal processing applications including the creation of Delta Sigma ADCs.

- The I<sup>2</sup>C module provides 100- and 400-kHz communication over two wires. slave, master, and multi-master are supported.

- Low-voltage detection (LVD) interrupts can signal the application of falling voltage levels, while the advanced POR circuit eliminates the need for a system supervisor.

- An internal 1.3 V reference provides an absolute reference for the analog system, including ADCs and DACs.

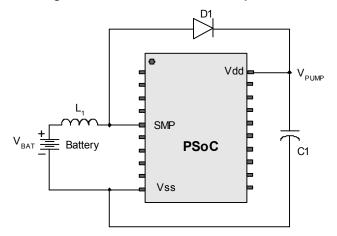

- An integrated switch-mode pump generates normal operating voltages from a single 1.2 V battery cell, providing a low cost boost converter.

#### **PSoC Device Characteristics**

Depending on your PSoC device characteristics, the digital and analog systems can have 16, 8, or 4 digital blocks, and 12, 6, or 4 analog blocks. Table 1 on page 6 lists the resources available for specific PSoC device groups. The PSoC device covered by this datasheet is highlighted in this table.

| PSoC Part<br>Number | Digital<br>I/O | Digital<br>Rows | Digital<br>Blocks | Analog<br>Inputs | Analog<br>Outputs | Analog<br>Columns | Analog<br>Blocks               | SRAM<br>Size | Flash<br>Size |

|---------------------|----------------|-----------------|-------------------|------------------|-------------------|-------------------|--------------------------------|--------------|---------------|

| CY8C29x66           | up to 64       | 4               | 16                | up to 12         | 4                 | 4                 | 12                             | 2 K          | 32 K          |

| CY8C28xxx           | up to 44       | up to 3         | up to 12          | up to 44         | up to 4           | up to 6           | up to<br>12 + 4 <sup>[2]</sup> | 1 K          | 16 K          |

| CY8C27x43           | up to 44       | 2               | 8                 | up to 12         | 4                 | 4                 | 12                             | 256          | 16 K          |

| CY8C24x94           | up to 56       | 1               | 4                 | up to 48         | 2                 | 2                 | 6                              | 1 K          | 16 K          |

| CY8C24x23A          | up to 24       | 1               | 4                 | up to 12         | 2                 | 2                 | 6                              | 256          | 4 K           |

| CY8C23x33           | up to 26       | 1               | 4                 | up to 12         | 2                 | 2                 | 4                              | 256          | 8 K           |

| CY8C22x45           | up to 38       | 2               | 8                 | up to 38         | 0                 | 4                 | 6 <sup>[2]</sup>               | 1 K          | 16 K          |

| CY8C21x45           | up to 24       | 1               | 4                 | up to 24         | 0                 | 4                 | 6 <sup>[2]</sup>               | 512          | 8 K           |

| CY8C21x34           | up to 28       | 1               | 4                 | up to 28         | 0                 | 2                 | 4 <sup>[2]</sup>               | 512          | 8 K           |

| CY8C21x23           | up to 16       | 1               | 4                 | up to 8          | 0                 | 2                 | 4 <sup>[2]</sup>               | 256          | 4 K           |

| CY8C20x34           | up to 28       | 0               | 0                 | up to 28         | 0                 | 0                 | 3 <sup>[2,3]</sup>             | 512          | 8 K           |

| CY8C20xx6           | up to 36       | 0               | 0                 | up to 36         | 0                 | 0                 | 3 <sup>[2,3]</sup>             | up to<br>2 K | up to<br>32 K |

#### Table 1. PSoC Device Characteristics

2. Limited analog functionality.

3. Two analog blocks and one CapSense<sup>®</sup>.

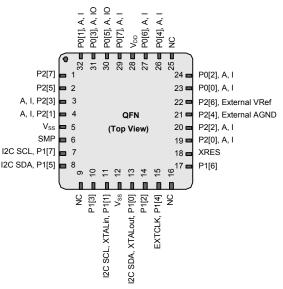

#### 32-Pin Part Pinout

#### Table 5. 32-Pin QFN<sup>[7]</sup>

| Pin No.  | Ту                        | vpe           | Pin             | Description                                              | 1 |

|----------|---------------------------|---------------|-----------------|----------------------------------------------------------|---|

| PIII NO. | Digital                   | Analog        | Name            | Description                                              | l |

| 1        | I/O                       |               | P2[7]           |                                                          |   |

| 2        | I/O                       |               | P2[5]           |                                                          | 1 |

| 3        | I/O                       | I             | P2[3]           | Direct switched capacitor block input                    | 1 |

| 4        | I/O                       | 1             | P2[1]           | Direct switched capacitor block input                    | 1 |

| 5        | Po                        | wer           | V <sub>SS</sub> | Ground connection                                        |   |

| 6        | Po                        | wer           | SMP             | SMP connection to external components required           |   |

| 7        | I/O                       |               | P1[7]           | I <sup>2</sup> C SCL                                     | 1 |

| 8        | I/O                       |               | P1[5]           | I <sup>2</sup> C SDA                                     |   |

| 9        |                           |               | NC              | No connection. Pin must be left floating                 |   |

| 10       | I/O                       |               | P1[3]           |                                                          |   |

| 11       | I/O                       |               | P1[1]           | XTALin, I <sup>2</sup> C SCL, ISSP-SCLK <sup>[8]</sup>   |   |

| 12       | Po                        | wer           | V <sub>SS</sub> | Ground Connection                                        |   |

| 13       | I/O                       |               | P1[0]           | XTALout, I <sup>2</sup> C SDA, ISSP-SDATA <sup>[8]</sup> |   |

| 14       | I/O                       |               | P1[2]           |                                                          |   |

| 15       | I/O                       |               | P1[4]           | Optional EXTCLK                                          |   |

| 16       |                           | •             | NC              | No connection. Pin must be left floating                 |   |

| 17       | I/O                       |               | P1[6]           |                                                          |   |

| 18       | In                        | put           | XRES            | Active high external reset with internal pull-down       |   |

| 19       | I/O                       | I             | P2[0]           | Direct switched capacitor block input                    |   |

| 20       | I/O                       | I             | P2[2]           | Direct switched capacitor block input                    |   |

| 21       | I/O                       |               | P2[4]           | External AGND                                            |   |

| 22       | I/O                       |               | P2[6]           | External V <sub>REF</sub>                                |   |

| 23       | I/O                       | I             | P0[0]           | Analog column mux input                                  |   |

| 24       | I/O                       | I             | P0[2]           | Analog column mux input                                  |   |

| 25       |                           | •             | NC              | No connection. Pin must be left floating                 |   |

| 26       | I/O                       | I             | P0[4]           | Analog column mux input                                  |   |

| 27       | I/O                       | I             | P0[6]           | Analog column mux input                                  |   |

| 28       | Po                        | wer           | V <sub>DD</sub> | Supply voltage                                           | 1 |

| 29       | I/O                       | I             | P0[7]           | Analog column mux input                                  |   |

| 30       | I/O                       | I/O           | P0[5]           | Analog column mux input and column output                | 1 |

| 31       | I/O                       | I/O           | P0[3]           | Analog column mux input and column output                |   |

| 32       | I/O                       | I             | P0[1]           | Analog column mux input                                  | 1 |

| LEOEND.  | $\Lambda = \Lambda$ polog | I = Input and |                 |                                                          | ~ |

#### Figure 7. CY8C24423A 32-Pin PSoC Device

LEGEND: A = Analog, I = Input, and O = Output.

#### Notes

- The center pad on the QFN package must be connected to ground (V<sub>SS</sub>) for best mechanical, thermal, and electrical performance. If not connected to ground, it must be electrically floated and not connected to any other signal.

These are the ISSP pins, which are not high Z at POR. See the PSoC Technical Reference Manual for details.

#### **Operating Temperature**

#### Table 10. Operating Temperature

| Symbol         | Description          | Min | Тур | Max  | Units | Notes                                                                                                                                                            |

|----------------|----------------------|-----|-----|------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| T <sub>A</sub> | Ambient temperature  | -40 | -   | +85  | °C    |                                                                                                                                                                  |

| TJ             | Junction temperature | -40 | -   | +100 |       | The temperature rise from ambient to junction is package specific. See Table 48 on page 57. You must limit the power consumption to comply with this requirement |

#### **DC Electrical Characteristics**

#### DC Chip-Level Specifications

Table 11 lists the guaranteed maximum and minimum specifications for the voltage and temperature ranges: 4.75 V to 5.25 V and -40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C, 3.0 V to 3.6 V and -40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C, or 2.4 V to 3.0 V and -40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C, respectively. Typical parameters are measured at 5 V, 3.3 V, and 2.7 V at 25 °C and are for design guidance only.

#### Table 11. DC Chip-Level Specifications

| Symbol              | Description                                                                                                     | Min  | Тур  | Max  | Units | Notes                                                                                                                                                                                                     |

|---------------------|-----------------------------------------------------------------------------------------------------------------|------|------|------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>DD</sub>     | Supply voltage                                                                                                  | 2.4  | -    | 5.25 | V     | See DC POR and LVD specifications,<br>Table 26 on page 35                                                                                                                                                 |

| I <sub>DD</sub>     | Supply current                                                                                                  | -    | 5    | 8    | mA    | Conditions are $V_{DD}$ = 5.0 V, $T_A$ = 25 °C,<br>CPU = 3 MHz, SYSCLK doubler<br>disabled, VC1 = 1.5 MHz,<br>VC2 = 93.75 kHz, VC3 = 93.75 kHz,<br>analog power = off<br>SLIMO mode = 0. IMO = 24 MHz     |

| I <sub>DD3</sub>    | Supply current                                                                                                  | _    | 3.3  | 6.0  | mA    | Conditions are $V_{DD}$ = 3.3 V, $T_A$ = 25 °C,<br>CPU = 3 MHz, SYSCLK doubler<br>disabled, VC1 = 1.5 MHz,<br>VC2 = 93.75 kHz, VC3 = 93.75 kHz,<br>analog power = off. SLIMO mode = 0.<br>IMO = 24 MHz    |

| I <sub>DD27</sub>   | Supply current                                                                                                  | -    | 2    | 4    | mA    | Conditions are $V_{DD}$ = 2.7 V, $T_A$ = 25 °C,<br>CPU = 0.75 MHz, SYSCLK doubler<br>disabled, VC1 = 0.375 MHz,<br>VC2 = 23.44 kHz, VC3 = 0.09 kHz,<br>analog power = off. SLIMO mode = 1.<br>IMO = 6 MHz |

| I <sub>SB</sub>     | Sleep (mode) current with POR, LVD, sleep timer, and WDT. $^{[10]}$                                             | -    | 3    | 6.5  | μA    | Conditions are with internal slow speed oscillator, $V_{DD}$ = 3.3 V, –40 $^\circ C \leq T_A \leq$ 55 $^\circ C$ , analog power = off                                                                     |

| I <sub>SBH</sub>    | Sleep (mode) current with POR, LVD, sleep timer, and WDT at high temperature. <sup>[10]</sup>                   | _    | 4    | 25   | μA    | Conditions are with internal slow speed oscillator, V_DD = 3.3 V, 55 °C < T_A $\leq$ 85 °C, analog power = off                                                                                            |

| I <sub>SBXTL</sub>  | Sleep (mode) current with POR, LVD, sleep timer, WDT, and external crystal. <sup>[10]</sup>                     | _    | 4    | 7.5  | μA    | Conditions are with properly loaded,<br>1 $\mu$ W max, 32.768 kHz crystal.<br>V <sub>DD</sub> = 3.3 V, -40 °C $\leq$ T <sub>A</sub> $\leq$ 55 °C, analog<br>power = off                                   |

| I <sub>SBXTLH</sub> | Sleep (Mode) current with POR, LVD, sleep timer, WDT, and external crystal at high temperature. <sup>[10]</sup> | _    | 5    | 26   | μA    | Conditions are with properly loaded, 1 $\mu$ W max, 32.768 kHz crystal. V <sub>DD</sub> = 3.3 V, 55 °C < T <sub>A</sub> $\leq$ 85 °C, analog power = off                                                  |

| V <sub>REF</sub>    | Reference voltage (Bandgap)                                                                                     | 1.28 | 1.30 | 1.32 | V     | Trimmed for appropriate $V_{DD}$ .<br>$V_{DD} > 3.0 V$                                                                                                                                                    |

| V <sub>REF27</sub>  | Reference voltage (Bandgap)                                                                                     | 1.16 | 1.30 | 1.32 | V     | Trimmed for appropriate $V_{DD}$ .<br>$V_{DD}$ = 2.4 V to 3.0 V                                                                                                                                           |

#### Note

10. Standby current includes all functions (POR, LVD, WDT, sleep time) needed for reliable system operation. This must be compared with devices that have similar functions enabled.

#### DC GPIO Specifications

The following tables list the guaranteed maximum and minimum specifications for the voltage and temperature ranges: 4.75 V to 5.25 V and –40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C, 3.0 V to 3.6 V and –40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C, or 2.4 V to 3.0 V and –40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C, respectively. Typical parameters are measured at 5 V, 3.3 V, and 2.7 V at 25 °C and are for design guidance only.

#### Table 12. 5-V and 3.3-V DC GPIO Specifications

| Symbol           | Description                       | Min                   | Тур | Max  | Units | Notes                                                                                                                                                                                                                            |

|------------------|-----------------------------------|-----------------------|-----|------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| R <sub>PU</sub>  | Pull-up resistor                  | 4                     | 5.6 | 8    | kΩ    |                                                                                                                                                                                                                                  |

| R <sub>PD</sub>  | Pull-down resistor                | 4                     | 5.6 | 8    | kΩ    |                                                                                                                                                                                                                                  |

| V <sub>OH</sub>  | High output level                 | V <sub>DD</sub> – 1.0 | Ι   | _    | V     | $I_{OH}$ = 10 mA, $V_{DD}$ = 4.75 to 5.25 V<br>(maximum 40 mA on even port pins<br>(for example, P0[2], P1[4]), maximum<br>40 mA on odd port pins (for example,<br>P0[3], P1[5])). 80 mA maximum<br>combined $I_{OH}$ budget.    |

| V <sub>OL</sub>  | Low output level                  | _                     | -   | 0.75 | V     | $I_{OL}$ = 25 mA, $V_{DD}$ = 4.75 to 5.25 V<br>(maximum 100 mA on even port pins<br>(for example, P0[2], P1[4]), maximum<br>100 mA on odd port pins (for<br>example, P0[3], P1[5])). 150 mA<br>maximum combined $I_{OL}$ budget. |

| I <sub>ОН</sub>  | High level source current         | 10                    | -   | -    | mA    | $V_{OH} = V_{DD} - 1.0 V$ , see the limitations of the total current in the note for $V_{OH}$                                                                                                                                    |

| I <sub>OL</sub>  | Low level sink current            | 25                    | -   | -    | mA    | $V_{OL}$ = 0.75 V, see the limitations of the total current in the note for $V_{OL}$                                                                                                                                             |

| V <sub>IL</sub>  | Input low level                   | -                     | -   | 0.8  | V     | V <sub>DD</sub> = 3.0 to 5.25                                                                                                                                                                                                    |

| V <sub>IH</sub>  | Input high level                  | 2.1                   | -   |      | V     | V <sub>DD</sub> = 3.0 to 5.25                                                                                                                                                                                                    |

| V <sub>H</sub>   | Input hysterisis                  | -                     | 60  | -    | mV    |                                                                                                                                                                                                                                  |

| Ι <sub>ΙL</sub>  | Input leakage (absolute value)    | -                     | 1   | -    | nA    | Gross tested to 1 µA                                                                                                                                                                                                             |

| C <sub>IN</sub>  | Capacitive load on pins as input  | -                     | 3.5 | 10   | pF    | Package and pin dependent.<br>Temp = 25 °C                                                                                                                                                                                       |

| C <sub>OUT</sub> | Capacitive load on pins as output | -                     | 3.5 | 10   | pF    | Package and pin dependent.<br>Temp = 25 °C                                                                                                                                                                                       |

#### Table 13. 2.7-V DC GPIO Specifications

| Symbol           | Description                       | Min                   | Тур | Мах  | Units | Notes                                                                                                          |

|------------------|-----------------------------------|-----------------------|-----|------|-------|----------------------------------------------------------------------------------------------------------------|

| R <sub>PU</sub>  | Pull-up resistor                  | 4                     | 5.6 | 8    | kΩ    |                                                                                                                |

| R <sub>PD</sub>  | Pull-down resistor                | 4                     | 5.6 | 8    | kΩ    |                                                                                                                |

| V <sub>OH</sub>  | High output level                 | V <sub>DD</sub> – 0.4 | -   | _    | V     | $I_{OH}$ = 2 mA (6.25 Typ), $V_{DD}$ = 2.4 to<br>3.0 V (16 mA maximum, 50 mA Typ<br>combined $I_{OH}$ budget). |

| V <sub>OL</sub>  | Low output level                  | -                     | -   | 0.75 | V     | $I_{OL}$ = 11.25 mA, $V_{DD}$ = 2.4 to 3.0 V (90 mA maximum combined $I_{OL}$ budget).                         |

| I <sub>OH</sub>  | High level source current         | 2                     | -   | -    | mA    | $V_{OH} = V_{DD} - 0.4$ , see the limitations of total current in note for $V_{OH}$ .                          |

| V <sub>IL</sub>  | Input low level                   | -                     | -   | 0.75 | V     | V <sub>DD</sub> = 2.4 to 3.0                                                                                   |

| V <sub>IH</sub>  | Input high level                  | 2.0                   | -   | -    | V     | V <sub>DD</sub> = 2.4 to 3.0                                                                                   |

| V <sub>H</sub>   | Input hysteresis                  | -                     | 90  | -    | mV    |                                                                                                                |

| I <sub>OL</sub>  | Low level sink current            | 11.25                 | _   | -    | mA    | $V_{OL}$ = .75, see the limitations of total current in note for $V_{OL}$ .                                    |

| IIL              | Input leakage (absolute value)    | -                     | 1   | -    | nA    | Gross tested to 1 µA                                                                                           |

| C <sub>IN</sub>  | Capacitive load on pins as input  | -                     | 3.5 | 10   | pF    | Package and pin dependent.<br>Temp = 25 °C                                                                     |

| C <sub>OUT</sub> | Capacitive load on pins as output | -                     | 3.5 | 10   | pF    | Package and pin dependent.<br>Temp = 25 °C                                                                     |

# Table 15. 3.3-V DC Operational Amplifier Specifications

| Symbol               | Description                                                                                                                                                                                                                                                           | Min                                                | Тур                                    | Max                                    | Units                      | Notes                                                                                                                                                                                                  |

|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|----------------------------------------|----------------------------------------|----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>OSOA</sub>    | Input offset voltage (absolute value)<br>Power = Iow, Opamp bias = high<br>Power = medium, Opamp bias = high<br>Power = high, Opamp bias = high                                                                                                                       |                                                    | 1.65<br>1.32<br>–                      | 10<br>8<br>-                           | mV<br>mV<br>mV             | Power = high, Opamp bias = high<br>setting is not allowed for 3.3 V V <sub>DD</sub><br>operation.                                                                                                      |

| TCV <sub>OSOA</sub>  | Average input offset voltage drift                                                                                                                                                                                                                                    | -                                                  | 7.0                                    | 35.0                                   | µV/°C                      |                                                                                                                                                                                                        |

| I <sub>EBOA</sub>    | Input leakage current (port 0 analog pins)                                                                                                                                                                                                                            | -                                                  | 20                                     | -                                      | pА                         | Gross tested to 1 µA                                                                                                                                                                                   |

| C <sub>INOA</sub>    | Input capacitance (port 0 analog pins)                                                                                                                                                                                                                                | -                                                  | 4.5                                    | 9.5                                    | pF                         | Package and pin dependent.<br>Temp = 25 °C                                                                                                                                                             |

| V <sub>CMOA</sub>    | Common mode voltage range                                                                                                                                                                                                                                             | 0.2                                                | _                                      | V <sub>DD</sub> – 0.2                  | V                          | The common-mode input voltage<br>range is measured through an<br>analog output buffer. The<br>specification includes the limitations<br>imposed by the characteristics of the<br>analog output buffer. |

| G <sub>OLOA</sub>    | Open loop gain<br>Power = low, ppamp Opamp bias = low<br>Power = medium, Opamp bias = low<br>Power = high, Opamp bias = low                                                                                                                                           | 60<br>60<br>80                                     | _<br>_<br>_                            | -<br>-<br>-                            | dB<br>dB<br>dB             | Specification is applicable at low<br>Opamp bias. For high Opamp bias<br>mode (except high power, high<br>Opamp bias), minimum is 60 dB.                                                               |

| V <sub>OHIGHOA</sub> | High output voltage swing (internal signals)<br>Power = low, Opamp bias = low<br>Power = medium, Opamp bias = low<br>Power = high, Opamp bias = low                                                                                                                   | $V_{DD} - 0.2$<br>$V_{DD} - 0.2$<br>$V_{DD} - 0.2$ | _<br>_<br>_                            | -<br>-<br>-                            | V<br>V<br>V                | Power = high, Opamp bias = high<br>setting is not allowed for 3.3 V V <sub>DD</sub><br>operation.                                                                                                      |

| V <sub>OLOWOA</sub>  | Low output voltage swing (internal signals)<br>Power = low, ppamp Opamp bias = low<br>Power = medium, Opamp bias = low<br>Power = high, Opamp bias = low                                                                                                              |                                                    | _<br>_<br>_                            | 0.2<br>0.2<br>0.2                      | V<br>V<br>V                | Power = high, Opamp bias = high<br>setting is not allowed for 3.3 V V <sub>DD</sub><br>operation.                                                                                                      |

| I <sub>SOA</sub>     | Supply current (including associated AGND<br>buffer)<br>Power = low, Opamp bias = low<br>Power = low, Opamp bias = high<br>Power = medium, Opamp bias = low<br>Power = medium, Opamp bias = high<br>Power = high, Opamp bias = low<br>Power = high, Opamp bias = high | -<br>-<br>-<br>-<br>-                              | 150<br>300<br>600<br>1200<br>2400<br>- | 200<br>400<br>800<br>1600<br>3200<br>- | μΑ<br>μΑ<br>μΑ<br>μΑ<br>μΑ | Power = high, Opamp bias = high<br>setting is not allowed for 3.3 V V <sub>DD</sub><br>operation.                                                                                                      |

| PSRR <sub>OA</sub>   | Supply voltage rejection ratio                                                                                                                                                                                                                                        | 64                                                 | 80                                     | _                                      | dB                         | $V_{SS} \leq V_{IN} \leq (V_{DD}-2.25) \text{ or } \\ (V_{DD}-1.25 \text{ V}) \leq V_{IN} \leq V_{DD}$                                                                                                 |

#### Table 16. 2.7-V DC Operational Amplifier Specifications

| Symbol               | Description                                                                                                                                                                                                                                                           | Min                                                                     | Тур                                    | Max                                    | Units                | Notes                                                                                                                                                                                                  |

|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|----------------------------------------|----------------------------------------|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>OSOA</sub>    | Input offset voltage (absolute value)<br>Power = low, Opamp bias = high<br>Power = medium, Opamp bias = high<br>Power = high, Opamp bias = high                                                                                                                       | -<br>-<br>-                                                             | 1.65<br>1.32<br>–                      | 10<br>8<br>-                           | mV<br>mV<br>mV       | Power = high, Opamp bias = high<br>setting is not allowed for 2.7 V V <sub>DD</sub><br>operation.                                                                                                      |

| TCV <sub>OSOA</sub>  | Average input offset voltage drift                                                                                                                                                                                                                                    | -                                                                       | 7.0                                    | 35.0                                   | μV/°C                |                                                                                                                                                                                                        |

| I <sub>EBOA</sub>    | Input leakage current (port 0 analog pins)                                                                                                                                                                                                                            | -                                                                       | 20                                     | -                                      | pА                   | Gross tested to 1 µA                                                                                                                                                                                   |

| C <sub>INOA</sub>    | Input capacitance (port 0 analog pins)                                                                                                                                                                                                                                | -                                                                       | 4.5                                    | 9.5                                    | pF                   | Package and pin dependent.<br>Temp = 25 °C                                                                                                                                                             |

| V <sub>CMOA</sub>    | Common mode voltage range                                                                                                                                                                                                                                             | 0.2                                                                     | -                                      | V <sub>DD</sub> – 0.2                  | V                    | The common-mode input voltage<br>range is measured through an analog<br>output buffer. The specification<br>includes the limitations imposed by<br>the characteristics of the analog<br>output buffer. |

| G <sub>OLOA</sub>    | Open loop gain<br>Power = low, Opamp bias = low<br>Power = medium, Opamp bias = low<br>Power = high, Opamp bias = low                                                                                                                                                 | 60<br>60<br>80                                                          |                                        | -<br>-<br>-                            | dB<br>dB<br>dB       | Specification is applicable at low<br>Opamp bias. For high Opamp bias<br>mode, (except high power, high<br>Opamp bias), minimum is 60 dB.                                                              |

| V <sub>OHIGHOA</sub> | High output voltage swing (internal signals)<br>Power = low, Opamp bias = low<br>Power = medium, Opamp bias = low<br>Power = high, Opamp bias = low                                                                                                                   | V <sub>DD</sub> - 0.2<br>V <sub>DD</sub> - 0.2<br>V <sub>DD</sub> - 0.2 |                                        | -<br>-<br>-                            | V<br>V<br>V          | Power = high, Opamp bias = high<br>setting is not allowed for 2.7 V V <sub>DD</sub><br>operation.                                                                                                      |

| V <sub>OLOWOA</sub>  | Low output voltage swing (internal signals)<br>Power = low, Opamp bias = low<br>Power = medium, Opamp bias = low<br>Power = high, Opamp bias = low                                                                                                                    | -<br>-<br>-                                                             |                                        | 0.2<br>0.2<br>0.2                      | V<br>V<br>V          | Power = high, Opamp bias = high<br>setting is not allowed for 2.7 V V <sub>DD</sub><br>operation.                                                                                                      |

| I <sub>SOA</sub>     | Supply current (including associated AGND<br>buffer)<br>Power = low, Opamp bias = low<br>Power = low, Opamp bias = high<br>Power = medium, Opamp bias = low<br>Power = medium, Opamp bias = high<br>Power = high, Opamp bias = low<br>Power = high, Opamp bias = high | -<br>-<br>-<br>-<br>-                                                   | 150<br>300<br>600<br>1200<br>2400<br>- | 200<br>400<br>800<br>1600<br>3200<br>- | μΑ<br>μΑ<br>μΑ<br>μΑ | Power = high, Opamp bias = high<br>setting is not allowed for 2.7 V V <sub>DD</sub><br>operation.                                                                                                      |

| PSRR <sub>OA</sub>   | Supply voltage rejection ratio                                                                                                                                                                                                                                        | 64                                                                      | 80                                     | -                                      | dB                   | $V_{SS} \leq V_{IN} \leq (V_{DD}-2.25) \text{ or } \\ (V_{DD}-1.25 \text{ V}) \leq V_{IN} \leq V_{DD}$                                                                                                 |

#### DC Low Power Comparator Specifications

Table 17 lists the guaranteed maximum and minimum specifications for the voltage and temperature ranges: 4.75 V to 5.25 V and  $-40 \degree C \le T_A \le 85 \degree C$ , 3.0 V to 3.6 V and  $-40 \degree C \le T_A \le 85 \degree C$ , or 2.4 V to 3.0 V and  $-40 \degree C \le T_A \le 85 \degree C$ , respectively. Typical parameters are measured at 5 V at 25 °C and are for design guidance only.

| Table 17. | <b>DC Low Power</b> | Comparator | Specifications |

|-----------|---------------------|------------|----------------|

|-----------|---------------------|------------|----------------|

| Symbol              | Description                                        | Min | Тур | Max                 | Units | Notes |

|---------------------|----------------------------------------------------|-----|-----|---------------------|-------|-------|

| V <sub>REFLPC</sub> | Low power comparator (LPC) reference voltage range | 0.2 | -   | V <sub>DD</sub> – 1 | V     |       |

| I <sub>SLPC</sub>   | LPC supply current                                 | -   | 10  | 40                  | μA    |       |

| V <sub>OSLPC</sub>  | LPC voltage offset                                 | -   | 2.5 | 30                  | mV    |       |

# Table 20. 2.7-V DC Analog Output Buffer Specifications

| Symbol               | Description                                                                                         | Min                                                        | Тур        | Мах                                                        | Units    | Notes                                                                                                |

|----------------------|-----------------------------------------------------------------------------------------------------|------------------------------------------------------------|------------|------------------------------------------------------------|----------|------------------------------------------------------------------------------------------------------|

| CL                   | Load Capacitance                                                                                    | -                                                          | _          | 200                                                        | pF       | This specification applies to the external circuit that is being driven by the analog output buffer. |

| V <sub>OSOB</sub>    | Input offset voltage (absolute value)                                                               | -                                                          | 3          | 12                                                         | mV       |                                                                                                      |

| TCV <sub>OSOB</sub>  | Average input offset voltage drift                                                                  | -                                                          | +6         | -                                                          | μV/°C    |                                                                                                      |

| V <sub>CMOB</sub>    | Common mode input voltage range                                                                     | 0.5                                                        | _          | V <sub>DD</sub> – 1.0                                      | V        |                                                                                                      |

| R <sub>OUTOB</sub>   | Output resistance<br>Power = low<br>Power = high                                                    | -                                                          | 1<br>1     |                                                            | Ω<br>Ω   |                                                                                                      |

| V <sub>OHIGHOB</sub> | High output voltage swing (Load =<br>1 K ohms to V <sub>DD/2</sub> )<br>Power = low<br>Power = high | 0.5 × V <sub>DD</sub> + 0.2<br>0.5 × V <sub>DD</sub> + 0.2 |            |                                                            | V<br>V   |                                                                                                      |

| V <sub>OLOWOB</sub>  | Low output voltage swing (Load = 1<br>K ohms to $V_{DD/2}$ )<br>Power = low<br>Power = high         |                                                            | -          | 0.5 × V <sub>DD</sub> – 0.7<br>0.5 × V <sub>DD</sub> – 0.7 | V<br>V   |                                                                                                      |

| I <sub>SOB</sub>     | Supply current including Opamp<br>bias cell (No Load)<br>Power = low<br>Power = high                | _                                                          | 0.8<br>2.0 | 2.0<br>4.3                                                 | mA<br>mA |                                                                                                      |

| PSRR <sub>OB</sub>   | Supply voltage rejection ratio                                                                      | 52                                                         | 64         | -                                                          | dB       | V <sub>OUT</sub> > (V <sub>DD</sub> – 1.25).                                                         |

#### Figure 10. Basic Switch Mode Pump Circuit

### Table 22. 5-V DC Analog Reference Specifications (continued)

| Reference<br>ARF_CR<br>[5:3] | Reference Power<br>Settings            | Symbol             | Reference | Description                            | Min                                             | Тур                        | Мах                        | Units |

|------------------------------|----------------------------------------|--------------------|-----------|----------------------------------------|-------------------------------------------------|----------------------------|----------------------------|-------|

| 0b010                        | RefPower = high                        | V <sub>REFHI</sub> | Ref High  | V <sub>DD</sub>                        | V <sub>DD</sub> – 0.121                         | V <sub>DD</sub> – 0.003    | V <sub>DD</sub>            | V     |

|                              | Opamp bias = high                      | V <sub>AGND</sub>  | AGND      | V <sub>DD</sub> /2                     | V <sub>DD</sub> /2-0.040                        | V <sub>DD</sub> /2         | V <sub>DD</sub> /2 + 0.034 | V     |

|                              |                                        | V <sub>REFLO</sub> | Ref Low   | V <sub>SS</sub>                        | V <sub>SS</sub>                                 | V <sub>SS</sub> + 0.006    | V <sub>SS</sub> + 0.019    | V     |

|                              | RefPower = high                        | V <sub>REFHI</sub> | Ref High  | V <sub>DD</sub>                        | V <sub>DD</sub> - 0.083 V <sub>DD</sub> - 0.002 |                            | V <sub>DD</sub>            | V     |

|                              | Opamp bias = low                       | V <sub>AGND</sub>  | AGND      | V <sub>DD</sub> /2                     | V <sub>DD</sub> /2-0.040                        | V <sub>DD</sub> /2 - 0.001 | V <sub>DD</sub> /2 + 0.033 | V     |

|                              |                                        | V <sub>REFLO</sub> | Ref Low   | V <sub>SS</sub>                        | V <sub>SS</sub>                                 | V <sub>SS</sub> + 0.004    | V <sub>SS</sub> + 0.016    | V     |

|                              | RefPower = medium                      | V <sub>REFHI</sub> | Ref High  | V <sub>DD</sub>                        | V <sub>DD</sub> – 0.075                         | V <sub>DD</sub> – 0.002    | V <sub>DD</sub>            | V     |

|                              | Opamp bias = high                      | V <sub>AGND</sub>  | AGND      | V <sub>DD</sub> /2                     | V <sub>DD</sub> /2-0.040                        | V <sub>DD</sub> /2 - 0.001 | V <sub>DD</sub> /2 + 0.032 | V     |

|                              |                                        | V <sub>REFLO</sub> | Ref Low   | V <sub>SS</sub>                        | V <sub>SS</sub>                                 | V <sub>SS</sub> + 0.003    | V <sub>SS</sub> + 0.015    | V     |

|                              | RefPower = medium                      | V <sub>REFHI</sub> | Ref High  | V <sub>DD</sub>                        | V <sub>DD</sub> - 0.074                         | V <sub>DD</sub> - 0.002    | V <sub>DD</sub>            | V     |

|                              | Opamp bias = low                       | V <sub>AGND</sub>  | AGND      | V <sub>DD</sub> /2                     | V <sub>DD</sub> /2-0.040                        | V <sub>DD</sub> /2 - 0.001 | V <sub>DD</sub> /2 + 0.032 | V     |

|                              |                                        | V <sub>REFLO</sub> | Ref Low   | V <sub>SS</sub>                        | V <sub>SS</sub>                                 | V <sub>SS</sub> + 0.002    | V <sub>SS</sub> + 0.014    | V     |

| 0b011                        | RefPower = high                        | V <sub>REFHI</sub> | Ref High  | 3 × Bandgap                            | 3.753                                           | 3.874                      | 3.979                      | V     |

|                              | Opamp bias = high                      | V <sub>AGND</sub>  | AGND      | 2 × Bandgap                            | 2.511                                           | 2.590                      | 2.657                      | V     |

|                              |                                        | V <sub>REFLO</sub> | Ref Low   | Bandgap                                | 1.243                                           | 1.297                      | 1.333                      | V     |

|                              | RefPower = high                        | V <sub>REFHI</sub> | Ref High  | 3 × Bandgap                            | 3.767                                           | 3.881                      | 3.974                      | V     |

|                              | Opamp bias = low                       | V <sub>AGND</sub>  | AGND      | 2 × Bandgap                            | 2.518                                           | 2.592                      | 2.652                      | V     |

|                              |                                        | V <sub>REFLO</sub> | Ref Low   | Bandgap                                | 1.241                                           | 1.295                      | 1.330                      | V     |

|                              | RefPower = medium                      | V <sub>REFHI</sub> | Ref High  | 3 × Bandgap                            | 2.771                                           | 3.885                      | 3.979                      | V     |

|                              | Opamp bias = high                      | V <sub>AGND</sub>  | AGND      | 2 × Bandgap                            | 2.521                                           | 2.593                      | 2.649                      | V     |

|                              |                                        | V <sub>REFLO</sub> | Ref Low   | Bandgap                                | 1.240                                           | 1.295                      | 1.331                      | V     |

|                              | RefPower = medium                      | V <sub>REFHI</sub> | Ref High  | 3 × Bandgap                            | 3.771                                           | 3.887                      | 3.977                      | V     |

|                              | Opamp bias = low                       | V <sub>AGND</sub>  | AGND      | 2 × Bandgap                            | 2.522                                           | 2.594                      | 2.648                      | V     |

|                              |                                        | V <sub>REFLO</sub> | Ref Low   | Bandgap                                | 1.239                                           | 1.295                      | 1.332                      | V     |

| 0b100                        | RefPower = high<br>Opamp bias = high   | V <sub>REFHI</sub> | Ref High  | 2 × Bandgap + P2[6]<br>(P2[6] = 1.3 V) | 2.481 + P2[6]                                   | 2.569 + P2[6]              | 2.639 + P2[6]              | V     |

|                              |                                        | V <sub>AGND</sub>  | AGND      | 2 × Bandgap                            | 2.511                                           | 2.590                      | 2.658                      | V     |

|                              |                                        | V <sub>REFLO</sub> | Ref Low   | 2 × Bandgap – P2[6]<br>(P2[6] = 1.3 V) | 2.515 – P2[6]                                   | 2.602 – P2[6]              | 2.654 – P2[6]              | V     |

|                              | RefPower = high<br>Opamp bias = low    | V <sub>REFHI</sub> | Ref High  | 2 × Bandgap + P2[6]<br>(P2[6] = 1.3 V) | 2.498 + P2[6]                                   | 2.579 + P2[6]              | 2.642 + P2[6]              | V     |

|                              |                                        | V <sub>AGND</sub>  | AGND      | 2 × Bandgap                            | 2.518                                           | 2.592                      | 2.652                      | V     |

|                              |                                        | V <sub>REFLO</sub> | Ref Low   | 2 × Bandgap – P2[6]<br>(P2[6] = 1.3 V) | 2.513 – P2[6]                                   | 2.598 – P2[6]              | 2.650 – P2[6]              | V     |

|                              | RefPower = medium<br>Opamp bias = high | V <sub>REFHI</sub> | Ref High  | 2 × Bandgap + P2[6]<br>(P2[6] = 1.3 V) | 2.504 + P2[6]                                   | 2.583 + P2[6]              | 2.646 + P2[6]              | V     |

|                              |                                        | V <sub>AGND</sub>  | AGND      | 2 × Bandgap                            | 2.521                                           | 2.592                      | 2.650                      | V     |

|                              |                                        | V <sub>REFLO</sub> | Ref Low   | 2 × Bandgap – P2[6]<br>(P2[6] = 1.3 V) | 2.513 – P2[6]                                   | 2.596 – P2[6]              | 2.649 – P2[6]              | V     |

|                              | RefPower = medium<br>Opamp bias = low  | V <sub>REFHI</sub> | Ref High  | 2 × Bandgap + P2[6]<br>(P2[6] = 1.3 V) | 2.505 + P2[6]                                   | 2.586 + P2[6]              | 2.648 + P2[6]              | V     |

|                              |                                        | V <sub>AGND</sub>  | AGND      | 2 × Bandgap                            | 2.521                                           | 2.594                      | 2.648                      | V     |

|                              |                                        | V <sub>REFLO</sub> | Ref Low   | 2 × Bandgap – P2[6]<br>(P2[6] = 1.3 V) | 2.513 – P2[6]                                   | 2.595 – P2[6]              | 2.648 – P2[6]              | V     |

#### Table 24. 2.7-V DC Analog Reference Specifications

| Reference<br>ARF_CR<br>[5:3] | Reference Power<br>Settings                | Symbol             | Reference | Description                                                | Min                      | Тур                        | Мах                        | Units |

|------------------------------|--------------------------------------------|--------------------|-----------|------------------------------------------------------------|--------------------------|----------------------------|----------------------------|-------|

| 0b000                        | All power settings<br>Not allowed at 2.7 V | -                  | _         | -                                                          | -                        | -                          | -                          | -     |

| 0b001                        | RefPower = medium<br>Opamp bias = high     | V <sub>REFHI</sub> | Ref High  | P2[4]+P2[6] (P2[4] =<br>V <sub>DD</sub> /2, P2[6] = 0.5 V) | P2[4] + P2[6]<br>- 0.739 | P2[4]+P2[6]-<br>0.016      | P2[4]+P2[6]+<br>0.759      | V     |

|                              |                                            | V <sub>AGND</sub>  | AGND      | P2[4]                                                      | P2[4]                    | P2[4]                      | P2[4]                      | -     |

|                              |                                            | V <sub>REFLO</sub> | Ref Low   | P2[4]–P2[6] (P2[4] =<br>V <sub>DD</sub> /2, P2[6] = 0.5 V) | P2[4] – P2[6]<br>– 1.675 | P2[4]-P2[6]+<br>0.013      | P2[4]-P2[6]+<br>1.825      | V     |

|                              | RefPower = medium<br>Opamp bias = low      | V <sub>REFHI</sub> | Ref High  | P2[4]+P2[6] (P2[4] =<br>V <sub>DD</sub> /2, P2[6] = 0.5 V) | P2[4] + P2[6]<br>- 0.098 | P2[4]+P2[6]-<br>0.011      | P2[4]+P2[6]+<br>0.067      | V     |

|                              |                                            | V <sub>AGND</sub>  | AGND      | P2[4]                                                      | P2[4]                    | P2[4]                      | P2[4]                      | -     |

|                              |                                            | V <sub>REFLO</sub> | Ref Low   | P2[4]–P2[6] (P2[4] =<br>V <sub>DD</sub> /2, P2[6] = 0.5 V) | P2[4] – P2[6]<br>– 0.308 | P2[4]-P2[6]+<br>0.004      | P2[4]-P2[6]+<br>0.362      | V     |

|                              | RefPower = low<br>Opamp bias = high        | V <sub>REFHI</sub> | Ref High  | P2[4]+P2[6] (P2[4] =<br>V <sub>DD</sub> /2, P2[6] = 0.5 V) | P2[4] + P2[6]<br>- 0.042 | P2[4]+P2[6]-<br>0.005      | P2[4]+P2[6]+<br>0.035      | V     |

|                              |                                            | V <sub>AGND</sub>  | AGND      | P2[4]                                                      | P2[4]                    | P2[4]                      | P2[4]                      | -     |

|                              |                                            | V <sub>REFLO</sub> | Ref Low   | P2[4]–P2[6] (P2[4] =<br>V <sub>DD</sub> /2, P2[6] = 0.5 V) | P2[4] – P2[6]<br>– 0.030 | P2[4] – P2[6]              | P2[4]-P2[6]+<br>0.030      | V     |

|                              | RefPower = low<br>Opamp bias = low         | V <sub>REFHI</sub> | Ref High  | P2[4]+P2[6] (P2[4] =<br>V <sub>DD</sub> /2, P2[6] = 0.5 V) | P2[4] + P2[6]<br>- 0.367 | P2[4]+P2[6]-<br>0.005      | P2[4]+P2[6]+<br>0.308      | V     |

|                              |                                            | V <sub>AGND</sub>  | AGND      | P2[4]                                                      | P2[4]                    | P2[4]                      | P2[4]                      | -     |

|                              |                                            | V <sub>REFLO</sub> | Ref Low   | P2[4]–P2[6] (P2[4] =<br>V <sub>DD</sub> /2, P2[6] = 0.5 V) | P2[4] – P2[6]<br>– 0.345 | P2[4] – P2[6]              | P2[4]-P2[6]+<br>0.301      | V     |

| 0b010                        | RefPower = high                            | V <sub>REFHI</sub> | Ref High  | V <sub>DD</sub>                                            | V <sub>DD</sub> – 0.100  | V <sub>DD</sub> – 0.003    | V <sub>DD</sub>            | V     |

|                              | Opamp bias = high                          | V <sub>AGND</sub>  | AGND      | V <sub>DD</sub> /2                                         | V <sub>DD</sub> /2-0.038 | V <sub>DD</sub> /2         | V <sub>DD</sub> /2 + 0.036 | V     |

|                              |                                            | V <sub>REFLO</sub> | Ref Low   | V <sub>SS</sub>                                            | V <sub>SS</sub>          | V <sub>SS</sub> + 0.005    | V <sub>SS</sub> + 0.016    | V     |

|                              | RefPower = high                            | V <sub>REFHI</sub> | Ref High  | V <sub>DD</sub>                                            | V <sub>DD</sub> – 0.065  | V <sub>DD</sub> – 0.002    | V <sub>DD</sub>            | V     |

|                              | Opamp bias = low                           | V <sub>AGND</sub>  | AGND      | V <sub>DD</sub> /2                                         | V <sub>DD</sub> /2-0.025 | V <sub>DD</sub> /2         | V <sub>DD</sub> /2 + 0.023 | V     |

|                              |                                            | V <sub>REFLO</sub> | Ref Low   | V <sub>SS</sub>                                            | V <sub>SS</sub>          | V <sub>SS</sub> + 0.003    | V <sub>SS</sub> + 0.012    | V     |

|                              | RefPower = medium<br>Opamp bias = high     | V <sub>REFHI</sub> | Ref High  | V <sub>DD</sub>                                            | V <sub>DD</sub> – 0.054  | V <sub>DD</sub> – 0.002    | V <sub>DD</sub>            | V     |

|                              | Opamp blas – high                          | V <sub>AGND</sub>  | AGND      | V <sub>DD</sub> /2                                         | V <sub>DD</sub> /2-0.024 | V <sub>DD</sub> /2 – 0.001 | V <sub>DD</sub> /2 + 0.020 | V     |

|                              |                                            | V <sub>REFLO</sub> | Ref Low   | V <sub>SS</sub>                                            | V <sub>SS</sub>          | V <sub>SS</sub> + 0.002    | V <sub>SS</sub> + 0.012    | V     |

|                              | RefPower = medium                          | V <sub>REFHI</sub> | Ref High  | V <sub>DD</sub>                                            | V <sub>DD</sub> – 0.042  | V <sub>DD</sub> – 0.002    | V <sub>DD</sub>            | V     |

|                              | Opamp bias = low                           | V <sub>AGND</sub>  | AGND      | V <sub>DD</sub> /2                                         | V <sub>DD</sub> /2-0.027 | V <sub>DD</sub> /2 – 0.001 | V <sub>DD</sub> /2 + 0.022 | V     |

|                              |                                            | V <sub>REFLO</sub> | Ref Low   | V <sub>SS</sub>                                            | V <sub>SS</sub>          | V <sub>SS</sub> + 0.001    | V <sub>SS</sub> + 0.010    | V     |

|                              | RefPower = low                             | V <sub>REFHI</sub> | Ref High  | V <sub>DD</sub>                                            | V <sub>DD</sub> - 0.042  | V <sub>DD</sub> – 0.002    | V <sub>DD</sub>            | V     |

|                              | Opamp bias = high                          | V <sub>AGND</sub>  | AGND      | V <sub>DD</sub> /2                                         | V <sub>DD</sub> /2-0.028 | V <sub>DD</sub> /2 - 0.001 | V <sub>DD</sub> /2 + 0.023 | V     |

|                              |                                            | V <sub>REFLO</sub> | Ref Low   | V <sub>SS</sub>                                            | V <sub>SS</sub>          | V <sub>SS</sub> + 0.001    | V <sub>SS</sub> + 0.010    | V     |

|                              | RefPower = low                             | V <sub>REFHI</sub> | Ref High  | V <sub>DD</sub>                                            | V <sub>DD</sub> – 0.036  | V <sub>DD</sub> – 0.002    | V <sub>DD</sub>            | V     |

|                              | Opamp bias = low                           | V <sub>AGND</sub>  | AGND      | V <sub>DD</sub> /2                                         | V <sub>DD</sub> /2-0.184 | V <sub>DD</sub> /2 – 0.001 | V <sub>DD</sub> /2 + 0.159 | V     |

|                              |                                            | V <sub>REFLO</sub> | Ref Low   | V <sub>SS</sub>                                            | V <sub>SS</sub>          | V <sub>SS</sub> + 0.001    | V <sub>SS</sub> + 0.009    | V     |

#### DC Programming Specifications

Table 27 lists the guaranteed maximum and minimum specifications for the voltage and temperature ranges: 4.75 V to 5.25 V and -40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C, 3.0 V to 3.6 V and -40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C, or 2.4 V to 3.0 V and -40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C, respectively. Typical parameters are measured at 5 V, 3.3 V, and 2.7 V at 25 °C and are for design guidance only.

| Table 27. | . DC Programming Specificatio | ns |

|-----------|-------------------------------|----|

|-----------|-------------------------------|----|

| Symbol                | Description                                                                                 | Min                    | Тур | Max                    | Units | Notes                                                                                             |

|-----------------------|---------------------------------------------------------------------------------------------|------------------------|-----|------------------------|-------|---------------------------------------------------------------------------------------------------|

| V <sub>DDP</sub>      | V <sub>DD</sub> for programming and erase                                                   | 4.5                    | 5   | 5.5                    | V     | This specification applies<br>to the functional require-<br>ments of external<br>programmer tools |

| V <sub>DDLV</sub>     | Low V <sub>DD</sub> for verify                                                              | 2.4                    | 2.5 | 2.6                    | V     | This specification applies<br>to the functional require-<br>ments of external<br>programmer tools |

| V <sub>DDHV</sub>     | High V <sub>DD</sub> for verify                                                             | 5.1                    | 5.2 | 5.3                    | V     | This specification applies<br>to the functional require-<br>ments of external<br>programmer tools |

| V <sub>DDIWRITE</sub> | Supply voltage for flash write operation                                                    | 2.7                    |     | 5.25                   | V     | This specification applies<br>to this device when it is<br>executing internal flash<br>writes     |

| I <sub>DDP</sub>      | Supply current during programming or verify                                                 | -                      | 5   | 25                     | mA    |                                                                                                   |

| V <sub>ILP</sub>      | Input low voltage during programming or verify                                              | -                      | -   | 0.8                    | V     |                                                                                                   |

| V <sub>IHP</sub>      | Input high voltage during programming or verify                                             | 2.1                    | -   | -                      | V     |                                                                                                   |

| I <sub>ILP</sub>      | Input current when applying V <sub>ILP</sub> to P1[0] or P1[1] during programming or verify | -                      | -   | 0.2                    | mA    | Driving internal pull-down resistor                                                               |

| I <sub>IHP</sub>      | Input current when applying V <sub>IHP</sub> to P1[0] or P1[1] during programming or verify | -                      | -   | 1.5                    | mA    | Driving internal pull-down resistor                                                               |

| V <sub>OLV</sub>      | Output low voltage during programming or verify                                             | -                      | -   | V <sub>SS</sub> + 0.75 | V     |                                                                                                   |

| V <sub>OHV</sub>      | Output high voltage during programming or verify                                            | V <sub>DD</sub> – 1.0  | -   | V <sub>DD</sub>        | V     |                                                                                                   |

| Flash <sub>ENPB</sub> | Flash endurance (per block)                                                                 | 50,000 <sup>[16]</sup> | -   | -                      | -     | Erase/write cycles per<br>block                                                                   |

| Flash <sub>ENT</sub>  | Flash endurance (total) <sup>[17]</sup>                                                     | 1,800,000              | -   | -                      | -     | Erase/write cycles                                                                                |

| Flash <sub>DR</sub>   | Flash data retention                                                                        | 10                     | -   | -                      | Years |                                                                                                   |

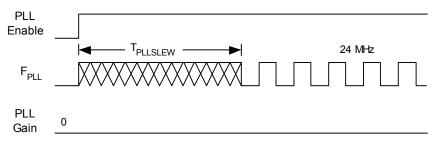

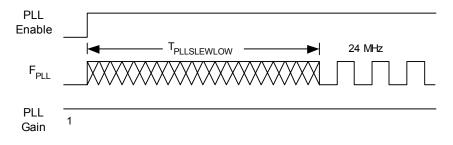

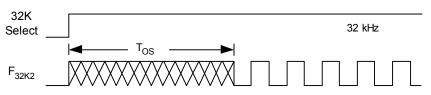

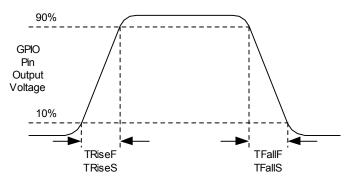

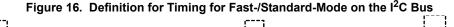

#### DC I<sup>2</sup>C Specifications