Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                              |

|----------------------------|------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                     |

| Core Processor             | M8C                                                                          |

| Core Size                  | 8-Bit                                                                        |

| Speed                      | 24MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                            |

| Peripherals                | POR, PWM, WDT                                                                |

| Number of I/O              | 16                                                                           |

| Program Memory Size        | 4KB (4K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | -                                                                            |

| RAM Size                   | 256 x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 2.4V ~ 5.25V                                                                 |

| Data Converters            | A/D 8x14b; D/A 2x9b                                                          |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

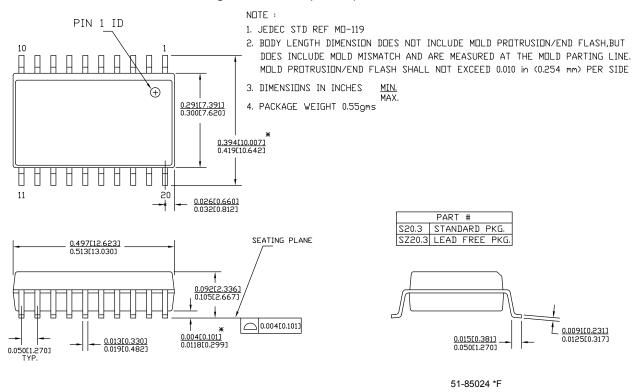

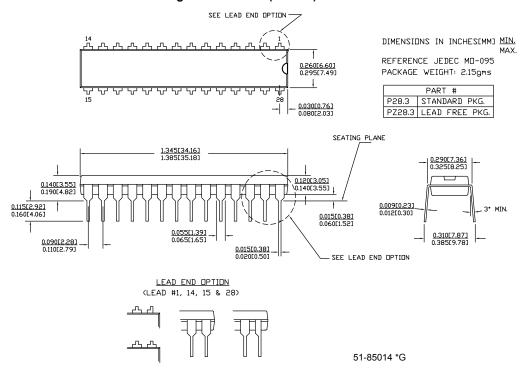

| Mounting Type              | Surface Mount                                                                |

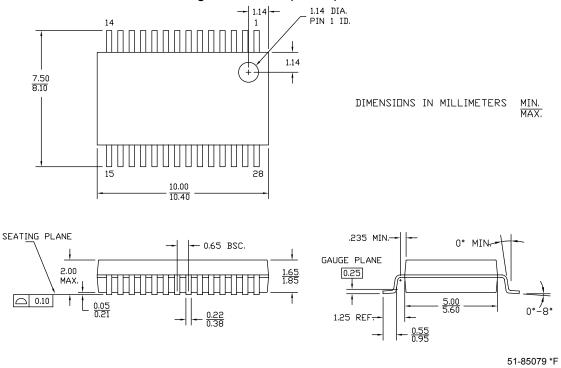

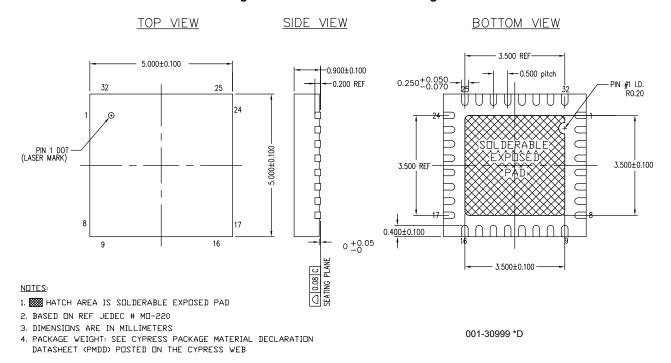

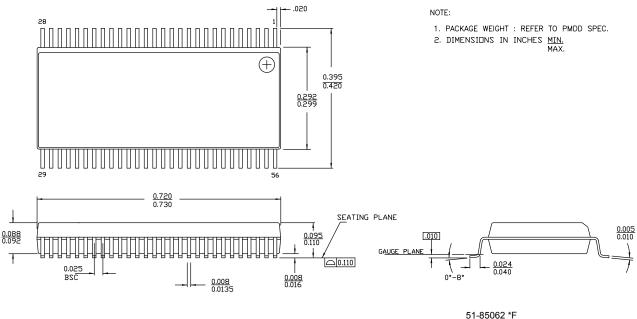

| Package / Case             | 20-SOIC (0.295", 7.50mm Width)                                               |

| Supplier Device Package    | 20-SOIC                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/cy8c24223a-24sxit |

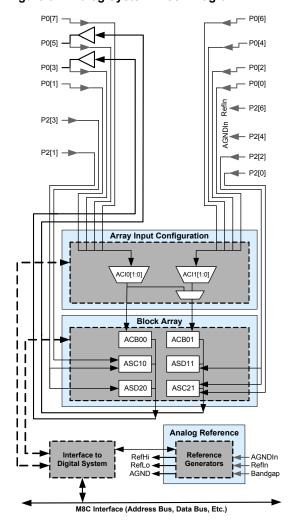

## **Analog System**

The analog system consists of six configurable blocks, each consisting of an opamp circuit that allows the creation of complex analog signal flows. Analog peripherals are very flexible and can be customized to support specific application requirements. Some of the more common PSoC analog functions (most available as user modules) are:

- ADCs (up to two, with 6- to 14-bit resolution, selectable as incremental, delta sigma, and SAR)

- Filters (two and four pole band-pass, low-pass, and notch)

- Amplifiers (up to two, with selectable gain to 48x)

- Instrumentation amplifiers (one with selectable gain to 93x)

- Comparators (up to two, with 16 selectable thresholds)

- DACs (up to two, with 6 to 9-bit resolution)

- Multiplying DACs (up to two, with 6 to 9-bit resolution)

- High current output drivers (two with 30 mA drive as a PSoC Core resource)

- 1.3 V reference (as a system resource)

- DTMF dialer

- Modulators

- Correlators

- Peak detectors

- Many other topologies possible

Analog blocks are arranged in a column of three, which includes one continuous time (CT) and two switched capacitor (SC) blocks, as shown in Figure 3

Figure 3. Analog System Block Diagram

## **Register Reference**

This section lists the registers of the CY8C24x23A PSoC device. For detailed register information, see the PSoC Programmable Sytem-on-Chip Reference Manual.

## **Register Conventions**

Abbreviations Used

The register conventions specific to this section are listed in the following table.

Table 7. Abbreviations

| Convention | Description                  |

|------------|------------------------------|

| R          | Read register or bit(s)      |

| W          | Write register or bit(s)     |

| L          | Logical register or bit(s)   |

| С          | Clearable register or bit(s) |

| #          | Access is bit specific       |

## **Register Mapping Tables**

The PSoC device has a total register address space of 512 bytes. The register space is referred to as I/O space and is divided into two banks, Bank 0 and Bank 1. The XOI bit in the Flag register (CPU\_F) determines which bank the user is currently in. When the XOI bit is set, the user is in Bank 1.

**Note** In the following register mapping tables, blank fields are reserved and must not be accessed.

Table 8. Register Map Bank 0 Table: User Space

| Name     | Addr (0,Hex) |    | Name     | Addr (0,Hex) | Access | Name       | Addr (0,Hex) | Access | Name        | Addr (0,Hex) | Access |

|----------|--------------|----|----------|--------------|--------|------------|--------------|--------|-------------|--------------|--------|

| PRT0DR   | 00           | RW |          | 40           |        | ASC10CR0   | 80           | RW     |             | C0           |        |

| PRT0IE   | 01           | RW |          | 41           |        | ASC10CR1   | 81           | RW     |             | C1           |        |

| PRT0GS   | 02           | RW |          | 42           |        | ASC10CR2   | 82           | RW     |             | C2           |        |

| PRT0DM2  | 03           | RW |          | 43           |        | ASC10CR3   | 83           | RW     |             | C3           |        |

| PRT1DR   | 04           | RW |          | 44           |        | ASD11CR0   | 84           | RW     |             | C4           |        |

| PRT1IE   | 05           | RW |          | 45           |        | ASD11CR1   | 85           | RW     |             | C5           |        |

| PRT1GS   | 06           | RW |          | 46           |        | ASD11CR2   | 86           | RW     |             | C6           |        |

| PRT1DM2  | 07           | RW |          | 47           |        | ASD11CR3   | 87           | RW     |             | C7           |        |

| PRT2DR   | 08           | RW |          | 48           |        |            | 88           |        |             | C8           |        |

| PRT2IE   | 09           | RW |          | 49           |        |            | 89           |        |             | C9           |        |

| PRT2GS   | 0A           | RW |          | 4A           |        |            | 8A           |        |             | CA           |        |

| PRT2DM2  | 0B           | RW |          | 4B           |        |            | 8B           |        |             | СВ           |        |

|          | 0C           |    |          | 4C           |        |            | 8C           |        |             | CC           |        |

|          | 0D           |    |          | 4D           |        |            | 8D           |        |             | CD           |        |

|          | 0E           |    |          | 4E           |        |            | 8E           |        |             | CE           |        |

|          | 0F           |    |          | 4F           |        |            | 8F           |        |             | CF           |        |

|          | 10           |    |          | 50           |        | ASD20CR0   | 90           | RW     |             | D0           |        |

|          | 11           |    |          | 51           |        | ASD20CR1   | 91           | RW     |             | D1           |        |

|          | 12           |    |          | 52           |        | ASD20CR2   | 92           | RW     |             | D2           |        |

|          | 13           |    |          | 53           |        | ASD20CR3   | 93           | RW     |             | D3           |        |

|          | 14           |    |          | 54           |        | ASC21CR0   | 94           | RW     |             | D4           |        |

|          | 15           |    |          | 55           |        | ASC21CR1   | 95           | RW     |             | D5           |        |

|          | 16           |    |          | 56           |        | ASC21CR2   | 96           | RW     | I2C_CFG     | D6           | RW     |

|          | 17           |    |          | 57           |        | ASC21CR3   | 97           | RW     | I2C SCR     | D7           | #      |

|          | 18           |    |          | 58           |        | 7100210110 | 98           | 1444   | I2C_DR      | D8           | RW     |

|          | 19           |    |          | 59           |        |            | 99           |        | I2C MSCR    | D9           | #      |

|          | 1A           |    |          | 5A           |        |            | 9A           |        | INT_CLR0    | DA           | RW     |

|          | 1B           |    |          | 5B           |        |            | 9B           |        | INT_CLR1    | DB           | RW     |

|          | 1C           |    |          | 5C           |        |            | 9C           |        | INT_CLKT    | DC           | KVV    |

|          | 1D           |    |          | 5D           |        |            | 9D           |        | INT_CLR3    | DD           | RW     |

|          | 1E           |    |          | 5E           |        |            | 9E           |        | INT_CERS    | DE           | RW     |

|          | 1F           |    |          |              |        |            | 9F           |        | IIVI_IVISKS | DF           | IXVV   |

| DDDOODDO |              | ш  | ANAV INI | 5F           | DW     |            |              |        | INIT MOKO   | E0           | DW     |

| DBB00DR0 | 20           | #  | AMX_IN   | 60           | RW     |            | A0           |        | INT_MSK0    |              | RW     |

| DBB00DR1 | 21           | W  |          | 61           |        |            | A1           |        | INT_MSK1    | E1           | RW     |

| DBB00DR2 | 22           | RW | ADE OD   | 62           | DW     |            | A2           |        | INT_VC      | E2           | RC     |

| DBB00CR0 | 23           | #  | ARF_CR   | 63           | RW     |            | A3           |        | RES_WDT     | E3           | W      |

| DBB01DR0 | 24           | #  | CMP_CR0  | 64           | #      |            | A4           |        | DEC_DH      | E4           | RC     |

| DBB01DR1 | 25           | W  | ASY_CR   | 65           | #      |            | A5           |        | DEC_DL      | E5           | RC     |

| DBB01DR2 | 26           | RW | CMP_CR1  | 66           | RW     |            | A6           |        | DEC_CR0     | E6           | RW     |

| DBB01CR0 | 27           | #  |          | 67           |        |            | A7           |        | DEC_CR1     | E7           | RW     |

| DCB02DR0 | 28           | #  |          | 68           |        |            | A8           |        | MUL_X       | E8           | W      |

| DCB02DR1 | 29           | W  |          | 69           |        |            | A9           |        | MUL_Y       | E9           | W      |

| DCB02DR2 | 2A           | RW |          | 6A           |        |            | AA           |        | MUL_DH      | EA           | R      |

| DCB02CR0 | 2B           | #  |          | 6B           |        |            | AB           |        | MUL_DL      | EB           | R      |

| DCB03DR0 | 2C           | #  |          | 6C           |        |            | AC           |        | ACC_DR1     | EC           | RW     |

| DCB03DR1 | 2D           | W  |          | 6D           |        |            | AD           |        | ACC_DR0     | ED           | RW     |

| DCB03DR2 | 2E           | RW |          | 6E           |        |            | AE           |        | ACC_DR3     | EE           | RW     |

| DCB03CR0 | 2F           | #  |          | 6F           |        |            | AF           |        | ACC_DR2     | EF           | RW     |

|          | 30           |    | ACB00CR3 | 70           | RW     | RDI0RI     | B0           | RW     |             | F0           |        |

|          | 31           |    | ACB00CR0 | 71           | RW     | RDI0SYN    | B1           | RW     |             | F1           |        |

|          | 32           |    | ACB00CR1 | 72           | RW     | RDI0IS     | B2           | RW     |             | F2           |        |

|          | 33           |    | ACB00CR2 | 73           | RW     | RDI0LT0    | B3           | RW     |             | F3           |        |

|          | 34           |    | ACB01CR3 | 74           | RW     | RDI0LT1    | B4           | RW     |             | F4           |        |

|          | 35           |    | ACB01CR0 | 75           | RW     | RDI0RO0    | B5           | RW     |             | F5           |        |

|          | 36           |    | ACB01CR1 | 76           | RW     | RDI0RO1    | B6           | RW     |             | F6           |        |

|          | 37           |    | ACB01CR2 | 77           | RW     |            | B7           |        | CPU_F       | F7           | RL     |

|          | 38           |    |          | 78           |        |            | B8           |        |             | F8           |        |

|          | 39           |    |          | 79           |        |            | B9           |        |             | F9           |        |

|          | 3A           |    |          | 7A           |        |            | BA           |        |             | FA           |        |

|          | 3B           |    |          | 7B           |        |            | BB           |        |             | FB           |        |

|          | 3C           |    |          | 7C           |        |            | BC           |        |             | FC           |        |

|          | 3D           |    |          | 7D           |        |            | BD           |        |             | FD           |        |

|          | 3E           |    |          | 7E           |        |            | BE           |        | CPU SCR1    | FE           | #      |

|          | 3F           |    |          | 7F           |        |            | BF           |        | CPU SCR0    | FF           | #      |

|          |              |    |          |              |        |            |              |        |             |              |        |

Blank fields are Reserved and must not be accessed.

# Access is bit specific.

Table 15. 3.3-V DC Operational Amplifier Specifications

| Symbol               | Description                                                                                                                                                                                                                                      | Min                                                                     | Тур                               | Max                               | Units                      | Notes                                                                                                                                                                                   |

|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|-----------------------------------|-----------------------------------|----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>OSOA</sub>    | Input offset voltage (absolute value) Power = low, Opamp bias = high Power = medium, Opamp bias = high Power = high, Opamp bias = high                                                                                                           | -<br>-<br>-                                                             | 1.65<br>1.32<br>–                 | 10<br>8<br>-                      | mV<br>mV<br>mV             | Power = high, Opamp bias = high setting is not allowed for $3.3 \text{ V V}_{DD}$ operation.                                                                                            |

| TCV <sub>OSOA</sub>  | Average input offset voltage drift                                                                                                                                                                                                               | -                                                                       | 7.0                               | 35.0                              | μV/°C                      |                                                                                                                                                                                         |

| I <sub>EBOA</sub>    | Input leakage current (port 0 analog pins)                                                                                                                                                                                                       | -                                                                       | 20                                | -                                 | pА                         | Gross tested to 1 μA                                                                                                                                                                    |

| C <sub>INOA</sub>    | Input capacitance (port 0 analog pins)                                                                                                                                                                                                           |                                                                         | 4.5                               | 9.5                               | pF                         | Package and pin dependent.<br>Temp = 25 °C                                                                                                                                              |

| V <sub>CMOA</sub>    | Common mode voltage range                                                                                                                                                                                                                        | 0.2                                                                     | -                                 | V <sub>DD</sub> – 0.2             | V                          | The common-mode input voltage range is measured through an analog output buffer. The specification includes the limitations imposed by the characteristics of the analog output buffer. |

| G <sub>OLOA</sub>    | Open loop gain Power = low, ppamp Opamp bias = low Power = medium, Opamp bias = low Power = high, Opamp bias = low                                                                                                                               | 60<br>60<br>80                                                          | _<br>_<br>_                       | -<br>-<br>-                       | dB<br>dB<br>dB             | Specification is applicable at low<br>Opamp bias. For high Opamp bias<br>mode (except high power, high<br>Opamp bias), minimum is 60 dB.                                                |

| V <sub>OHIGHOA</sub> | High output voltage swing (internal signals) Power = low, Opamp bias = low Power = medium, Opamp bias = low Power = high, Opamp bias = low                                                                                                       | V <sub>DD</sub> - 0.2<br>V <sub>DD</sub> - 0.2<br>V <sub>DD</sub> - 0.2 | _<br>_<br>_                       | -<br>-<br>-                       | V<br>V<br>V                | Power = high, Opamp bias = high setting is not allowed for 3.3 V V <sub>DD</sub> operation.                                                                                             |

| V <sub>OLOWOA</sub>  | Low output voltage swing (internal signals) Power = low, ppamp Opamp bias = low Power = medium, Opamp bias = low Power = high, Opamp bias = low                                                                                                  | -<br>-<br>-                                                             | _<br>_<br>_                       | 0.2<br>0.2<br>0.2                 | V<br>V                     | Power = high, Opamp bias = high setting is not allowed for 3.3 V V <sub>DD</sub> operation.                                                                                             |

| Isoa                 | Supply current (including associated AGND buffer) Power = low, Opamp bias = low Power = low, Opamp bias = high Power = medium, Opamp bias = low Power = medium, Opamp bias = high Power = high, Opamp bias = low Power = high, Opamp bias = high |                                                                         | 150<br>300<br>600<br>1200<br>2400 | 200<br>400<br>800<br>1600<br>3200 | µА<br>µА<br>µА<br>µА<br>µА | Power = high, Opamp bias = high setting is not allowed for 3.3 V V <sub>DD</sub> operation.                                                                                             |

| PSRR <sub>OA</sub>   | Supply voltage rejection ratio                                                                                                                                                                                                                   | 64                                                                      | 80                                | -                                 | dB                         | $V_{SS} \le V_{IN} \le (V_{DD} - 2.25)$ or $(V_{DD} - 1.25 \ V) \le V_{IN} \le V_{DD}$                                                                                                  |

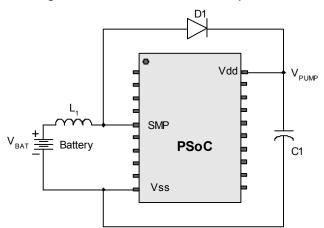

## DC Switch Mode Pump Specifications

Table 21 lists the guaranteed maximum and minimum specifications for the voltage and temperature ranges: 4.75 V to 5.25 V and  $-40~^{\circ}\text{C} \le T_{A} \le 85~^{\circ}\text{C}$ , 3.0 V to 3.6 V and  $-40~^{\circ}\text{C} \le T_{A} \le 85~^{\circ}\text{C}$ , or 2.4 V to 3.0 V and  $-40~^{\circ}\text{C} \le T_{A} \le 85~^{\circ}\text{C}$ , respectively. Typical parameters are measured at 5 V, 3.3 V, and 2.7 V at 25  $^{\circ}\text{C}$  and are for design guidance only.

Table 21. DC Switch Mode Pump (SMP) Specifications

| Symbol                    | Description                                       | Min         | Тур  | Max         | Units           | Notes                                                                                                                                                                                        |

|---------------------------|---------------------------------------------------|-------------|------|-------------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>PUMP</sub> 5 V     | 5 V output voltage from pump                      | 4.75        | 5.0  | 5.25        | V               | Configuration listed in footnote. <sup>[11]</sup> Average, neglecting ripple. SMP trip voltage is set to 5.0 V.                                                                              |

| V <sub>PUMP</sub> 3 V     | 3.3 V output voltage from pump                    | 3.00        | 3.25 | 3.60        | V               | Configuration listed in footnote. [11] Average, neglecting ripple. SMP trip voltage is set to 3.25 V.                                                                                        |

| V <sub>PUMP</sub> 2 V     | 2.6 V output voltage from pump                    | 2.45        | 2.55 | 2.80        | V               | Configuration listed in footnote. [11] Average, neglecting ripple. SMP trip voltage is set to 2.55 V.                                                                                        |

| I <sub>PUMP</sub>         |                                                   | 5<br>8<br>8 |      | -<br>-<br>- | mA<br>mA<br>mA  | Configuration listed in footnote. [11] SMP trip voltage is set to 5.0 V. SMP trip voltage is set to 3.25 V. SMP trip voltage is set to 2.55 V.                                               |

| V <sub>BAT</sub> 5 V      | Input voltage range from battery                  | 1.8         | _    | 5.0         | V               | Configuration listed in footnote. <sup>[11]</sup> SMP trip voltage is set to 5.0 V.                                                                                                          |

| V <sub>BAT</sub> 3 V      | Input voltage range from battery                  | 1.0         | _    | 3.3         | V               | Configuration listed in footnote. <sup>[11]</sup> SMP trip voltage is set to 3.25 V.                                                                                                         |

| V <sub>BAT</sub> 2 V      | Input voltage range from battery                  | 1.0         | _    | 3.0         | V               | Configuration listed in footnote. <sup>[11]</sup> SMP trip voltage is set to 2.55 V.                                                                                                         |

| V <sub>BATSTART</sub>     | Minimum input voltage from battery to start pump  | 1.2         | -    | -           | V               | Configuration listed in footnote. $^{[11]}$ 0 °C $\leq$ T <sub>A</sub> $\leq$ 100. 1.25 V at T <sub>A</sub> = $-40$ °C                                                                       |

| ΔV <sub>PUMP_Line</sub>   | Line regulation (over V <sub>BAT</sub> range)     | -           | 5    | -           | %V <sub>O</sub> | Configuration listed in footnote. [11] V <sub>O</sub> is the V <sub>DD</sub> Value for PUMP Trip" specified by the VM[2:0] setting in the DC POR and LVD Specification, Table 26 on page 35. |

| ΔV <sub>PUMP_Load</sub>   | Load regulation                                   | -           | 5    | -           | %V <sub>O</sub> | Configuration listed in footnote. [11] $V_O$ is the " $V_{DD}$ value for PUMP Trip" specified by the VM[2:0] setting in the DC POR and LVD Specification, Table 26 on page 35.               |

| $\Delta V_{PUMP\_Ripple}$ | Output voltage ripple (depends on capacitor/load) | _           | 100  | _           | mVpp            | Configuration listed in footnote. <sup>[11]</sup> Load is 5 mA.                                                                                                                              |

| E <sub>3</sub>            | Efficiency                                        | 35          | 50   | -           | %               | Configuration listed in footnote. <sup>[11]</sup> Load is 5 mA. SMP trip voltage is set to 3.25 V.                                                                                           |

| E <sub>2</sub>            | Efficiency                                        | -           | _    | ı           |                 |                                                                                                                                                                                              |

| F <sub>PUMP</sub>         | Switching frequency                               | -           | 1.3  | _           | MHz             |                                                                                                                                                                                              |

| DC <sub>PUMP</sub>        | Switching duty cycle                              |             | 50   |             | %               |                                                                                                                                                                                              |

Figure 10. Basic Switch Mode Pump Circuit

Table 22. 5-V DC Analog Reference Specifications (continued)

| Reference<br>ARF_CR<br>[5:3] | Reference Power<br>Settings            | Symbol             | Reference | Description                            | Min                        | Тур                        | Max                        | Units |

|------------------------------|----------------------------------------|--------------------|-----------|----------------------------------------|----------------------------|----------------------------|----------------------------|-------|

| 0b010                        | RefPower = high                        | V <sub>REFHI</sub> | Ref High  | $V_{DD}$                               | V <sub>DD</sub> – 0.121    | V <sub>DD</sub> – 0.003    | V <sub>DD</sub>            | V     |

|                              | Opamp bias = high                      | $V_{AGND}$         | AGND      | V <sub>DD</sub> /2                     | V <sub>DD</sub> /2 – 0.040 | V <sub>DD</sub> /2         | $V_{DD}/2 + 0.034$         | V     |

|                              |                                        | $V_{REFLO}$        | Ref Low   | V <sub>SS</sub>                        | V <sub>SS</sub>            | V <sub>SS</sub> + 0.006    | V <sub>SS</sub> + 0.019    | V     |

|                              | RefPower = high                        | $V_{REFHI}$        | Ref High  | $V_{DD}$                               | V <sub>DD</sub> – 0.083    | V <sub>DD</sub> – 0.002    | $V_{DD}$                   | V     |

|                              | Opamp bias = low                       | $V_{AGND}$         | AGND      | V <sub>DD</sub> /2                     | V <sub>DD</sub> /2 – 0.040 | V <sub>DD</sub> /2 – 0.001 | $V_{DD}/2 + 0.033$         | V     |

|                              |                                        | $V_{REFLO}$        | Ref Low   | V <sub>SS</sub>                        | V <sub>SS</sub>            | V <sub>SS</sub> + 0.004    | V <sub>SS</sub> + 0.016    | V     |

|                              | RefPower = medium<br>Opamp bias = high | V <sub>REFHI</sub> | Ref High  | $V_{DD}$                               | V <sub>DD</sub> – 0.075    | V <sub>DD</sub> – 0.002    | $V_{DD}$                   | V     |

|                              |                                        | V <sub>AGND</sub>  | AGND      | V <sub>DD</sub> /2                     | V <sub>DD</sub> /2 – 0.040 | V <sub>DD</sub> /2 – 0.001 | $V_{DD}/2 + 0.032$         | V     |

|                              |                                        | V <sub>REFLO</sub> | Ref Low   | V <sub>SS</sub>                        | V <sub>SS</sub>            | V <sub>SS</sub> + 0.003    | V <sub>SS</sub> + 0.015    | V     |

|                              | RefPower = medium                      | V <sub>REFHI</sub> | Ref High  | $V_{DD}$                               | V <sub>DD</sub> – 0.074    | V <sub>DD</sub> – 0.002    | $V_{DD}$                   | V     |

|                              | Opamp bias = low                       | V <sub>AGND</sub>  | AGND      | V <sub>DD</sub> /2                     | V <sub>DD</sub> /2 – 0.040 | V <sub>DD</sub> /2 – 0.001 | V <sub>DD</sub> /2 + 0.032 | V     |

|                              |                                        | V <sub>REFLO</sub> | Ref Low   | V <sub>SS</sub>                        | V <sub>SS</sub>            | V <sub>SS</sub> + 0.002    | V <sub>SS</sub> + 0.014    | V     |

| 0b011                        | RefPower = high                        | V <sub>REFHI</sub> | Ref High  | 3 × Bandgap                            | 3.753                      | 3.874                      | 3.979                      | V     |

|                              | Opamp bias = high                      | V <sub>AGND</sub>  | AGND      | 2 × Bandgap                            | 2.511                      | 2.590                      | 2.657                      | V     |

|                              |                                        | V <sub>REFLO</sub> | Ref Low   | Bandgap                                | 1.243                      | 1.297                      | 1.333                      | V     |

|                              | RefPower = high                        | V <sub>REFHI</sub> | Ref High  | 3 × Bandgap                            | 3.767                      | 3.881                      | 3.974                      | V     |

|                              | Opamp bias = low                       | V <sub>AGND</sub>  | AGND      | 2 × Bandgap                            | 2.518                      | 2.592                      | 2.652                      | V     |

|                              |                                        | V <sub>REFLO</sub> | Ref Low   | Bandgap                                | 1.241                      | 1.295                      | 1.330                      | V     |

|                              | RefPower = medium                      | V <sub>REFHI</sub> | Ref High  | 3 × Bandgap                            | 2.771                      | 3.885                      | 3.979                      | V     |

|                              | Opamp bias = high                      | V <sub>AGND</sub>  | AGND      | 2 × Bandgap                            | 2.521                      | 2.593                      | 2.649                      | V     |

|                              |                                        | V <sub>REFLO</sub> | Ref Low   | Bandgap                                | 1.240                      | 1.295                      | 1.331                      | V     |

|                              | RefPower = medium<br>Opamp bias = low  | V <sub>REFHI</sub> | Ref High  | 3 × Bandgap                            | 3.771                      | 3.887                      | 3.977                      | V     |

|                              |                                        | V <sub>AGND</sub>  | AGND      | 2 × Bandgap                            | 2.522                      | 2.594                      | 2.648                      | V     |

|                              |                                        | V <sub>REFLO</sub> | Ref Low   | Bandgap                                | 1.239                      | 1.295                      | 1.332                      | V     |

| 0b100                        | RefPower = high<br>Opamp bias = high   | V <sub>REFHI</sub> | Ref High  | 2 × Bandgap + P2[6]<br>(P2[6] = 1.3 V) | 2.481 + P2[6]              | 2.569 + P2[6]              | 2.639 + P2[6]              | V     |

|                              |                                        | V <sub>AGND</sub>  | AGND      | 2 × Bandgap                            | 2.511                      | 2.590                      | 2.658                      | V     |

|                              |                                        | V <sub>REFLO</sub> | Ref Low   | 2 × Bandgap – P2[6]<br>(P2[6] = 1.3 V) | 2.515 – P2[6]              | 2.602 - P2[6]              | 2.654 - P2[6]              | V     |

|                              | RefPower = high<br>Opamp bias = low    | $V_{REFHI}$        | Ref High  | 2 × Bandgap + P2[6]<br>(P2[6] = 1.3 V) | 2.498 + P2[6]              | 2.579 + P2[6]              | 2.642 + P2[6]              | V     |

|                              |                                        | $V_{AGND}$         | AGND      | 2 × Bandgap                            | 2.518                      | 2.592                      | 2.652                      | V     |

|                              |                                        | V <sub>REFLO</sub> | Ref Low   | 2 × Bandgap – P2[6]<br>(P2[6] = 1.3 V) | 2.513 – P2[6]              | 2.598 - P2[6]              | 2.650 - P2[6]              | V     |

|                              | RefPower = medium<br>Opamp bias = high | $V_{REFHI}$        | Ref High  | 2 × Bandgap + P2[6]<br>(P2[6] = 1.3 V) | 2.504 + P2[6]              | 2.583 + P2[6]              | 2.646 + P2[6]              | V     |

|                              |                                        | $V_{AGND}$         | AGND      | 2 × Bandgap                            | 2.521                      | 2.592                      | 2.650                      | V     |

|                              |                                        | V <sub>REFLO</sub> | Ref Low   | 2 × Bandgap – P2[6]<br>(P2[6] = 1.3 V) | 2.513 – P2[6]              | 2.596 - P2[6]              | 2.649 - P2[6]              | V     |

|                              | RefPower = medium<br>Opamp bias = low  | $V_{REFHI}$        | Ref High  | 2 × Bandgap + P2[6]<br>(P2[6] = 1.3 V) | 2.505 + P2[6]              | 2.586 + P2[6]              | 2.648 + P2[6]              | V     |

|                              |                                        | $V_{AGND}$         | AGND      | 2 × Bandgap                            | 2.521                      | 2.594                      | 2.648                      | V     |

|                              |                                        | V <sub>REFLO</sub> | Ref Low   | 2 × Bandgap – P2[6]<br>(P2[6] = 1.3 V) | 2.513 – P2[6]              | 2.595 – P2[6]              | 2.648 – P2[6]              | V     |

Table 22. 5-V DC Analog Reference Specifications (continued)

| Reference       |                                        |                    |           |                                                 |                 |                         |                         |       |

|-----------------|----------------------------------------|--------------------|-----------|-------------------------------------------------|-----------------|-------------------------|-------------------------|-------|

| ARF_CR<br>[5:3] | Reference Power<br>Settings            | Symbol             | Reference | Description                                     | Min             | Тур                     | Max                     | Units |

| 0b101           | RefPower = high<br>Opamp bias = high   | V <sub>REFHI</sub> | Ref High  | P2[4] + Bandgap<br>(P2[4] = V <sub>DD</sub> /2) | P2[4] + 1.228   | P2[4] + 1.284           | P2[4] + 1.332           | V     |

|                 |                                        | $V_{AGND}$         | AGND      | P2[4]                                           | P2[4]           | P2[4]                   | P2[4]                   | -     |

|                 |                                        | V <sub>REFLO</sub> | Ref Low   | P2[4] – Bandgap<br>(P2[4] = V <sub>DD</sub> /2) | P2[4] – 1.358   | P2[4] – 1.293           | P2[4] – 1.226           | V     |

|                 | RefPower = high<br>Opamp bias = low    | V <sub>REFHI</sub> | Ref High  | P2[4] + Bandgap<br>(P2[4] = V <sub>DD</sub> /2) | P2[4] + 1.236   | P2[4] + 1.289           | P2[4] + 1.332           | V     |

|                 |                                        | V <sub>AGND</sub>  | AGND      | P2[4]                                           | P2[4]           | P2[4]                   | P2[4]                   | -     |

|                 |                                        | $V_{REFLO}$        | Ref Low   | P2[4] - Bandgap<br>(P2[4] = $V_{DD}/2$ )        | P2[4] – 1.357   | P2[4] – 1.297           | P2[4] - 1.229           | V     |

|                 | RefPower = medium<br>Opamp bias = high | V <sub>REFHI</sub> | Ref High  | P2[4] + Bandgap<br>(P2[4] = V <sub>DD</sub> /2) | P2[4] + 1.237   | P2[4] + 1.291           | P2[4] + 1.337           | V     |

|                 |                                        | $V_{AGND}$         | AGND      | P2[4]                                           | P2[4]           | P2[4]                   | P2[4]                   | -     |

|                 |                                        | V <sub>REFLO</sub> | Ref Low   | P2[4] - Bandgap<br>(P2[4] = $V_{DD}/2$ )        | P2[4] – 1.356   | P2[4] – 1.299           | P2[4] – 1.232           | V     |

|                 | RefPower = medium<br>Opamp bias = low  | $V_{REFHI}$        | Ref High  | P2[4] + Bandgap<br>(P2[4] = $V_{DD}/2$ )        | P2[4] + 1.237   | P2[4] + 1.292           | P2[4] + 1.337           | V     |

|                 |                                        | V <sub>AGND</sub>  | AGND      | P2[4]                                           | P2[4]           | P2[4]                   | P2[4]                   | -     |

|                 |                                        | $V_{REFLO}$        | Ref Low   | P2[4] - Bandgap<br>(P2[4] = $V_{DD}/2$ )        | P2[4] – 1.357   | P2[4] – 1.300           | P2[4] – 1.233           | V     |

| 0b110           | RefPower = high                        | V <sub>REFHI</sub> | Ref High  | 2 × Bandgap                                     | 2.512           | 2.594                   | 2.654                   | V     |

|                 | Opamp bias = high                      | $V_{AGND}$         | AGND      | Bandgap                                         | 1.250           | 1.303                   | 1.346                   | V     |

|                 |                                        | $V_{REFLO}$        | Ref Low   | $V_{SS}$                                        | V <sub>SS</sub> | $V_{SS} + 0.011$        | $V_{SS} + 0.027$        | V     |

|                 | RefPower = high                        | $V_{REFHI}$        | Ref High  | 2 × Bandgap                                     | 2.515           | 2.592                   | 2.654                   | V     |

|                 | Opamp bias = low                       | $V_{AGND}$         | AGND      | Bandgap                                         | 1.253           | 1.301                   | 1.340                   | V     |

|                 |                                        | $V_{REFLO}$        | Ref Low   | $V_{SS}$                                        | V <sub>SS</sub> | $V_{SS} + 0.006$        | $V_{SS} + 0.02$         | V     |

|                 | RefPower = medium                      | $V_{REFHI}$        | Ref High  | 2 × Bandgap                                     | 2.518           | 2.593                   | 2.651                   | V     |

|                 | Opamp bias = high                      | $V_{AGND}$         | AGND      | Bandgap                                         | 1.254           | 1.301                   | 1.338                   | ٧     |

|                 |                                        | $V_{REFLO}$        | Ref Low   | $V_{SS}$                                        | V <sub>SS</sub> | $V_{SS} + 0.004$        | $V_{SS} + 0.017$        | V     |

|                 | RefPower = medium                      | $V_{REFHI}$        | Ref High  | 2 × Bandgap                                     | 2.517           | 2.594                   | 2.650                   | V     |

|                 | Opamp bias = low                       | V <sub>AGND</sub>  | AGND      | Bandgap                                         | 1.255           | 1.300                   | 1.337                   | V     |

|                 |                                        | V <sub>REFLO</sub> | Ref Low   | V <sub>SS</sub>                                 | V <sub>SS</sub> | V <sub>SS</sub> + 0.003 | V <sub>SS</sub> + 0.015 | V     |

| 0b111           | RefPower = high                        | V <sub>REFHI</sub> | Ref High  | 3.2 × Bandgap                                   | 4.011           | 4.143                   | 4.203                   | V     |

|                 | Opamp bias = high                      | V <sub>AGND</sub>  | AGND      | 1.6 × Bandgap                                   | 2.020           | 2.075                   | 2.118                   | V     |

|                 |                                        | V <sub>REFLO</sub> | Ref Low   | V <sub>SS</sub>                                 | V <sub>SS</sub> | V <sub>SS</sub> + 0.011 | V <sub>SS</sub> + 0.026 | V     |

|                 | RefPower = high                        | V <sub>REFHI</sub> | Ref High  | 3.2 × Bandgap                                   | 4.022           | 4.138                   | 4.203                   | V     |

|                 | Opamp bias = low                       | $V_{AGND}$         | AGND      | 1.6 × Bandgap                                   | 2.023           | 2.075                   | 2.114                   | V     |

|                 |                                        | $V_{REFLO}$        | Ref Low   | V <sub>SS</sub>                                 | V <sub>SS</sub> | V <sub>SS</sub> + 0.006 | V <sub>SS</sub> + 0.017 | V     |

|                 | RefPower = medium                      | $V_{REFHI}$        | Ref High  | 3.2 × Bandgap                                   | 4.026           | 4.141                   | 4.207                   | V     |

|                 | Opamp bias = high                      | $V_{AGND}$         | AGND      | 1.6 × Bandgap                                   | 2.024           | 2.075                   | 2.114                   | V     |

|                 |                                        | $V_{REFLO}$        | Ref Low   | V <sub>SS</sub>                                 | V <sub>SS</sub> | V <sub>SS</sub> + 0.004 | V <sub>SS</sub> + 0.015 | V     |

|                 | RefPower = medium                      | V <sub>REFHI</sub> | Ref High  | 3.2 × Bandgap                                   | 4.030           | 4.143                   | 4.206                   | V     |

|                 | Opamp bias = low                       | $V_{AGND}$         | AGND      | 1.6 × Bandgap                                   | 2.024           | 2.076                   | 2.112                   | V     |

|                 |                                        | $V_{REFLO}$        | Ref Low   | V <sub>SS</sub>                                 | V <sub>SS</sub> | $V_{SS} + 0.003$        | V <sub>SS</sub> + 0.013 | V     |

Table 23. 3.3-V DC Analog Reference Specifications

| Reference<br>ARF_CR<br>[5:3] | Reference Power<br>Settings                | Symbol             | Reference | Description                                             | Min                        | Тур                        | Max                        | Units |

|------------------------------|--------------------------------------------|--------------------|-----------|---------------------------------------------------------|----------------------------|----------------------------|----------------------------|-------|

| 0b000                        | RefPower = high                            | V <sub>REFHI</sub> | Ref High  | V <sub>DD</sub> /2 + Bandgap                            | V <sub>DD</sub> /2 + 1.170 | V <sub>DD</sub> /2 + 1.288 | V <sub>DD</sub> /2 + 1.376 | V     |

|                              | Opamp bias = high                          | V <sub>AGND</sub>  | AGND      | V <sub>DD</sub> /2                                      | $V_{DD}/2 - 0.098$         | $V_{DD}/2 + 0.003$         | $V_{DD}/2 + 0.097$         | V     |

|                              |                                            | V <sub>REFLO</sub> | Ref Low   | V <sub>DD</sub> /2 – Bandgap                            | V <sub>DD</sub> /2 – 1.386 | V <sub>DD</sub> /2 – 1.287 | V <sub>DD</sub> /2 – 1.169 | V     |

|                              | RefPower = high                            | V <sub>REFHI</sub> | Ref High  | V <sub>DD</sub> /2 + Bandgap                            | V <sub>DD</sub> /2 + 1.210 | V <sub>DD</sub> /2 + 1.290 | V <sub>DD</sub> /2 + 1.355 | V     |

|                              | Opamp bias = low                           | V <sub>AGND</sub>  | AGND      | V <sub>DD</sub> /2                                      | $V_{DD}/2 - 0.055$         | V <sub>DD</sub> /2 + 0.001 | $V_{DD}/2 + 0.054$         | V     |

|                              |                                            | V <sub>REFLO</sub> | Ref Low   | V <sub>DD</sub> /2 – Bandgap                            | V <sub>DD</sub> /2 – 1.359 | V <sub>DD</sub> /2 – 1.292 | V <sub>DD</sub> /2 – 1.214 | V     |

|                              | RefPower = medium                          | $V_{REFHI}$        | Ref High  | V <sub>DD</sub> /2 + Bandgap                            | V <sub>DD</sub> /2 + 1.198 | V <sub>DD</sub> /2 + 1.292 | V <sub>DD</sub> /2 + 1.368 | V     |

|                              | Opamp bias = high                          | V <sub>AGND</sub>  | AGND      | V <sub>DD</sub> /2                                      | V <sub>DD</sub> /2 – 0.041 | V <sub>DD</sub> /2         | $V_{DD}/2 + 0.04$          | V     |

|                              |                                            | V <sub>REFLO</sub> | Ref Low   | V <sub>DD</sub> /2 – Bandgap                            | V <sub>DD</sub> /2 – 1.362 | V <sub>DD</sub> /2 – 1.295 | V <sub>DD</sub> /2 – 1.220 | V     |

|                              | RefPower = medium                          | $V_{REFHI}$        | Ref High  | V <sub>DD</sub> /2 + Bandgap                            | V <sub>DD</sub> /2 + 1.202 | V <sub>DD</sub> /2 + 1.292 | V <sub>DD</sub> /2 + 1.364 | V     |

|                              | Opamp bias = low                           | V <sub>AGND</sub>  | AGND      | V <sub>DD</sub> /2                                      | $V_{DD}/2 - 0.033$         | V <sub>DD</sub> /2         | $V_{DD}/2 + 0.030$         | V     |

|                              |                                            | $V_{REFLO}$        | Ref Low   | V <sub>DD</sub> /2 – Bandgap                            | V <sub>DD</sub> /2 – 1.364 | V <sub>DD</sub> /2 – 1.297 | V <sub>DD</sub> /2 – 1.222 | V     |

| 0b001                        | RefPower = high<br>Opamp bias = high       | $V_{REFHI}$        | Ref High  | P2[4]+P2[6] (P2[4] = V <sub>DD</sub> /2, P2[6] = 0.5 V) | P2[4] + P2[6]<br>- 0.072   | P2[4] + P2[6] - 0.017      | P2[4] + P2[6] +<br>0.041   | V     |

|                              |                                            | V <sub>AGND</sub>  | AGND      | P2[4]                                                   | P2[4]                      | P2[4]                      | P2[4]                      | -     |

|                              |                                            | V <sub>REFLO</sub> | Ref Low   | P2[4]–P2[6] (P2[4] = V <sub>DD</sub> /2, P2[6] = 0.5 V) | P2[4] – P2[6]<br>– 0.029   | P2[4]-P2[6]+<br>0.010      | P2[4]-P2[6]+<br>0.048      | V     |

|                              | RefPower = high<br>Opamp bias = low        | V <sub>REFHI</sub> | Ref High  | P2[4]+P2[6] (P2[4] = V <sub>DD</sub> /2, P2[6] = 0.5 V) | P2[4] + P2[6]<br>- 0.066   | P2[4] + P2[6] –<br>0.010   | P2[4] + P2[6] +<br>0.043   | V     |

|                              |                                            | V <sub>AGND</sub>  | AGND      | P2[4]                                                   | P2[4]                      | P2[4]                      | P2[4]                      | -     |

|                              |                                            | V <sub>REFLO</sub> | Ref Low   | P2[4]–P2[6] (P2[4] = V <sub>DD</sub> /2, P2[6] = 0.5 V) | P2[4] – P2[6]<br>– 0.024   | P2[4]-P2[6]+<br>0.004      | P2[4]-P2[6]+<br>0.034      | V     |

|                              | RefPower = medium<br>Opamp bias = high     | V <sub>REFHI</sub> | Ref High  | P2[4]+P2[6] (P2[4] = V <sub>DD</sub> /2, P2[6] = 0.5 V) | P2[4] + P2[6]<br>- 0.073   | P2[4] + P2[6] –<br>0.007   | P2[4] + P2[6] +<br>0.053   | V     |

|                              |                                            | V <sub>AGND</sub>  | AGND      | P2[4]                                                   | P2[4]                      | P2[4]                      | P2[4]                      | -     |

|                              |                                            | V <sub>REFLO</sub> | Ref Low   | P2[4]–P2[6] (P2[4] = V <sub>DD</sub> /2, P2[6] = 0.5 V) | P2[4] – P2[6]<br>– 0.028   | P2[4]-P2[6]+<br>0.002      | P2[4]-P2[6]+<br>0.033      | V     |

|                              | RefPower = medium<br>Opamp bias = low      | V <sub>REFHI</sub> | Ref High  | P2[4]+P2[6] (P2[4] = V <sub>DD</sub> /2, P2[6] = 0.5 V) | P2[4] + P2[6]<br>- 0.073   | P2[4] + P2[6] –<br>0.006   | P2[4] + P2[6] +<br>0.056   | V     |

|                              |                                            | $V_{AGND}$         | AGND      | P2[4]                                                   | P2[4]                      | P2[4]                      | P2[4]                      | _     |

|                              |                                            | $V_{REFLO}$        | Ref Low   | P2[4]–P2[6] (P2[4] = V <sub>DD</sub> /2, P2[6] = 0.5 V) | P2[4] – P2[6]<br>– 0.030   | P2[4] – P2[6]              | P2[4]-P2[6]+<br>0.032      | V     |

| 0b010                        | RefPower = high                            | V <sub>REFHI</sub> | Ref High  | $V_{DD}$                                                | V <sub>DD</sub> – 0.102    | V <sub>DD</sub> – 0.003    | $V_{DD}$                   | V     |

|                              | Opamp bias = high                          | V <sub>AGND</sub>  | AGND      | V <sub>DD</sub> /2                                      | V <sub>DD</sub> /2 – 0.040 | V <sub>DD</sub> /2 + 0.001 | $V_{DD}/2 + 0.039$         | V     |

|                              |                                            | V <sub>REFLO</sub> | Ref Low   | V <sub>SS</sub>                                         | V <sub>SS</sub>            | V <sub>SS</sub> + 0.005    | V <sub>SS</sub> + 0.020    | V     |

|                              | RefPower = high                            | V <sub>REFHI</sub> | Ref High  | $V_{DD}$                                                | V <sub>DD</sub> – 0.082    | V <sub>DD</sub> – 0.002    | $V_{DD}$                   | V     |

|                              | Opamp bias = Tow                           | V <sub>AGND</sub>  | AGND      | V <sub>DD</sub> /2                                      | $V_{DD}/2 - 0.031$         | V <sub>DD</sub> /2         | $V_{DD}/2 + 0.028$         | V     |

|                              |                                            | V <sub>REFLO</sub> | Ref Low   | V <sub>SS</sub>                                         | V <sub>SS</sub>            | V <sub>SS</sub> + 0.003    | V <sub>SS</sub> + 0.015    | V     |

|                              | RefPower = medium                          | $V_{REFHI}$        | Ref High  | $V_{DD}$                                                | V <sub>DD</sub> – 0.083    | V <sub>DD</sub> – 0.002    | $V_{DD}$                   | V     |

|                              | Opamp bias = high                          | V <sub>AGND</sub>  | AGND      | V <sub>DD</sub> /2                                      | $V_{DD}/2 - 0.032$         | V <sub>DD</sub> /2 – 0.001 | $V_{DD}/2 + 0.029$         | V     |

|                              |                                            | $V_{REFLO}$        | Ref Low   | V <sub>SS</sub>                                         | V <sub>SS</sub>            | V <sub>SS</sub> + 0.002    | V <sub>SS</sub> + 0.014    | V     |

|                              | RefPower = medium                          | $V_{REFHI}$        | Ref High  | $V_{DD}$                                                | V <sub>DD</sub> – 0.081    | V <sub>DD</sub> – 0.002    | $V_{DD}$                   | V     |

|                              | Opamp bias = low                           | $V_{AGND}$         | AGND      | V <sub>DD</sub> /2                                      | $V_{DD}/2 - 0.033$         | V <sub>DD</sub> /2 – 0.001 | V <sub>DD</sub> /2 + 0.029 | V     |

|                              |                                            | V <sub>REFLO</sub> | Ref Low   | V <sub>SS</sub>                                         | V <sub>SS</sub>            | V <sub>SS</sub> + 0.002    | V <sub>SS</sub> + 0.013    | V     |

| 0b011                        | All power settings<br>Not allowed at 3.3 V | -                  | -         | _                                                       | _                          | _                          | _                          | _     |

Table 23. 3.3-V DC Analog Reference Specifications (continued)

| Reference<br>ARF_CR<br>[5:3] | Reference Power<br>Settings                | Symbol             | Reference | Description                                     | Min             | Тур                     | Max                     | Units |

|------------------------------|--------------------------------------------|--------------------|-----------|-------------------------------------------------|-----------------|-------------------------|-------------------------|-------|

| 0b100                        | All power settings<br>Not allowed at 3.3 V | -                  | _         | _                                               | _               | _                       | _                       | _     |

| 0b101                        | RefPower = high<br>Opamp bias = high       | V <sub>REFHI</sub> | Ref High  | P2[4] + Bandgap<br>(P2[4] = V <sub>DD</sub> /2) | P2[4] + 1.211   | P2[4] + 1.285           | P2[4] + 1.348           | V     |

|                              |                                            | $V_{AGND}$         | AGND      | P2[4]                                           | P2[4]           | P2[4]                   | P2[4]                   | -     |

|                              |                                            | V <sub>REFLO</sub> | Ref Low   | P2[4] – Bandgap<br>(P2[4] = V <sub>DD</sub> /2) | P2[4] - 1.354   | P2[4] - 1.290           | P2[4] – 1.197           | V     |

|                              | RefPower = high<br>Opamp bias = low        | $V_{REFHI}$        | Ref High  | P2[4] + Bandgap<br>(P2[4] = V <sub>DD</sub> /2) | P2[4] + 1.209   | P2[4] + 1.289           | P2[4] + 1.353           | V     |

|                              |                                            | $V_{AGND}$         | AGND      | P2[4]                                           | P2[4]           | P2[4]                   | P2[4]                   | -     |

|                              |                                            | $V_{REFLO}$        | Ref Low   | P2[4] – Bandgap<br>(P2[4] = V <sub>DD</sub> /2) | P2[4] – 1.352   | P2[4] – 1.294           | P2[4] – 1.222           | V     |

|                              | RefPower = medium<br>Opamp bias = high     | V <sub>REFHI</sub> | Ref High  | P2[4] + Bandgap<br>(P2[4] = V <sub>DD</sub> /2) | P2[4] + 1.218   | P2[4] + 1.291           | P2[4] + 1.351           | V     |

|                              |                                            | $V_{AGND}$         | AGND      | P2[4]                                           | P2[4]           | P2[4]                   | P2[4]                   | -     |

|                              |                                            | V <sub>REFLO</sub> | Ref Low   | P2[4] – Bandgap<br>(P2[4] = V <sub>DD</sub> /2) | P2[4] - 1.351   | P2[4] - 1.296           | P2[4] - 1.224           | V     |

|                              | RefPower = medium<br>Opamp bias = low      | V <sub>REFHI</sub> | Ref High  | P2[4] + Bandgap<br>(P2[4] = V <sub>DD</sub> /2) | P2[4] + 1.215   | P2[4] + 1.292           | P2[4] + 1.354           | V     |

|                              |                                            | $V_{AGND}$         | AGND      | P2[4]                                           | P2[4]           | P2[4]                   | P2[4]                   | -     |

|                              |                                            | V <sub>REFLO</sub> | Ref Low   | P2[4] – Bandgap<br>(P2[4] = V <sub>DD</sub> /2) | P2[4] - 1.352   | P2[4] – 1.297           | P2[4] - 1.227           | V     |

| 0b110                        | RefPower = high                            | $V_{REFHI}$        | Ref High  | 2 × Bandgap                                     | 2.460           | 2.594                   | 2.695                   | ٧     |

|                              | Opamp bias = high                          | $V_{AGND}$         | AGND      | Bandgap                                         | 1.257           | 1.302                   | 1.335                   | V     |

|                              |                                            | $V_{REFLO}$        | Ref Low   | V <sub>SS</sub>                                 | V <sub>SS</sub> | V <sub>SS</sub> + 0.01  | V <sub>SS</sub> + 0.029 | V     |

|                              | RefPower = high<br>Opamp bias = low        | $V_{REFHI}$        | Ref High  | 2 × Bandgap                                     | 2.462           | 2.592                   | 2.692                   | V     |

|                              | Opamp bias = low                           | $V_{AGND}$         | AGND      | Bandgap                                         | 1.256           | 1.301                   | 1.332                   | V     |

|                              |                                            | $V_{REFLO}$        | Ref Low   | V <sub>SS</sub>                                 | $V_{SS}$        | $V_{SS} + 0.005$        | V <sub>SS</sub> + 0.017 | V     |

|                              | RefPower = medium                          | $V_{REFHI}$        | Ref High  | 2 × Bandgap                                     | 2.473           | 2.593                   | 2.682                   | V     |

|                              | Opamp bias = high                          | $V_{AGND}$         | AGND      | Bandgap                                         | 1.257           | 1.301                   | 1.330                   | V     |

|                              |                                            | $V_{REFLO}$        | Ref Low   | V <sub>SS</sub>                                 | V <sub>SS</sub> | $V_{SS} + 0.003$        | V <sub>SS</sub> + 0.014 | V     |

|                              | RefPower = medium<br>Opamp bias = low      | $V_{REFHI}$        | Ref High  | 2 × Bandgap                                     | 2.470           | 2.594                   | 2.685                   | V     |

|                              |                                            | $V_{AGND}$         | AGND      | Bandgap                                         | 1.256           | 1.300                   | 1.332                   | V     |

|                              |                                            | $V_{REFLO}$        | Ref Low   | V <sub>SS</sub>                                 | V <sub>SS</sub> | V <sub>SS</sub> + 0.002 | V <sub>SS</sub> + 0.012 | V     |

| 0b111                        | All power settings<br>Not allowed at 3.3 V | -                  | _         | _                                               | _               | _                       | _                       | _     |

## AC Operational Amplifier Specifications

The following tables list the guaranteed maximum and minimum specifications for the voltage and temperature ranges: 4.75 V to 5.25 V and –40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C, 3.0 V to 3.6 V and –40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C, or 2.4 V to 3.0 V and –40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C, respectively. Typical parameters are measured at 5 V, 3.3 V, and 2.7 V at 25 °C and are for design guidance only.

Settling times, slew rates, and gain bandwidth are based on the analog continuous time PSoC block.

Power = high and Opamp bias = high is not supported at 3.3 V and 2.7 V.

Table 33. 5-V AC Operational Amplifier Specifications

| Symbol            | Description                                                                                                                                                                                         | Min                | Тур         | Max                 | Units                |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-------------|---------------------|----------------------|

| t <sub>ROA</sub>  | Rising settling time from 80% of $\Delta V$ to 0.1% of $\Delta V$ (10 pF load, unity gain)<br>Power = low, Opamp bias = low<br>Power = medium, Opamp bias = high<br>Power = high, Opamp bias = high | -<br>-<br>-        | _<br>_<br>_ | 3.9<br>0.72<br>0.62 | μs<br>μs<br>μs       |

| t <sub>SOA</sub>  | Falling settling time from 20% of $\Delta V$ to 0.1% of $\Delta V$ (10 pF load, unity gain) Power = low, Opamp bias = low Power = medium, Opamp bias = high Power = high, Opamp bias = high         | -<br>-<br>-        | _<br>_<br>_ | 5.9<br>0.92<br>0.72 | μs<br>μs<br>μs       |

| SR <sub>ROA</sub> | Rising slew rate (20% to 80%) (10 pF load, unity gain) Power = low, Opamp bias = low Power = medium, Opamp bias = high Power = high, Opamp bias = high                                              | 0.15<br>1.7<br>6.5 | -<br>-<br>- | -<br>-<br>-         | V/μs<br>V/μs<br>V/μs |

| SR <sub>FOA</sub> | Falling slew rate (20% to 80%) (10 pF load, unity gain) Power = low, Opamp bias = low Power = medium, Opamp bias = high Power = high, Opamp bias = high                                             | 0.01<br>0.5<br>4.0 | -<br>-<br>- | -<br>-<br>-         | V/μs<br>V/μs<br>V/μs |

| BW <sub>OA</sub>  | Gain bandwidth product Power = low, Opamp bias = low Power = medium, Opamp bias = high Power = high, Opamp bias = high                                                                              | 0.75<br>3.1<br>5.4 | _<br>_<br>_ | -<br>-<br>-         | MHz<br>MHz<br>MHz    |

| E <sub>NOA</sub>  | Noise at 1 kHz (Power = medium, Opamp bias = high)                                                                                                                                                  | _                  | 100         | _                   | nV/rt-Hz             |

Table 34. 3.3-V AC Operational Amplifier Specifications

| Symbol            | Description                                                                                                                                                       | Min         | Тур    | Max          | Units        |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--------|--------------|--------------|

| t <sub>ROA</sub>  | Rising settling time from 80% of $\Delta V$ to 0.1% of $\Delta V$ (10 pF load, unity gain)<br>Power = low, Opamp bias = low<br>Power = medium, Opamp bias = high  |             | -<br>- | 3.92<br>0.72 | μs<br>μs     |

| t <sub>SOA</sub>  | Falling settling time from 20% of $\Delta V$ to 0.1% of $\Delta V$ (10 pF load, unity gain)<br>Power = low, Opamp bias = low<br>Power = medium, Opamp bias = high |             |        | 5.41<br>0.72 | μs<br>μs     |

| SR <sub>ROA</sub> | Rising slew rate (20% to 80%) (10 pF load, unity gain) Power = low, Opamp bias = low Power = medium, Opamp bias = high                                            | 0.31<br>2.7 | _<br>_ | <u>-</u>     | V/µs<br>V/µs |

| SR <sub>FOA</sub> | Falling slew rate (20% to 80%) (10 pF load, unity gain) Power = low, Opamp bias = low Power = medium, Opamp bias = high                                           | 0.24<br>1.8 | _<br>_ | _<br>_       | V/µs<br>V/µs |

| BW <sub>OA</sub>  | Gain bandwidth product Power = low, Opamp bias = low Power = medium, Opamp bias = high                                                                            | 0.67<br>2.8 | _<br>_ | _<br>_       | MHz<br>MHz   |

| E <sub>NOA</sub>  | Noise at 1 kHz (Power = medium, Opamp bias = high)                                                                                                                | -           | 100    | -            | nV/rt-Hz     |

Table 41. 2.7-V AC Analog Output Buffer Specifications

| Symbol            | Description                                                                                      | Min        | Тур      | Max           | Units        |

|-------------------|--------------------------------------------------------------------------------------------------|------------|----------|---------------|--------------|

| t <sub>ROB</sub>  | Rising settling time to 0.1%, 1 V Step, 100 pF load<br>Power = low<br>Power = high               |            | _<br>_   | 4<br>4        | μs<br>μs     |

| t <sub>SOB</sub>  | Falling settling time to 0.1%, 1 V Step, 100 pF load Power = low Power = high                    | _<br>_     | _<br>_   | 3<br>3        | μs<br>μs     |

| SR <sub>ROB</sub> | Rising slew rate (20% to 80%), 1 V Step, 100 pF load<br>Power = low<br>Power = high              | 0.4<br>0.4 | <u>-</u> | <u>-</u><br>- | V/µs<br>V/µs |

| SR <sub>FOB</sub> | Falling slew rate (80% to 20%), 1 V Step, 100 pF load<br>Power = low<br>Power = high             | 0.4<br>0.4 | _<br>_   | _<br>_<br>_   | V/µs<br>V/µs |

| BW <sub>OB</sub>  | Small signal bandwidth, 20 mV <sub>pp</sub> , 3dB BW, 100 pF load<br>Power = low<br>Power = high | 0.6<br>0.6 | _<br>_   | _<br>_<br>_   | MHz<br>MHz   |

| BW <sub>OB</sub>  | Large signal bandwidth, 1 V <sub>pp</sub> , 3dB BW, 100 pF load<br>Power = low<br>Power = high   | 180<br>180 | <u>-</u> | <u>-</u><br>- | kHz<br>kHz   |

## AC External Clock Specifications

The following tables list the guaranteed maximum and minimum specifications for the voltage and temperature ranges: 4.75 V to 5.25 V and  $-40~^{\circ}\text{C} \le T_A \le 85~^{\circ}\text{C}$ , 3.0 V to 3.6 V and  $-40~^{\circ}\text{C} \le T_A \le 85~^{\circ}\text{C}$ , or 2.4 V to 3.0 V and  $-40~^{\circ}\text{C} \le T_A \le 85~^{\circ}\text{C}$ , respectively. Typical parameters are measured at 5 V, 3.3 V, and 2.7 V at 25  $^{\circ}\text{C}$  and are for design guidance only.

Table 42. 5-V AC External Clock Specifications

| Symbol              | Description            | Min   | Тур | Max  | Units |

|---------------------|------------------------|-------|-----|------|-------|

| F <sub>OSCEXT</sub> | Frequency              | 0.093 | _   | 24.6 | MHz   |

| _                   | High period            | 20.6  | _   | 5300 | ns    |

| _                   | Low period             | 20.6  | _   | _    | ns    |

| _                   | Power-up IMO to switch | 150   | _   | _    | μS    |

## Table 43. 3.3-V AC External Clock Specifications

| Symbol              | Description                                                     | Min   | Тур | Max  | Units |

|---------------------|-----------------------------------------------------------------|-------|-----|------|-------|

| F <sub>OSCEXT</sub> | Frequency with CPU clock divide by 1 <sup>[32]</sup>            | 0.093 | _   | 12.3 | MHz   |

| F <sub>OSCEXT</sub> | Frequency with CPU clock divide by 2 or greater <sup>[33]</sup> | 0.186 | _   | 24.6 | MHz   |

| _                   | High period with CPU clock divide by 1                          | 41.7  | _   | 5300 | ns    |

| _                   | Low period with CPU clock divide by 1                           | 41.7  | _   | _    | ns    |

| _                   | Power-up IMO to switch                                          | 150   | ı   | _    | μS    |

#### Notes

Document Number: 38-12028 Rev. \*V Page 48 of 71

<sup>32.</sup> Maximum CPU frequency is 12 MHz at 3.3 V. With the CPU clock divider set to 1, the external clock must adhere to the maximum frequency and duty cycle requirements.

<sup>33.</sup> If the frequency of the external clock is greater than 12 MHz, the CPU clock divider must be set to 2 or greater. In this case, the CPU clock divider ensures that the fifty percent duty cycle requirement is met

Table 44. 2.7-V AC External Clock Specifications

| Symbol              | Description                                                     | Min   | Тур | Max  | Units | Notes |

|---------------------|-----------------------------------------------------------------|-------|-----|------|-------|-------|

| F <sub>OSCEXT</sub> | Frequency with CPU clock divide by 1 <sup>[34]</sup>            | 0.093 | _   | 12.3 | MHz   |       |

| F <sub>OSCEXT</sub> | Frequency with CPU clock divide by 2 or greater <sup>[35]</sup> | 0.186 | _   | 12.3 | MHz   |       |

| _                   | High period with CPU clock divide by 1                          | 41.7  | _   | 5300 | ns    |       |

| _                   | Low period with CPU clock divide by 1                           | 41.7  | -   | -    | ns    |       |

| _                   | Power-up IMO to switch                                          | 150   | _   | -    | μs    |       |

#### AC Programming Specifications

Table 45 lists the guaranteed maximum and minimum specifications for the voltage and temperature ranges: 4.75 V to 5.25 V and  $-40~^{\circ}\text{C} \le T_{A} \le 85~^{\circ}\text{C}$ , 3.0 V to 3.6 V and  $-40~^{\circ}\text{C} \le T_{A} \le 85~^{\circ}\text{C}$ , or 2.4 V to 3.0 V and  $-40~^{\circ}\text{C} \le T_{A} \le 85~^{\circ}\text{C}$ , respectively. Typical parameters are measured at 5 V, 3.3 V, and 2.7 V at 25  $^{\circ}\text{C}$  and are for design guidance only.

**Table 45. AC Programming Specifications**

| Symbol                    | Description                                | Min | Тур | Max                 | Units | Notes                                                         |

|---------------------------|--------------------------------------------|-----|-----|---------------------|-------|---------------------------------------------------------------|

| t <sub>RSCLK</sub>        | Rise time of SCLK                          | 1   | _   | 20                  | ns    |                                                               |

| t <sub>FSCLK</sub>        | Fall time of SCLK                          | 1   | _   | 20                  | ns    |                                                               |

| t <sub>SSCLK</sub>        | Data setup time to falling edge of SCLK    | 40  | _   | _                   | ns    |                                                               |

| t <sub>HSCLK</sub>        | Data hold time from falling edge of SCLK   | 40  | _   | -                   | ns    |                                                               |

| F <sub>SCLK</sub>         | Frequency of SCLK                          | 0   | _   | 8                   | MHz   |                                                               |

| t <sub>ERASEB</sub>       | Flash erase time (block)                   | _   | 20  | _                   | ms    |                                                               |

| t <sub>WRITE</sub>        | Flash block write time                     | _   | 80  | -                   | ms    |                                                               |

| t <sub>DSCLK</sub>        | Data out delay from falling edge of SCLK   | _   | _   | 45                  | ns    | V <sub>DD</sub> > 3.6                                         |

| t <sub>DSCLK3</sub>       | Data out delay from falling edge of SCLK   | _   | _   | 50                  | ns    | $3.0 \leq V_{DD} \leq 3.6$                                    |

| t <sub>DSCLK2</sub>       | Data out delay from falling edge of SCLK   | _   | _   | 70                  | ns    | $2.4 \leq V_{DD} \leq 3.0$                                    |

| t <sub>ERASEALL</sub>     | Flash erase time (Bulk)                    | _   | 20  | _                   | ms    | Erase all blocks and protection fields at once                |

| t <sub>PROGRAM_HOT</sub>  | Flash block erase + flash block write time | _   | _   | 200 <sup>[36]</sup> | ms    | 0 °C ≤ Tj ≤ 100 °C                                            |

| t <sub>PROGRAM_COLD</sub> | Flash block erase + flash block write time | _   | _   | 400 <sup>[36]</sup> | ms    | $-40  ^{\circ}\text{C} \le \text{Tj} \le 0  ^{\circ}\text{C}$ |

#### Notes

<sup>34.</sup> Maximum CPU frequency is 12 MHz at 3.3 V. With the CPU clock divider set to 1, the external clock must adhere to the maximum frequency and duty cycle requirements.

<sup>35.</sup> If the frequency of the external clock is greater than 12 MHz, the CPU clock divider must be set to 2 or greater. In this case, the CPU clock divider ensures that the fifty percent duty cycle requirement is met.