Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                      |

| Core Processor             | M8C                                                                           |

| Core Size                  | 8-Bit                                                                         |

| Speed                      | 24MHz                                                                         |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                             |

| Peripherals                | POR, PWM, WDT                                                                 |

| Number of I/O              | 16                                                                            |

| Program Memory Size        | 4KB (4K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | -                                                                             |

| RAM Size                   | 256 x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 2.4V ~ 5.25V                                                                  |

| Data Converters            | A/D 8x14b; D/A 2x9b                                                           |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                                                |

| Supplier Device Package    | 20-SSOP                                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/cy8c24223a4-24pvxi |

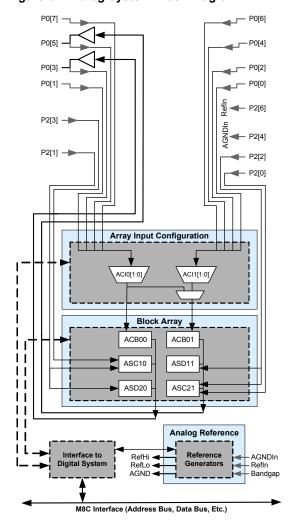

## **Analog System**

The analog system consists of six configurable blocks, each consisting of an opamp circuit that allows the creation of complex analog signal flows. Analog peripherals are very flexible and can be customized to support specific application requirements. Some of the more common PSoC analog functions (most available as user modules) are:

- ADCs (up to two, with 6- to 14-bit resolution, selectable as incremental, delta sigma, and SAR)

- Filters (two and four pole band-pass, low-pass, and notch)

- Amplifiers (up to two, with selectable gain to 48x)

- Instrumentation amplifiers (one with selectable gain to 93x)

- Comparators (up to two, with 16 selectable thresholds)

- DACs (up to two, with 6 to 9-bit resolution)

- Multiplying DACs (up to two, with 6 to 9-bit resolution)

- High current output drivers (two with 30 mA drive as a PSoC Core resource)

- 1.3 V reference (as a system resource)

- DTMF dialer

- Modulators

- Correlators

- Peak detectors

- Many other topologies possible

Analog blocks are arranged in a column of three, which includes one continuous time (CT) and two switched capacitor (SC) blocks, as shown in Figure 3

Figure 3. Analog System Block Diagram

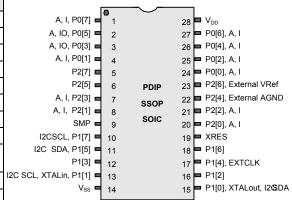

## 28-Pin Part Pinout

Table 4. 28-Pin PDIP, SSOP, and SOIC

| Pin | Ту      | pe     | Pin      | Description                                              |

|-----|---------|--------|----------|----------------------------------------------------------|

| No. | Digital | Analog | Name     | Description                                              |

| 1   | I/O     | I      | P0[7]    | Analog column mux input                                  |

| 2   | I/O     | I/O    | P0[5]    | Analog column mux input and column output                |

| 3   | I/O     | I/O    | P0[3]    | Analog column mux input and column output                |

| 4   | I/O     | I      | P0[1]    | Analog column mux input                                  |

| 5   | I/O     |        | P2[7]    |                                                          |

| 6   | I/O     |        | P2[5]    |                                                          |

| 7   | I/O     | I      | P2[3]    | Direct switched capacitor block input                    |

| 8   | I/O     | I      | P2[1]    | Direct switched capacitor block input                    |

| 9   | Po      | wer    | SMP      | SMP connection to external components required           |

| 10  | I/O     |        | P1[7]    | I <sup>2</sup> C SCL                                     |

| 11  | I/O     |        | P1[5]    | I <sup>2</sup> C SDA                                     |

| 12  | I/O     |        | P1[3]    |                                                          |

| 13  | I/O     |        | P1[1]    | XTALin, I <sup>2</sup> C SCL, ISSP-SCLK <sup>[6]</sup>   |

| 14  | Po      | wer    | $V_{SS}$ | Ground connection.                                       |

| 15  | I/O     |        | P1[0]    | XTALout, I <sup>2</sup> C SDA, ISSP-SDATA <sup>[6]</sup> |

| 16  | I/O     |        | P1[2]    |                                                          |

| 17  | I/O     |        | P1[4]    | Optional EXTCLK                                          |

| 18  | I/O     |        | P1[6]    |                                                          |

| 19  | Inp     | out    | XRES     | Active high external reset with internal pull-down       |

| 20  | I/O     | I      | P2[0]    | Direct switched capacitor block input                    |

| 21  | I/O     | I      | P2[2]    | Direct switched capacitor block input                    |

| 22  | I/O     |        | P2[4]    | External analog ground (AGND)                            |

| 23  | I/O     |        | P2[6]    | External voltage reference (V <sub>REF</sub> )           |

| 24  | 1/0     | I      | P0[0]    | Analog column mux input                                  |

| 25  | I/O     | I      | P0[2]    | Analog column mux input                                  |

| 26  | I/O     | I      | P0[4]    | Analog column mux input                                  |

| 27  | I/O     | I      | P0[6]    | Analog column mux input                                  |

| 28  | Po      | wer    | $V_{DD}$ | Supply voltage                                           |

Figure 6. CY8C24423A 28-Pin PSoC Device

**Not for Production**

LEGEND : A = Analog, I = Input, and O = Output.

## Note

<sup>6.</sup> These are the ISSP pins, which are not high Z at POR. See the PSoC Technical Reference Manual for details.

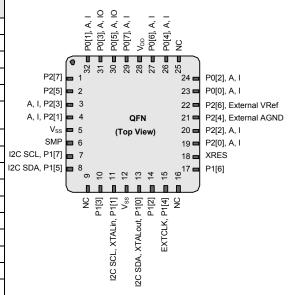

## 32-Pin Part Pinout

Table 5. 32-Pin QFN<sup>[7]</sup>

| Table 5. 52-Fill Qi N- |               |              |                 |                                                          |  |  |  |  |

|------------------------|---------------|--------------|-----------------|----------------------------------------------------------|--|--|--|--|

| Pin No.                | Ty<br>Digital | pe<br>Analog | Pin<br>Name     | Description                                              |  |  |  |  |

| 1                      | I/O           | Allalog      | P2[7]           |                                                          |  |  |  |  |

| 2                      | I/O           |              | P2[5]           |                                                          |  |  |  |  |

| 3                      | I/O           | ı            | P2[3]           | Direct switched capacitor block input                    |  |  |  |  |

| 4                      | 1/0           | ı            | P2[1]           | Direct switched capacitor block input                    |  |  |  |  |

| 5                      | _             | wer          |                 | Ground connection                                        |  |  |  |  |

| 6                      |               | wer          | V <sub>SS</sub> | SMP connection to external components                    |  |  |  |  |

| 0                      | FU            | wei          | 0               | required                                                 |  |  |  |  |

| 7                      | I/O           |              | P1[7]           | I <sup>2</sup> C SCL                                     |  |  |  |  |

| 8                      | I/O           |              | P1[5]           | I <sup>2</sup> C SDA                                     |  |  |  |  |

| 9                      |               |              | NC              | No connection. Pin must be left floating                 |  |  |  |  |

| 10                     | I/O           |              | P1[3]           |                                                          |  |  |  |  |

| 11                     | I/O           |              | P1[1]           | XTALin, I <sup>2</sup> C SCL, ISSP-SCLK <sup>[8]</sup>   |  |  |  |  |

| 12                     | Po            | wer          | $V_{SS}$        | Ground Connection                                        |  |  |  |  |

| 13                     | I/O           |              | P1[0]           | XTALout, I <sup>2</sup> C SDA, ISSP-SDATA <sup>[8]</sup> |  |  |  |  |

| 14                     | I/O           |              | P1[2]           |                                                          |  |  |  |  |

| 15                     | I/O           |              | P1[4]           | Optional EXTCLK                                          |  |  |  |  |

| 16                     |               |              | NC              | No connection. Pin must be left floating                 |  |  |  |  |

| 17                     | I/O           |              | P1[6]           |                                                          |  |  |  |  |

| 18                     | In            | put          | XRES            | Active high external reset with internal pull-down       |  |  |  |  |

| 19                     | I/O           | I            | P2[0]           | Direct switched capacitor block input                    |  |  |  |  |

| 20                     | I/O           | I            | P2[2]           | Direct switched capacitor block input                    |  |  |  |  |

| 21                     | I/O           |              | P2[4]           | External AGND                                            |  |  |  |  |

| 22                     | I/O           |              | P2[6]           | External V <sub>REF</sub>                                |  |  |  |  |

| 23                     | I/O           | I            | P0[0]           | Analog column mux input                                  |  |  |  |  |

| 24                     | I/O           | I            | P0[2]           | Analog column mux input                                  |  |  |  |  |

| 25                     |               |              | NC              | No connection. Pin must be left floating                 |  |  |  |  |

| 26                     | I/O           | I            | P0[4]           | Analog column mux input                                  |  |  |  |  |

| 27                     | I/O           | I            | P0[6]           | Analog column mux input                                  |  |  |  |  |

| 28                     | Po            | wer          | $V_{DD}$        | Supply voltage                                           |  |  |  |  |

| 29                     | I/O           | I            | P0[7]           | Analog column mux input                                  |  |  |  |  |

| 30                     | I/O           | I/O          | P0[5]           | Analog column mux input and column output                |  |  |  |  |

| 31                     | I/O           | I/O          | P0[3]           | Analog column mux input and column output                |  |  |  |  |

| 32                     | I/O           | I            | P0[1]           | Analog column mux input                                  |  |  |  |  |

|                        |               |              |                 |                                                          |  |  |  |  |

Figure 7. CY8C24423A 32-Pin PSoC Device

**LEGEND**: A = Analog, I = Input, and O = Output.

The center pad on the QFN package must be connected to ground (V<sub>SS</sub>) for best mechanical, thermal, and electrical performance. If not connected to ground, it must be electrically floated and not connected to any other signal.

These are the ISSP pins, which are not high Z at POR. See the PSoC Technical Reference Manual for details.

## **Register Reference**

This section lists the registers of the CY8C24x23A PSoC device. For detailed register information, see the PSoC Programmable Sytem-on-Chip Reference Manual.

## **Register Conventions**

Abbreviations Used

The register conventions specific to this section are listed in the following table.

Table 7. Abbreviations

| Convention | Description                  |

|------------|------------------------------|

| R          | Read register or bit(s)      |

| W          | Write register or bit(s)     |

| L          | Logical register or bit(s)   |

| С          | Clearable register or bit(s) |

| #          | Access is bit specific       |

## **Register Mapping Tables**

The PSoC device has a total register address space of 512 bytes. The register space is referred to as I/O space and is divided into two banks, Bank 0 and Bank 1. The XOI bit in the Flag register (CPU\_F) determines which bank the user is currently in. When the XOI bit is set, the user is in Bank 1.

**Note** In the following register mapping tables, blank fields are reserved and must not be accessed.

## DC Operational Amplifier Specifications

The following tables list the guaranteed maximum and minimum specifications for the voltage and temperature ranges: 4.75 V to 5.25 V and –40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C, 3.0 V to 3.6 V and –40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C, or 2.4 V to 3.0 V and –40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C, respectively. Typical parameters are measured at 5 V, 3.3 V, and 2.7 V at 25 °C and are for design guidance only.

The operational amplifier is a component of both the analog continuous time PSoC blocks and the Analog Switched Cap PSoC blocks. The guaranteed specifications are measured in the analog continuous time PSoC block. Typical parameters are measured at 5 V at 25 °C and are for design guidance only.

Table 14. 5-V DC Operational Amplifier Specifications

| Symbol               | Description                                                                                                                                                                                                                                      | Min                                                                     | Тур                                       | Max                                       | Units                                          | Notes                                                                                                                                                                                   |

|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|-------------------------------------------|-------------------------------------------|------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>OSOA</sub>    | Input offset voltage (absolute value) Power = low, Opamp bias = high Power = medium, Opamp bias = high Power = high, Opamp bias = high                                                                                                           | -<br>-<br>-                                                             | 1.6<br>1.3<br>1.2                         | 10<br>8<br>7.5                            | mV<br>mV<br>mV                                 |                                                                                                                                                                                         |

| TCV <sub>OSOA</sub>  | Average input offset voltage drift                                                                                                                                                                                                               | _                                                                       | 7.0                                       | 35.0                                      | μV/°C                                          |                                                                                                                                                                                         |

| I <sub>EBOA</sub>    | Input leakage current (port 0 analog pins)                                                                                                                                                                                                       | _                                                                       | 20                                        | _                                         | pА                                             | Gross tested to 1 µA                                                                                                                                                                    |

| C <sub>INOA</sub>    | Input capacitance (port 0 analog pins)                                                                                                                                                                                                           | -                                                                       | 4.5                                       | 9.5                                       | pF                                             | Package and pin dependent.<br>Temp = 25 °C                                                                                                                                              |

| V <sub>CMOA</sub>    | Common mode voltage range<br>Common mode voltage range (high power or high<br>Opamp bias)                                                                                                                                                        | 0.0<br>0.5                                                              | 1                                         | V <sub>DD</sub><br>V <sub>DD</sub> – 0.5  | V                                              | The common mode input voltage range is measured through an analog output buffer. The specification includes the limitations imposed by the characteristics of the analog output buffer. |

| G <sub>OLOA</sub>    | Open loop gain Power = low, Opamp bias = high Power = medium, Opamp bias = high Power = high, Opamp bias = high                                                                                                                                  | 60<br>60<br>80                                                          | _<br>_<br>_                               | -<br>-<br>-                               | dB<br>dB<br>dB                                 | Specification is applicable at high<br>Opamp bias. For low Opamp bias<br>mode, minimum is 60 dB.                                                                                        |

| V <sub>OHIGHOA</sub> | High output voltage swing (internal signals) Power = low, Opamp bias = high Power = medium, Opamp bias = high Power = high, Opamp bias = high                                                                                                    | V <sub>DD</sub> - 0.2<br>V <sub>DD</sub> - 0.2<br>V <sub>DD</sub> - 0.5 | -<br>-<br>-                               | -<br>-<br>-                               | V<br>V<br>V                                    |                                                                                                                                                                                         |

| V <sub>OLOWOA</sub>  | Low output voltage swing (internal signals) Power = low, Opamp bias = high Power = medium, Opamp bias = high Power = high, Opamp bias = high                                                                                                     | -<br>-<br>-                                                             | 111                                       | 0.2<br>0.2<br>0.5                         | V<br>V<br>V                                    |                                                                                                                                                                                         |

| I <sub>SOA</sub>     | Supply current (including associated AGND buffer) Power = low, Opamp bias = low Power = low, Opamp bias = high Power = medium, Opamp bias = low Power = medium, Opamp bias = high Power = high, Opamp bias = low Power = high, Opamp bias = high | -<br>-<br>-<br>-<br>-                                                   | 150<br>300<br>600<br>1200<br>2400<br>4600 | 200<br>400<br>800<br>1600<br>3200<br>6400 | 4<br>4<br>4<br>4<br>4<br>4<br>4<br>4<br>4<br>4 |                                                                                                                                                                                         |

| PSRR <sub>OA</sub>   | Supply voltage rejection ratio                                                                                                                                                                                                                   | 64                                                                      | 80                                        | _                                         | dB                                             | $V_{SS} \le V_{IN} \le (V_{DD} - 2.25)$ or $(V_{DD} - 1.25 \ V) \le V_{IN} \le V_{DD}$                                                                                                  |

## DC Analog Output Buffer Specifications

The following tables list the guaranteed maximum and minimum specifications for the voltage and temperature ranges: 4.75 V to 5.25 V and –40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C, 3.0 V to 3.6 V and –40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C, or 2.4 V to 3.0 V and –40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C, respectively. Typical parameters are measured at 5 V, 3.3 V, and 2.7 V at 25 °C and are for design guidance only.

Table 18. 5-V DC Analog Output Buffer Specifications

| Symbol               | Description                                                                                       | Min                                                        | Тур        | Max                                                       | Units    | Notes                                                                                                |

|----------------------|---------------------------------------------------------------------------------------------------|------------------------------------------------------------|------------|-----------------------------------------------------------|----------|------------------------------------------------------------------------------------------------------|

| C <sub>L</sub>       | Load Capacitance                                                                                  | -                                                          | _          | 200                                                       | pF       | This specification applies to the external circuit that is being driven by the analog output buffer. |

| V <sub>OSOB</sub>    | Input offset voltage (absolute value)                                                             | -                                                          | 3          | 12                                                        | mV       |                                                                                                      |

| TCV <sub>OSOB</sub>  | Average input offset voltage drift                                                                | -                                                          | +6         | _                                                         | μV/°C    |                                                                                                      |

| V <sub>CMOB</sub>    | Common mode input voltage range                                                                   | 0.5                                                        | -          | V <sub>DD</sub> – 1.0                                     | V        |                                                                                                      |

| R <sub>OUTOB</sub>   | Output resistance<br>Power = low<br>Power = high                                                  | _<br>_                                                     | 1          | _<br>_                                                    | W<br>W   |                                                                                                      |

| V <sub>OHIGHOB</sub> | High output voltage swing (Load = 32 ohms to V <sub>DD/2</sub> ) Power = low Power = high         | 0.5 × V <sub>DD</sub> + 1.1<br>0.5 × V <sub>DD</sub> + 1.1 | _<br>_     | _<br>_                                                    | V        |                                                                                                      |

| V <sub>OLOWOB</sub>  | Low output voltage swing<br>(Load = 32 ohms to V <sub>DD/2</sub> )<br>Power = low<br>Power = high | -<br>-                                                     | _<br>_     | .5 × V <sub>DD</sub> – 1.3<br>0.5 × V <sub>DD</sub> – 1.3 | V        |                                                                                                      |

| I <sub>SOB</sub>     | Supply current including Opamp bias cell (No Load) Power = low Power = high                       | -<br>-                                                     | 1.1<br>2.6 | 5.1<br>8.8                                                | mA<br>mA |                                                                                                      |

| PSRR <sub>OB</sub>   | Supply voltage rejection ratio                                                                    | 52                                                         | 64         | _                                                         | dB       | $V_{OUT} > (V_{DD} - 1.25)$                                                                          |

Table 19. 3.3-V DC Analog Output Buffer Specifications

| Symbol               | Description                                                                                | Min                                                        | Тур        | Max                                                        | Units    | Notes                                                                                                |

|----------------------|--------------------------------------------------------------------------------------------|------------------------------------------------------------|------------|------------------------------------------------------------|----------|------------------------------------------------------------------------------------------------------|

| C <sub>L</sub>       | Load Capacitance                                                                           | -                                                          | -          | 200                                                        | pF       | This specification applies to the external circuit that is being driven by the analog output buffer. |

| V <sub>OSOB</sub>    | Input offset voltage (absolute value)                                                      | _                                                          | 3          | 12                                                         | mV       |                                                                                                      |

| TCV <sub>OSOB</sub>  | Average input offset voltage drift                                                         | _                                                          | +6         | _                                                          | μV/°C    |                                                                                                      |

| $V_{CMOB}$           | Common mode input voltage range                                                            | 0.5                                                        | -          | V <sub>DD</sub> – 1.0                                      | V        |                                                                                                      |

| R <sub>OUTOB</sub>   | Output resistance<br>Power = low<br>Power = high                                           |                                                            | 1          | _<br>_                                                     | Ω        |                                                                                                      |

| V <sub>OHIGHOB</sub> | High output voltage swing (Load = 1 K ohms to V <sub>DD/2</sub> ) Power = low Power = high | 0.5 × V <sub>DD</sub> + 1.0<br>0.5 × V <sub>DD</sub> + 1.0 | _<br>_     | -<br>-                                                     | V        |                                                                                                      |

| V <sub>OLOWOB</sub>  | Low output voltage swing (Load = 1 K ohms to V <sub>DD/2</sub> ) Power = low Power = high  | -<br>-                                                     | _<br>_     | 0.5 × V <sub>DD</sub> – 1.0<br>0.5 × V <sub>DD</sub> – 1.0 | V        |                                                                                                      |

| I <sub>SOB</sub>     | Supply current including Opamp bias cell (no load) Power = low Power = high                |                                                            | 0.8<br>2.0 | 2.0<br>4.3                                                 | mA<br>mA |                                                                                                      |

| PSRR <sub>OB</sub>   | Supply voltage rejection ratio                                                             | 52                                                         | 64         | _                                                          | dB       | V <sub>OUT</sub> > (V <sub>DD</sub> – 1.25)                                                          |

Table 22. 5-V DC Analog Reference Specifications (continued)

| Reference<br>ARF_CR<br>[5:3] | Reference Power<br>Settings            | Symbol             | Reference | Description                            | Min                        | Тур                        | Max                        | Units |

|------------------------------|----------------------------------------|--------------------|-----------|----------------------------------------|----------------------------|----------------------------|----------------------------|-------|

| 0b010                        | RefPower = high                        | V <sub>REFHI</sub> | Ref High  | $V_{DD}$                               | V <sub>DD</sub> – 0.121    | V <sub>DD</sub> – 0.003    | V <sub>DD</sub>            | V     |

|                              | Opamp bias = high                      | $V_{AGND}$         | AGND      | V <sub>DD</sub> /2                     | V <sub>DD</sub> /2 – 0.040 | V <sub>DD</sub> /2         | $V_{DD}/2 + 0.034$         | V     |

|                              |                                        | $V_{REFLO}$        | Ref Low   | V <sub>SS</sub>                        | V <sub>SS</sub>            | V <sub>SS</sub> + 0.006    | V <sub>SS</sub> + 0.019    | V     |

|                              | RefPower = high                        | $V_{REFHI}$        | Ref High  | $V_{DD}$                               | V <sub>DD</sub> – 0.083    | V <sub>DD</sub> – 0.002    | $V_{DD}$                   | V     |

|                              | Opamp bias = low                       |                    | AGND      | V <sub>DD</sub> /2                     | V <sub>DD</sub> /2 – 0.040 | V <sub>DD</sub> /2 – 0.001 | $V_{DD}/2 + 0.033$         | V     |

|                              |                                        | V <sub>AGND</sub>  | Ref Low   | V <sub>SS</sub>                        | V <sub>SS</sub>            | V <sub>SS</sub> + 0.004    | V <sub>SS</sub> + 0.016    | V     |

|                              | RefPower = medium                      | V <sub>REFHI</sub> | Ref High  | $V_{DD}$                               | V <sub>DD</sub> – 0.075    | V <sub>DD</sub> – 0.002    | $V_{DD}$                   | V     |

|                              | Opamp bias = high                      | V <sub>AGND</sub>  | AGND      | V <sub>DD</sub> /2                     | V <sub>DD</sub> /2 – 0.040 | V <sub>DD</sub> /2 – 0.001 | $V_{DD}/2 + 0.032$         | V     |

|                              |                                        | V <sub>REFLO</sub> | Ref Low   | V <sub>SS</sub>                        | V <sub>SS</sub>            | V <sub>SS</sub> + 0.003    | V <sub>SS</sub> + 0.015    | V     |

|                              | RefPower = medium                      | V <sub>REFHI</sub> | Ref High  | $V_{DD}$                               | V <sub>DD</sub> – 0.074    | V <sub>DD</sub> – 0.002    | $V_{DD}$                   | V     |

|                              | Opamp bias = low                       | V <sub>AGND</sub>  | AGND      | V <sub>DD</sub> /2                     | V <sub>DD</sub> /2 – 0.040 | V <sub>DD</sub> /2 – 0.001 | V <sub>DD</sub> /2 + 0.032 | V     |

|                              |                                        | V <sub>REFLO</sub> | Ref Low   | V <sub>SS</sub>                        | V <sub>SS</sub>            | V <sub>SS</sub> + 0.002    | V <sub>SS</sub> + 0.014    | V     |

| 0b011                        | RefPower = high                        | V <sub>REFHI</sub> | Ref High  | 3 × Bandgap                            | 3.753                      | 3.874                      | 3.979                      | V     |

|                              | Opamp bias = high                      | V <sub>AGND</sub>  | AGND      | 2 × Bandgap                            | 2.511                      | 2.590                      | 2.657                      | V     |

|                              |                                        | V <sub>REFLO</sub> | Ref Low   | Bandgap                                | 1.243                      | 1.297                      | 1.333                      | V     |

|                              | RefPower = high                        | V <sub>REFHI</sub> | Ref High  | 3 × Bandgap                            | 3.767                      | 3.881                      | 3.974                      | V     |

|                              | Opamp bias = low                       | V <sub>AGND</sub>  | AGND      | 2 × Bandgap                            | 2.518                      | 2.592                      | 2.652                      | V     |

|                              |                                        | V <sub>REFLO</sub> | Ref Low   | Bandgap                                | 1.241                      | 1.295                      | 1.330                      | V     |

|                              | RefPower = medium                      | V <sub>REFHI</sub> | Ref High  | 3 × Bandgap                            | 2.771                      | 3.885                      | 3.979                      | V     |

|                              | Opamp bias = high                      | V <sub>AGND</sub>  | AGND      | 2 × Bandgap                            | 2.521                      | 2.593                      | 2.649                      | V     |

|                              |                                        | V <sub>REFLO</sub> | Ref Low   | Bandgap                                | 1.240                      | 1.295                      | 1.331                      | V     |

|                              | RefPower = medium<br>Opamp bias = low  | V <sub>REFHI</sub> | Ref High  | 3 × Bandgap                            | 3.771                      | 3.887                      | 3.977                      | V     |

|                              |                                        | V <sub>AGND</sub>  | AGND      | 2 × Bandgap                            | 2.522                      | 2.594                      | 2.648                      | V     |

|                              |                                        | V <sub>REFLO</sub> | Ref Low   | Bandgap                                | 1.239                      | 1.295                      | 1.332                      | V     |

| 0b100                        | RefPower = high<br>Opamp bias = high   | V <sub>REFHI</sub> | Ref High  | 2 × Bandgap + P2[6]<br>(P2[6] = 1.3 V) | 2.481 + P2[6]              | 2.569 + P2[6]              | 2.639 + P2[6]              | V     |

|                              |                                        | V <sub>AGND</sub>  | AGND      | 2 × Bandgap                            | 2.511                      | 2.590                      | 2.658                      | V     |

|                              |                                        | V <sub>REFLO</sub> | Ref Low   | 2 × Bandgap – P2[6]<br>(P2[6] = 1.3 V) | 2.515 – P2[6]              | 2.602 - P2[6]              | 2.654 - P2[6]              | V     |

|                              | RefPower = high<br>Opamp bias = low    | $V_{REFHI}$        | Ref High  | 2 × Bandgap + P2[6]<br>(P2[6] = 1.3 V) | 2.498 + P2[6]              | 2.579 + P2[6]              | 2.642 + P2[6]              | V     |

|                              |                                        | $V_{AGND}$         | AGND      | 2 × Bandgap                            | 2.518                      | 2.592                      | 2.652                      | V     |

|                              |                                        | V <sub>REFLO</sub> | Ref Low   | 2 × Bandgap – P2[6]<br>(P2[6] = 1.3 V) | 2.513 – P2[6]              | 2.598 - P2[6]              | 2.650 - P2[6]              | V     |

|                              | RefPower = medium<br>Opamp bias = high | $V_{REFHI}$        | Ref High  | 2 × Bandgap + P2[6]<br>(P2[6] = 1.3 V) | 2.504 + P2[6]              | 2.583 + P2[6]              | 2.646 + P2[6]              | V     |

|                              |                                        | $V_{AGND}$         | AGND      | 2 × Bandgap                            | 2.521                      | 2.592                      | 2.650                      | V     |

|                              |                                        | V <sub>REFLO</sub> | Ref Low   | 2 × Bandgap – P2[6]<br>(P2[6] = 1.3 V) | 2.513 – P2[6]              | 2.596 - P2[6]              | 2.649 - P2[6]              | V     |

|                              | RefPower = medium<br>Opamp bias = low  | $V_{REFHI}$        | Ref High  | 2 × Bandgap + P2[6]<br>(P2[6] = 1.3 V) | 2.505 + P2[6]              | 2.586 + P2[6]              | 2.648 + P2[6]              | V     |

|                              |                                        | $V_{AGND}$         | AGND      | 2 × Bandgap                            | 2.521                      | 2.594                      | 2.648                      | V     |

|                              |                                        | V <sub>REFLO</sub> | Ref Low   | 2 × Bandgap – P2[6]<br>(P2[6] = 1.3 V) | 2.513 – P2[6]              | 2.595 – P2[6]              | 2.648 – P2[6]              | V     |

Table 24. 2.7-V DC Analog Reference Specifications

| Reference<br>ARF_CR<br>[5:3] | Reference Power<br>Settings                | Symbol             | Reference | Description                                             | Min                        | Тур                        | Max                        | Units |

|------------------------------|--------------------------------------------|--------------------|-----------|---------------------------------------------------------|----------------------------|----------------------------|----------------------------|-------|

| 0b000                        | All power settings<br>Not allowed at 2.7 V | -                  | _         | _                                                       | _                          | _                          | -                          | _     |

| 0b001                        | RefPower = medium<br>Opamp bias = high     | V <sub>REFHI</sub> | Ref High  | P2[4]+P2[6] (P2[4] = V <sub>DD</sub> /2, P2[6] = 0.5 V) | P2[4] + P2[6]<br>- 0.739   | P2[4] + P2[6] –<br>0.016   | P2[4] + P2[6] +<br>0.759   | V     |

|                              |                                            | $V_{AGND}$         | AGND      | P2[4]                                                   | P2[4]                      | P2[4]                      | P2[4]                      | _     |

|                              |                                            | V <sub>REFLO</sub> | Ref Low   | P2[4]–P2[6] (P2[4] = V <sub>DD</sub> /2, P2[6] = 0.5 V) | P2[4] – P2[6]<br>– 1.675   | P2[4]-P2[6]+<br>0.013      | P2[4]-P2[6]+<br>1.825      | V     |

|                              | RefPower = medium<br>Opamp bias = low      | V <sub>REFHI</sub> | Ref High  | P2[4]+P2[6] (P2[4] = V <sub>DD</sub> /2, P2[6] = 0.5 V) | P2[4] + P2[6]<br>- 0.098   | P2[4] + P2[6] –<br>0.011   | P2[4] + P2[6] +<br>0.067   | V     |

|                              |                                            | V <sub>AGND</sub>  | AGND      | P2[4]                                                   | P2[4]                      | P2[4]                      | P2[4]                      | _     |

|                              |                                            | V <sub>REFLO</sub> | Ref Low   | P2[4]–P2[6] (P2[4] = V <sub>DD</sub> /2, P2[6] = 0.5 V) | P2[4] – P2[6]<br>– 0.308   | P2[4]-P2[6]+<br>0.004      | P2[4] – P2[6] +<br>0.362   | V     |

|                              | RefPower = low<br>Opamp bias = high        | V <sub>REFHI</sub> | Ref High  | P2[4]+P2[6] (P2[4] = V <sub>DD</sub> /2, P2[6] = 0.5 V) | P2[4] + P2[6]<br>- 0.042   | P2[4] + P2[6] –<br>0.005   | P2[4] + P2[6] +<br>0.035   | V     |

|                              |                                            | V <sub>AGND</sub>  | AGND      | P2[4]                                                   | P2[4]                      | P2[4]                      | P2[4]                      | _     |

|                              |                                            | V <sub>REFLO</sub> | Ref Low   | P2[4]–P2[6] (P2[4] = V <sub>DD</sub> /2, P2[6] = 0.5 V) | P2[4] – P2[6]<br>– 0.030   | P2[4] – P2[6]              | P2[4]-P2[6]+<br>0.030      | V     |

|                              | RefPower = low<br>Opamp bias = low         | $V_{REFHI}$        | Ref High  | P2[4]+P2[6] (P2[4] = V <sub>DD</sub> /2, P2[6] = 0.5 V) | P2[4] + P2[6]<br>- 0.367   | P2[4] + P2[6] –<br>0.005   | P2[4] + P2[6] +<br>0.308   | V     |

|                              |                                            | $V_{AGND}$         | AGND      | P2[4]                                                   | P2[4]                      | P2[4]                      | P2[4]                      | -     |

|                              |                                            | $V_{REFLO}$        | Ref Low   | P2[4]–P2[6] (P2[4] = V <sub>DD</sub> /2, P2[6] = 0.5 V) | P2[4] – P2[6]<br>– 0.345   | P2[4] – P2[6]              | P2[4]-P2[6]+<br>0.301      | V     |

| 0b010                        | RefPower = high                            | $V_{REFHI}$        | Ref High  | $V_{DD}$                                                | V <sub>DD</sub> – 0.100    | $V_{DD} - 0.003$           | $V_{DD}$                   | V     |

|                              | Opamp bias = high                          | V <sub>AGND</sub>  | AGND      | V <sub>DD</sub> /2                                      | V <sub>DD</sub> /2 – 0.038 | V <sub>DD</sub> /2         | V <sub>DD</sub> /2 + 0.036 | V     |

|                              |                                            | $V_{REFLO}$        | Ref Low   | V <sub>SS</sub>                                         | V <sub>SS</sub>            | V <sub>SS</sub> + 0.005    | V <sub>SS</sub> + 0.016    | V     |

|                              | RefPower = high<br>Opamp bias = low        | $V_{REFHI}$        | Ref High  | $V_{DD}$                                                | V <sub>DD</sub> – 0.065    | $V_{DD} - 0.002$           | $V_{DD}$                   | V     |

|                              | Opamp blas – low                           | V <sub>AGND</sub>  | AGND      | V <sub>DD</sub> /2                                      | V <sub>DD</sub> /2 – 0.025 | V <sub>DD</sub> /2         | V <sub>DD</sub> /2 + 0.023 | V     |

|                              |                                            | $V_{REFLO}$        | Ref Low   | V <sub>SS</sub>                                         | V <sub>SS</sub>            | V <sub>SS</sub> + 0.003    | V <sub>SS</sub> + 0.012    | V     |

|                              | RefPower = medium<br>Opamp bias = high     | $V_{REFHI}$        | Ref High  | $V_{DD}$                                                | V <sub>DD</sub> – 0.054    | V <sub>DD</sub> – 0.002    | $V_{DD}$                   | V     |

|                              | Opamp blas – mgn                           | $V_{AGND}$         | AGND      | V <sub>DD</sub> /2                                      | V <sub>DD</sub> /2 – 0.024 |                            |                            | V     |

|                              |                                            | $V_{REFLO}$        | Ref Low   | V <sub>SS</sub>                                         | V <sub>SS</sub>            | V <sub>SS</sub> + 0.002    | V <sub>SS</sub> + 0.012    | V     |

|                              | RefPower = medium<br>Opamp bias = low      | V <sub>REFHI</sub> | Ref High  | V <sub>DD</sub>                                         | V <sub>DD</sub> – 0.042    | V <sub>DD</sub> – 0.002    | $V_{DD}$                   | V     |

|                              | Opamp blas – low                           | V <sub>AGND</sub>  | AGND      | V <sub>DD</sub> /2                                      | V <sub>DD</sub> /2 – 0.027 |                            | V <sub>DD</sub> /2 + 0.022 | V     |

|                              |                                            | $V_{REFLO}$        | Ref Low   | V <sub>SS</sub>                                         | V <sub>SS</sub>            | V <sub>SS</sub> + 0.001    | V <sub>SS</sub> + 0.010    | V     |

|                              | RefPower = low                             | $V_{REFHI}$        | Ref High  | $V_{DD}$                                                | V <sub>DD</sub> – 0.042    | V <sub>DD</sub> – 0.002    | $V_{DD}$                   | V     |

|                              | Opamp bias = high                          | $V_{AGND}$         | AGND      | V <sub>DD</sub> /2                                      | V <sub>DD</sub> /2 – 0.028 | V <sub>DD</sub> /2 – 0.001 | V <sub>DD</sub> /2 + 0.023 | V     |

|                              |                                            | $V_{REFLO}$        | Ref Low   | V <sub>SS</sub>                                         | V <sub>SS</sub>            | V <sub>SS</sub> + 0.001    | V <sub>SS</sub> + 0.010    | V     |

|                              | RefPower = low                             | $V_{REFHI}$        | Ref High  | $V_{DD}$                                                | V <sub>DD</sub> – 0.036    | V <sub>DD</sub> – 0.002    | $V_{DD}$                   | V     |

|                              | Opamp bias = low                           | $V_{AGND}$         | AGND      | V <sub>DD</sub> /2                                      | V <sub>DD</sub> /2 – 0.184 | V <sub>DD</sub> /2 – 0.001 | V <sub>DD</sub> /2 + 0.159 | V     |

|                              |                                            | V <sub>REFLO</sub> | Ref Low   | $V_{SS}$                                                | V <sub>SS</sub>            | V <sub>SS</sub> + 0.001    | V <sub>SS</sub> + 0.009    | V     |

## DC POR, SMP, and LVD Specifications

Table 24 lists the guaranteed maximum and minimum specifications for the voltage and temperature ranges: 4.75 V to 5.25 V and  $-40~^{\circ}\text{C} \le T_{A} \le 85~^{\circ}\text{C}$ , 3.0 V to 3.6 V and  $-40~^{\circ}\text{C} \le T_{A} \le 85~^{\circ}\text{C}$ , or 2.4 V to 3.0 V and  $-40~^{\circ}\text{C} \le T_{A} \le 85~^{\circ}\text{C}$ , respectively. Typical parameters are measured at 5 V, 3.3 V, and 2.7 V at 25 °C and are for design guidance only.

Note The bits PORLEV and VM in the following table refer to bits in the VLT\_CR register. See the PSoC Programmable Sytem-on-Chip Technical Reference Manual for more information on the VLT\_CR register.

Table 26. DC POR and LVD Specifications

| Symbol                                                                       | Description                                                                                                                                                                        | Min                                                          | Тур                                                          | Max                                                                                          | Units                           | Notes                                                                                                                   |

|------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|--------------------------------------------------------------|----------------------------------------------------------------------------------------------|---------------------------------|-------------------------------------------------------------------------------------------------------------------------|

| V <sub>PPOR0</sub><br>V <sub>PPOR1</sub><br>V <sub>PPOR2</sub>               | V <sub>DD</sub> value for PPOR trip<br>PORLEV[1:0] = 00b<br>PORLEV[1:0] = 01b<br>PORLEV[1:0] = 10b                                                                                 | -                                                            | 2.36<br>2.82<br>4.55                                         | 2.40<br>2.95<br>4.70                                                                         | V<br>V                          | V <sub>DD</sub> must be greater than or equal to 2.5 V during startup, reset from the XRES pin, or reset from watchdog. |

| VLVD0<br>VLVD1<br>VLVD2<br>VLVD3<br>VLVD4<br>VLVD5<br>VLVD6<br>VLVD7         | V <sub>DD</sub> value for LVD trip<br>VM[2:0] = 000b<br>VM[2:0] = 001b<br>VM[2:0] = 010b<br>VM[2:0] = 011b<br>VM[2:0] = 100b<br>VM[2:0] = 101b<br>VM[2:0] = 110b<br>VM[2:0] = 111b | 2.40<br>2.85<br>2.95<br>3.06<br>4.37<br>4.50<br>4.62<br>4.71 | 2.45<br>2.92<br>3.02<br>3.13<br>4.48<br>4.64<br>4.73<br>4.81 | 2.51 <sup>[12]</sup><br>2.99 <sup>[13]</sup><br>3.09<br>3.20<br>4.55<br>4.75<br>4.83<br>4.95 | V V V V V V                     |                                                                                                                         |

| VPUMP0<br>VPUMP1<br>VPUMP2<br>VPUMP3<br>VPUMP4<br>VPUMP5<br>VPUMP6<br>VPUMP7 | V <sub>DD</sub> value for SMP trip<br>VM[2:0] = 000b<br>VM[2:0] = 001b<br>VM[2:0] = 010b<br>VM[2:0] = 011b<br>VM[2:0] = 100b<br>VM[2:0] = 101b<br>VM[2:0] = 110b<br>VM[2:0] = 111b | 2.50<br>2.96<br>3.03<br>3.18<br>4.54<br>4.62<br>4.71<br>4.89 | 2.55<br>3.02<br>3.10<br>3.25<br>4.64<br>4.73<br>4.82<br>5.00 | 2.62 <sup>[14]</sup> 3.09 3.16 3.32 <sup>[15]</sup> 4.74 4.83 4.92 5.12                      | \<br>\<br>\<br>\<br>\<br>\<br>\ |                                                                                                                         |

<sup>12.</sup> Always greater than 50 mV above  $V_{\rm PPOR}$  (PORLEV=00) for falling supply. 13. Always greater than 50 mV above  $V_{\rm PPOR}$  (PORLEV=01) for falling supply. 14. Always greater than 50 mV above  $V_{\rm LVD0}$ . 15. Always greater than 50 mV above  $V_{\rm LVD3}$ .

## Table 29. 5-V and 3.3-V AC Chip-Level Specifications (continued)

| Symbol                               | Description                                             | Min  | Тур  | Max                      | Units | Notes                                                                                          |

|--------------------------------------|---------------------------------------------------------|------|------|--------------------------|-------|------------------------------------------------------------------------------------------------|

| DC24M                                | 24 MHz duty cycle                                       | 40   | 50   | 60                       | %     |                                                                                                |

| DC <sub>ILO</sub>                    | ILO duty cycle                                          | 20   | 50   | 80                       | %     |                                                                                                |

| Step24M                              | 24 MHz trim step size                                   | _    | 50   | _                        | kHz   |                                                                                                |

| Fout48M                              | 48 MHz output frequency                                 | 46.8 | 48.0 | 49.2 <sup>[24, 25]</sup> | MHz   | Trimmed. Using factory trim values.                                                            |

| F <sub>MAX</sub>                     | Maximum frequency of signal on row input or row output. | _    | -    | 12.3                     | MHz   |                                                                                                |

| SR <sub>POWER_UP</sub>               | Power supply slew rate                                  | _    | _    | 250                      | V/ms  | V <sub>DD</sub> slew rate during power-up.                                                     |

| t <sub>POWERUP</sub>                 | Time from end of POR to CPU executing code              | -    | 16   | 100                      | ms    | Power-up from 0 V. See the System<br>Resets section of the PSoC<br>Technical Reference Manual. |

| t <sub>jit_IMO</sub> <sup>[26]</sup> | 24 MHz IMO cycle-to-cycle jitter (RMS)                  | _    | 200  | 700                      | ps    | N = 32                                                                                         |

| -                                    | 24 MHz IMO long term N cycle-to-cycle jitter (RMS)      | _    | 300  | 900                      | ps    |                                                                                                |

|                                      | 24 MHz IMO period jitter (RMS)                          | _    | 100  | 400                      | ps    |                                                                                                |

| t <sub>jit_PLL</sub> <sup>[26]</sup> | 24 MHz IMO cycle-to-cycle jitter (RMS)                  | -    | 200  | 800                      | ps    | N = 32                                                                                         |

|                                      | 24 MHz IMO long term N cycle-to-cycle jitter (RMS)      | _    | 300  | 1200                     |       |                                                                                                |

|                                      | 24 MHz IMO period jitter (RMS)                          | 1    | 100  | 700                      |       |                                                                                                |

24.4.75 V < V<sub>DD</sub> < 5.25 V.

25.3.0 V < V<sub>DD</sub> < 3.6 V. See application note Adjusting PSoC<sup>®</sup> Trims for 3.3 V and 2.7 V Operation – AN2012 for information on trimming for operation at 3.3 V.

26. Refer to Cypress Jitter Specifications application note, Understanding Datasheet Jitter Specifications for Cypress Timing Products – AN5054 for more information.

Table 30. 2.7-V AC Chip-Level Specifications

| Symbol                               | Description                                             | Min   | Тур | Max                      | Units | Notes                                                                                                                                                                   |

|--------------------------------------|---------------------------------------------------------|-------|-----|--------------------------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| F <sub>IMO12</sub>                   | IMO frequency for 12 MHz                                | 11.5  | 12  | 12.7 <sup>[27, 28]</sup> | MHz   | Trimmed for 2.7 V operation using factory trim values. See Figure 8 on page 18. SLIMO mode = 1.                                                                         |

| F <sub>IMO6</sub>                    | IMO frequency for 6 MHz                                 | 5.5   | 6   | 6.5 <sup>[27, 28]</sup>  | MHz   | Trimmed for 2.7 V operation using factory trim values. See Figure 8 on page 18. SLIMO mode = 1.                                                                         |

| F <sub>CPU1</sub>                    | CPU frequency (2.7 V nominal)                           | 0.937 | 3   | 3.15 <sup>[27]</sup>     | MHz   | SLIMO mode = 0.                                                                                                                                                         |

| F <sub>BLK27</sub>                   | Digital PSoC block frequency (2.7 V nominal)            | 0     | 12  | 12.7 <sup>[27, 28]</sup> | MHz   | Refer to the AC Digital Block Specifications.                                                                                                                           |

| F <sub>32K1</sub>                    | ILO frequency                                           | 8     | 32  | 96                       | kHz   |                                                                                                                                                                         |

| F <sub>32K_U</sub>                   | ILO untrimmed frequency                                 | 5     | _   | 100                      | kHz   | After a reset and before the M8C starts to run, the ILO is not trimmed. See the System Resets section of the PSoC Technical Reference Manual for details on timing this |

| t <sub>XRST</sub>                    | External reset pulse width                              | 10    | _   | _                        | μs    |                                                                                                                                                                         |

| DC12M                                | 12 MHz duty cycle                                       | 40    | 50  | 60                       | %     |                                                                                                                                                                         |

| DC <sub>ILO</sub>                    | ILO duty cycle                                          | 20    | 50  | 80                       | %     |                                                                                                                                                                         |

| F <sub>MAX</sub>                     | Maximum frequency of signal on row input or row output. | _     | -   | 12.7                     | MHz   |                                                                                                                                                                         |

| SR <sub>POWER_UP</sub>               | Power supply slew rate                                  | _     | _   | 250                      | V/ms  | V <sub>DD</sub> slew rate during power-up.                                                                                                                              |

| t <sub>POWERUP</sub>                 | Time from end of POR to CPU executing code              | _     | 16  | 100                      | ms    | Power-up from 0 V. See the System<br>Resets section of the PSoC<br>Technical Reference Manual.                                                                          |

| t <sub>jit_IMO</sub> <sup>[29]</sup> | 12 MHz IMO cycle-to-cycle jitter (RMS)                  | _     | 400 | 1000                     | ps    | N = 32                                                                                                                                                                  |

| 7 -                                  | 12 MHz IMO long term N cycle-to-cycle jitter (RMS)      | -     | 600 | 1300                     | ps    |                                                                                                                                                                         |

|                                      | 12 MHz IMO period jitter (RMS)                          | -     | 100 | 500                      | ps    |                                                                                                                                                                         |

| t <sub>jit_PLL</sub> <sup>[29]</sup> | 12 MHz IMO cycle-to-cycle jitter (RMS)                  | -     | 400 | 1000                     | ps    | N = 32                                                                                                                                                                  |

|                                      | 12 MHz IMO long term N cycle-to-cycle jitter (RMS)      | _     | 700 | 1300                     |       |                                                                                                                                                                         |

|                                      | 12 MHz IMO period jitter (RMS)                          | _     | 300 | 500                      |       |                                                                                                                                                                         |

Notes

27. 2.4 V < V<sub>DD</sub> < 3.0 V.

28. Refer to application note Adjusting PSoC® Trims for 3.3 V and 2.7 V Operation – AN2012 for information on trimming for operation at 3.3 V.

29. Refer to Cypress Jitter Specifications application note, Understanding Datasheet Jitter Specifications for Cypress Timing Products – AN5054 for more information.

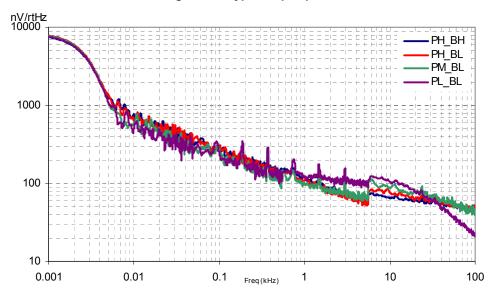

## AC Operational Amplifier Specifications

The following tables list the guaranteed maximum and minimum specifications for the voltage and temperature ranges: 4.75 V to 5.25 V and –40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C, 3.0 V to 3.6 V and –40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C, or 2.4 V to 3.0 V and –40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C, respectively. Typical parameters are measured at 5 V, 3.3 V, and 2.7 V at 25 °C and are for design guidance only.

Settling times, slew rates, and gain bandwidth are based on the analog continuous time PSoC block.

Power = high and Opamp bias = high is not supported at 3.3 V and 2.7 V.

Table 33. 5-V AC Operational Amplifier Specifications

| Symbol            | Description                                                                                                                                                                                 | Min                | Тур         | Max                 | Units                |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-------------|---------------------|----------------------|

| t <sub>ROA</sub>  | Rising settling time from 80% of $\Delta V$ to 0.1% of $\Delta V$ (10 pF load, unity gain) Power = low, Opamp bias = low Power = medium, Opamp bias = high Power = high, Opamp bias = high  | -<br>-<br>-        | _<br>_<br>_ | 3.9<br>0.72<br>0.62 | μs<br>μs<br>μs       |

| t <sub>SOA</sub>  | Falling settling time from 20% of $\Delta V$ to 0.1% of $\Delta V$ (10 pF load, unity gain) Power = low, Opamp bias = low Power = medium, Opamp bias = high Power = high, Opamp bias = high | = =                | _<br>_<br>_ | 5.9<br>0.92<br>0.72 | μs<br>μs<br>μs       |

| SR <sub>ROA</sub> | Rising slew rate (20% to 80%) (10 pF load, unity gain) Power = low, Opamp bias = low Power = medium, Opamp bias = high Power = high, Opamp bias = high                                      | 0.15<br>1.7<br>6.5 | -<br>-<br>- | -<br>-<br>-         | V/µs<br>V/µs<br>V/µs |

| SR <sub>FOA</sub> | Falling slew rate (20% to 80%) (10 pF load, unity gain) Power = low, Opamp bias = low Power = medium, Opamp bias = high Power = high, Opamp bias = high                                     | 0.01<br>0.5<br>4.0 | -<br>-<br>- | -<br>-<br>-         | V/µs<br>V/µs<br>V/µs |

| BW <sub>OA</sub>  | Gain bandwidth product Power = low, Opamp bias = low Power = medium, Opamp bias = high Power = high, Opamp bias = high                                                                      | 0.75<br>3.1<br>5.4 | -<br>-<br>- | -<br>-<br>-         | MHz<br>MHz<br>MHz    |

| E <sub>NOA</sub>  | Noise at 1 kHz (Power = medium, Opamp bias = high)                                                                                                                                          | _                  | 100         | -                   | nV/rt-Hz             |

Table 34. 3.3-V AC Operational Amplifier Specifications

| Symbol            | Description                                                                                                                                                       | Min         | Тур    | Max          | Units        |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--------|--------------|--------------|

| t <sub>ROA</sub>  | Rising settling time from 80% of $\Delta V$ to 0.1% of $\Delta V$ (10 pF load, unity gain)<br>Power = low, Opamp bias = low<br>Power = medium, Opamp bias = high  | _<br>_      |        | 3.92<br>0.72 | μs<br>μs     |

| t <sub>SOA</sub>  | Falling settling time from 20% of $\Delta V$ to 0.1% of $\Delta V$ (10 pF load, unity gain)<br>Power = low, Opamp bias = low<br>Power = medium, Opamp bias = high | _<br>_      | _<br>_ | 5.41<br>0.72 | μs<br>μs     |

| SR <sub>ROA</sub> | Rising slew rate (20% to 80%) (10 pF load, unity gain) Power = low, Opamp bias = low Power = medium, Opamp bias = high                                            | 0.31<br>2.7 |        | _<br>_       | V/µs<br>V/µs |

| SR <sub>FOA</sub> | Falling slew rate (20% to 80%) (10 pF load, unity gain) Power = low, Opamp bias = low Power = medium, Opamp bias = high                                           | 0.24<br>1.8 |        | _<br>_       | V/µs<br>V/µs |

| BW <sub>OA</sub>  | Gain bandwidth product Power = low, Opamp bias = low Power = medium, Opamp bias = high                                                                            | 0.67<br>2.8 | _<br>_ | _<br>_       | MHz<br>MHz   |

| E <sub>NOA</sub>  | Noise at 1 kHz (Power = medium, Opamp bias = high)                                                                                                                | _           | 100    | _            | nV/rt-Hz     |

Figure 15. Typical Opamp Noise

## AC Low Power Comparator Specifications

Table 36 lists the guaranteed maximum and minimum specifications for the voltage and temperature ranges: 4.75 V to 5.25 V and  $-40~^{\circ}\text{C} \le T_{A} \le 85~^{\circ}\text{C}$ , 3.0 V to 3.6 V and  $-40~^{\circ}\text{C} \le T_{A} \le 85~^{\circ}\text{C}$ , or 2.4 V to 3.0 V and  $-40~^{\circ}\text{C} \le T_{A} \le 85~^{\circ}\text{C}$ , respectively. Typical parameters are measured at 5 V at 25  $^{\circ}\text{C}$  and are for design guidance only.

Table 36. AC Low Power Comparator Specifications

| Symbol            | Description       | Min | Тур | Max | Units | Notes                                                                 |

|-------------------|-------------------|-----|-----|-----|-------|-----------------------------------------------------------------------|

| t <sub>RLPC</sub> | LPC response time | -   | -   | 50  | μs    | ≥ 50 mV overdrive comparator reference set within V <sub>REFLPC</sub> |

Table 44. 2.7-V AC External Clock Specifications

| Symbol              | Description                                                     | Min   | Тур | Max  | Units | Notes |

|---------------------|-----------------------------------------------------------------|-------|-----|------|-------|-------|

| F <sub>OSCEXT</sub> | Frequency with CPU clock divide by 1 <sup>[34]</sup>            | 0.093 | _   | 12.3 | MHz   |       |

| F <sub>OSCEXT</sub> | Frequency with CPU clock divide by 2 or greater <sup>[35]</sup> | 0.186 | _   | 12.3 | MHz   |       |

| _                   | High period with CPU clock divide by 1                          |       | _   | 5300 | ns    |       |

| _                   | Low period with CPU clock divide by 1                           | 41.7  | -   | -    | ns    |       |

| _                   | Power-up IMO to switch                                          | 150   | _   | -    | μs    |       |

#### AC Programming Specifications

Table 45 lists the guaranteed maximum and minimum specifications for the voltage and temperature ranges: 4.75 V to 5.25 V and  $-40~^{\circ}\text{C} \le T_{A} \le 85~^{\circ}\text{C}$ , 3.0 V to 3.6 V and  $-40~^{\circ}\text{C} \le T_{A} \le 85~^{\circ}\text{C}$ , or 2.4 V to 3.0 V and  $-40~^{\circ}\text{C} \le T_{A} \le 85~^{\circ}\text{C}$ , respectively. Typical parameters are measured at 5 V, 3.3 V, and 2.7 V at 25  $^{\circ}\text{C}$  and are for design guidance only.

**Table 45. AC Programming Specifications**

| Symbol                    | Description                                | Min | Тур | Max                 | Units | Notes                                                         |

|---------------------------|--------------------------------------------|-----|-----|---------------------|-------|---------------------------------------------------------------|

| t <sub>RSCLK</sub>        | Rise time of SCLK                          | 1   | _   | 20                  | ns    |                                                               |

| t <sub>FSCLK</sub>        | Fall time of SCLK                          | 1   | _   | 20                  | ns    |                                                               |

| t <sub>SSCLK</sub>        | Data setup time to falling edge of SCLK    | 40  | _   | _                   | ns    |                                                               |

| t <sub>HSCLK</sub>        | Data hold time from falling edge of SCLK   | 40  | _   | -                   | ns    |                                                               |

| F <sub>SCLK</sub>         | Frequency of SCLK                          | 0   | _   | 8                   | MHz   |                                                               |

| t <sub>ERASEB</sub>       | Flash erase time (block)                   | _   | 20  | _                   | ms    |                                                               |

| t <sub>WRITE</sub>        | Flash block write time                     | _   | 80  | -                   | ms    |                                                               |

| t <sub>DSCLK</sub>        | Data out delay from falling edge of SCLK   | _   | _   | 45                  | ns    | V <sub>DD</sub> > 3.6                                         |

| t <sub>DSCLK3</sub>       | Data out delay from falling edge of SCLK   | _   | _   | 50                  | ns    | $3.0 \leq V_{DD} \leq 3.6$                                    |

| t <sub>DSCLK2</sub>       | Data out delay from falling edge of SCLK   | _   | _   | 70                  | ns    | $2.4 \leq V_{DD} \leq 3.0$                                    |

| t <sub>ERASEALL</sub>     | Flash erase time (Bulk)                    | -   | 20  | _                   | ms    | Erase all blocks and protection fields at once                |

| t <sub>PROGRAM_HOT</sub>  | Flash block erase + flash block write time | _   | _   | 200 <sup>[36]</sup> | ms    | 0 °C ≤ Tj ≤ 100 °C                                            |

| t <sub>PROGRAM_COLD</sub> | Flash block erase + flash block write time | _   | _   | 400 <sup>[36]</sup> | ms    | $-40  ^{\circ}\text{C} \le \text{Tj} \le 0  ^{\circ}\text{C}$ |

#### Notes

<sup>34.</sup> Maximum CPU frequency is 12 MHz at 3.3 V. With the CPU clock divider set to 1, the external clock must adhere to the maximum frequency and duty cycle requirements.

<sup>35.</sup> If the frequency of the external clock is greater than 12 MHz, the CPU clock divider must be set to 2 or greater. In this case, the CPU clock divider ensures that the fifty percent duty cycle requirement is met.

<sup>36.</sup> For the full industrial range, you must employ a temperature sensor user module (FlashTemp) and feed the result to the temperature argument before writing Refer to the Flash APIs application note Design Aids – Reading and Writing PSoC® Flash – AN2015 for more information.

# **Packaging Information**

This section illustrates the packaging specifications for the CY8C24x23A PSoC device, along with the thermal impedances for each package and the typical package capacitance on crystal pins.

**Important Note** Emulation tools may require a larger area on the target PCB than the chip's footprint. For a detailed description of the emulation tools' dimensions, see the emulator pod drawings at http://www.cypress.com/design/MR10161.

## **Packaging Dimensions**

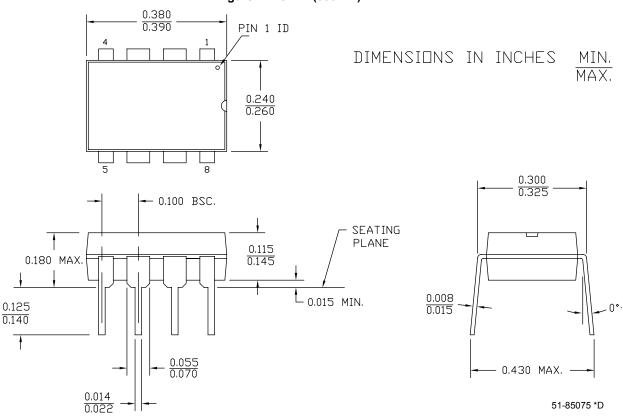

Figure 17. 8-Pin (300-Mil) PDIP

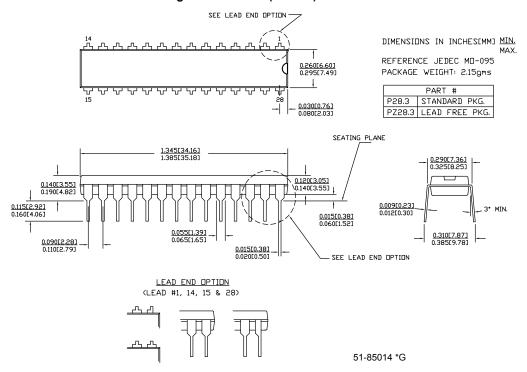

Figure 22. 28-Pin (300-Mil) Molded DIP

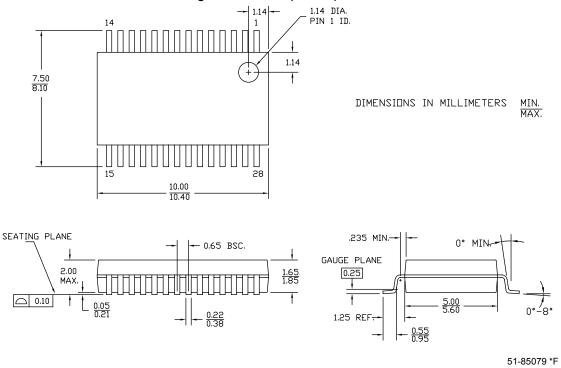

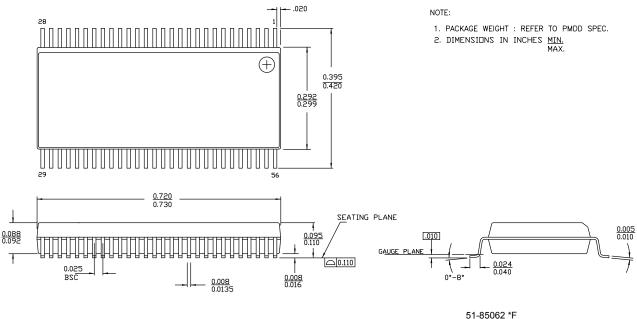

Figure 23. 28-Pin (210-Mil) SSOP

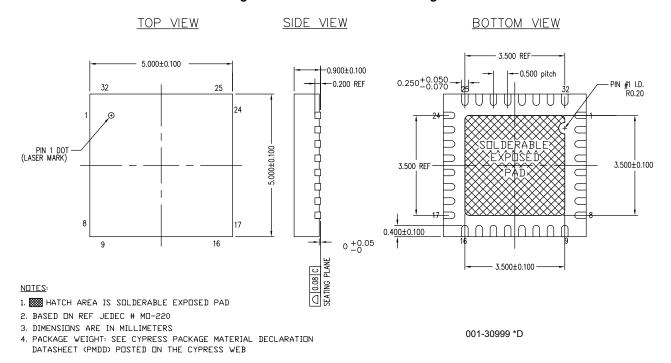

Figure 25. 32-Pin Sawn QFN Package

**Important Note** For information on the preferred dimensions for mounting QFN packages, see the application note, *Application Notes* for Surface Mount Assembly of Amkor's MicroLeadFrame (MLF) Packages available at http://www.amkor.com.

Figure 26. 56-Pin (300-Mil) SSOP

## Glossary (continued)

bias

- 1. A systematic deviation of a value from a reference value.

- The amount by which the average of a set of values departs from a reference value.

- 3. The electrical, mechanical, magnetic, or other force (field) applied to a device to establish a reference level to operate the device.

block

- 1. A functional unit that performs a single function, such as an oscillator.

- A functional unit that may be configured to perform one of several functions, such as a digital PSoC block or an analog PSoC block.

buffer