# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 2014110                    |                                                                              |

|----------------------------|------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                     |

| Core Processor             | M8C                                                                          |

| Core Size                  | 8-Bit                                                                        |

| Speed                      | 24MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                            |

| Peripherals                | POR, PWM, WDT                                                                |

| Number of I/O              | 24                                                                           |

| Program Memory Size        | 4KB (4K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | -                                                                            |

| RAM Size                   | 256 × 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 2.4V ~ 5.25V                                                                 |

| Data Converters            | A/D 12x14b; D/A 2x9b                                                         |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                               |

| Supplier Device Package    | 28-SSOP                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/cy8c24423a-24pvxa |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## More Information

Cypress provides a wealth of data at www.cypress.com to help you to select the right PSoC device for your design, and to help you to quickly and effectively integrate the device into your design. Following is an abbreviated list for PSoC 1:

- Overview: PSoC Portfolio, PSoC Roadmap

- Product Selectors: PSoC 1, PSoC 3, PSoC 4, or PSoC 5LP In addition, PSoC Designer offers a device selection tool within PSoC 1, at the time of creating a new project.

- Datasheets: Describe and provide electrical specifications for all the PSoC 1 family of devices. Visit the PSoC 1 datasheets web page for a complete list

- Application notes and code examples:

- □ Visit the PSoC 1 Code Examples web page for a comprehensive list of code examples

- Cypress offers a large number of PSoC application notes covering a broad range of topics, from basic to advanced level. Recommended application notes for getting started with PSoC 1 are:

- AN75320: Getting Started with PSoC® 1

- AN2094: PSoC<sup>®</sup> 1 Getting Started with GPIO

- AN2015: PSoC<sup>®</sup> 1 Getting Started with Flash & E2PROM

- AN2014: Basics of PSoC<sup>®</sup> 1 Programming

- AN32200: PSoC<sup>®</sup> 1 Clocks and Global Resources

- AN2010: PSoC<sup>®</sup> 1 Best Practices and Recommendations

- Technical Reference Manual (TRM):

- Visit the PSoC 1 TRM page for the complete list of TRMs. Following documents provide detailed descriptions of the Architecture, Programming specification and Register map details of CY8C2XXXX PSoC 1 device family. PSoC1 CY8C2XXXX TRM

- PSoC1 ISSP Programming Specifications

- Development Kits:

- CY3210 CY8C24x23 PSoC(R) Evaluation Pods (EvalPod) are 28-pin PDIP adapters that seamlessly connect any PSoC device to the 28-pin PDIP connector on any Cypress PSoC development kit. CY3210-24x23 provides evaluation of the CY8C24x23A PSoC device family on any PSoC developer kit. PSoC developer kits are sold separately.

- □ Visit the PSoC® 1 Kits page and refer the Kit Selector Guide document to find out the suitable development kits and debuggers for all PSoC 1 families.

- The CY3217-MiniProg1 and CY8CKIT-002 PSoC® MiniProg3 device provide an interface for flash programming.

- Knowledge Base Articles (KBA): Provide design and application tips from experts on the devices/kits. For example, Flash read/write access from firmware, explains how we can read and write to flash in PSoC 1 devices

#### **PSoC Designer**

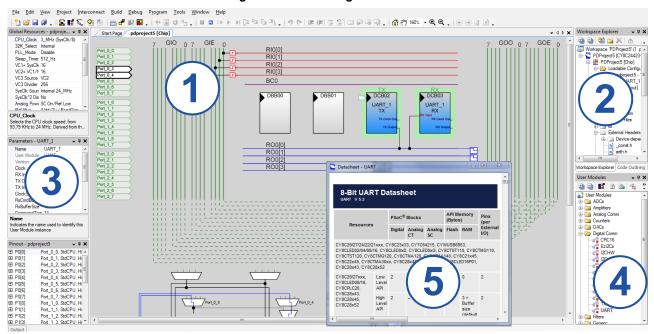

PSoC Designer is a free Windows-based Integrated Design Environment (IDE). It enables concurrent hardware and firmware design of systems based on CapSense (see Figure 1). With PSoC Designer, you can:

- 1. Drag and drop user modules to build your hardware system design in the main design workspace

- 2. Codesign your application firmware with the PSoC hardware, using the PSoC Designer IDE C compiler

- 3. Configure user module

- 4. Explore the library of user modules

- 5. Review user module datasheets

- - Figure 1. PSoC Designer Features

#### Additional System Resources

System resources, some of which are listed in the previous sections, provide additional capability useful to complete systems. Additional resources include a multiplier, decimator, switch-mode pump, low-voltage detection, and power-on-reset (POR). Statements describing the merits of each system resource follow:

- Digital clock dividers provide three customizable clock frequencies for use in applications. The clocks can be routed to both the digital and analog systems. Additional clocks may be generated using digital PSoC blocks as clock dividers.

- A multiply accumulate (MAC) provides a fast 8-bit multiplier with 32-bit accumulate, to assist in both general math and digital filters.

- The decimator provides a custom hardware filter for digital signal processing applications including the creation of Delta Sigma ADCs.

- The I<sup>2</sup>C module provides 100- and 400-kHz communication over two wires. slave, master, and multi-master are supported.

- Low-voltage detection (LVD) interrupts can signal the application of falling voltage levels, while the advanced POR circuit eliminates the need for a system supervisor.

- An internal 1.3 V reference provides an absolute reference for the analog system, including ADCs and DACs.

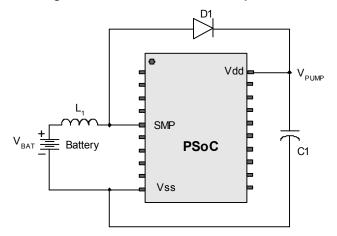

- An integrated switch-mode pump generates normal operating voltages from a single 1.2 V battery cell, providing a low cost boost converter.

#### **PSoC Device Characteristics**

Depending on your PSoC device characteristics, the digital and analog systems can have 16, 8, or 4 digital blocks, and 12, 6, or 4 analog blocks. Table 1 on page 6 lists the resources available for specific PSoC device groups. The PSoC device covered by this datasheet is highlighted in this table.

| PSoC Part<br>Number | Digital<br>I/O | Digital<br>Rows | Digital<br>Blocks | Analog<br>Inputs | Analog<br>Outputs | Analog<br>Columns | Analog<br>Blocks               | SRAM<br>Size | Flash<br>Size |

|---------------------|----------------|-----------------|-------------------|------------------|-------------------|-------------------|--------------------------------|--------------|---------------|

| CY8C29x66           | up to 64       | 4               | 16                | up to 12         | 4                 | 4                 | 12                             | 2 K          | 32 K          |

| CY8C28xxx           | up to 44       | up to 3         | up to 12          | up to 44         | up to 4           | up to 6           | up to<br>12 + 4 <sup>[2]</sup> | 1 K          | 16 K          |

| CY8C27x43           | up to 44       | 2               | 8                 | up to 12         | 4                 | 4                 | 12                             | 256          | 16 K          |

| CY8C24x94           | up to 56       | 1               | 4                 | up to 48         | 2                 | 2                 | 6                              | 1 K          | 16 K          |

| CY8C24x23A          | up to 24       | 1               | 4                 | up to 12         | 2                 | 2                 | 6                              | 256          | 4 K           |

| CY8C23x33           | up to 26       | 1               | 4                 | up to 12         | 2                 | 2                 | 4                              | 256          | 8 K           |

| CY8C22x45           | up to 38       | 2               | 8                 | up to 38         | 0                 | 4                 | 6 <sup>[2]</sup>               | 1 K          | 16 K          |

| CY8C21x45           | up to 24       | 1               | 4                 | up to 24         | 0                 | 4                 | 6 <sup>[2]</sup>               | 512          | 8 K           |

| CY8C21x34           | up to 28       | 1               | 4                 | up to 28         | 0                 | 2                 | 4 <sup>[2]</sup>               | 512          | 8 K           |

| CY8C21x23           | up to 16       | 1               | 4                 | up to 8          | 0                 | 2                 | 4 <sup>[2]</sup>               | 256          | 4 K           |

| CY8C20x34           | up to 28       | 0               | 0                 | up to 28         | 0                 | 0                 | 3 <sup>[2,3]</sup>             | 512          | 8 K           |

| CY8C20xx6           | up to 36       | 0               | 0                 | up to 36         | 0                 | 0                 | 3 <sup>[2,3]</sup>             | up to<br>2 K | up to<br>32 K |

#### Table 1. PSoC Device Characteristics

2. Limited analog functionality.

3. Two analog blocks and one CapSense<sup>®</sup>.

## Pinouts

This section describes, lists, and illustrates the CY8C24x23A PSoC device pins and pinout configurations. Every port pin (labeled with a "P") is capable of digital I/O. However,  $V_{SS}$ ,  $V_{DD}$ , SMP, and XRES are not capable of digital I/O.

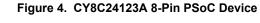

#### 8-Pin Part Pinout

| Pin | Type Pin |        | Pin             | Description                                                                             |

|-----|----------|--------|-----------------|-----------------------------------------------------------------------------------------|

| No. | Digital  | Analog | Name            | Description                                                                             |

| 1   | I/O      | I/O    | P0[5]           | Analog column mux input and column output                                               |

| 2   | I/O      | I/O    | P0[3]           | Analog column mux input and column output                                               |

| 3   | I/O      |        | P1[1]           | Crystal input (XTALin), I <sup>2</sup> C serial clock (SCL), ISSP-SCLK <sup>[4]</sup>   |

| 4   | Po       | wer    | V <sub>SS</sub> | Ground connection                                                                       |

| 5   | I/O      |        | P1[0]           | Crystal output (XTALout), I <sup>2</sup> C serial data (SDA), ISSP-SDATA <sup>[4]</sup> |

| 6   | I/O      | I      | P0[2]           | Analog column mux input                                                                 |

| 7   | I/O      | I      | P0[4]           | Analog column mux input                                                                 |

| 8   | Po       | wer    | $V_{DD}$        | Supply voltage                                                                          |

|     |          |        |                 |                                                                                         |

#### Table 2. 8-Pin PDIP and SOIC

**LEGEND**: A = Analog, I = Input, and O = Output.

#### 20-Pin Part Pinout

#### Table 3. 20-Pin PDIP, SSOP, and SOIC

| Pin | Ту      | ре     | Pin             | Description                                              |  |  |  |

|-----|---------|--------|-----------------|----------------------------------------------------------|--|--|--|

| No. | Digital | Analog | Name            | Description                                              |  |  |  |

| 1   | I/O     | I      | P0[7]           | Analog column mux input                                  |  |  |  |

| 2   | I/O     | I/O    | P0[5]           | Analog column mux input and column output                |  |  |  |

| 3   | I/O     | I/O    | P0[3]           | Analog column mux input and column output                |  |  |  |

| 4   | I/O     | I      | P0[1]           | Analog column mux input                                  |  |  |  |

| 5   | Po      | wer    | SMP             | SMP connection to external components required           |  |  |  |

| 6   | I/O     |        | P1[7]           | I <sup>2</sup> C SCL                                     |  |  |  |

| 7   | I/O     |        | P1[5]           | I <sup>2</sup> C SDA                                     |  |  |  |

| 8   | I/O     |        | P1[3]           |                                                          |  |  |  |

| 9   | I/O     |        | P1[1]           | XTALin, I <sup>2</sup> C SCL, ISSP-SCLK <sup>[5]</sup>   |  |  |  |

| 10  | Po      | wer    | V <sub>SS</sub> | Ground connection.                                       |  |  |  |

| 11  | I/O     |        | P1[0]           | XTALout, I <sup>2</sup> C SDA, ISSP-SDATA <sup>[5]</sup> |  |  |  |

| 12  | I/O     |        | P1[2]           |                                                          |  |  |  |

| 13  | I/O     |        | P1[4]           | Optional external clock input (EXTCLK)                   |  |  |  |

| 14  | I/O     |        | P1[6]           |                                                          |  |  |  |

| 15  | Inj     | put    | XRES            | Active high external reset with internal<br>pull-down    |  |  |  |

| 16  | I/O     | I      | P0[0]           | Analog column mux input                                  |  |  |  |

| 17  | I/O     | I      | P0[2]           | Analog column mux input                                  |  |  |  |

| 18  | I/O     | I      | P0[4]           | Analog column mux input                                  |  |  |  |

| 19  | I/O     | I      | P0[6]           | Analog column mux input                                  |  |  |  |

| 20  | Po      | wer    | V <sub>DD</sub> | Supply voltage                                           |  |  |  |

|     |         |        |                 |                                                          |  |  |  |

#### Figure 5. CY8C24223A 20-Pin PSoC Device

**LEGEND**: A = Analog, I = Input, and O = Output.

Note

5. These are the ISSP pins, which are not high Z at POR. See the PSoC Technical Reference Manual for details.

#### 28-Pin Part Pinout

#### Table 4. 28-Pin PDIP, SSOP, and SOIC

| Pin  |         |        | Pin             | Description                                              | Figure 6. CY8C24423A 28-Pin PSoC Device                                            |

|------|---------|--------|-----------------|----------------------------------------------------------|------------------------------------------------------------------------------------|

| No.  | Digital | Analog | Name            | Description                                              |                                                                                    |

| 1    | I/O     | Ι      | P0[7]           | Analog column mux input                                  | A, I, P0[7] <b>=</b> 1 28 <b>D</b> V <sub>DD</sub>                                 |

| 2    | I/O     | I/O    | P0[5]           | Analog column mux input and column output                |                                                                                    |

| 3    | I/O     | I/O    | P0[3]           | Analog column mux input and column output                | A, IO, P0[3] = 3 26 = P0[4], A, I<br>A, I, P0[1] = 4 25 = P0[2], A, I              |

| 4    | I/O     | I      | P0[1]           | Analog column mux input                                  | P2[7] = 5 24 = P0[0], A, I                                                         |

| 5    | I/O     |        | P2[7]           |                                                          | P2[5]                                                                              |

| 6    | I/O     |        | P2[5]           |                                                          | A, I, P2[3] = 7 SSOP 22 = P2[4], External AGND<br>A, I, P2[1] = 8 21 = P2[2], A, I |

| 7    | I/O     | I      | P2[3]           | Direct switched capacitor block input                    | A, I, P2[1] = 8 21 = P2[2], A, I<br>SMP = 9 SOIC 20 = P2[0], A, I                  |

| 8    | I/O     | I      | P2[1]           | Direct switched capacitor block input                    | 12CSCL, P1[7] = 10 19 EXRES                                                        |

| 9    | Pov     | wer    | SMP             | SMP connection to external components                    | I2C SDA, P1[5] ■ 11 18 ■ P1[6]                                                     |

| - 10 |         |        |                 | required                                                 | P1[3] ■ 12 17 ■ P1[4], EXTCLK<br>12C SCL, XTALin, P1[1] ■ 13 16 ■ P1[2]            |

| 10   | I/O     |        | P1[7]           | I <sup>2</sup> C SCL                                     | V <sub>ss</sub> = 14 15 = P1[0], XTALout, I2(SD.                                   |

| 11   | I/O     |        | P1[5]           | I <sup>2</sup> C SDA                                     |                                                                                    |

| 12   | I/O     |        | P1[3]           | 2                                                        |                                                                                    |

| 13   | I/O     |        | P1[1]           | XTALin, I <sup>2</sup> C SCL, ISSP-SCLK <sup>[6]</sup>   |                                                                                    |

| 14   |         | wer    | V <sub>SS</sub> | Ground connection.                                       |                                                                                    |

| 15   | I/O     |        | P1[0]           | XTALout, I <sup>2</sup> C SDA, ISSP-SDATA <sup>[6]</sup> |                                                                                    |

| 16   | I/O     |        | P1[2]           |                                                          |                                                                                    |

| 17   | I/O     |        | P1[4]           | Optional EXTCLK                                          | -                                                                                  |

| 18   | I/O     |        | P1[6]           |                                                          | -                                                                                  |

| 19   | Inp     | out    | XRES            | Active high external reset with internal<br>pull-down    |                                                                                    |

| 20   | I/O     | I      | P2[0]           | Direct switched capacitor block input                    | Not for Production                                                                 |

| 21   | I/O     | I      | P2[2]           | Direct switched capacitor block input                    |                                                                                    |

| 22   | I/O     |        | P2[4]           | External analog ground (AGND)                            |                                                                                    |

| 23   | I/O     |        | P2[6]           | External voltage reference (V <sub>REF</sub> )           |                                                                                    |

| 24   | I/O     | I      | P0[0]           | Analog column mux input                                  |                                                                                    |

| 25   | I/O     | I      | P0[2]           | Analog column mux input                                  |                                                                                    |

| 26   | I/O     | I      | P0[4]           | Analog column mux input                                  |                                                                                    |

| 27   | I/O     | I      | P0[6]           | Analog column mux input                                  | ]                                                                                  |

| 28   | Pov     | wer    | $V_{DD}$        | Supply voltage                                           | ]                                                                                  |

**LEGEND**: A = Analog, I = Input, and O = Output.

Note

6. These are the ISSP pins, which are not high Z at POR. See the PSoC Technical Reference Manual for details.

## **Electrical Specifications**

This section presents the DC and AC electrical specifications of the CY8C24x23A PSoC device. For the latest electrical specifications, check if you have the most recent datasheet by visiting the website at http://www.cypress.com.

Specifications are valid for –40  $^\circ C \le T_A \le 85 \ ^\circ C$  and  $T_J \le 100 \ ^\circ C,$  except where noted.

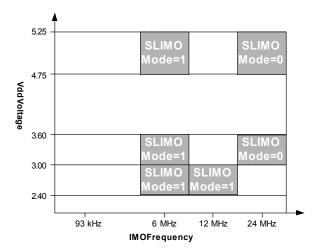

Refer to Table 29 on page 37 for the electrical specifications for the IMO using SLIMO mode.

#### Figure 8. IMO Frequency Trim Options

#### Absolute Maximum Ratings

Exceeding maximum ratings may shorten the useful life of the device. User guidelines are not tested.

| Symbol                | Description                                     | Min                     | Тур | Max                     | Units | Notes                                                                                                                                                                                                 |

|-----------------------|-------------------------------------------------|-------------------------|-----|-------------------------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| T <sub>STG</sub>      | Storage temperature                             | -55                     | 25  | +100                    | °C    | Higher storage temperatures<br>reduce data retention time.<br>Recommended storage<br>temperature is +25 °C ± 25 °C.<br>Extended duration storage<br>temperatures above 65 °C<br>degrades reliability. |

| T <sub>BAKETEMP</sub> | Bake temperature                                | -                       | 125 | See<br>package<br>label | °C    |                                                                                                                                                                                                       |

| t <sub>BAKETIME</sub> | Bake time                                       | See<br>package<br>label | -   | 72                      | Hours |                                                                                                                                                                                                       |

| T <sub>A</sub>        | Ambient temperature with power applied          | -40                     | _   | +85                     | °C    |                                                                                                                                                                                                       |

| V <sub>DD</sub>       | Supply voltage on $V_{DD}$ relative to $V_{SS}$ | -0.5                    | -   | +6.0                    | V     |                                                                                                                                                                                                       |

| V <sub>IO</sub>       | DC input voltage                                | $V_{SS} - 0.5$          | _   | V <sub>DD</sub> + 0.5   | V     |                                                                                                                                                                                                       |

| V <sub>IOZ</sub>      | DC voltage applied to tri-state                 | $V_{SS} - 0.5$          | -   | V <sub>DD</sub> + 0.5   | V     |                                                                                                                                                                                                       |

| I <sub>MIO</sub>      | Maximum current into any port pin               | -25                     | -   | +50                     | mA    |                                                                                                                                                                                                       |

| ESD                   | Electrostatic discharge voltage                 | 2000                    | -   | -                       | V     | Human body model ESD.                                                                                                                                                                                 |

| LU                    | Latch up current                                | _                       | -   | 200                     | mA    |                                                                                                                                                                                                       |

#### Table 9. Absolute Maximum Ratings

#### DC GPIO Specifications

The following tables list the guaranteed maximum and minimum specifications for the voltage and temperature ranges: 4.75 V to 5.25 V and –40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C, 3.0 V to 3.6 V and –40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C, or 2.4 V to 3.0 V and –40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C, respectively. Typical parameters are measured at 5 V, 3.3 V, and 2.7 V at 25 °C and are for design guidance only.

#### Table 12. 5-V and 3.3-V DC GPIO Specifications

| Symbol           | Description                       | Min                   | Тур | Max  | Units | Notes                                                                                                                                                                                                                            |

|------------------|-----------------------------------|-----------------------|-----|------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| R <sub>PU</sub>  | Pull-up resistor                  | 4                     | 5.6 | 8    | kΩ    |                                                                                                                                                                                                                                  |

| R <sub>PD</sub>  | Pull-down resistor                | 4                     | 5.6 | 8    | kΩ    |                                                                                                                                                                                                                                  |

| V <sub>OH</sub>  | High output level                 | V <sub>DD</sub> – 1.0 | Ι   | _    | V     | $I_{OH}$ = 10 mA, $V_{DD}$ = 4.75 to 5.25 V<br>(maximum 40 mA on even port pins<br>(for example, P0[2], P1[4]), maximum<br>40 mA on odd port pins (for example,<br>P0[3], P1[5])). 80 mA maximum<br>combined $I_{OH}$ budget.    |

| V <sub>OL</sub>  | Low output level                  | _                     | -   | 0.75 | V     | $I_{OL}$ = 25 mA, $V_{DD}$ = 4.75 to 5.25 V<br>(maximum 100 mA on even port pins<br>(for example, P0[2], P1[4]), maximum<br>100 mA on odd port pins (for<br>example, P0[3], P1[5])). 150 mA<br>maximum combined $I_{OL}$ budget. |

| I <sub>ОН</sub>  | High level source current         | 10                    | -   | -    | mA    | $V_{OH} = V_{DD} - 1.0 V$ , see the limitations of the total current in the note for $V_{OH}$                                                                                                                                    |

| I <sub>OL</sub>  | Low level sink current            | 25                    | -   | -    | mA    | $V_{OL}$ = 0.75 V, see the limitations of the total current in the note for $V_{OL}$                                                                                                                                             |

| V <sub>IL</sub>  | Input low level                   | -                     | -   | 0.8  | V     | V <sub>DD</sub> = 3.0 to 5.25                                                                                                                                                                                                    |

| V <sub>IH</sub>  | Input high level                  | 2.1                   | -   |      | V     | V <sub>DD</sub> = 3.0 to 5.25                                                                                                                                                                                                    |

| V <sub>H</sub>   | Input hysterisis                  | -                     | 60  | -    | mV    |                                                                                                                                                                                                                                  |

| Ι <sub>ΙL</sub>  | Input leakage (absolute value)    | -                     | 1   | -    | nA    | Gross tested to 1 µA                                                                                                                                                                                                             |

| C <sub>IN</sub>  | Capacitive load on pins as input  | -                     | 3.5 | 10   | pF    | Package and pin dependent.<br>Temp = 25 °C                                                                                                                                                                                       |

| C <sub>OUT</sub> | Capacitive load on pins as output | -                     | 3.5 | 10   | pF    | Package and pin dependent.<br>Temp = 25 °C                                                                                                                                                                                       |

#### Table 13. 2.7-V DC GPIO Specifications

| Symbol           | Description                       | Min                   | Тур | Мах  | Units | Notes                                                                                                          |

|------------------|-----------------------------------|-----------------------|-----|------|-------|----------------------------------------------------------------------------------------------------------------|

| R <sub>PU</sub>  | Pull-up resistor                  | 4                     | 5.6 | 8    | kΩ    |                                                                                                                |

| R <sub>PD</sub>  | Pull-down resistor                | 4                     | 5.6 | 8    | kΩ    |                                                                                                                |

| V <sub>OH</sub>  | High output level                 | V <sub>DD</sub> – 0.4 | -   | _    | V     | $I_{OH}$ = 2 mA (6.25 Typ), $V_{DD}$ = 2.4 to<br>3.0 V (16 mA maximum, 50 mA Typ<br>combined $I_{OH}$ budget). |

| V <sub>OL</sub>  | Low output level                  | -                     | -   | 0.75 | V     | $I_{OL}$ = 11.25 mA, $V_{DD}$ = 2.4 to 3.0 V (90 mA maximum combined $I_{OL}$ budget).                         |

| I <sub>OH</sub>  | High level source current         | 2                     | -   | -    | mA    | $V_{OH} = V_{DD} - 0.4$ , see the limitations of total current in note for $V_{OH}$ .                          |

| V <sub>IL</sub>  | Input low level                   | -                     | -   | 0.75 | V     | V <sub>DD</sub> = 2.4 to 3.0                                                                                   |

| V <sub>IH</sub>  | Input high level                  | 2.0                   | -   | -    | V     | V <sub>DD</sub> = 2.4 to 3.0                                                                                   |

| V <sub>H</sub>   | Input hysteresis                  | -                     | 90  | -    | mV    |                                                                                                                |

| I <sub>OL</sub>  | Low level sink current            | 11.25                 | _   | -    | mA    | $V_{OL}$ = .75, see the limitations of total current in note for $V_{OL}$ .                                    |

| IIL              | Input leakage (absolute value)    | -                     | 1   | -    | nA    | Gross tested to 1 µA                                                                                           |

| C <sub>IN</sub>  | Capacitive load on pins as input  | -                     | 3.5 | 10   | pF    | Package and pin dependent.<br>Temp = 25 °C                                                                     |

| C <sub>OUT</sub> | Capacitive load on pins as output | -                     | 3.5 | 10   | pF    | Package and pin dependent.<br>Temp = 25 °C                                                                     |

#### Figure 10. Basic Switch Mode Pump Circuit

#### DC POR, SMP, and LVD Specifications

Table 24 lists the guaranteed maximum and minimum specifications for the voltage and temperature ranges: 4.75 V to 5.25 V and -40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C, 3.0 V to 3.6 V and -40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C, or 2.4 V to 3.0 V and -40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C, respectively. Typical parameters are measured at 5 V, 3.3 V, and 2.7 V at 25 °C and are for design guidance only.

Note The bits PORLEV and VM in the following table refer to bits in the VLT\_CR register. See the PSoC Programmable Sytem-on-Chip Technical Reference Manual for more information on the VLT\_CR register.

Table 26. DC POR and LVD Specifications

| Symbol                                                                                                                                                               | Description                                                                                                                                                                                                           | Min                                                          | Тур                                                          | Max                                                                                          | Units                                   | Notes                                                                                                                            |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|--------------------------------------------------------------|----------------------------------------------------------------------------------------------|-----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|

| V <sub>PPOR0</sub><br>V <sub>PPOR1</sub><br>V <sub>PPOR2</sub>                                                                                                       | V <sub>DD</sub> value for PPOR trip<br>PORLEV[1:0] = 00b<br>PORLEV[1:0] = 01b<br>PORLEV[1:0] = 10b                                                                                                                    | _                                                            | 2.36<br>2.82<br>4.55                                         | 2.40<br>2.95<br>4.70                                                                         | V<br>V<br>V                             | V <sub>DD</sub> must be greater than or<br>equal to 2.5 V during startup,<br>reset from the XRES pin, or<br>reset from watchdog. |

| V <sub>LVD0</sub><br>V <sub>LVD1</sub><br>V <sub>LVD2</sub><br>V <sub>LVD3</sub><br>V <sub>LVD4</sub><br>V <sub>LVD5</sub><br>V <sub>LVD6</sub><br>V <sub>LVD7</sub> | $ \begin{array}{l} V_{DD} \text{ value for LVD trip} \\ VM[2:0] = 000b \\ VM[2:0] = 001b \\ VM[2:0] = 010b \\ VM[2:0] = 011b \\ VM[2:0] = 100b \\ VM[2:0] = 100b \\ VM[2:0] = 101b \\ VM[2:0] = 111b \\ \end{array} $ | 2.40<br>2.85<br>2.95<br>3.06<br>4.37<br>4.50<br>4.62<br>4.71 | 2.45<br>2.92<br>3.02<br>3.13<br>4.48<br>4.64<br>4.73<br>4.81 | 2.51 <sup>[12]</sup><br>2.99 <sup>[13]</sup><br>3.09<br>3.20<br>4.55<br>4.75<br>4.83<br>4.95 | V<br>V<br>V<br>V<br>V<br>V<br>V<br>V    |                                                                                                                                  |

| Vpumpo<br>Vpump1<br>Vpump2<br>Vpump3<br>Vpump3<br>Vpump5<br>Vpump5<br>Vpump6<br>Vpump7                                                                               | $\begin{array}{l} V_{DD} \text{ value for SMP trip} \\ VM[2:0] = 000b \\ VM[2:0] = 001b \\ VM[2:0] = 010b \\ VM[2:0] = 011b \\ VM[2:0] = 100b \\ VM[2:0] = 101b \\ VM[2:0] = 110b \\ VM[2:0] = 111b \end{array}$      | 2.50<br>2.96<br>3.03<br>3.18<br>4.54<br>4.62<br>4.71<br>4.89 | 2.55<br>3.02<br>3.10<br>3.25<br>4.64<br>4.73<br>4.82<br>5.00 | 2.62 <sup>[14]</sup><br>3.09<br>3.16<br>3.32 <sup>[15]</sup><br>4.74<br>4.83<br>4.92<br>5.12 | >>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>> |                                                                                                                                  |

Notes

- 12. Always greater than 50 mV above V<sub>PPOR</sub> (PORLEV=00) for falling supply. 13. Always greater than 50 mV above V<sub>PPOR</sub> (PORLEV=01) for falling supply. 14. Always greater than 50 mV above V<sub>LVD0</sub>. 15. Always greater than 50 mV above V<sub>LVD0</sub>.

#### **AC Electrical Characteristics**

#### AC Chip-Level Specifications

These tables list the guaranteed maximum and minimum specifications for the voltage and temperature ranges: 4.75 V to 5.25 V and -40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C, 3.0 V to 3.6 V and -40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C, or 2.4 V to 3.0 V and -40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C, respectively. Typical parameters are measured at 5 V, 3.3 V, and 2.7 V at 25 °C and are for design guidance only.

Table 29. 5-V and 3.3-V AC Chip-Level Specifications

| Symbol                             | Description                                         | Min   | Тур    | Max                     | Units | Notes                                                                                                                                                                                                                                                                                                                    |

|------------------------------------|-----------------------------------------------------|-------|--------|-------------------------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| F <sub>IMO24</sub> <sup>[19]</sup> | Internal main oscillator (IMO) frequency for 24 MHz | 22.8  | 24     | 25.2 <sup>[20,21]</sup> | MHz   | Trimmed for 5 V or 3.3 V operation<br>using factory trim values.<br>See Figure 8 on page 18.<br>SLIMO mode = 0.                                                                                                                                                                                                          |

| F <sub>IMO6</sub>                  | IMO frequency for 6 MHz                             | 5.5   | 6      | 6.5 <sup>[20,21]</sup>  | MHz   | Trimmed for 5 V or 3.3 V operation<br>using factory trim values.<br>See Figure 8 on page 18.<br>SLIMO mode = 1.                                                                                                                                                                                                          |

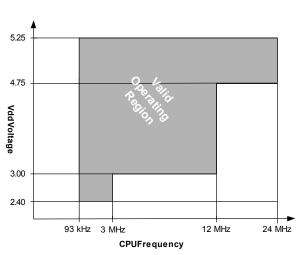

| F <sub>CPU1</sub>                  | CPU frequency (5 V nominal)                         | 0.937 | 24     | 24.6 <sup>[20]</sup>    | MHz   | SLIMO mode = 0.                                                                                                                                                                                                                                                                                                          |

| F <sub>CPU2</sub>                  | CPU frequency (3.3 V nominal)                       | 0.937 | 12     | 12.3 <sup>[21]</sup>    | MHz   | SLIMO mode = 0.                                                                                                                                                                                                                                                                                                          |

| F <sub>48M</sub>                   | Digital PSoC block frequency                        | 0     | 48     | 49.2 <sup>[20,22]</sup> | MHz   | Refer to the AC Digital Block<br>Specifications.                                                                                                                                                                                                                                                                         |

| F <sub>24M</sub>                   | Digital PSoC block frequency                        | 0     | 24     | 24.6 <sup>[22]</sup>    | MHz   |                                                                                                                                                                                                                                                                                                                          |

| F <sub>32K1</sub>                  | ILO frequency                                       | 15    | 32     | 64                      | kHz   |                                                                                                                                                                                                                                                                                                                          |

| F <sub>32K2</sub>                  | External crystal oscillator                         | -     | 32.768 | _                       | kHz   | Accuracy is capacitor and crystal dependent. 50% duty cycle.                                                                                                                                                                                                                                                             |

| F <sub>32K_U</sub>                 | ILO untrimmed frequency                             | 5     | -      | 100                     | kHz   | After a reset and before the M8C<br>starts to run, the ILO is not trimmed.<br>See the System Resets section of<br>the PSoC Technical Reference<br>Manual for details on timing this                                                                                                                                      |

| F <sub>PLL</sub>                   | PLL frequency                                       | -     | 23.986 | _                       | MHz   | Is a multiple (x732) of crystal frequency.                                                                                                                                                                                                                                                                               |

| T <sub>PLLSLEW</sub>               | PLL lock time                                       | 0.5   | -      | 10                      | ms    |                                                                                                                                                                                                                                                                                                                          |

| T <sub>PLLSLEWSLOW</sub>           | PLL lock time for low gain setting                  | 0.5   | -      | 50                      | ms    |                                                                                                                                                                                                                                                                                                                          |

| T <sub>OS</sub>                    | External crystal oscillator startup to 1%           | -     | 1700   | 2620                    | ms    |                                                                                                                                                                                                                                                                                                                          |

| TOSACC                             | External crystal oscillator startup to 100 ppm      | _     | 2800   | 3800                    | ms    | The crystal oscillator frequency is within 100 ppm of its final value by the end of the T <sub>osacc</sub> period. Correct operation assumes a properly loaded 1 $\mu$ W maximum drive level 32.768 kHz crystal. 3.0 V $\leq$ V <sub>DD</sub> $\leq$ 5.5 V, $-40 \degree$ C $\leq$ T <sub>A</sub> $\leq$ 85 $\degree$ C. |

| t <sub>XRST</sub>                  | External reset pulse width                          | 10    | -      | -                       | μS    |                                                                                                                                                                                                                                                                                                                          |

Notes

- 19. Errata: When the device is operated within 0 °C to 70 °C, the frequency tolerance is reduced to  $\pm 2.5\%$ , but if operated at extreme temperature (below 0 °C or above 70 °C), frequency tolerance deviates from  $\pm 2.5\%$  to  $\pm 5\%$ . For more information, see "Errata" on page 67. 20. 4.75 V < V<sub>DD</sub> < 5.25 V. 21. 3.0 V < V<sub>DD</sub> < 3.6 V. See application note Adjusting PSoC<sup>®</sup> Trims for 3.3 V and 2.7 V Operation AN2012 for information on trimming for operation at 3.3 V.

- 22. See the individual user module datasheets for information on maximum frequencies for user modules.

- 23. Refer to Cypress Jitter Specifications application note, Understanding Datasheet Jitter Specifications for Cypress Timing Products AN5054 for more information.

#### Table 30. 2.7-V AC Chip-Level Specifications

| Symbol                               | Description                                             | Min   | Тур | Мах                      | Units | Notes                                                                                                                                                                               |

|--------------------------------------|---------------------------------------------------------|-------|-----|--------------------------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| F <sub>IMO12</sub>                   | IMO frequency for 12 MHz                                | 11.5  | 12  | 12.7 <sup>[27, 28]</sup> | MHz   | Trimmed for 2.7 V operation using factory trim values.<br>See Figure 8 on page 18.<br>SLIMO mode = 1.                                                                               |

| F <sub>IMO6</sub>                    | IMO frequency for 6 MHz                                 | 5.5   | 6   | 6.5 <sup>[27, 28]</sup>  | MHz   | Trimmed for 2.7 V operation using factory trim values.<br>See Figure 8 on page 18.<br>SLIMO mode = 1.                                                                               |

| F <sub>CPU1</sub>                    | CPU frequency (2.7 V nominal)                           | 0.937 | 3   | 3.15 <sup>[27]</sup>     | MHz   | SLIMO mode = 0.                                                                                                                                                                     |

| F <sub>BLK27</sub>                   | Digital PSoC block frequency (2.7 V nominal)            | 0     | 12  | 12.7 <sup>[27, 28]</sup> | MHz   | Refer to the AC Digital Block<br>Specifications.                                                                                                                                    |

| F <sub>32K1</sub>                    | ILO frequency                                           | 8     | 32  | 96                       | kHz   |                                                                                                                                                                                     |

| F <sub>32K_U</sub>                   | ILO untrimmed frequency                                 | 5     | -   | 100                      | kHz   | After a reset and before the M8C<br>starts to run, the ILO is not trimmed.<br>See the System Resets section of<br>the PSoC Technical Reference<br>Manual for details on timing this |

| t <sub>XRST</sub>                    | External reset pulse width                              | 10    | -   | -                        | μs    |                                                                                                                                                                                     |

| DC12M                                | 12 MHz duty cycle                                       | 40    | 50  | 60                       | %     |                                                                                                                                                                                     |

| DC <sub>ILO</sub>                    | ILO duty cycle                                          | 20    | 50  | 80                       | %     |                                                                                                                                                                                     |

| F <sub>MAX</sub>                     | Maximum frequency of signal on row input or row output. | -     | -   | 12.7                     | MHz   |                                                                                                                                                                                     |

| SR <sub>POWER_UP</sub>               | Power supply slew rate                                  | -     | -   | 250                      | V/ms  | V <sub>DD</sub> slew rate during power-up.                                                                                                                                          |

| t <sub>POWERUP</sub>                 | Time from end of POR to CPU executing code              | -     | 16  | 100                      | ms    | Power-up from 0 V. See the System<br>Resets section of the PSoC<br>Technical Reference Manual.                                                                                      |

| t <sub>jit_IMO</sub> <sup>[29]</sup> | 12 MHz IMO cycle-to-cycle jitter (RMS)                  | _     | 400 | 1000                     | ps    | N = 32                                                                                                                                                                              |

|                                      | 12 MHz IMO long term N cycle-to-cycle jitter (RMS)      | -     | 600 | 1300                     | ps    |                                                                                                                                                                                     |

|                                      | 12 MHz IMO period jitter (RMS)                          | -     | 100 | 500                      | ps    |                                                                                                                                                                                     |

| t <sub>jit_PLL</sub> <sup>[29]</sup> | 12 MHz IMO cycle-to-cycle jitter (RMS)                  | _     | 400 | 1000                     | ps    | N = 32                                                                                                                                                                              |

|                                      | 12 MHz IMO long term N cycle-to-cycle jitter (RMS)      | -     | 700 | 1300                     |       |                                                                                                                                                                                     |

|                                      | 12 MHz IMO period jitter (RMS)                          | -     | 300 | 500                      |       |                                                                                                                                                                                     |

Notes 27. 2.4 V < V<sub>DD</sub> < 3.0 V. 28. Refer to application note Adjusting PSoC<sup>®</sup> Trims for 3.3 V and 2.7 V Operation – AN2012 for information on trimming for operation at 3.3 V. 29. Refer to Cypress Jitter Specifications application note, Understanding Datasheet Jitter Specifications for Cypress Timing Products – AN5054 for more information.

#### Table 35. 2.7-V AC Operational Amplifier Specifications

| Symbol            | Description                                                                                                                                                          | Min         | Тур | Мах          | Units        |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-----|--------------|--------------|

| t <sub>ROA</sub>  | Rising settling time from 80% of $\Delta V$ to 0.1% of $\Delta V$<br>(10 pF load, unity gain)<br>Power = low, Opamp bias = low<br>Power = medium, Opamp bias = high  |             |     | 3.92<br>0.72 | hs<br>hs     |

| t <sub>SOA</sub>  | Falling settling time from 20% of $\Delta V$ to 0.1% of $\Delta V$<br>(10 pF load, unity gain)<br>Power = low, Opamp bias = low<br>Power = medium, Opamp bias = high |             |     | 5.41<br>0.72 | hs<br>hs     |

| SR <sub>ROA</sub> | Rising slew rate (20% to 80%) (10 pF load, unity gain)<br>Power = low, Opamp bias = low<br>Power = medium, Opamp bias = high                                         | 0.31<br>2.7 |     |              | V/µs<br>V/µs |

| SR <sub>FOA</sub> | Falling slew rate (20% to 80%) (10 pF load, unity gain)<br>Power = low, Opamp bias = low<br>Power = medium, Opamp bias = high                                        | 0.24<br>1.8 |     |              | V/µs<br>V/µs |

| BW <sub>OA</sub>  | Gain bandwidth product<br>Power = low, Opamp bias = low<br>Power = medium, Opamp bias = high                                                                         | 0.67<br>2.8 |     |              | MHz<br>MHz   |

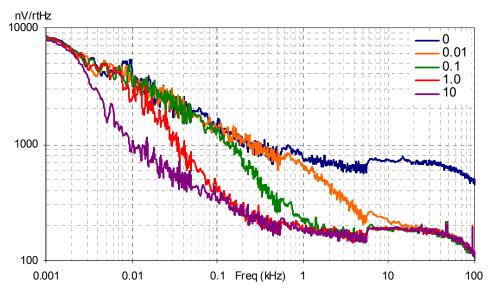

| E <sub>NOA</sub>  | Noise at 1 kHz (Power = medium, Opamp bias = high)                                                                                                                   | -           | 100 | -            | nV/rt-Hz     |

When bypassed by a capacitor on P2[4], the noise of the analog ground signal distributed to each block is reduced by a factor of up to 5 (14 dB). This is at frequencies above the corner frequency defined by the on-chip 8.1 K resistance and the external capacitor.

#### Figure 14. Typical AGND Noise with P2[4] Bypass

At low frequencies, the opamp noise is proportional to 1/f, power independent, and determined by device geometry. At high frequencies, increased power level reduces the noise spectrum level.

#### Table 44. 2.7-V AC External Clock Specifications

| Symbol              | Description                                                     | Min   | Тур | Max  | Units | Notes |

|---------------------|-----------------------------------------------------------------|-------|-----|------|-------|-------|

| F <sub>OSCEXT</sub> | Frequency with CPU clock divide by 1 <sup>[34]</sup>            | 0.093 | -   | 12.3 | MHz   |       |

| F <sub>OSCEXT</sub> | Frequency with CPU clock divide by 2 or greater <sup>[35]</sup> | 0.186 | -   | 12.3 | MHz   |       |

| -                   | High period with CPU clock divide by 1                          | 41.7  | -   | 5300 | ns    |       |

| -                   | Low period with CPU clock divide by 1                           | 41.7  | -   | -    | ns    |       |

| -                   | Power-up IMO to switch                                          | 150   | -   | -    | μs    |       |

#### AC Programming Specifications

Table 45 lists the guaranteed maximum and minimum specifications for the voltage and temperature ranges: 4.75 V to 5.25 V and -40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C, 3.0 V to 3.6 V and -40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C, or 2.4 V to 3.0 V and -40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C, respectively. Typical parameters are measured at 5 V, 3.3 V, and 2.7 V at 25 °C and are for design guidance only.

Table 45. AC Programming Specifications

| Symbol                    | Description                                | Min | Тур       | Max                            | Units                                          | Notes                                  |

|---------------------------|--------------------------------------------|-----|-----------|--------------------------------|------------------------------------------------|----------------------------------------|

| t <sub>RSCLK</sub>        | Rise time of SCLK                          | 1   | 1 – 20 ns |                                |                                                |                                        |

| t <sub>FSCLK</sub>        | Fall time of SCLK                          | 1   | -         | 20                             | ns                                             |                                        |

| t <sub>SSCLK</sub>        | Data setup time to falling edge of SCLK    | 40  | -         | -                              | ns                                             |                                        |

| t <sub>HSCLK</sub>        | Data hold time from falling edge of SCLK   | 40  | -         | -                              | ns                                             |                                        |

| F <sub>SCLK</sub>         | Frequency of SCLK                          | 0   | -         | 8                              | MHz                                            |                                        |

| t <sub>ERASEB</sub>       | Flash erase time (block)                   | -   | 20        | -                              | ms                                             |                                        |

| t <sub>WRITE</sub>        | Flash block write time                     | -   | 80        | -                              | ms                                             |                                        |

| t <sub>DSCLK</sub>        | Data out delay from falling edge of SCLK   | -   | -         | 45                             | 5 ns V <sub>DD</sub> > 3.6                     |                                        |

| t <sub>DSCLK3</sub>       | Data out delay from falling edge of SCLK   | -   | -         | 50 ns $3.0 \le V_{DD} \le 3.6$ |                                                | $3.0 \le V_{DD} \le 3.6$               |

| t <sub>DSCLK2</sub>       | Data out delay from falling edge of SCLK   | -   | -         | 70                             | 70 ns $2.4 \le V_{DD} \le 3$                   |                                        |

| t <sub>ERASEALL</sub>     | Flash erase time (Bulk)                    | -   |           |                                | Erase all blocks and protection fields at once |                                        |

| t <sub>PROGRAM_HOT</sub>  | Flash block erase + flash block write time | -   | -         | 200 <sup>[36]</sup>            | ms                                             | $0~^\circ C \leq Tj \leq 100~^\circ C$ |

| t <sub>PROGRAM_COLD</sub> | Flash block erase + flash block write time | -   | -         | 400 <sup>[36]</sup>            | ms                                             | $-40~^\circ C \le Tj \le 0~^\circ C$   |

Notes

34. Maximum CPU frequency is 12 MHz at 3.3 V. With the CPU clock divider set to 1, the external clock must adhere to the maximum frequency and duty cycle requirements.

<sup>35.</sup> If the frequency of the external clock is greater than 12 MHz, the CPU clock divider must be set to 2 or greater. In this case, the CPU clock divider ensures that the fifty percent duty cycle requirement is met.

<sup>36.</sup> For the full industrial range, you must employ a temperature sensor user module (FlashTemp) and feed the result to the temperature argument before writing Refer to the Flash APIs application note Design Aids – Reading and Writing PSoC<sup>®</sup> Flash – AN2015 for more information.

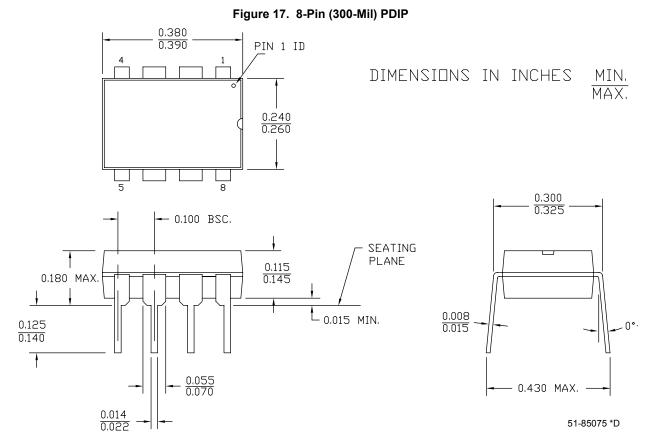

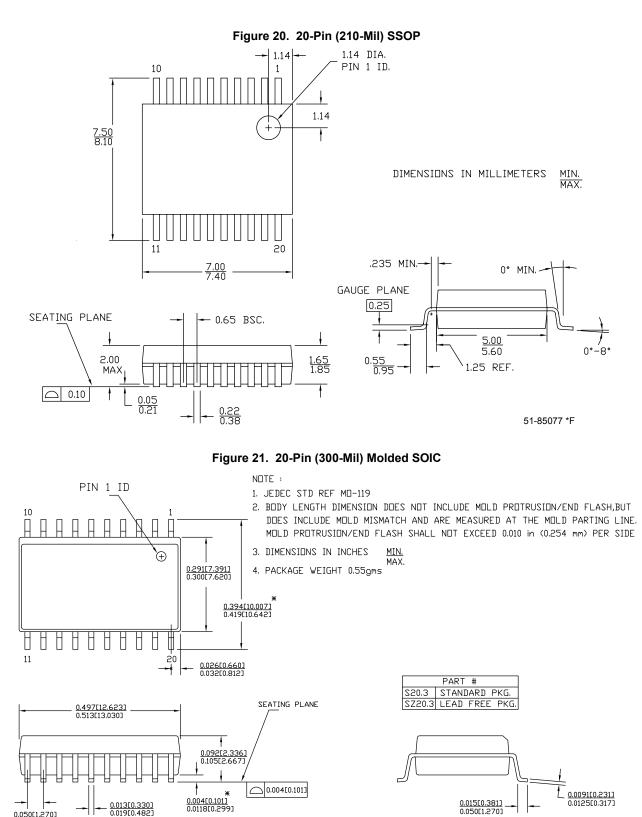

## **Packaging Information**

This section illustrates the packaging specifications for the CY8C24x23A PSoC device, along with the thermal impedances for each package and the typical package capacitance on crystal pins.

**Important Note** Emulation tools may require a larger area on the target PCB than the chip's footprint. For a detailed description of the emulation tools' dimensions, see the emulator pod drawings at http://www.cypress.com/design/MR10161.

#### Packaging Dimensions

0.050[1.270] TYP.

0.013[0.330] 0.019[0.482]

0.015[0.381] 0.050[1.270]

51-85024 \*F

## Acronyms

#### **Acronyms Used**

Table 53 lists the acronyms that are used in this document.

#### Table 53. Acronyms Used in this Datasheet

| Acronym | Description                                         | Acronym          | Description                                   |

|---------|-----------------------------------------------------|------------------|-----------------------------------------------|

| AC      | alternating current                                 | MIPS             | million instructions per second               |

| ADC     | analog-to-digital converter                         | OCD              | on-chip debug                                 |

| API     | application programming interface                   | PCB              | printed circuit board                         |

| CMOS    | complementary metal oxide semiconductor             | PDIP             | plastic dual-in-line package                  |

| CPU     | central processing unit                             | PGA              | programmable gain amplifier                   |

| CRC     | cyclic redundancy check                             | PLL              | phase-locked loop                             |

| СТ      | continuous time                                     | POR              | power on reset                                |

| DAC     | digital-to-analog converter                         | PPOR             | precision power on reset                      |

| DC      | direct current                                      | PRS              | pseudo-random sequence                        |

| DTMF    | dual-tone multi-frequency                           | PSoC®            | Programmable System-on-Chip                   |

| ECO     | external crystal oscillator                         | PWM              | pulse width modulator                         |

| EEPROM  | electrically erasable programmable read-only memory | QFN              | quad flat no leads                            |

| GPIO    | general purpose I/O                                 | RTC              | real time clock                               |

| ICE     | in-circuit emulator                                 | SAR              | successive approximation                      |

| IDE     | integrated development environment                  | SC               | switched capacitor                            |

| ILO     | internal low speed oscillator                       | SLIMO            | slow IMO                                      |

| IMO     | internal main oscillator                            | SMP              | switch mode pump                              |

| I/O     | input/output                                        | SOIC             | small-outline integrated circuit              |

| IrDA    | infrared data association                           | SPI <sup>™</sup> | serial peripheral interface                   |

| ISSP    | in-system serial programming                        | SRAM             | static random access memory                   |

| LCD     | liquid crystal display                              | SROM             | supervisory read only memory                  |

| LED     | light-emitting diode                                | SSOP             | shrink small-outline package                  |

| LPC     | low power comparator                                | UART             | universal asynchronous receiver / transmitter |

| LVD     | low voltage detect                                  | USB              | universal serial bus                          |

| MAC     | multiply-accumulate                                 | WDT              | watchdog timer                                |

| MCU     | microcontroller unit                                | XRES             | external reset                                |

## **Reference Documents**

CY8CPLC20, CY8CLED16P01, CY8C29x66, CY8C27x43, CY8C24x94, CY8C24x23, CY8C24x23A, CY8C22x13, CY8C21x34, CY8C21x23, CY7C64215, CY7C603xx, CY8CNP1xx, and CYWUSB6953 PSoC® Programmable System-on-Chip Technical Reference Manual (TRM) (001-14463)

Design Aids – Reading and Writing PSoC<sup>®</sup> Flash – AN2015 (001-40459)

Application Notes for Surface Mount Assembly of Amkor's MicroLeadFrame (MLF) Packages – available at http://www.amkor.com.

## **Document Conventions**

#### Units of Measure

Table 54 lists the unit sof measures.

#### Table 54. Units of Measure

| Symbol | Unit of Measure | Symbol | Unit of Measure         |

|--------|-----------------|--------|-------------------------|

| kB     | 1024 bytes      | μs     | microsecond             |

| dB     | decibels        | ms     | millisecond             |

| °C     | degree Celsius  | ns     | nanosecond              |

| fF     | femto farad     | ps     | picosecond              |

| pF     | picofarad       | μV     | microvolts              |

| kHz    | kilohertz       | mV     | millivolts              |

| MHz    | megahertz       | mVpp   | millivolts peak-to-peak |

| rt-Hz  | root hertz      | nV     | nanovolts               |

| kΩ     | kilohm          | V      | volts                   |

| Ω      | ohm             | μW     | microwatts              |

| μA     | microampere     | W      | watt                    |

| mA     | milliampere     | mm     | millimeter              |

| nA     | nanoampere      | ppm    | parts per million       |

| pА     | pikoampere      | %      | percent                 |

| mH     | millihenry      |        | · ·                     |

#### **Numeric Conventions**

Hexadecimal numbers are represented with all letters in uppercase with an appended lowercase 'h' (for example, '14h' or '3Ah'). Hexadecimal numbers may also be represented by a '0x' prefix, the C coding convention. Binary numbers have an appended lowercase 'b' (for example, 01010100b' or '01000011b'). Numbers not indicated by an 'h' or 'b' are decimals.

#### Glossary

| active high                                   | 10.A logic signal having its asserted state as the logic 1 state.<br>11.A logic signal having the logic 1 state as the higher voltage of the two states.                                                                                                                                                                |

|-----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| analog blocks                                 | The basic programmable opamp circuits. These are SC (switched capacitor) and CT (continuous time) blocks. These blocks can be interconnected to provide ADCs, DACs, multi-pole filters, gain stages, and much more.                                                                                                     |

| analog-to-digital<br>(ADC)                    | A device that changes an analog signal to a digital signal of corresponding magnitude. Typically, an ADC converts a voltage to a digital number. The digital-to-analog (DAC) converter performs the reverse operation.                                                                                                  |

| API (Application<br>Programming<br>Interface) | A series of software routines that comprise an interface between a computer application and lower level services and functions (for example, user modules and libraries). APIs serve as building blocks for programmers that create software applications.                                                              |

| asynchronous                                  | A signal whose data is acknowledged or acted upon immediately, irrespective of any clock signal.                                                                                                                                                                                                                        |

| Bandgap<br>reference                          | A stable voltage reference design that matches the positive temperature coefficient of VT with the negative temperature coefficient of VBE, to produce a zero temperature coefficient (ideally) reference.                                                                                                              |

| bandwidth                                     | <ol> <li>The frequency range of a message or information processing system measured in hertz.</li> <li>The width of the spectral region over which an amplifier (or absorber) has substantial gain (or loss); it is<br/>sometimes represented more specifically as, for example, full width at half maximum.</li> </ol> |

## Glossary (continued)

| duty cycle                      | The relationship of a clock period high time to its low time, expressed as a percent.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|---------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| emulator                        | Duplicates (provides an emulation of) the functions of one system with a different system, so that the second system appears to behave like the first system.                                                                                                                                                                                                                                                                                                                                                                                                             |

| external reset<br>(XRES)        | An active high signal that is driven into the PSoC device. It causes all operation of the CPU and blocks to stop and return to a pre-defined state.                                                                                                                                                                                                                                                                                                                                                                                                                       |

| flash                           | An electrically programmable and erasable, non-volatile technology that provides users with the programmability and data storage of EPROMs, plus in-system erasability. Non-volatile means that the data is retained when power is off.                                                                                                                                                                                                                                                                                                                                   |

| Flash block                     | The smallest amount of Flash ROM space that may be programmed at one time and the smallest amount of Flash space that may be protected. A Flash block holds 64 bytes.                                                                                                                                                                                                                                                                                                                                                                                                     |