#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| 2014112                    |                                                                              |

|----------------------------|------------------------------------------------------------------------------|

| Product Status             | Active                                                                       |

| Core Processor             | M8C                                                                          |

| Core Size                  | 8-Bit                                                                        |

| Speed                      | 24MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                            |

| Peripherals                | POR, PWM, WDT                                                                |

| Number of I/O              | 24                                                                           |

| Program Memory Size        | 4KB (4K × 8)                                                                 |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | -                                                                            |

| RAM Size                   | 256 x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 2.4V ~ 5.25V                                                                 |

| Data Converters            | A/D 10x14b; D/A 2x9b                                                         |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                               |

| Supplier Device Package    | 28-SOIC                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/cy8c24423a-24sxit |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# More Information

Cypress provides a wealth of data at www.cypress.com to help you to select the right PSoC device for your design, and to help you to quickly and effectively integrate the device into your design. Following is an abbreviated list for PSoC 1:

- Overview: PSoC Portfolio, PSoC Roadmap

- Product Selectors: PSoC 1, PSoC 3, PSoC 4, or PSoC 5LP In addition, PSoC Designer offers a device selection tool within PSoC 1, at the time of creating a new project.

- Datasheets: Describe and provide electrical specifications for all the PSoC 1 family of devices. Visit the PSoC 1 datasheets web page for a complete list

- Application notes and code examples:

- □ Visit the PSoC 1 Code Examples web page for a comprehensive list of code examples

- Cypress offers a large number of PSoC application notes covering a broad range of topics, from basic to advanced level. Recommended application notes for getting started with PSoC 1 are:

- AN75320: Getting Started with PSoC® 1

- AN2094: PSoC<sup>®</sup> 1 Getting Started with GPIO

- AN2015: PSoC<sup>®</sup> 1 Getting Started with Flash & E2PROM

- AN2014: Basics of PSoC<sup>®</sup> 1 Programming

- AN32200: PSoC<sup>®</sup> 1 Clocks and Global Resources

- AN2010: PSoC<sup>®</sup> 1 Best Practices and Recommendations

- Technical Reference Manual (TRM):

- Visit the PSoC 1 TRM page for the complete list of TRMs. Following documents provide detailed descriptions of the Architecture, Programming specification and Register map details of CY8C2XXXX PSoC 1 device family. PSoC1 CY8C2XXXX TRM

- PSoC1 ISSP Programming Specifications

- Development Kits:

- CY3210 CY8C24x23 PSoC(R) Evaluation Pods (EvalPod) are 28-pin PDIP adapters that seamlessly connect any PSoC device to the 28-pin PDIP connector on any Cypress PSoC development kit. CY3210-24x23 provides evaluation of the CY8C24x23A PSoC device family on any PSoC developer kit. PSoC developer kits are sold separately.

- □ Visit the PSoC® 1 Kits page and refer the Kit Selector Guide document to find out the suitable development kits and debuggers for all PSoC 1 families.

- The CY3217-MiniProg1 and CY8CKIT-002 PSoC® MiniProg3 device provide an interface for flash programming.

- Knowledge Base Articles (KBA): Provide design and application tips from experts on the devices/kits. For example, Flash read/write access from firmware, explains how we can read and write to flash in PSoC 1 devices

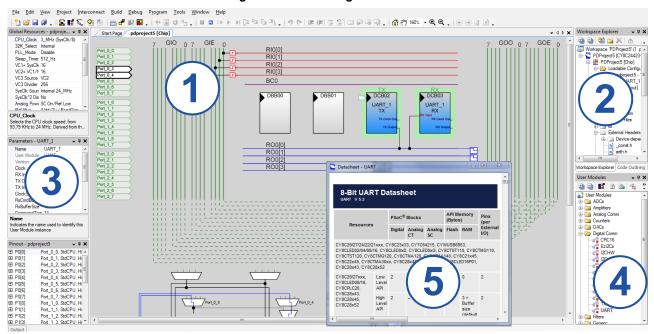

#### **PSoC Designer**

PSoC Designer is a free Windows-based Integrated Design Environment (IDE). It enables concurrent hardware and firmware design of systems based on CapSense (see Figure 1). With PSoC Designer, you can:

- 1. Drag and drop user modules to build your hardware system design in the main design workspace

- 2. Codesign your application firmware with the PSoC hardware, using the PSoC Designer IDE C compiler

- 3. Configure user module

- 4. Explore the library of user modules

- 5. Review user module datasheets

- - Figure 1. PSoC Designer Features

# **Getting Started**

For in depth information, along with detailed programming details, see the  $PSoC^{\textcircled{R}}$  Technical Reference Manual.

For up-to-date ordering, packaging, and electrical specification information, see the latest PSoC device datasheets on the web.

## **Application Notes**

Cypress application notes are an excellent introduction to the wide variety of possible PSoC designs.

### **Development Kits**

PSoC Development Kits are available online from and through a growing number of regional and global distributors, which include Arrow, Avnet, Digi-Key, Farnell, Future Electronics, and Newark.

### Training

Free PSoC technical training (on demand, webinars, and workshops), which is available online via www.cypress.com,

covers a wide variety of topics and skill levels to assist you in your designs.

## **CYPros Consultants**

Certified PSoC Consultants offer everything from technical assistance to completed PSoC designs. To contact or become a PSoC Consultant go to the CYPros Consultants web site.

### **Solutions Library**

Visit our growing library of solution focused designs. Here you can find various application designs that include firmware and hardware design files that enable you to complete your designs quickly.

#### **Technical Support**

Technical support – including a searchable knowledge base articles and technical forums – is also available online. If you cannot find an answer to your question, call our Technical Support hotline at 1-800-541-4736.

# **Register Reference**

This section lists the registers of the CY8C24x23A PSoC device. For detailed register information, see the PSoC Programmable Sytem-on-Chip Reference Manual.

## **Register Conventions**

#### Abbreviations Used

The register conventions specific to this section are listed in the following table.

#### Table 7. Abbreviations

| Convention | Description                  |

|------------|------------------------------|

| R          | Read register or bit(s)      |

| W          | Write register or bit(s)     |

| L          | Logical register or bit(s)   |

| С          | Clearable register or bit(s) |

| #          | Access is bit specific       |

## **Register Mapping Tables**

The PSoC device has a total register address space of 512 bytes. The register space is referred to as I/O space and is divided into two banks, Bank 0 and Bank 1. The XOI bit in the Flag register (CPU\_F) determines which bank the user is currently in. When the XOI bit is set, the user is in Bank 1.

**Note** In the following register mapping tables, blank fields are reserved and must not be accessed.

### DC Operational Amplifier Specifications

The following tables list the guaranteed maximum and minimum specifications for the voltage and temperature ranges: 4.75 V to 5.25 V and –40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C, 3.0 V to 3.6 V and –40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C, or 2.4 V to 3.0 V and –40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C, respectively. Typical parameters are measured at 5 V, 3.3 V, and 2.7 V at 25 °C and are for design guidance only.

The operational amplifier is a component of both the analog continuous time PSoC blocks and the Analog Switched Cap PSoC blocks. The guaranteed specifications are measured in the analog continuous time PSoC block. Typical parameters are measured at 5 V at 25 °C and are for design guidance only.

| Symbol               | Description                                                                                                                                                                                                                                                        | Min                                                | Тур                                       | Max                                       | Units                      | Notes                                                                                                                                                                                                     |

|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|-------------------------------------------|-------------------------------------------|----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>OSOA</sub>    | Input offset voltage (absolute value)<br>Power = low, Opamp bias = high<br>Power = medium, Opamp bias = high<br>Power = high, Opamp bias = high                                                                                                                    | -<br>-<br>-                                        | 1.6<br>1.3<br>1.2                         | 10<br>8<br>7.5                            | mV<br>mV<br>mV             |                                                                                                                                                                                                           |

| TCV <sub>OSOA</sub>  | Average input offset voltage drift                                                                                                                                                                                                                                 | -                                                  | 7.0                                       | 35.0                                      | µV/°C                      |                                                                                                                                                                                                           |

| I <sub>EBOA</sub>    | Input leakage current (port 0 analog pins)                                                                                                                                                                                                                         | -                                                  | 20                                        | -                                         | рА                         | Gross tested to 1 µA                                                                                                                                                                                      |

| C <sub>INOA</sub>    | Input capacitance (port 0 analog pins)                                                                                                                                                                                                                             | -                                                  | 4.5                                       | 9.5                                       | pF                         | Package and pin dependent.<br>Temp = 25 °C                                                                                                                                                                |

| V <sub>CMOA</sub>    | Common mode voltage range<br>Common mode voltage range (high power or high<br>Opamp bias)                                                                                                                                                                          | 0.0<br>0.5                                         | -                                         | V <sub>DD</sub><br>V <sub>DD</sub> – 0.5  | V                          | The common mode input voltage<br>range is measured through an<br>analog output buffer. The<br>specification includes the<br>limitations imposed by the<br>characteristics of the analog output<br>buffer. |

| G <sub>OLOA</sub>    | Open loop gain<br>Power = low, Opamp bias = high<br>Power = medium, Opamp bias = high<br>Power = high, Opamp bias = high                                                                                                                                           | 60<br>60<br>80                                     |                                           | -<br>-<br>-                               | dB<br>dB<br>dB             | Specification is applicable at high<br>Opamp bias. For low Opamp bias<br>mode, minimum is 60 dB.                                                                                                          |

| V <sub>OHIGHOA</sub> | High output voltage swing (internal signals)<br>Power = low, Opamp bias = high<br>Power = medium, Opamp bias = high<br>Power = high, Opamp bias = high                                                                                                             | $V_{DD} - 0.2$<br>$V_{DD} - 0.2$<br>$V_{DD} - 0.5$ |                                           | -<br>-<br>-                               | V<br>V<br>V                |                                                                                                                                                                                                           |

| V <sub>OLOWOA</sub>  | Low output voltage swing (internal signals)<br>Power = low, Opamp bias = high<br>Power = medium, Opamp bias = high<br>Power = high, Opamp bias = high                                                                                                              | -<br>-<br>-                                        |                                           | 0.2<br>0.2<br>0.5                         | V<br>V<br>V                |                                                                                                                                                                                                           |

| I <sub>SOA</sub>     | Supply current (including associated AGND buffer)<br>Power = low, Opamp bias = low<br>Power = low, Opamp bias = high<br>Power = medium, Opamp bias = low<br>Power = medium, Opamp bias = high<br>Power = high, Opamp bias = low<br>Power = high, Opamp bias = high | -<br>-<br>-<br>-<br>-                              | 150<br>300<br>600<br>1200<br>2400<br>4600 | 200<br>400<br>800<br>1600<br>3200<br>6400 | μΑ<br>μΑ<br>μΑ<br>μΑ<br>μΑ |                                                                                                                                                                                                           |

| PSRR <sub>OA</sub>   | Supply voltage rejection ratio                                                                                                                                                                                                                                     | 64                                                 | 80                                        | -                                         | dB                         | $V_{SS} \leq V_{IN} \leq (V_{DD} - 2.25) \text{ or } \\ (V_{DD} - 1.25 \text{ V}) \leq V_{IN} \leq V_{DD}$                                                                                                |

#### Table 14. 5-V DC Operational Amplifier Specifications

### DC Analog Output Buffer Specifications

The following tables list the guaranteed maximum and minimum specifications for the voltage and temperature ranges: 4.75 V to 5.25 V and –40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C, 3.0 V to 3.6 V and –40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C, or 2.4 V to 3.0 V and –40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C, respectively. Typical parameters are measured at 5 V, 3.3 V, and 2.7 V at 25 °C and are for design guidance only.

| Symbol               | Description                                                                                        | Min                                                        | Тур        | Max                                                       | Units    | Notes                                                                                                |

|----------------------|----------------------------------------------------------------------------------------------------|------------------------------------------------------------|------------|-----------------------------------------------------------|----------|------------------------------------------------------------------------------------------------------|

| CL                   | Load Capacitance                                                                                   | _                                                          | _          | 200                                                       | pF       | This specification applies to the external circuit that is being driven by the analog output buffer. |

| V <sub>OSOB</sub>    | Input offset voltage (absolute value)                                                              | -                                                          | 3          | 12                                                        | mV       |                                                                                                      |

| TCV <sub>OSOB</sub>  | Average input offset voltage drift                                                                 | -                                                          | +6         | -                                                         | μV/°C    |                                                                                                      |

| V <sub>CMOB</sub>    | Common mode input voltage range                                                                    | 0.5                                                        | -          | V <sub>DD</sub> – 1.0                                     | V        |                                                                                                      |

| R <sub>OUTOB</sub>   | Output resistance<br>Power = low<br>Power = high                                                   |                                                            | 1<br>1     |                                                           | W<br>W   |                                                                                                      |

| V <sub>OHIGHOB</sub> | High output voltage swing<br>(Load = 32 ohms to V <sub>DD/2</sub> )<br>Power = low<br>Power = high | 0.5 × V <sub>DD</sub> + 1.1<br>0.5 × V <sub>DD</sub> + 1.1 | -          |                                                           | V<br>V   |                                                                                                      |

| V <sub>OLOWOB</sub>  | Low output voltage swing<br>(Load = 32 ohms to V <sub>DD/2</sub> )<br>Power = low<br>Power = high  |                                                            | -          | .5 × V <sub>DD</sub> – 1.3<br>0.5 × V <sub>DD</sub> – 1.3 | V<br>V   |                                                                                                      |

| I <sub>SOB</sub>     | Supply current including Opamp bias<br>cell<br>(No Load)<br>Power = low<br>Power = high            |                                                            | 1.1<br>2.6 | 5.1<br>8.8                                                | mA<br>mA |                                                                                                      |

| PSRR <sub>OB</sub>   | Supply voltage rejection ratio                                                                     | 52                                                         | 64         | -                                                         | dB       | V <sub>OUT</sub> > (V <sub>DD</sub> – 1.25)                                                          |

### Table 19. 3.3-V DC Analog Output Buffer Specifications

| Symbol               | Description                                                                               | Min                                                        | Тур        | Max                                                        | Units           | Notes                                                                                                |

|----------------------|-------------------------------------------------------------------------------------------|------------------------------------------------------------|------------|------------------------------------------------------------|-----------------|------------------------------------------------------------------------------------------------------|

| CL                   | Load Capacitance                                                                          | -                                                          | -          | 200                                                        | pF              | This specification applies to the external circuit that is being driven by the analog output buffer. |

| V <sub>OSOB</sub>    | Input offset voltage (absolute value)                                                     | —                                                          | 3          | 12                                                         | mV              |                                                                                                      |

| TCV <sub>OSOB</sub>  | Average input offset voltage drift                                                        | -                                                          | +6         | -                                                          | μV/°C           |                                                                                                      |

| V <sub>CMOB</sub>    | Common mode input voltage range                                                           | 0.5                                                        | -          | V <sub>DD</sub> – 1.0                                      | V               |                                                                                                      |

| R <sub>OUTOB</sub>   | Output resistance<br>Power = low<br>Power = high                                          |                                                            | 1<br>1     |                                                            | $\Omega \Omega$ |                                                                                                      |

| V <sub>OHIGHOB</sub> | High output voltage swing (Load = 1 K ohms to $V_{DD/2}$ )<br>Power = Iow<br>Power = high | 0.5 × V <sub>DD</sub> + 1.0<br>0.5 × V <sub>DD</sub> + 1.0 |            |                                                            | V<br>V          |                                                                                                      |

| V <sub>OLOWOB</sub>  | Low output voltage swing (Load = 1 K ohms to $V_{DD/2}$ )<br>Power = low<br>Power = high  |                                                            | -          | 0.5 × V <sub>DD</sub> – 1.0<br>0.5 × V <sub>DD</sub> – 1.0 | V<br>V          |                                                                                                      |

| I <sub>SOB</sub>     | Supply current including Opamp bias<br>cell<br>(no load)<br>Power = low<br>Power = high   | -<br>-                                                     | 0.8<br>2.0 | 2.0<br>4.3                                                 | mA<br>mA        |                                                                                                      |

| PSRR <sub>OB</sub>   | Supply voltage rejection ratio                                                            | 52                                                         | 64         | -                                                          | dB              | V <sub>OUT</sub> > (V <sub>DD</sub> - 1.25)                                                          |

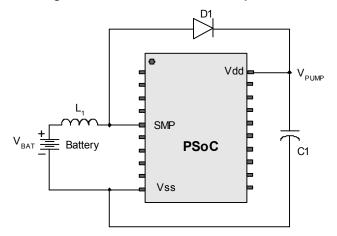

## Figure 10. Basic Switch Mode Pump Circuit

# Table 22. 5-V DC Analog Reference Specifications (continued)

| Reference<br>ARF_CR<br>[5:3] | Reference Power<br>Settings            | Symbol             | Reference | Description                                     | Min             | Тур                     | Max                     | Units |

|------------------------------|----------------------------------------|--------------------|-----------|-------------------------------------------------|-----------------|-------------------------|-------------------------|-------|

| 0b101                        | RefPower = high<br>Opamp bias = high   | V <sub>REFHI</sub> | Ref High  | P2[4] + Bandgap<br>(P2[4] = V <sub>DD</sub> /2) | P2[4] + 1.228   | P2[4] + 1.284           | P2[4] + 1.332           | V     |

|                              |                                        | V <sub>AGND</sub>  | AGND      | P2[4]                                           | P2[4]           | P2[4]                   | P2[4]                   | -     |

|                              |                                        | V <sub>REFLO</sub> | Ref Low   | P2[4] – Bandgap<br>(P2[4] = V <sub>DD</sub> /2) | P2[4] – 1.358   | P2[4] – 1.293           | P2[4] – 1.226           | V     |

|                              | RefPower = high<br>Opamp bias = low    | V <sub>REFHI</sub> | Ref High  | P2[4] + Bandgap<br>(P2[4] = V <sub>DD</sub> /2) | P2[4] + 1.236   | P2[4] + 1.289           | P2[4] + 1.332           | V     |

|                              |                                        | V <sub>AGND</sub>  | AGND      | P2[4]                                           | P2[4]           | P2[4]                   | P2[4]                   | -     |

|                              |                                        | V <sub>REFLO</sub> | Ref Low   | P2[4] – Bandgap<br>(P2[4] = V <sub>DD</sub> /2) | P2[4] – 1.357   | P2[4] – 1.297           | P2[4] – 1.229           | V     |

|                              | RefPower = medium<br>Opamp bias = high | V <sub>REFHI</sub> | Ref High  | P2[4] + Bandgap<br>(P2[4] = V <sub>DD</sub> /2) | P2[4] + 1.237   | P2[4] + 1.291           | P2[4] + 1.337           | V     |

|                              |                                        | V <sub>AGND</sub>  | AGND      | P2[4]                                           | P2[4]           | P2[4]                   | P2[4]                   | -     |

|                              |                                        | V <sub>REFLO</sub> | Ref Low   | P2[4] – Bandgap<br>(P2[4] = V <sub>DD</sub> /2) | P2[4] – 1.356   | P2[4] – 1.299           | P2[4] – 1.232           | V     |

|                              | RefPower = medium<br>Opamp bias = low  | V <sub>REFHI</sub> | Ref High  | P2[4] + Bandgap<br>(P2[4] = V <sub>DD</sub> /2) | P2[4] + 1.237   | P2[4] + 1.292           | P2[4] + 1.337           | V     |

|                              |                                        | V <sub>AGND</sub>  | AGND      | P2[4]                                           | P2[4]           | P2[4]                   | P2[4]                   | -     |

|                              |                                        | V <sub>REFLO</sub> | Ref Low   | P2[4] – Bandgap<br>(P2[4] = V <sub>DD</sub> /2) | P2[4] – 1.357   | P2[4] – 1.300           | P2[4] – 1.233           | V     |

| 0b110                        | RefPower = high                        | V <sub>REFHI</sub> | Ref High  | 2 × Bandgap                                     | 2.512           | 2.594                   | 2.654                   | V     |

|                              | Opamp bias = high                      | V <sub>AGND</sub>  | AGND      | Bandgap                                         | 1.250           | 1.303                   | 1.346                   | V     |

|                              |                                        | V <sub>REFLO</sub> | Ref Low   | V <sub>SS</sub>                                 | V <sub>SS</sub> | V <sub>SS</sub> + 0.011 | V <sub>SS</sub> + 0.027 | V     |

|                              | RefPower = high                        | V <sub>REFHI</sub> | Ref High  | 2 × Bandgap                                     | 2.515           | 2.592                   | 2.654                   | V     |

|                              | Opamp bias = low                       | V <sub>AGND</sub>  | AGND      | Bandgap                                         | 1.253           | 1.301                   | 1.340                   | V     |

|                              |                                        | V <sub>REFLO</sub> | Ref Low   | V <sub>SS</sub>                                 | V <sub>SS</sub> | V <sub>SS</sub> + 0.006 | V <sub>SS</sub> + 0.02  | V     |

|                              | RefPower = medium                      | V <sub>REFHI</sub> | Ref High  | 2 × Bandgap                                     | 2.518           | 2.593                   | 2.651                   | V     |

|                              | Opamp bias = high                      | V <sub>AGND</sub>  | AGND      | Bandgap                                         | 1.254           | 1.301                   | 1.338                   | V     |

|                              |                                        | V <sub>REFLO</sub> | Ref Low   | V <sub>SS</sub>                                 | V <sub>SS</sub> | V <sub>SS</sub> + 0.004 | V <sub>SS</sub> + 0.017 | V     |

|                              | RefPower = medium                      | V <sub>REFHI</sub> | Ref High  | 2 × Bandgap                                     | 2.517           | 2.594                   | 2.650                   | V     |

|                              | Opamp bias = low                       | V <sub>AGND</sub>  | AGND      | Bandgap                                         | 1.255           | 1.300                   | 1.337                   | V     |

|                              |                                        | V <sub>REFLO</sub> | Ref Low   | V <sub>SS</sub>                                 | V <sub>SS</sub> | V <sub>SS</sub> + 0.003 | V <sub>SS</sub> + 0.015 | V     |

| 0b111                        | RefPower = high                        | V <sub>REFHI</sub> | Ref High  | 3.2 × Bandgap                                   | 4.011           | 4.143                   | 4.203                   | V     |

|                              | Opamp bias = high                      | V <sub>AGND</sub>  | AGND      | 1.6 × Bandgap                                   | 2.020           | 2.075                   | 2.118                   | V     |

|                              |                                        | V <sub>REFLO</sub> | Ref Low   | V <sub>SS</sub>                                 | V <sub>SS</sub> | V <sub>SS</sub> + 0.011 | V <sub>SS</sub> + 0.026 | V     |

|                              | RefPower = high                        | V <sub>REFHI</sub> | Ref High  | 3.2 × Bandgap                                   | 4.022           | 4.138                   | 4.203                   | V     |

|                              | Opamp bias = low                       | V <sub>AGND</sub>  | AGND      | 1.6 × Bandgap                                   | 2.023           | 2.075                   | 2.114                   | V     |

|                              |                                        | V <sub>REFLO</sub> | Ref Low   | V <sub>SS</sub>                                 | V <sub>SS</sub> | V <sub>SS</sub> + 0.006 | V <sub>SS</sub> + 0.017 | V     |

|                              | RefPower = medium                      | V <sub>REFHI</sub> | Ref High  | 3.2 × Bandgap                                   | 4.026           | 4.141                   | 4.207                   | V     |

|                              | Opamp bias = high                      | V <sub>AGND</sub>  | AGND      | 1.6 × Bandgap                                   | 2.024           | 2.075                   | 2.114                   | V     |

|                              |                                        | V <sub>REFLO</sub> | Ref Low   | V <sub>SS</sub>                                 | V <sub>SS</sub> | V <sub>SS</sub> + 0.004 | V <sub>SS</sub> + 0.015 | V     |

|                              | RefPower = medium                      | V <sub>REFHI</sub> | Ref High  | 3.2 × Bandgap                                   | 4.030           | 4.143                   | 4.206                   | V     |

|                              | Opamp bias = low                       | V <sub>AGND</sub>  | AGND      | 1.6 × Bandgap                                   | 2.024           | 2.076                   | 2.112                   | V     |

|                              |                                        | V <sub>REFLO</sub> | Ref Low   | V <sub>SS</sub>                                 | V <sub>SS</sub> | V <sub>SS</sub> + 0.003 | V <sub>SS</sub> + 0.013 | V     |

## Table 23. 3.3-V DC Analog Reference Specifications

| Reference<br>ARF_CR<br>[5:3] | Reference Power<br>Settings                | Symbol                                  | Reference | Description                                                | Min                        | Тур                        | Max                        | Units |

|------------------------------|--------------------------------------------|-----------------------------------------|-----------|------------------------------------------------------------|----------------------------|----------------------------|----------------------------|-------|

| 0b000                        | RefPower = high                            | V <sub>REFHI</sub>                      | Ref High  | V <sub>DD</sub> /2 + Bandgap                               | V <sub>DD</sub> /2 + 1.170 | V <sub>DD</sub> /2 + 1.288 | V <sub>DD</sub> /2 + 1.376 | V     |

|                              | Opamp bias = high                          |                                         | AGND      | V <sub>DD</sub> /2                                         | V <sub>DD</sub> /2-0.098   | $V_{DD}/2 + 0.003$         | V <sub>DD</sub> /2 + 0.097 | V     |

|                              |                                            | V <sub>AGND</sub><br>V <sub>REFLO</sub> | Ref Low   | V <sub>DD</sub> /2 – Bandgap                               | V <sub>DD</sub> /2-1.386   | V <sub>DD</sub> /2 – 1.287 | V <sub>DD</sub> /2 – 1.169 | V     |

|                              | RefPower = high                            | V <sub>REFHI</sub>                      | Ref High  | V <sub>DD</sub> /2 + Bandgap                               | V <sub>DD</sub> /2 + 1.210 | V <sub>DD</sub> /2 + 1.290 | V <sub>DD</sub> /2 + 1.355 | V     |

|                              | Opamp bias = low                           | V <sub>AGND</sub>                       | AGND      | V <sub>DD</sub> /2                                         | $V_{DD}/2 - 0.055$         | V <sub>DD</sub> /2 + 0.001 | V <sub>DD</sub> /2 + 0.054 | V     |

|                              |                                            | V <sub>REFLO</sub>                      | Ref Low   | V <sub>DD</sub> /2 – Bandgap                               | V <sub>DD</sub> /2-1.359   | V <sub>DD</sub> /2 – 1.292 | V <sub>DD</sub> /2 – 1.214 | V     |

|                              | RefPower = medium                          | V <sub>REFHI</sub>                      | Ref High  | V <sub>DD</sub> /2 + Bandgap                               | 22                         | V <sub>DD</sub> /2 + 1.292 | V <sub>DD</sub> /2 + 1.368 | V     |

|                              | Opamp bias = high                          | V <sub>AGND</sub>                       | AGND      | V <sub>DD</sub> /2                                         | $V_{DD}/2 - 0.041$         | V <sub>DD</sub> /2         | V <sub>DD</sub> /2 + 0.04  | V     |

|                              |                                            | V <sub>REFLO</sub>                      | Ref Low   | V <sub>DD</sub> /2 – Bandgap                               | $V_{DD}/2 - 1.362$         | 66                         | V <sub>DD</sub> /2 – 1.220 | V     |

|                              | RefPower = medium                          | V <sub>REFHI</sub>                      | Ref High  | V <sub>DD</sub> /2 + Bandgap                               | V <sub>DD</sub> /2 + 1.202 | V <sub>DD</sub> /2 + 1.292 | V <sub>DD</sub> /2 + 1.364 | V     |

|                              | Opamp bias = low                           | V <sub>AGND</sub>                       | AGND      | V <sub>DD</sub> /2                                         | $V_{DD}/2 - 0.033$         | V <sub>DD</sub> /2         | $V_{DD}/2 + 0.030$         | V     |

|                              |                                            | V <sub>REFLO</sub>                      | Ref Low   | V <sub>DD</sub> /2 – Bandgap                               | V <sub>DD</sub> /2-1.364   | V <sub>DD</sub> /2 – 1.297 | V <sub>DD</sub> /2 – 1.222 | V     |

| 0b001                        | RefPower = high<br>Opamp bias = high       | V <sub>REFHI</sub>                      | Ref High  | P2[4]+P2[6] (P2[4] =<br>V <sub>DD</sub> /2, P2[6] = 0.5 V) | P2[4] + P2[6]<br>- 0.072   | P2[4]+P2[6]-<br>0.017      | P2[4]+P2[6]+<br>0.041      | V     |

|                              |                                            | V <sub>AGND</sub>                       | AGND      | P2[4]                                                      | P2[4]                      | P2[4]                      | P2[4]                      | -     |

|                              |                                            | V <sub>REFLO</sub>                      | Ref Low   | P2[4]–P2[6] (P2[4] =<br>V <sub>DD</sub> /2, P2[6] = 0.5 V) | P2[4] – P2[6]<br>– 0.029   | P2[4]-P2[6]+<br>0.010      | P2[4]-P2[6]+<br>0.048      | V     |

|                              | RefPower = high<br>Opamp bias = low        | V <sub>REFHI</sub>                      | Ref High  | P2[4]+P2[6] (P2[4] =<br>V <sub>DD</sub> /2, P2[6] = 0.5 V) | P2[4] + P2[6]<br>- 0.066   | P2[4] + P2[6] –<br>0.010   | P2[4]+P2[6]+<br>0.043      | V     |

|                              |                                            | V <sub>AGND</sub>                       | AGND      | P2[4]                                                      | P2[4]                      | P2[4]                      | P2[4]                      | -     |

|                              |                                            | V <sub>REFLO</sub>                      | Ref Low   | P2[4]–P2[6] (P2[4] =<br>V <sub>DD</sub> /2, P2[6] = 0.5 V) | P2[4] – P2[6]<br>– 0.024   | P2[4]-P2[6]+<br>0.004      | P2[4]-P2[6]+<br>0.034      | V     |

|                              | RefPower = medium<br>Opamp bias = high     | V <sub>REFHI</sub>                      | Ref High  | P2[4]+P2[6] (P2[4] =<br>V <sub>DD</sub> /2, P2[6] = 0.5 V) | P2[4] + P2[6]<br>- 0.073   | P2[4]+P2[6]-<br>0.007      | P2[4]+P2[6]+<br>0.053      | V     |

|                              |                                            | V <sub>AGND</sub>                       | AGND      | P2[4]                                                      | P2[4]                      | P2[4]                      | P2[4]                      | -     |

|                              |                                            | V <sub>REFLO</sub>                      | Ref Low   | P2[4]–P2[6] (P2[4] =<br>V <sub>DD</sub> /2, P2[6] = 0.5 V) | P2[4] – P2[6]<br>– 0.028   | P2[4]-P2[6]+<br>0.002      | P2[4]-P2[6]+<br>0.033      | V     |

|                              | RefPower = medium<br>Opamp bias = low      | V <sub>REFHI</sub>                      | Ref High  | P2[4]+P2[6] (P2[4] =<br>V <sub>DD</sub> /2, P2[6] = 0.5 V) | P2[4] + P2[6]<br>- 0.073   | P2[4] + P2[6] -<br>0.006   | P2[4] + P2[6] +<br>0.056   | V     |

|                              |                                            | V <sub>AGND</sub>                       | AGND      | P2[4]                                                      | P2[4]                      | P2[4]                      | P2[4]                      | -     |

|                              |                                            | V <sub>REFLO</sub>                      | Ref Low   | P2[4]–P2[6] (P2[4] =<br>V <sub>DD</sub> /2, P2[6] = 0.5 V) | P2[4] – P2[6]<br>– 0.030   | P2[4] – P2[6]              | P2[4]-P2[6]+<br>0.032      | V     |

| 0b010                        | RefPower = high<br>Opamp bias = high       | V <sub>REFHI</sub>                      | Ref High  | V <sub>DD</sub>                                            | V <sub>DD</sub> – 0.102    | V <sub>DD</sub> – 0.003    | V <sub>DD</sub>            | V     |

|                              | Opartip blas – flight                      | V <sub>AGND</sub>                       | AGND      | V <sub>DD</sub> /2                                         |                            | $V_{DD}/2 + 0.001$         |                            | V     |

|                              |                                            | V <sub>REFLO</sub>                      | Ref Low   | V <sub>SS</sub>                                            | V <sub>SS</sub>            | V <sub>SS</sub> + 0.005    | V <sub>SS</sub> + 0.020    | V     |

|                              | RefPower = high                            | V <sub>REFHI</sub>                      | Ref High  | V <sub>DD</sub>                                            | V <sub>DD</sub> – 0.082    | V <sub>DD</sub> – 0.002    | V <sub>DD</sub>            | V     |

|                              | Opamp bias = low                           | V <sub>AGND</sub>                       | AGND      | V <sub>DD</sub> /2                                         | $V_{DD}/2 - 0.031$         | V <sub>DD</sub> /2         | $V_{DD}/2 + 0.028$         | V     |

|                              |                                            | V <sub>REFLO</sub>                      | Ref Low   | V <sub>SS</sub>                                            | V <sub>SS</sub>            | V <sub>SS</sub> + 0.003    | V <sub>SS</sub> + 0.015    | V     |

|                              | RefPower = medium<br>Opamp bias = high     | V <sub>REFHI</sub>                      | Ref High  | V <sub>DD</sub>                                            | V <sub>DD</sub> – 0.083    | V <sub>DD</sub> – 0.002    | V <sub>DD</sub>            | V     |

|                              | Cpainp bias - night                        | V <sub>AGND</sub>                       | AGND      | V <sub>DD</sub> /2                                         | $V_{DD}/2 - 0.032$         | V <sub>DD</sub> /2 – 0.001 | $V_{DD}/2 + 0.029$         | V     |

|                              |                                            | V <sub>REFLO</sub>                      | Ref Low   | V <sub>SS</sub>                                            | V <sub>SS</sub>            | V <sub>SS</sub> + 0.002    | V <sub>SS</sub> + 0.014    | V     |

|                              | RefPower = medium<br>Opamp bias = low      | V <sub>REFHI</sub>                      | Ref High  | V <sub>DD</sub>                                            | V <sub>DD</sub> – 0.081    | V <sub>DD</sub> – 0.002    | V <sub>DD</sub>            | V     |

|                              |                                            | V <sub>AGND</sub>                       | AGND      | V <sub>DD</sub> /2                                         | $V_{DD}/2 - 0.033$         | = =                        | $V_{DD}/2 + 0.029$         | V     |

|                              |                                            | V <sub>REFLO</sub>                      | Ref Low   | V <sub>SS</sub>                                            | V <sub>SS</sub>            | V <sub>SS</sub> + 0.002    | V <sub>SS</sub> + 0.013    | V     |

| 0b011                        | All power settings<br>Not allowed at 3.3 V | _                                       | _         | -                                                          | -                          | _                          | -                          | _     |

| Reference<br>ARF_CR<br>[5:3] | Reference Power<br>Settings                | Symbol             | Reference | Description     | Min             | Тур                     | Мах                     | Units |

|------------------------------|--------------------------------------------|--------------------|-----------|-----------------|-----------------|-------------------------|-------------------------|-------|

| 0b011                        | All power settings<br>Not allowed at 2.7 V | -                  | -         | -               | -               | -                       | -                       | -     |

| 0b100                        | All power settings<br>Not allowed at 2.7 V | -                  | _         | -               | -               | -                       | _                       | -     |

| 0b101                        | All power settings<br>Not allowed at 2.7 V | -                  | _         | -               | -               | -                       | _                       | -     |

| 0b110                        | RefPower = high                            | V <sub>REFHI</sub> | Ref High  | 2 × Bandgap     | Not allowed     | Not allowed             | Not allowed             | V     |

|                              | Opamp bias = high                          | V <sub>AGND</sub>  | AGND      | Bandgap         | 1.160           | 1.302                   | 1.340                   | V     |

|                              |                                            | V <sub>REFLO</sub> | Ref Low   | V <sub>SS</sub> | V <sub>SS</sub> | V <sub>SS</sub> + 0.007 | V <sub>SS</sub> + 0.025 | V     |

|                              | RefPower = high                            | V <sub>REFHI</sub> | Ref High  | 2 × Bandgap     | Not allowed     | Not allowed             | Not allowed             | V     |

|                              | Opamp bias = low                           | V <sub>AGND</sub>  | AGND      | Bandgap         | 1.160           | 1.301                   | 1.338                   | V     |

|                              |                                            | V <sub>REFLO</sub> | Ref Low   | V <sub>SS</sub> | V <sub>SS</sub> | V <sub>SS</sub> + 0.004 | V <sub>SS</sub> + 0.017 | V     |

|                              | RefPower = medium                          | V <sub>REFHI</sub> | Ref High  | 2 × Bandgap     | Not allowed     | Not allowed             | Not allowed             | V     |

|                              | Opamp bias = high                          | V <sub>AGND</sub>  | AGND      | Bandgap         | 1.160           | 1.301                   | 1.338                   | V     |

|                              |                                            | V <sub>REFLO</sub> | Ref Low   | V <sub>SS</sub> | V <sub>SS</sub> | V <sub>SS</sub> + 0.003 | V <sub>SS</sub> + 0.013 | V     |

|                              | RefPower = medium                          | V <sub>REFHI</sub> | Ref High  | 2 × Bandgap     | Not allowed     | Not allowed             | Not allowed             | V     |

|                              | Opamp bias = low                           | V <sub>AGND</sub>  | AGND      | Bandgap         | 1.160           | 1.300                   | 1.337                   | V     |

|                              |                                            | V <sub>REFLO</sub> | Ref Low   | V <sub>SS</sub> | V <sub>SS</sub> | V <sub>SS</sub> + 0.002 | V <sub>SS</sub> + 0.011 | V     |

|                              | RefPower = low                             | V <sub>REFHI</sub> | Ref High  | 2 × Bandgap     | Not allowed     | Not allowed             | Not allowed             | V     |

|                              | Opamp bias = high                          | V <sub>AGND</sub>  | AGND      | Bandgap         | 1.252           | 1.300                   | 1.339                   | V     |

|                              |                                            | V <sub>REFLO</sub> | Ref Low   | V <sub>SS</sub> | V <sub>SS</sub> | V <sub>SS</sub> + 0.002 | V <sub>SS</sub> + 0.011 | V     |

|                              | RefPower = low                             | V <sub>REFHI</sub> | Ref High  | 2 × Bandgap     | Not allowed     | Not allowed             | Not allowed             | V     |

|                              | Opamp bias = low                           | V <sub>AGND</sub>  | AGND      | Bandgap         | 1.252           | 1.300                   | 1.339                   | V     |

|                              |                                            | V <sub>REFLO</sub> | Ref Low   | V <sub>SS</sub> | V <sub>SS</sub> | V <sub>SS</sub> + 0.001 | V <sub>SS</sub> + 0.01  | V     |

| 0b111                        | All power settings<br>Not allowed at 2.7 V | -                  | -         | -               | -               | -                       | -                       | -     |

### Table 24. 2.7-V DC Analog Reference Specifications (continued) (continued)

### DC Analog PSoC Block Specifications

Table 23 lists the guaranteed maximum and minimum specifications for the voltage and temperature ranges: 4.75 V to 5.25 V and -40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C, 3.0 V to 3.6 V and -40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C, or 2.4 V to 3.0 V and -40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C, respectively. Typical parameters are measured at 5 V, 3.3 V, and 2.7 V at 25 °C and are for design guidance only.

#### Table 25. DC Analog PSoC Block Specifications

| Symbol          | Description                               | Min | Тур  | Max | Units | Notes |

|-----------------|-------------------------------------------|-----|------|-----|-------|-------|

| R <sub>CT</sub> | Resistor unit value (continuous time)     | -   | 12.2 | -   | kΩ    |       |

| C <sub>SC</sub> | Capacitor unit value (switched capacitor) | -   | 80   | _   | fF    |       |

#### Table 30. 2.7-V AC Chip-Level Specifications

| Symbol                               | Description                                             | Min   | Тур | Мах                      | Units | Notes                                                                                                                                                                               |

|--------------------------------------|---------------------------------------------------------|-------|-----|--------------------------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| F <sub>IMO12</sub>                   | IMO frequency for 12 MHz                                | 11.5  | 12  | 12.7 <sup>[27, 28]</sup> | MHz   | Trimmed for 2.7 V operation using factory trim values.<br>See Figure 8 on page 18.<br>SLIMO mode = 1.                                                                               |

| F <sub>IMO6</sub>                    | IMO frequency for 6 MHz                                 | 5.5   | 6   | 6.5 <sup>[27, 28]</sup>  | MHz   | Trimmed for 2.7 V operation using factory trim values.<br>See Figure 8 on page 18.<br>SLIMO mode = 1.                                                                               |

| F <sub>CPU1</sub>                    | CPU frequency (2.7 V nominal)                           | 0.937 | 3   | 3.15 <sup>[27]</sup>     | MHz   | SLIMO mode = 0.                                                                                                                                                                     |

| F <sub>BLK27</sub>                   | Digital PSoC block frequency (2.7 V nominal)            | 0     | 12  | 12.7 <sup>[27, 28]</sup> | MHz   | Refer to the AC Digital Block<br>Specifications.                                                                                                                                    |

| F <sub>32K1</sub>                    | ILO frequency                                           | 8     | 32  | 96                       | kHz   |                                                                                                                                                                                     |

| F <sub>32K_U</sub>                   | ILO untrimmed frequency                                 | 5     | -   | 100                      | kHz   | After a reset and before the M8C<br>starts to run, the ILO is not trimmed.<br>See the System Resets section of<br>the PSoC Technical Reference<br>Manual for details on timing this |

| t <sub>XRST</sub>                    | External reset pulse width                              | 10    | -   | -                        | μs    |                                                                                                                                                                                     |

| DC12M                                | 12 MHz duty cycle                                       | 40    | 50  | 60                       | %     |                                                                                                                                                                                     |

| DC <sub>ILO</sub>                    | ILO duty cycle                                          | 20    | 50  | 80                       | %     |                                                                                                                                                                                     |

| F <sub>MAX</sub>                     | Maximum frequency of signal on row input or row output. | -     | -   | 12.7                     | MHz   |                                                                                                                                                                                     |

| SR <sub>POWER_UP</sub>               | Power supply slew rate                                  | -     | -   | 250                      | V/ms  | V <sub>DD</sub> slew rate during power-up.                                                                                                                                          |

| t <sub>POWERUP</sub>                 | Time from end of POR to CPU executing code              | -     | 16  | 100                      | ms    | Power-up from 0 V. See the System<br>Resets section of the PSoC<br>Technical Reference Manual.                                                                                      |

| t <sub>jit_IMO</sub> <sup>[29]</sup> | 12 MHz IMO cycle-to-cycle jitter (RMS)                  | _     | 400 | 1000                     | ps    | N = 32                                                                                                                                                                              |

|                                      | 12 MHz IMO long term N cycle-to-cycle jitter (RMS)      | -     | 600 | 1300                     | ps    |                                                                                                                                                                                     |

|                                      | 12 MHz IMO period jitter (RMS)                          | -     | 100 | 500                      | ps    |                                                                                                                                                                                     |

| t <sub>jit_PLL</sub> <sup>[29]</sup> | 12 MHz IMO cycle-to-cycle jitter (RMS)                  | _     | 400 | 1000                     | ps    | N = 32                                                                                                                                                                              |

|                                      | 12 MHz IMO long term N cycle-to-cycle jitter (RMS)      | -     | 700 | 1300                     |       |                                                                                                                                                                                     |

|                                      | 12 MHz IMO period jitter (RMS)                          | -     | 300 | 500                      |       |                                                                                                                                                                                     |

Notes 27. 2.4 V < V<sub>DD</sub> < 3.0 V. 28. Refer to application note Adjusting PSoC<sup>®</sup> Trims for 3.3 V and 2.7 V Operation – AN2012 for information on trimming for operation at 3.3 V. 29. Refer to Cypress Jitter Specifications application note, Understanding Datasheet Jitter Specifications for Cypress Timing Products – AN5054 for more information.

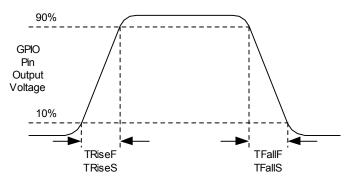

## AC GPIO Specifications

These tables list the guaranteed maximum and minimum specifications for the voltage and temperature ranges: 4.75 V to 5.25 V and -40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C, 3.0 V to 3.6 V and -40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C, or 2.4 V to 3.0 V and -40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C, respectively. Typical parameters are measured at 5 V, 3.3 V, and 2.7 V at 25 °C and are for design guidance only.

| Table 31. | 5-V and 3.3-V | AC GPIO | Specifications |

|-----------|---------------|---------|----------------|

|-----------|---------------|---------|----------------|

| Symbol            | Description                                  | Min | Тур | Max | Units | Notes                                       |

|-------------------|----------------------------------------------|-----|-----|-----|-------|---------------------------------------------|

| F <sub>GPIO</sub> | GPIO operating frequency                     | 0   | -   | 12  | MHz   | Normal Strong Mode                          |

| tRiseF            | Rise time, normal strong mode, Cload = 50 pF | 3   | -   | 18  | ns    | V <sub>DD</sub> = 4.5 to 5.25 V, 10% to 90% |

| tFallF            | Fall time, normal strong mode, Cload = 50 pF | 2   | -   | 18  | ns    | V <sub>DD</sub> = 4.5 to 5.25 V, 10% to 90% |

| tRiseS            | Rise time, slow strong mode, Cload = 50 pF   | 10  | 27  | -   | ns    | V <sub>DD</sub> = 3 to 5.25 V, 10% to 90%   |

| tFallS            | Fall time, slow strong mode, Cload = 50 pF   | 10  | 22  | -   | ns    | V <sub>DD</sub> = 3 to 5.25 V, 10% to 90%   |

Table 32. 2.7-V AC GPIO Specifications

| Symbol            | Description                                  | Min | Тур | Max | Units | Notes                                      |

|-------------------|----------------------------------------------|-----|-----|-----|-------|--------------------------------------------|

| F <sub>GPIO</sub> | GPIO operating frequency                     | 0   | -   | 3   | MHz   | Normal strong mode                         |

| tRiseF            | Rise time, normal strong mode, Cload = 50 pF | 6   | -   | 50  | ns    | V <sub>DD</sub> = 2.4 to 3.0 V, 10% to 90% |

| tFallF            | Fall time, normal strong mode, Cload = 50 pF | 6   | -   | 50  | ns    | V <sub>DD</sub> = 2.4 to 3.0 V, 10% to 90% |

| tRiseS            | Rise time, slow strong mode, Cload = 50 pF   | 18  | 40  | 120 | ns    | V <sub>DD</sub> = 2.4 to 3.0 V, 10% to 90% |

| tFallS            | Fall time, slow strong mode, Cload = 50 pF   | 18  | 40  | 120 | ns    | V <sub>DD</sub> = 2.4 to 3.0 V, 10% to 90% |

## Figure 0-1. GPIO Timing Diagram

#### AC Operational Amplifier Specifications

The following tables list the guaranteed maximum and minimum specifications for the voltage and temperature ranges: 4.75 V to 5.25 V and –40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C, 3.0 V to 3.6 V and –40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C, or 2.4 V to 3.0 V and –40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C, respectively. Typical parameters are measured at 5 V, 3.3 V, and 2.7 V at 25 °C and are for design guidance only.

Settling times, slew rates, and gain bandwidth are based on the analog continuous time PSoC block.

Power = high and Opamp bias = high is not supported at 3.3 V and 2.7 V.

| Table 33. | 5-V AC O | perational Am | plifier S | pecifications |

|-----------|----------|---------------|-----------|---------------|

|-----------|----------|---------------|-----------|---------------|

| Symbol            | Description                                                                                                                                                                                             | Min                | Тур         | Max                 | Units                |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-------------|---------------------|----------------------|

| t <sub>ROA</sub>  | Rising settling time from 80% of $\Delta V$ to 0.1% of $\Delta V$<br>(10 pF load, unity gain)<br>Power = low, Opamp bias = low<br>Power = medium, Opamp bias = high<br>Power = high, Opamp bias = high  |                    |             | 3.9<br>0.72<br>0.62 | μs<br>μs<br>μs       |

| t <sub>SOA</sub>  | Falling settling time from 20% of $\Delta V$ to 0.1% of $\Delta V$<br>(10 pF load, unity gain)<br>Power = low, Opamp bias = low<br>Power = medium, Opamp bias = high<br>Power = high, Opamp bias = high | -<br>-<br>-        |             | 5.9<br>0.92<br>0.72 | μs<br>μs<br>μs       |

| SR <sub>ROA</sub> | Rising slew rate (20% to 80%) (10 pF load, unity gain)<br>Power = low, Opamp bias = low<br>Power = medium, Opamp bias = high<br>Power = high, Opamp bias = high                                         | 0.15<br>1.7<br>6.5 |             |                     | V/µs<br>V/µs<br>V/µs |

| SR <sub>FOA</sub> | Falling slew rate (20% to 80%) (10 pF load, unity gain)<br>Power = low, Opamp bias = low<br>Power = medium, Opamp bias = high<br>Power = high, Opamp bias = high                                        | 0.01<br>0.5<br>4.0 |             |                     | V/µs<br>V/µs<br>V/µs |

| BW <sub>OA</sub>  | Gain bandwidth product<br>Power = low, Opamp bias = low<br>Power = medium, Opamp bias = high<br>Power = high, Opamp bias = high                                                                         | 0.75<br>3.1<br>5.4 | -<br>-<br>- |                     | MHz<br>MHz<br>MHz    |

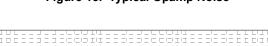

| E <sub>NOA</sub>  | Noise at 1 kHz (Power = medium, Opamp bias = high)                                                                                                                                                      | -                  | 100         | -                   | nV/rt-Hz             |

#### Table 34. 3.3-V AC Operational Amplifier Specifications

| Symbol            | Description                                                                                                                                                          | Min         | Тур | Max          | Units        |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-----|--------------|--------------|

| t <sub>ROA</sub>  | Rising settling time from 80% of $\Delta V$ to 0.1% of $\Delta V$<br>(10 pF load, unity gain)<br>Power = low, Opamp bias = low<br>Power = medium, Opamp bias = high  |             |     | 3.92<br>0.72 | μs<br>μs     |

| t <sub>SOA</sub>  | Falling settling time from 20% of $\Delta V$ to 0.1% of $\Delta V$<br>(10 pF load, unity gain)<br>Power = low, Opamp bias = low<br>Power = medium, Opamp bias = high |             |     | 5.41<br>0.72 | μs<br>μs     |

| SR <sub>ROA</sub> | Rising slew rate (20% to 80%) (10 pF load, unity gain)<br>Power = low, Opamp bias = low<br>Power = medium, Opamp bias = high                                         | 0.31<br>2.7 |     |              | V/µs<br>V/µs |

| SR <sub>FOA</sub> | Falling slew rate (20% to 80%) (10 pF load, unity gain)<br>Power = low, Opamp bias = low<br>Power = medium, Opamp bias = high                                        | 0.24<br>1.8 |     |              | V/µs<br>V/µs |

| BW <sub>OA</sub>  | Gain bandwidth product<br>Power = low, Opamp bias = low<br>Power = medium, Opamp bias = high                                                                         | 0.67<br>2.8 |     | -<br>-       | MHz<br>MHz   |

| E <sub>NOA</sub>  | Noise at 1 kHz (Power = medium, Opamp bias = high)                                                                                                                   | -           | 100 | -            | nV/rt-Hz     |

#### AC Low Power Comparator Specifications

nV/rtHz 10000 -

Table 36 lists the guaranteed maximum and minimum specifications for the voltage and temperature ranges: 4.75 V to 5.25 V and -40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C, 3.0 V to 3.6 V and -40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C, or 2.4 V to 3.0 V and -40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C, respectively. Typical parameters are measured at 5 V at 25 °C and are for design guidance only.

Table 36. AC Low Power Comparator Specifications

| Symbol            | Description       | Min | Тур | Max | Units | Notes                                                                      |

|-------------------|-------------------|-----|-----|-----|-------|----------------------------------------------------------------------------|

| t <sub>RLPC</sub> | LPC response time | -   | -   | 50  | μs    | $\geq$ 50 mV overdrive comparator reference set within V <sub>REFLPC</sub> |

0.050[1.270] TYP.

0.013[0.330] 0.019[0.482]

0.015[0.381] 0.050[1.270]

51-85024 \*F

1.25 REF-

- 0.55

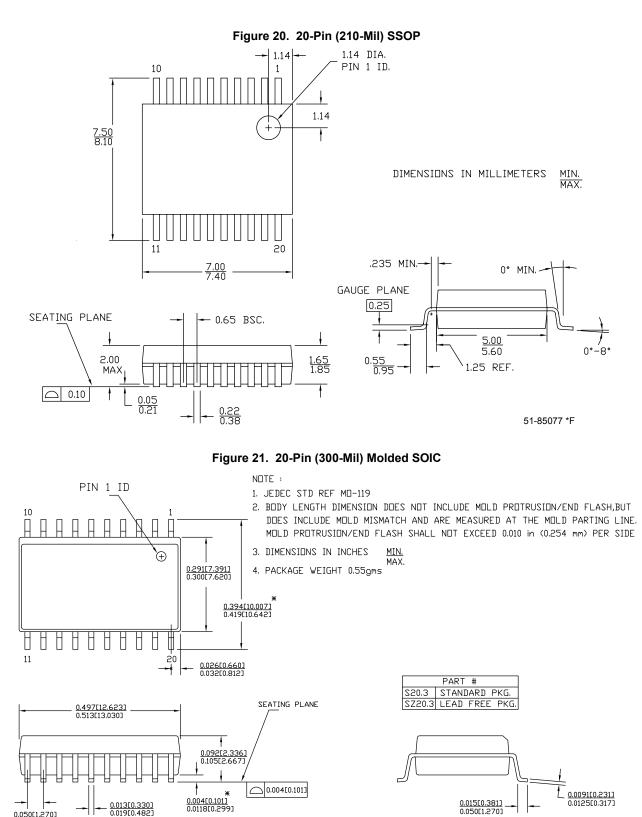

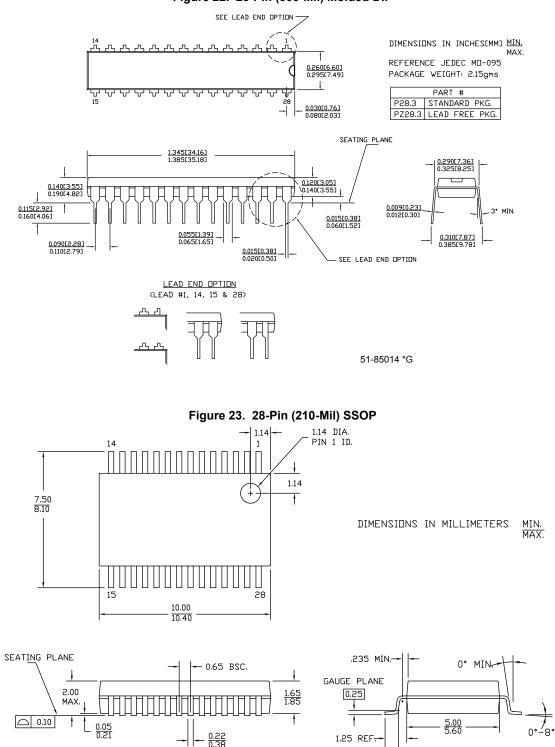

Figure 22. 28-Pin (300-Mil) Molded DIP

51-85079 \*F

# Acronyms

### **Acronyms Used**

Table 53 lists the acronyms that are used in this document.

#### Table 53. Acronyms Used in this Datasheet

| Acronym | Description                                         | Acronym          | Description                                   |

|---------|-----------------------------------------------------|------------------|-----------------------------------------------|

| AC      | alternating current                                 | MIPS             | million instructions per second               |

| ADC     | analog-to-digital converter                         | OCD              | on-chip debug                                 |

| API     | application programming interface                   | PCB              | printed circuit board                         |

| CMOS    | complementary metal oxide semiconductor             | PDIP             | plastic dual-in-line package                  |

| CPU     | central processing unit                             | PGA              | programmable gain amplifier                   |

| CRC     | cyclic redundancy check                             | PLL              | phase-locked loop                             |

| СТ      | continuous time                                     | POR              | power on reset                                |

| DAC     | digital-to-analog converter                         | PPOR             | precision power on reset                      |

| DC      | direct current                                      | PRS              | pseudo-random sequence                        |

| DTMF    | dual-tone multi-frequency                           | PSoC®            | Programmable System-on-Chip                   |

| ECO     | external crystal oscillator                         | PWM              | pulse width modulator                         |

| EEPROM  | electrically erasable programmable read-only memory | QFN              | quad flat no leads                            |

| GPIO    | general purpose I/O                                 | RTC              | real time clock                               |

| ICE     | in-circuit emulator                                 | SAR              | successive approximation                      |

| IDE     | integrated development environment                  | SC               | switched capacitor                            |

| ILO     | internal low speed oscillator                       | SLIMO            | slow IMO                                      |

| IMO     | internal main oscillator                            | SMP              | switch mode pump                              |

| I/O     | input/output                                        | SOIC             | small-outline integrated circuit              |

| IrDA    | infrared data association                           | SPI <sup>™</sup> | serial peripheral interface                   |

| ISSP    | in-system serial programming                        | SRAM             | static random access memory                   |

| LCD     | liquid crystal display                              | SROM             | supervisory read only memory                  |

| LED     | light-emitting diode                                | SSOP             | shrink small-outline package                  |

| LPC     | low power comparator                                | UART             | universal asynchronous receiver / transmitter |

| LVD     | low voltage detect                                  | USB              | universal serial bus                          |

| MAC     | multiply-accumulate                                 | WDT              | watchdog timer                                |

| MCU     | microcontroller unit                                | XRES             | external reset                                |

# **Reference Documents**

CY8CPLC20, CY8CLED16P01, CY8C29x66, CY8C27x43, CY8C24x94, CY8C24x23, CY8C24x23A, CY8C22x13, CY8C21x34, CY8C21x23, CY7C64215, CY7C603xx, CY8CNP1xx, and CYWUSB6953 PSoC® Programmable System-on-Chip Technical Reference Manual (TRM) (001-14463)

Design Aids – Reading and Writing PSoC<sup>®</sup> Flash – AN2015 (001-40459)

Application Notes for Surface Mount Assembly of Amkor's MicroLeadFrame (MLF) Packages – available at http://www.amkor.com.

# **Document Conventions**

### Units of Measure

Table 54 lists the unit sof measures.

#### Table 54. Units of Measure

| Symbol | Unit of Measure | Symbol | Unit of Measure         |

|--------|-----------------|--------|-------------------------|

| kB     | 1024 bytes      | μs     | microsecond             |

| dB     | decibels        | ms     | millisecond             |

| °C     | degree Celsius  | ns     | nanosecond              |

| fF     | femto farad     | ps     | picosecond              |

| pF     | picofarad       | μV     | microvolts              |

| kHz    | kilohertz       | mV     | millivolts              |

| MHz    | megahertz       | mVpp   | millivolts peak-to-peak |

| rt-Hz  | root hertz      | nV     | nanovolts               |

| kΩ     | kilohm          | V      | volts                   |

| Ω      | ohm             | μW     | microwatts              |

| μA     | microampere     | W      | watt                    |

| mA     | milliampere     | mm     | millimeter              |

| nA     | nanoampere      | ppm    | parts per million       |

| pА     | pikoampere      | %      | percent                 |

| mH     | millihenry      |        | · ·                     |

#### **Numeric Conventions**

Hexadecimal numbers are represented with all letters in uppercase with an appended lowercase 'h' (for example, '14h' or '3Ah'). Hexadecimal numbers may also be represented by a '0x' prefix, the C coding convention. Binary numbers have an appended lowercase 'b' (for example, 01010100b' or '01000011b'). Numbers not indicated by an 'h' or 'b' are decimals.

## Glossary

| active high                                   | 10.A logic signal having its asserted state as the logic 1 state.<br>11.A logic signal having the logic 1 state as the higher voltage of the two states.                                                                                                                                                                |

|-----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| analog blocks                                 | The basic programmable opamp circuits. These are SC (switched capacitor) and CT (continuous time) blocks. These blocks can be interconnected to provide ADCs, DACs, multi-pole filters, gain stages, and much more.                                                                                                     |

| analog-to-digital<br>(ADC)                    | A device that changes an analog signal to a digital signal of corresponding magnitude. Typically, an ADC converts a voltage to a digital number. The digital-to-analog (DAC) converter performs the reverse operation.                                                                                                  |

| API (Application<br>Programming<br>Interface) | A series of software routines that comprise an interface between a computer application and lower level services and functions (for example, user modules and libraries). APIs serve as building blocks for programmers that create software applications.                                                              |

| asynchronous                                  | A signal whose data is acknowledged or acted upon immediately, irrespective of any clock signal.                                                                                                                                                                                                                        |

| Bandgap<br>reference                          | A stable voltage reference design that matches the positive temperature coefficient of VT with the negative temperature coefficient of VBE, to produce a zero temperature coefficient (ideally) reference.                                                                                                              |

| bandwidth                                     | <ol> <li>The frequency range of a message or information processing system measured in hertz.</li> <li>The width of the spectral region over which an amplifier (or absorber) has substantial gain (or loss); it is<br/>sometimes represented more specifically as, for example, full width at half maximum.</li> </ol> |

# Glossary (continued)