Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                      |

| Core Processor             | м8С                                                                           |

| Core Size                  | 8-Bit                                                                         |

| Speed                      | 24MHz                                                                         |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                             |

| Peripherals                | POR, PWM, WDT                                                                 |

| Number of I/O              | 24                                                                            |

| Program Memory Size        | 4KB (4K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | -                                                                             |

| RAM Size                   | 256 x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 2.4V ~ 5.25V                                                                  |

| Data Converters            | A/D 10x14b; D/A 2x9b                                                          |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 32-VFQFN Exposed Pad                                                          |

| Supplier Device Package    | 32-QFN (5x5)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/cy8c24423a4-24ltxi |

# Contents

| PSoC Functional Overview          | . 3 |

|-----------------------------------|-----|

| PSoC Core                         | . 3 |

| Digital System                    | . 3 |

| Analog System                     | .4  |

| Additional System Resources       | . 5 |

| PSoC Device Characteristics       |     |

| Getting Started                   | . 6 |

| Application Notes                 | .6  |

| Development Kits                  | . 6 |

| Training                          |     |

| CYPros Consultants                | . 6 |

| Solutions Library                 |     |

| Technical Support                 | . 6 |

| Development Tools                 |     |

| PSoC Designer Software Subsystems |     |

| Designing with PSoC Designer      |     |

| Select User Modules               |     |

| Configure User Modules            |     |

| Organize and Connect              |     |

| Generate, Verify, and Debug       | . 8 |

| Pinouts                           |     |

| 8-Pin Part Pinout                 |     |

| 20-Pin Part Pinout                |     |

| 28-Pin Part Pinout                |     |

| 32-Pin Part Pinout                |     |

| 56-Pin Part Pinout                | _   |

| Register Reference                |     |

| Register Conventions              |     |

| Register Mapping Tables           |     |

| Electrical Specifications         |     |

| Absolute Maximum Ratings          |     |

| Operating Temperature             |     |

| DC Flectrical Characteristics     | 18  |

| AC Electrical Characteristics             | 36 |

|-------------------------------------------|----|

| Packaging Information                     | 50 |

| Packaging Dimensions                      | 50 |

| Thermal Impedances                        |    |

| Capacitance on Crystal Pins               | 56 |

| Solder Reflow Specifications              | 56 |

| Development Tool Selection                | 57 |

| Software                                  |    |

| Development Kits                          |    |

| Evaluation Tools                          | 57 |

| Device Programmers                        | 58 |

| Accessories (Emulation and Programming) . | 58 |

| Ordering Information                      |    |

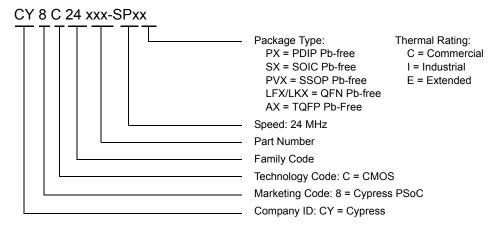

| Ordering Code Definitions                 | 59 |

| Acronyms                                  | 60 |

| Acronyms Used                             | 60 |

| Reference Documents                       |    |

| Document Conventions                      | 61 |

| Units of Measure                          | 61 |

| Numeric Conventions                       | 61 |

| Glossary                                  | 61 |

| Errata                                    | 66 |

| Part Numbers Affected                     | 66 |

| CY8C24123A Qualification Status           | 66 |

| CY8C24123A Errata Summary                 | 66 |

| Document History Page                     | 67 |

| Sales, Solutions, and Legal Information   |    |

| Worldwide Sales and Design Support        | 70 |

| Products                                  |    |

| PSoC® Solutions                           |    |

| Cypress Developer Community               | 70 |

| Technical Support                         | 70 |

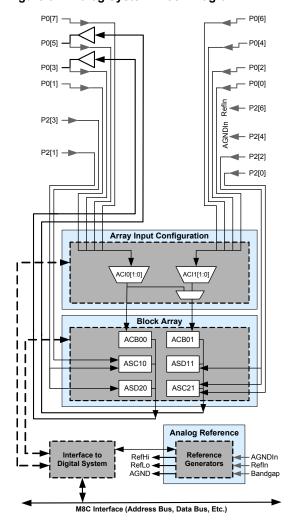

## **Analog System**

The analog system consists of six configurable blocks, each consisting of an opamp circuit that allows the creation of complex analog signal flows. Analog peripherals are very flexible and can be customized to support specific application requirements. Some of the more common PSoC analog functions (most available as user modules) are:

- ADCs (up to two, with 6- to 14-bit resolution, selectable as incremental, delta sigma, and SAR)

- Filters (two and four pole band-pass, low-pass, and notch)

- Amplifiers (up to two, with selectable gain to 48x)

- Instrumentation amplifiers (one with selectable gain to 93x)

- Comparators (up to two, with 16 selectable thresholds)

- DACs (up to two, with 6 to 9-bit resolution)

- Multiplying DACs (up to two, with 6 to 9-bit resolution)

- High current output drivers (two with 30 mA drive as a PSoC Core resource)

- 1.3 V reference (as a system resource)

- DTMF dialer

- Modulators

- Correlators

- Peak detectors

- Many other topologies possible

Analog blocks are arranged in a column of three, which includes one continuous time (CT) and two switched capacitor (SC) blocks, as shown in Figure 3

Figure 3. Analog System Block Diagram

# **Designing with PSoC Designer**

The development process for the PSoC device differs from that of a traditional fixed-function microprocessor. The configurable analog and digital hardware blocks give the PSoC architecture a unique flexibility that pays dividends in managing specification change during development and lowering inventory costs. These configurable resources, called PSoC blocks, have the ability to implement a wide variety of user-selectable functions. The PSoC development process is:

- 6. Select user modules.

- Configure user modules.

- 8. Organize and connect.

- 9. Generate, verify, and debug.

### Select User Modules

PSoC Designer provides a library of prebuilt, pretested hardware peripheral components called "user modules." User modules make selecting and implementing peripheral devices, both analog and digital, simple.

### **Configure User Modules**

Each user module that you select establishes the basic register settings that implement the selected function. They also provide parameters and properties that allow you to tailor their precise configuration to your particular application. For example, a PWM User Module configures one or more digital PSoC blocks, one for each eight bits of resolution. Using these parameters, you can establish the pulse width and duty cycle. Configure the parameters and properties to correspond to your chosen application. Enter values directly or by selecting values from drop-down menus. All of the user modules are documented in datasheets that may be viewed directly in PSoC Designer or on the Cypress website. These user module datasheets explain the internal operation of the user module and provide performance specifications. Each datasheet describes the use of each user

module parameter, and other information that you may need to successfully implement your design.

### **Organize and Connect**

Build signal chains at the chip level by interconnecting user modules to each other and the I/O pins. Perform the selection, configuration, and routing so that you have complete control over all on-chip resources.

# Generate, Verify, and Debug

When you are ready to test the hardware configuration or move on to developing code for the project, perform the "Generate Configuration Files" step. This causes PSoC Designer to generate source code that automatically configures the device to your specification and provides the software for the system. The generated code provides APIs with high-level functions to control and respond to hardware events at run time, and interrupt service routines that you can adapt as needed.

A complete code development environment lets you to develop and customize your applications in C, assembly language, or both.

The last step in the development process takes place inside PSoC Designer's Debugger (accessed by clicking the Connect icon). PSoC Designer downloads the HEX image to the ICE where it runs at full-speed. PSoC Designer debugging capabilities rival those of systems costing many times more. In addition to traditional single-step, run-to-breakpoint, and watch-variable features, the debug interface provides a large trace buffer. It lets you to define complex breakpoint events that include monitoring address and data bus values, memory locations, and external signals.

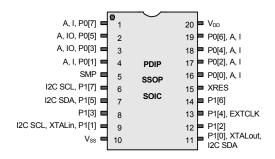

# 20-Pin Part Pinout

Table 3. 20-Pin PDIP, SSOP, and SOIC

| Pin | Ту      | ре     | Pin      | Description                                              |  |  |

|-----|---------|--------|----------|----------------------------------------------------------|--|--|

| No. | Digital | Analog | Name     | Description                                              |  |  |

| 1   | I/O     | I      | P0[7]    | Analog column mux input                                  |  |  |

| 2   | I/O     | I/O    | P0[5]    | Analog column mux input and column output                |  |  |

| 3   | I/O     | I/O    | P0[3]    | Analog column mux input and column output                |  |  |

| 4   | I/O     | ı      | P0[1]    | Analog column mux input                                  |  |  |

| 5   | Po      | wer    | SMP      | SMP connection to external components required           |  |  |

| 6   | I/O     |        | P1[7]    | I <sup>2</sup> C SCL                                     |  |  |

| 7   | I/O     |        | P1[5]    | I <sup>2</sup> C SDA                                     |  |  |

| 8   | I/O     |        | P1[3]    |                                                          |  |  |

| 9   | I/O     |        | P1[1]    | XTALin, I <sup>2</sup> C SCL, ISSP-SCLK <sup>[5]</sup>   |  |  |

| 10  | Po      | wer    | $V_{SS}$ | Ground connection.                                       |  |  |

| 11  | I/O     |        | P1[0]    | XTALout, I <sup>2</sup> C SDA, ISSP-SDATA <sup>[5]</sup> |  |  |

| 12  | I/O     |        | P1[2]    |                                                          |  |  |

| 13  | I/O     |        | P1[4]    | Optional external clock input (EXTCLK)                   |  |  |

| 14  | I/O     |        | P1[6]    |                                                          |  |  |

| 15  | In      | out    | XRES     | Active high external reset with internal pull-down       |  |  |

| 16  | I/O     | I      | P0[0]    | Analog column mux input                                  |  |  |

| 17  | I/O     |        | P0[2]    | Analog column mux input                                  |  |  |

| 18  | I/O     |        | P0[4]    | Analog column mux input                                  |  |  |

| 19  | I/O     |        | P0[6]    | Analog column mux input                                  |  |  |

| 20  | Po      | wer    | $V_{DD}$ | Supply voltage                                           |  |  |

Figure 5. CY8C24223A 20-Pin PSoC Device

**LEGEND**: A = Analog, I = Input, and O = Output.

### Note

<sup>5.</sup> These are the ISSP pins, which are not high Z at POR. See the PSoC Technical Reference Manual for details.

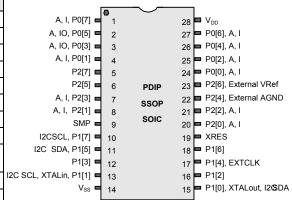

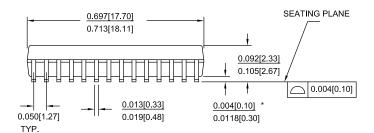

# 28-Pin Part Pinout

Table 4. 28-Pin PDIP, SSOP, and SOIC

| Pin | Ту      | pe     | Pin      | Description                                              |  |  |

|-----|---------|--------|----------|----------------------------------------------------------|--|--|

| No. | Digital | Analog | Name     | Description                                              |  |  |

| 1   | I/O     | I      | P0[7]    | Analog column mux input                                  |  |  |

| 2   | I/O     | I/O    | P0[5]    | Analog column mux input and column output                |  |  |

| 3   | I/O     | I/O    | P0[3]    | Analog column mux input and column output                |  |  |

| 4   | I/O     | I      | P0[1]    | Analog column mux input                                  |  |  |

| 5   | I/O     |        | P2[7]    |                                                          |  |  |

| 6   | I/O     |        | P2[5]    |                                                          |  |  |

| 7   | I/O     | I      | P2[3]    | Direct switched capacitor block input                    |  |  |

| 8   | I/O     | I      | P2[1]    | Direct switched capacitor block input                    |  |  |

| 9   | Po      | wer    | SMP      | SMP connection to external components required           |  |  |

| 10  | I/O     |        | P1[7]    | I <sup>2</sup> C SCL                                     |  |  |

| 11  | I/O     |        | P1[5]    | I <sup>2</sup> C SDA                                     |  |  |

| 12  | I/O     |        | P1[3]    |                                                          |  |  |

| 13  | I/O     |        | P1[1]    | XTALin, I <sup>2</sup> C SCL, ISSP-SCLK <sup>[6]</sup>   |  |  |

| 14  | Po      | wer    | $V_{SS}$ | Ground connection.                                       |  |  |

| 15  | I/O     |        | P1[0]    | XTALout, I <sup>2</sup> C SDA, ISSP-SDATA <sup>[6]</sup> |  |  |

| 16  | I/O     |        | P1[2]    |                                                          |  |  |

| 17  | I/O     |        | P1[4]    | Optional EXTCLK                                          |  |  |

| 18  | I/O     |        | P1[6]    |                                                          |  |  |

| 19  | Inp     | out    | XRES     | Active high external reset with internal pull-down       |  |  |

| 20  | I/O     | I      | P2[0]    | Direct switched capacitor block input                    |  |  |

| 21  | I/O     | I      | P2[2]    | Direct switched capacitor block input                    |  |  |

| 22  | I/O     |        | P2[4]    | External analog ground (AGND)                            |  |  |

| 23  | I/O     |        | P2[6]    | External voltage reference (V <sub>REF</sub> )           |  |  |

| 24  | 1/0     | I      | P0[0]    | Analog column mux input                                  |  |  |

| 25  | I/O     | I      | P0[2]    | Analog column mux input                                  |  |  |

| 26  | I/O     | I      | P0[4]    | Analog column mux input                                  |  |  |

| 27  | I/O     | I      | P0[6]    | Analog column mux input                                  |  |  |

| 28  | Po      | wer    | $V_{DD}$ | Supply voltage                                           |  |  |

Figure 6. CY8C24423A 28-Pin PSoC Device

**Not for Production**

LEGEND : A = Analog, I = Input, and O = Output.

### Note

<sup>6.</sup> These are the ISSP pins, which are not high Z at POR. See the PSoC Technical Reference Manual for details.

# **Register Reference**

This section lists the registers of the CY8C24x23A PSoC device. For detailed register information, see the PSoC Programmable Sytem-on-Chip Reference Manual.

# **Register Conventions**

Abbreviations Used

The register conventions specific to this section are listed in the following table.

Table 7. Abbreviations

| Convention | Description                  |

|------------|------------------------------|

| R          | Read register or bit(s)      |

| W          | Write register or bit(s)     |

| L          | Logical register or bit(s)   |

| С          | Clearable register or bit(s) |

| #          | Access is bit specific       |

# **Register Mapping Tables**

The PSoC device has a total register address space of 512 bytes. The register space is referred to as I/O space and is divided into two banks, Bank 0 and Bank 1. The XOI bit in the Flag register (CPU\_F) determines which bank the user is currently in. When the XOI bit is set, the user is in Bank 1.

**Note** In the following register mapping tables, blank fields are reserved and must not be accessed.

# **Electrical Specifications**

This section presents the DC and AC electrical specifications of the CY8C24x23A PSoC device. For the latest electrical specifications, check if you have the most recent datasheet by visiting the website at http://www.cypress.com.

Specifications are valid for –40  $^{\circ}C \le T_A \le 85 ^{\circ}C$  and  $T_J \le 100 ^{\circ}C$ , except where noted.

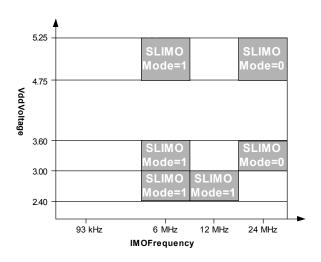

Refer to Table 29 on page 37 for the electrical specifications for the IMO using SLIMO mode.

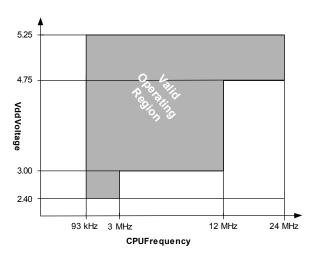

Figure 9. Voltage versus CPU Frequency

Figure 8. IMO Frequency Trim Options

# **Absolute Maximum Ratings**

Exceeding maximum ratings may shorten the useful life of the device. User guidelines are not tested.

**Table 9. Absolute Maximum Ratings**

| Symbol                | Description                                                   | Min                     | Тур | Max                     | Units | Notes                                                                                                                                                                               |

|-----------------------|---------------------------------------------------------------|-------------------------|-----|-------------------------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| T <sub>STG</sub>      | Storage temperature                                           | <b>-</b> 55             | 25  | +100                    | °C    | Higher storage temperatures reduce data retention time. Recommended storage temperature is +25 °C ± 25 °C. Extended duration storage temperatures above 65 °C degrades reliability. |

| T <sub>BAKETEMP</sub> | Bake temperature                                              | 1                       | 125 | See<br>package<br>label | °C    |                                                                                                                                                                                     |

| t <sub>BAKETIME</sub> | Bake time                                                     | See<br>package<br>label | -   | 72                      | Hours |                                                                                                                                                                                     |

| T <sub>A</sub>        | Ambient temperature with power applied                        | -40                     | _   | +85                     | °C    |                                                                                                                                                                                     |

| $V_{DD}$              | Supply voltage on V <sub>DD</sub> relative to V <sub>SS</sub> | -0.5                    | _   | +6.0                    | V     |                                                                                                                                                                                     |

| $V_{IO}$              | DC input voltage                                              | $V_{SS} - 0.5$          | -   | $V_{DD} + 0.5$          | V     |                                                                                                                                                                                     |

| $V_{IOZ}$             | DC voltage applied to tri-state                               | $V_{SS} - 0.5$          | -   | $V_{DD} + 0.5$          | V     |                                                                                                                                                                                     |

| I <sub>MIO</sub>      | Maximum current into any port pin                             | -25                     | _   | +50                     | mA    |                                                                                                                                                                                     |

| ESD                   | Electrostatic discharge voltage                               | 2000                    | _   | _                       | V     | Human body model ESD.                                                                                                                                                               |

| LU                    | Latch up current                                              | _                       | _   | 200                     | mA    |                                                                                                                                                                                     |

# DC GPIO Specifications

The following tables list the guaranteed maximum and minimum specifications for the voltage and temperature ranges: 4.75 V to 5.25 V and –40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C, 3.0 V to 3.6 V and –40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C, or 2.4 V to 3.0 V and –40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C, respectively. Typical parameters are measured at 5 V, 3.3 V, and 2.7 V at 25 °C and are for design guidance only.

Table 12. 5-V and 3.3-V DC GPIO Specifications

| Symbol           | Description                       | Min                   | Тур | Max  | Units | Notes                                                                                                                                                                                                             |

|------------------|-----------------------------------|-----------------------|-----|------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| R <sub>PU</sub>  | Pull-up resistor                  | 4                     | 5.6 | 8    | kΩ    |                                                                                                                                                                                                                   |

| R <sub>PD</sub>  | Pull-down resistor                | 4                     | 5.6 | 8    | kΩ    |                                                                                                                                                                                                                   |

| V <sub>OH</sub>  | High output level                 | V <sub>DD</sub> – 1.0 | I   | I    | V     | $I_{OH}$ = 10 mA, $V_{DD}$ = 4.75 to 5.25 V (maximum 40 mA on even port pins (for example, P0[2], P1[4]), maximum 40 mA on odd port pins (for example, P0[3], P1[5])). 80 mA maximum combined $I_{OH}$ budget.    |

| V <sub>OL</sub>  | Low output level                  |                       | -   | 0.75 | V     | $I_{OL}$ = 25 mA, $V_{DD}$ = 4.75 to 5.25 V (maximum 100 mA on even port pins (for example, P0[2], P1[4]), maximum 100 mA on odd port pins (for example, P0[3], P1[5])). 150 mA maximum combined $I_{OL}$ budget. |

| I <sub>OH</sub>  | High level source current         | 10                    | _   | -    | mA    | $V_{OH} = V_{DD} - 1.0 \text{ V}$ , see the limitations of the total current in the note for $V_{OH}$                                                                                                             |

| I <sub>OL</sub>  | Low level sink current            | 25                    | -   | -    | mA    | $V_{OL}$ = 0.75 V, see the limitations of the total current in the note for $V_{OL}$                                                                                                                              |

| V <sub>IL</sub>  | Input low level                   | _                     | -   | 0.8  | V     | V <sub>DD</sub> = 3.0 to 5.25                                                                                                                                                                                     |

| $V_{IH}$         | Input high level                  | 2.1                   | -   |      | V     | V <sub>DD</sub> = 3.0 to 5.25                                                                                                                                                                                     |

| V <sub>H</sub>   | Input hysterisis                  | _                     | 60  | _    | mV    |                                                                                                                                                                                                                   |

| I <sub>IL</sub>  | Input leakage (absolute value)    | _                     | 1   | _    | nA    | Gross tested to 1 µA                                                                                                                                                                                              |

| C <sub>IN</sub>  | Capacitive load on pins as input  | _                     | 3.5 | 10   | pF    | Package and pin dependent.<br>Temp = 25 °C                                                                                                                                                                        |

| C <sub>OUT</sub> | Capacitive load on pins as output | -                     | 3.5 | 10   | pF    | Package and pin dependent.<br>Temp = 25 °C                                                                                                                                                                        |

Table 13. 2.7-V DC GPIO Specifications

| Symbol           | Description                       | Min                   | Тур | Max  | Units | Notes                                                                                                    |

|------------------|-----------------------------------|-----------------------|-----|------|-------|----------------------------------------------------------------------------------------------------------|

| R <sub>PU</sub>  | Pull-up resistor                  | 4                     | 5.6 | 8    | kΩ    |                                                                                                          |

| R <sub>PD</sub>  | Pull-down resistor                | 4                     | 5.6 | 8    | kΩ    |                                                                                                          |

| V <sub>OH</sub>  | High output level                 | V <sub>DD</sub> – 0.4 | _   | _    | V     | $I_{OH}$ = 2 mA (6.25 Typ), $V_{DD}$ = 2.4 to 3.0 V (16 mA maximum, 50 mA Typ combined $I_{OH}$ budget). |

| V <sub>OL</sub>  | Low output level                  | _                     | ı   | 0.75 | V     | $I_{OL}$ = 11.25 mA, $V_{DD}$ = 2.4 to 3.0 V (90 mA maximum combined $I_{OL}$ budget).                   |

| I <sub>OH</sub>  | High level source current         | 2                     | -   | -    | mA    | $V_{OH}$ = $V_{DD}$ – 0.4, see the limitations of total current in note for $V_{OH}$ .                   |

| $V_{IL}$         | Input low level                   | _                     | -   | 0.75 | V     | V <sub>DD</sub> = 2.4 to 3.0                                                                             |

| V <sub>IH</sub>  | Input high level                  | 2.0                   | _   | -    | V     | V <sub>DD</sub> = 2.4 to 3.0                                                                             |

| $V_{H}$          | Input hysteresis                  | _                     | 90  | _    | mV    |                                                                                                          |

| I <sub>OL</sub>  | Low level sink current            | 11.25                 | -   | -    | mA    | $V_{OL}$ = .75, see the limitations of total current in note for $V_{OL}$ .                              |

| I <sub>IL</sub>  | Input leakage (absolute value)    | _                     | 1   | _    | nA    | Gross tested to 1 µA                                                                                     |

| C <sub>IN</sub>  | Capacitive load on pins as input  | _                     | 3.5 | 10   | pF    | Package and pin dependent.<br>Temp = 25 °C                                                               |

| C <sub>OUT</sub> | Capacitive load on pins as output | _                     | 3.5 | 10   | pF    | Package and pin dependent.<br>Temp = 25 °C                                                               |

## DC Switch Mode Pump Specifications

Table 21 lists the guaranteed maximum and minimum specifications for the voltage and temperature ranges: 4.75 V to 5.25 V and  $-40~^{\circ}\text{C} \le T_{A} \le 85~^{\circ}\text{C}$ , 3.0 V to 3.6 V and  $-40~^{\circ}\text{C} \le T_{A} \le 85~^{\circ}\text{C}$ , or 2.4 V to 3.0 V and  $-40~^{\circ}\text{C} \le T_{A} \le 85~^{\circ}\text{C}$ , respectively. Typical parameters are measured at 5 V, 3.3 V, and 2.7 V at 25  $^{\circ}\text{C}$  and are for design guidance only.

Table 21. DC Switch Mode Pump (SMP) Specifications

| Symbol                    | Description                                       | Min         | Тур  | Max         | Units           | Notes                                                                                                                                                                                        |

|---------------------------|---------------------------------------------------|-------------|------|-------------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>PUMP</sub> 5 V     | 5 V output voltage from pump                      | 4.75        | 5.0  | 5.25        | V               | Configuration listed in footnote. <sup>[11]</sup> Average, neglecting ripple. SMP trip voltage is set to 5.0 V.                                                                              |

| V <sub>PUMP</sub> 3 V     | 3.3 V output voltage from pump                    | 3.00        | 3.25 | 3.60        | V               | Configuration listed in footnote. [11] Average, neglecting ripple. SMP trip voltage is set to 3.25 V.                                                                                        |

| V <sub>PUMP</sub> 2 V     | 2.6 V output voltage from pump                    | 2.45        | 2.55 | 2.80        | V               | Configuration listed in footnote. [11] Average, neglecting ripple. SMP trip voltage is set to 2.55 V.                                                                                        |

| I <sub>PUMP</sub>         |                                                   | 5<br>8<br>8 |      | -<br>-<br>- | mA<br>mA<br>mA  | Configuration listed in footnote. [11] SMP trip voltage is set to 5.0 V. SMP trip voltage is set to 3.25 V. SMP trip voltage is set to 2.55 V.                                               |

| V <sub>BAT</sub> 5 V      | Input voltage range from battery                  | 1.8         | _    | 5.0         | V               | Configuration listed in footnote. <sup>[11]</sup> SMP trip voltage is set to 5.0 V.                                                                                                          |

| V <sub>BAT</sub> 3 V      | Input voltage range from battery                  | 1.0         | _    | 3.3         | V               | Configuration listed in footnote. <sup>[11]</sup> SMP trip voltage is set to 3.25 V.                                                                                                         |

| V <sub>BAT</sub> 2 V      | Input voltage range from battery                  | 1.0         | _    | 3.0         | V               | Configuration listed in footnote. <sup>[11]</sup> SMP trip voltage is set to 2.55 V.                                                                                                         |

| V <sub>BATSTART</sub>     | Minimum input voltage from battery to start pump  | 1.2         | -    | -           | V               | Configuration listed in footnote. $^{[11]}$ 0 °C $\leq$ T <sub>A</sub> $\leq$ 100. 1.25 V at T <sub>A</sub> = $-40$ °C                                                                       |

| ΔV <sub>PUMP_Line</sub>   | Line regulation (over V <sub>BAT</sub> range)     | -           | 5    | -           | %V <sub>O</sub> | Configuration listed in footnote. [11] V <sub>O</sub> is the V <sub>DD</sub> Value for PUMP Trip" specified by the VM[2:0] setting in the DC POR and LVD Specification, Table 26 on page 35. |

| ΔV <sub>PUMP_Load</sub>   | Load regulation                                   | -           | 5    | -           | %V <sub>O</sub> | Configuration listed in footnote. [11] $V_O$ is the " $V_{DD}$ value for PUMP Trip" specified by the VM[2:0] setting in the DC POR and LVD Specification, Table 26 on page 35.               |

| $\Delta V_{PUMP\_Ripple}$ | Output voltage ripple (depends on capacitor/load) | _           | 100  | _           | mVpp            | Configuration listed in footnote. <sup>[11]</sup> Load is 5 mA.                                                                                                                              |

| E <sub>3</sub>            | Efficiency                                        | 35          | 50   | -           | %               | Configuration listed in footnote. <sup>[11]</sup> Load is 5 mA. SMP trip voltage is set to 3.25 V.                                                                                           |

| E <sub>2</sub>            | Efficiency                                        | -           | _    | ı           |                 |                                                                                                                                                                                              |

| F <sub>PUMP</sub>         | Switching frequency                               | -           | 1.3  | _           | MHz             |                                                                                                                                                                                              |

| DC <sub>PUMP</sub>        | Switching duty cycle                              |             | 50   |             | %               |                                                                                                                                                                                              |

## DC POR, SMP, and LVD Specifications

Table 24 lists the guaranteed maximum and minimum specifications for the voltage and temperature ranges: 4.75 V to 5.25 V and  $-40~^{\circ}\text{C} \le T_{A} \le 85~^{\circ}\text{C}$ , 3.0 V to 3.6 V and  $-40~^{\circ}\text{C} \le T_{A} \le 85~^{\circ}\text{C}$ , or 2.4 V to 3.0 V and  $-40~^{\circ}\text{C} \le T_{A} \le 85~^{\circ}\text{C}$ , respectively. Typical parameters are measured at 5 V, 3.3 V, and 2.7 V at 25 °C and are for design guidance only.

Note The bits PORLEV and VM in the following table refer to bits in the VLT\_CR register. See the PSoC Programmable Sytem-on-Chip Technical Reference Manual for more information on the VLT\_CR register.

Table 26. DC POR and LVD Specifications

| Symbol                                                                       | Description                                                                                                                                                                        | Min                                                          | Тур                                                          | Max                                                                                          | Units                           | Notes                                                                                                                   |

|------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|--------------------------------------------------------------|----------------------------------------------------------------------------------------------|---------------------------------|-------------------------------------------------------------------------------------------------------------------------|

| V <sub>PPOR0</sub><br>V <sub>PPOR1</sub><br>V <sub>PPOR2</sub>               | V <sub>DD</sub> value for PPOR trip<br>PORLEV[1:0] = 00b<br>PORLEV[1:0] = 01b<br>PORLEV[1:0] = 10b                                                                                 | -                                                            | 2.36<br>2.82<br>4.55                                         | 2.40<br>2.95<br>4.70                                                                         | V<br>V                          | V <sub>DD</sub> must be greater than or equal to 2.5 V during startup, reset from the XRES pin, or reset from watchdog. |

| VLVD0<br>VLVD1<br>VLVD2<br>VLVD3<br>VLVD4<br>VLVD5<br>VLVD6<br>VLVD7         | V <sub>DD</sub> value for LVD trip<br>VM[2:0] = 000b<br>VM[2:0] = 001b<br>VM[2:0] = 010b<br>VM[2:0] = 011b<br>VM[2:0] = 100b<br>VM[2:0] = 101b<br>VM[2:0] = 110b<br>VM[2:0] = 111b | 2.40<br>2.85<br>2.95<br>3.06<br>4.37<br>4.50<br>4.62<br>4.71 | 2.45<br>2.92<br>3.02<br>3.13<br>4.48<br>4.64<br>4.73<br>4.81 | 2.51 <sup>[12]</sup><br>2.99 <sup>[13]</sup><br>3.09<br>3.20<br>4.55<br>4.75<br>4.83<br>4.95 | V V V V V V                     |                                                                                                                         |

| VPUMP0<br>VPUMP1<br>VPUMP2<br>VPUMP3<br>VPUMP4<br>VPUMP5<br>VPUMP6<br>VPUMP7 | V <sub>DD</sub> value for SMP trip<br>VM[2:0] = 000b<br>VM[2:0] = 001b<br>VM[2:0] = 010b<br>VM[2:0] = 011b<br>VM[2:0] = 100b<br>VM[2:0] = 101b<br>VM[2:0] = 110b<br>VM[2:0] = 111b | 2.50<br>2.96<br>3.03<br>3.18<br>4.54<br>4.62<br>4.71<br>4.89 | 2.55<br>3.02<br>3.10<br>3.25<br>4.64<br>4.73<br>4.82<br>5.00 | 2.62 <sup>[14]</sup> 3.09 3.16 3.32 <sup>[15]</sup> 4.74 4.83 4.92 5.12                      | \<br>\<br>\<br>\<br>\<br>\<br>\ |                                                                                                                         |

<sup>12.</sup> Always greater than 50 mV above  $V_{\rm PPOR}$  (PORLEV=00) for falling supply. 13. Always greater than 50 mV above  $V_{\rm PPOR}$  (PORLEV=01) for falling supply. 14. Always greater than 50 mV above  $V_{\rm LVD0}$ . 15. Always greater than 50 mV above  $V_{\rm LVD3}$ .

### DC Programming Specifications

Table 27 lists the guaranteed maximum and minimum specifications for the voltage and temperature ranges: 4.75 V to 5.25 V and  $-40 ^{\circ}\text{C} \le \text{T}_{\text{A}} \le 85 ^{\circ}\text{C}$ , 3.0 V to 3.6 V and  $-40 ^{\circ}\text{C} \le \text{T}_{\text{A}} \le 85 ^{\circ}\text{C}$ , or 2.4 V to 3.0 V and  $-40 ^{\circ}\text{C} \le \text{T}_{\text{A}} \le 85 ^{\circ}\text{C}$ , respectively. Typical parameters are measured at 5 V, 3.3 V, and 2.7 V at  $25 ^{\circ}\text{C}$  and are for design guidance only.

**Table 27. DC Programming Specifications**

| Symbol                | Description                                                                                 | Min                    | Тур | Max                    | Units | Notes                                                                                         |

|-----------------------|---------------------------------------------------------------------------------------------|------------------------|-----|------------------------|-------|-----------------------------------------------------------------------------------------------|

| V <sub>DDP</sub>      | V <sub>DD</sub> for programming and erase                                                   | 4.5                    | 5   | 5.5                    | V     | This specification applies to the functional requirements of external programmer tools        |

| V <sub>DDLV</sub>     | Low V <sub>DD</sub> for verify                                                              | 2.4                    | 2.5 | 2.6                    | V     | This specification applies to the functional requirements of external programmer tools        |

| V <sub>DDHV</sub>     | High V <sub>DD</sub> for verify                                                             | 5.1                    | 5.2 | 5.3                    | V     | This specification applies to the functional requirements of external programmer tools        |

| V <sub>DDIWRITE</sub> | Supply voltage for flash write operation                                                    | 2.7                    |     | 5.25                   | V     | This specification applies<br>to this device when it is<br>executing internal flash<br>writes |

| I <sub>DDP</sub>      | Supply current during programming or verify                                                 | _                      | 5   | 25                     | mA    |                                                                                               |

| V <sub>ILP</sub>      | Input low voltage during programming or verify                                              | _                      | _   | 0.8                    | V     |                                                                                               |

| V <sub>IHP</sub>      | Input high voltage during programming or verify                                             | 2.1                    | _   | _                      | V     |                                                                                               |

| I <sub>ILP</sub>      | Input current when applying V <sub>ILP</sub> to P1[0] or P1[1] during programming or verify | _                      | -   | 0.2                    | mA    | Driving internal pull-down resistor                                                           |

| I <sub>IHP</sub>      | Input current when applying V <sub>IHP</sub> to P1[0] or P1[1] during programming or verify | _                      | -   | 1.5                    | mA    | Driving internal pull-down resistor                                                           |

| V <sub>OLV</sub>      | Output low voltage during programming or verify                                             | _                      | _   | V <sub>SS</sub> + 0.75 | V     |                                                                                               |

| V <sub>OHV</sub>      | Output high voltage during programming or verify                                            | V <sub>DD</sub> – 1.0  | _   | $V_{DD}$               | V     |                                                                                               |

| Flash <sub>ENPB</sub> | Flash endurance (per block)                                                                 | 50,000 <sup>[16]</sup> | -   | _                      | -     | Erase/write cycles per block                                                                  |

| Flash <sub>ENT</sub>  | Flash endurance (total) <sup>[17]</sup>                                                     | 1,800,000              | _   | -                      | _     | Erase/write cycles                                                                            |

| Flash <sub>DR</sub>   | Flash data retention                                                                        | 10                     | _   | -                      | Years |                                                                                               |

### DC I<sup>2</sup>C Specifications

Table 28 lists the guaranteed maximum and minimum specifications for the voltage and temperature ranges: 4.75 V to 5.25 V and  $-40\,^{\circ}\text{C} \le T_{A} \le 85\,^{\circ}\text{C}$ , 3.0 V to 3.6 V and  $-40\,^{\circ}\text{C} \le T_{A} \le 85\,^{\circ}\text{C}$ , or 2.4 V to 3.0 V and  $-40\,^{\circ}\text{C} \le T_{A} \le 85\,^{\circ}\text{C}$ , respectively. Typical parameters are measured at 5 V, 3.3 V, and 2.7 V at 25  $^{\circ}\text{C}$  and are for design guidance only.

Table 28. DC I<sup>2</sup>C Specifications<sup>[18]</sup>

| Symbol             | Description      | Min                   | Тур | Max                    | Units | Notes                                                 |

|--------------------|------------------|-----------------------|-----|------------------------|-------|-------------------------------------------------------|

| V <sub>ILI2C</sub> | Input low level  | _                     | _   | 0.3 × V <sub>DD</sub>  | V     | $2.4 \text{ V} \le \text{V}_{DD} \le 3.6 \text{ V}$   |

|                    |                  | _                     | _   | 0.25 × V <sub>DD</sub> | V     | $4.75 \text{ V} \le \text{V}_{DD} \le 5.25 \text{ V}$ |

| V <sub>IHI2C</sub> | Input high level | 0.7 × V <sub>DD</sub> | _   | _                      | V     | $2.4 \text{ V} \le \text{V}_{DD} \le 5.25 \text{ V}$  |

### Notes

- 16. The 50,000 cycle flash endurance per block is only guaranteed if the flash is operating within one voltage range. Voltage ranges are 2.4 V to 3.0 V, 3.0 V to 3.6 V, and 4.75 V to 5.25 V.

- 17. A maximum of 36 × 50,000 block endurance cycles is allowed. This may be balanced between operations on 36 × 1 blocks of 50,000 maximum cycles each, 36 × 2 blocks of 25,000 maximum cycles each, or 36 × 4 blocks of 12,500 maximum cycles each (to limit the total number of cycles to 36 × 50,000 and that no single block ever sees more than 50,000 cycles).

- ever sees more than 50,000 cycles).

For the full industrial range, the user must employ a temperature sensor user module (FlashTemp) and feed the result to the temperature argument before writing.

Refer to the Flash APIs application note Design Aids Reading and Writing PSoC® Flash AN2015 for more information.

- 18. All GPIOs meet the DC GPIO V<sub>IL</sub> and V<sub>IH</sub> specifications found in the DC GPIO Specifications sections. The I<sup>2</sup>C GPIO pins also meet the above specs.

Table 30. 2.7-V AC Chip-Level Specifications

| Symbol                               | Description                                             | Min   | Тур | Max                      | Units | Notes                                                                                                                                                                   |

|--------------------------------------|---------------------------------------------------------|-------|-----|--------------------------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| F <sub>IMO12</sub>                   | IMO frequency for 12 MHz                                | 11.5  | 12  | 12.7 <sup>[27, 28]</sup> | MHz   | Trimmed for 2.7 V operation using factory trim values. See Figure 8 on page 18. SLIMO mode = 1.                                                                         |

| F <sub>IMO6</sub>                    | IMO frequency for 6 MHz                                 | 5.5   | 6   | 6.5 <sup>[27, 28]</sup>  | MHz   | Trimmed for 2.7 V operation using factory trim values. See Figure 8 on page 18. SLIMO mode = 1.                                                                         |

| F <sub>CPU1</sub>                    | CPU frequency (2.7 V nominal)                           | 0.937 | 3   | 3.15 <sup>[27]</sup>     | MHz   | SLIMO mode = 0.                                                                                                                                                         |

| F <sub>BLK27</sub>                   | Digital PSoC block frequency (2.7 V nominal)            | 0     | 12  | 12.7 <sup>[27, 28]</sup> | MHz   | Refer to the AC Digital Block Specifications.                                                                                                                           |

| F <sub>32K1</sub>                    | ILO frequency                                           | 8     | 32  | 96                       | kHz   |                                                                                                                                                                         |

| F <sub>32K_U</sub>                   | ILO untrimmed frequency                                 | 5     | _   | 100                      | kHz   | After a reset and before the M8C starts to run, the ILO is not trimmed. See the System Resets section of the PSoC Technical Reference Manual for details on timing this |

| t <sub>XRST</sub>                    | External reset pulse width                              | 10    | _   | _                        | μs    |                                                                                                                                                                         |

| DC12M                                | 12 MHz duty cycle                                       | 40    | 50  | 60                       | %     |                                                                                                                                                                         |

| DC <sub>ILO</sub>                    | ILO duty cycle                                          | 20    | 50  | 80                       | %     |                                                                                                                                                                         |

| F <sub>MAX</sub>                     | Maximum frequency of signal on row input or row output. | _     | -   | 12.7                     | MHz   |                                                                                                                                                                         |

| SR <sub>POWER_UP</sub>               | Power supply slew rate                                  | _     | _   | 250                      | V/ms  | V <sub>DD</sub> slew rate during power-up.                                                                                                                              |

| t <sub>POWERUP</sub>                 | Time from end of POR to CPU executing code              | _     | 16  | 100                      | ms    | Power-up from 0 V. See the System<br>Resets section of the PSoC<br>Technical Reference Manual.                                                                          |

| t <sub>jit_IMO</sub> <sup>[29]</sup> | 12 MHz IMO cycle-to-cycle jitter (RMS)                  | _     | 400 | 1000                     | ps    | N = 32                                                                                                                                                                  |

| 7 -                                  | 12 MHz IMO long term N cycle-to-cycle jitter (RMS)      | -     | 600 | 1300                     | ps    |                                                                                                                                                                         |

|                                      | 12 MHz IMO period jitter (RMS)                          | -     | 100 | 500                      | ps    |                                                                                                                                                                         |

| t <sub>jit_PLL</sub> <sup>[29]</sup> | 12 MHz IMO cycle-to-cycle jitter (RMS)                  | -     | 400 | 1000                     | ps    | N = 32                                                                                                                                                                  |

|                                      | 12 MHz IMO long term N cycle-to-cycle jitter (RMS)      | _     | 700 | 1300                     |       |                                                                                                                                                                         |

|                                      | 12 MHz IMO period jitter (RMS)                          | _     | 300 | 500                      |       |                                                                                                                                                                         |

Notes

27. 2.4 V < V<sub>DD</sub> < 3.0 V.

28. Refer to application note Adjusting PSoC® Trims for 3.3 V and 2.7 V Operation – AN2012 for information on trimming for operation at 3.3 V.

29. Refer to Cypress Jitter Specifications application note, Understanding Datasheet Jitter Specifications for Cypress Timing Products – AN5054 for more information.

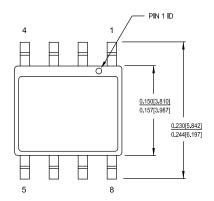

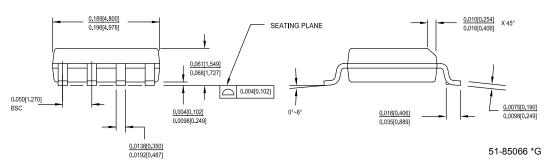

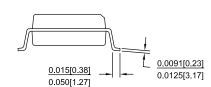

Figure 18. 8-Pin (150-Mil) SOIC

- 1. DIMENSIONS IN INCHES[MM]  $\frac{\text{MIN.}}{\text{MAX.}}$

- PIN 1 ID IS OPTIONAL,

ROUND ON SINGLE LEADFRAME

RECTANGULAR ON MATRIX LEADFRAME

- 3. REFERENCE JEDEC MS-012

- 4. PACKAGE WEIGHT 0.07gms

| PART #  |               |  |  |  |  |

|---------|---------------|--|--|--|--|

| S08.15  | STANDARD PKG  |  |  |  |  |

| SZ08.15 | LEAD FREE PKG |  |  |  |  |

| SW8.15  | LEAD FREE PKG |  |  |  |  |

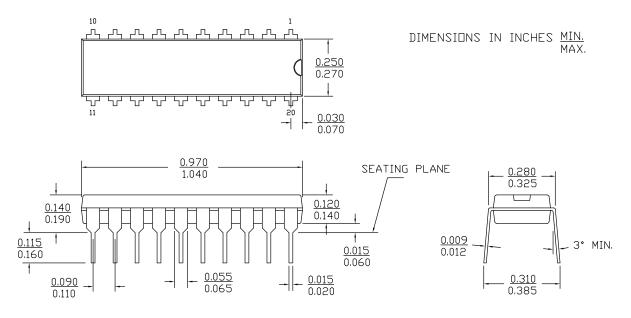

Figure 19. 20-Pin (300-Mil) Molded DIP

51-85011 \*D

Figure 20. 20-Pin (210-Mil) SSOP 1.14 DIA. PIN 1 ID. 10 1 1.14 7.50 8.10 DIMENSIONS IN MILLIMETERS MIN. MAX. 11 20 .235 MIN.- $\frac{7.00}{7.40}$ 0° MIN.-GAUGE PLANE 0.25 SEATING PLANE 0.65 BSC. <u>5.00</u> 5.60 0.-8. 2.00 1.65 1.85 0.55 1.25 REF. MAX 0.10 51-85077 \*F

Figure 21. 20-Pin (300-Mil) Molded SOIC

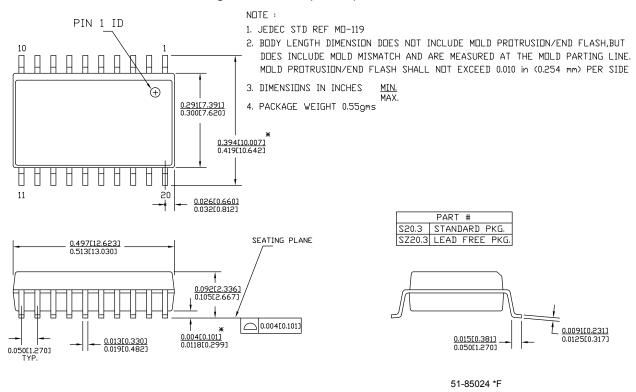

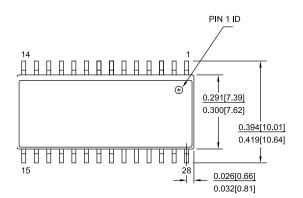

Figure 24. 28-Pin (300-Mil) Molded SOIC

### NOTE:

- 1. JEDEC STD REF MO-119

- 2. BODY LENGTH DIMENSION DOES NOT INCLUDE MOLD PROTRUSION/END FLASH,BUT DOES INCLUDE MOLD MISMATCH AND ARE MEASURED AT THE MOLD PARTING LINE. MOLD PROTRUSION/END FLASH SHALL NOT EXCEED 0.010 in (0.254 mm) PER SIDE

| PART # |                |  |  |  |  |

|--------|----------------|--|--|--|--|

| S28.3  | STANDARD PKG.  |  |  |  |  |

| SZ28.3 | LEAD FREE PKG. |  |  |  |  |

| SX28.3 | LEAD FREE PKG. |  |  |  |  |

51-85026 \*H

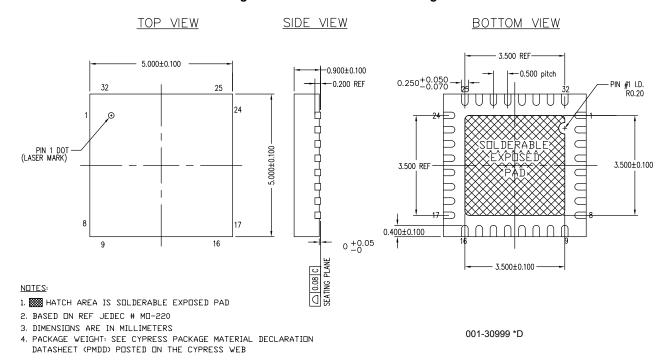

Figure 25. 32-Pin Sawn QFN Package

**Important Note** For information on the preferred dimensions for mounting QFN packages, see the application note, *Application Notes* for Surface Mount Assembly of Amkor's MicroLeadFrame (MLF) Packages available at http://www.amkor.com.

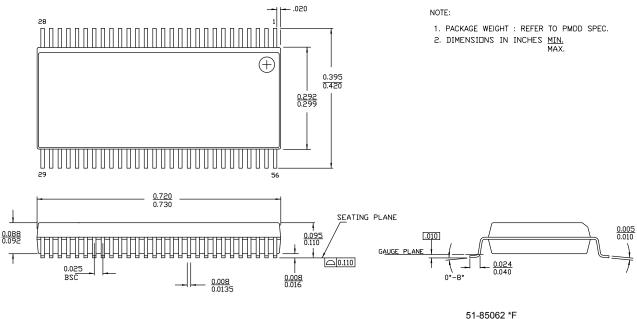

Figure 26. 56-Pin (300-Mil) SSOP

# **Thermal Impedances**

# Table 48. Thermal Impedances per Package

| Package                    | Typical θ <sub>JA</sub> <sup>[38]</sup> |

|----------------------------|-----------------------------------------|

| 8-pin PDIP                 | 123 °C/W                                |

| 8-pin SOIC                 | 185 °C/W                                |

| 20-pin PDIP                | 109 °C/W                                |

| 20-pin SSOP                | 117 °C/W                                |

| 20-pin SOIC                | 81 °C/W                                 |

| 28-pin PDIP                | 69 °C/W                                 |

| 28-pin SSOP                | 101 °C/W                                |

| 28-pin SOIC                | 74 °C/W                                 |

| 32-pin QFN <sup>[39]</sup> | 22 °C/W                                 |

# **Capacitance on Crystal Pins**

Table 49. Typical Package Capacitance on Crystal Pins

| Package     | Package Capacitance |

|-------------|---------------------|

| 8-pin PDIP  | 2.8 pF              |

| 8-pin SOIC  | 2.0 pF              |

| 20-pin PDIP | 3.0 pF              |

| 20-pin SSOP | 2.6 pF              |

| 20-pin SOIC | 2.5 pF              |

| 28-pin PDIP | 3.5 pF              |

| 28-pin SSOP | 2.8 pF              |

| 28-pin SOIC | 2.7 pF              |

| 32-pin QFN  | 2.0 pF              |

# **Solder Reflow Specifications**

Table 50 shows the solder reflow temperature limits that must not be exceeded.

Table 50. Solder Reflow Specifications

| Package           | Maximum Peak<br>Temperature (T <sub>C</sub> ) | Maximum Time<br>above T <sub>C</sub> – 5 °C |

|-------------------|-----------------------------------------------|---------------------------------------------|

| 8-pin PDIP 260 °C |                                               | 30 seconds                                  |

| 8-pin SOIC        | 260 °C                                        | 30 seconds                                  |

| 20-pin PDIP       | 260 °C                                        | 30 seconds                                  |

| 20-pin SSOP       | 260 °C                                        | 30 seconds                                  |

| 20-pin SOIC       | 260 °C                                        | 30 seconds                                  |

| 28-pin PDIP       | 260 °C                                        | 30 seconds                                  |

| 28-pin SSOP       | 260 °C                                        | 30 seconds                                  |

| 28-pin SOIC       | 260 °C                                        | 30 seconds                                  |

| 32-pin QFN        | 260 °C                                        | 30 seconds                                  |

<sup>38.</sup> T<sub>J</sub> = T<sub>A</sub> + Power × θ<sub>JA</sub>

39. To achieve the thermal impedance specified for the QFN package, refer to Application Notes for Surface Mount Assembly of Amkor's MicroLeadFrame (MLF) Packages available at www.amkor.com.

# **Ordering Information**

The following table lists the CY8C24x23A PSoC device's key package features and ordering codes.

Table 52. CY8C24x23A PSoC Device Key Features and Ordering Information

| Package                                                | Ordering<br>Code                  | Flash<br>(Bytes) | SRAM<br>(Bytes) | Switch Mode<br>Pump | Temperature<br>Range | Digital Blocks | Analog Blocks | Digital I/O Pins | Analog Inputs | Analog Outputs | XRES Pin |

|--------------------------------------------------------|-----------------------------------|------------------|-----------------|---------------------|----------------------|----------------|---------------|------------------|---------------|----------------|----------|

| 8-pin (300-mil) DIP                                    | CY8C24123A-24PXI                  | 4 K              | 256             | No                  | -40 °C to +85 °C     | 4              | 6             | 6                | 4             | 2              | No       |

| 8-pin (150-mil) SOIC                                   | CY8C24123A-24SXI                  | 4 K              | 256             | No                  | –40 °C to +85 °C     | 4              | 6             | 6                | 4             | 2              | No       |

| 8-pin (150-mil) SOIC<br>(Tape and Reel)                | CY8C24123A-24SXIT                 | 4 K              | 256             | No                  | –40 °C to +85 °C     | 4              | 6             | 6                | 4             | 2              | No       |

| 20-pin (300-mil) DIP                                   | CY8C24223A-24PXI                  | 4 K              | 256             | Yes                 | -40 °C to +85 °C     | 4              | 6             | 16               | 8             | 2              | Yes      |

| 20-pin (210-mil) SSOP                                  | CY8C24223A-24PVXI                 | 4 K              | 256             | Yes                 | -40 °C to +85 °C     | 4              | 6             | 16               | 8             | 2              | Yes      |

| 20-pin (210-mil) SSOP<br>(Tape and Reel)               | CY8C24223A-24PVXIT                | 4 K              | 256             | Yes                 | –40 °C to +85 °C     | 4              | 6             | 16               | 8             | 2              | Yes      |

| 20-pin (300-mil) SOIC                                  | CY8C24223A-24SXI                  | 4 K              | 256             | Yes                 | -40 °C to +85 °C     | 4              | 6             | 16               | 8             | 2              | Yes      |

| 20-pin (300-mil) SOIC<br>(Tape and Reel)               | CY8C24223A-24SXIT                 | 4 K              | 256             | Yes                 | –40 °C to +85 °C     | 4              | 6             | 16               | 8             | 2              | Yes      |

| 28-pin (300-mil) DIP                                   | CY8C24423A-24PXI                  | 4 K              | 256             | Yes                 | –40 °C to +85 °C     | 4              | 6             | 24               | 10            | 2              | Yes      |

| 28-pin (210-mil) SSOP                                  | CY8C24423A-24PVXI                 | 4 K              | 256             | Yes                 | –40 °C to +85 °C     | 4              | 6             | 24               | 10            | 2              | Yes      |

| 28-pin (210-mil) SSOP<br>(Tape and Reel)               | CY8C24423A-24PVXIT                | 4 K              | 256             | Yes                 | –40 °C to +85 °C     | 4              | 6             | 24               | 10            | 2              | Yes      |

| 28-pin (300-mil) SOIC                                  | CY8C24423A-24SXI                  | 4 K              | 256             | Yes                 | -40 °C to +85 °C     | 4              | 6             | 24               | 10            | 2              | Yes      |

| 28-pin (300-mil) SOIC<br>(Tape and Reel)               | CY8C24423A-24SXIT                 | 4 K              | 256             | Yes                 | –40 °C to +85 °C     | 4              | 6             | 24               | 10            | 2              | Yes      |

| 32-pin (5 × 5 mm 1.00 max)<br>Sawn QFN                 | CY8C24423A-24LTXI                 | 4 K              | 256             | Yes                 | –40 °C to +85 °C     | 4              | 6             | 24               | 10            | 2              | Yes      |

| 32-pin (5 × 5 mm 1.00 max)<br>Sawn QFN (Tape and Reel) | CY8C24423A-24LTXIT                | 4 K              | 256             | Yes                 | –40 °C to +85 °C     | 4              | 6             | 24               | 10            | 2              | Yes      |

| 56-pin OCD SSOP                                        | CY8C24000A-24PVXI <sup>[43]</sup> | 4 K              | 256             | Yes                 | –40 °C to +85 °C     | 4              | 6             | 24               | 10            | 2              | Yes      |

Note For Die sales information, contact a local Cypress sales office or Field Applications Engineer (FAE).

# **Ordering Code Definitions**

### Note

<sup>43.</sup> This part may be used for in-circuit debugging. It is NOT available for production.

## **Errata**

This section describes the errata for the CY8C24xxxA device family. Details include errata trigger conditions, scope of impact, available workaround, and silicon revision applicability. Contact your local Cypress Sales Representative if you have questions.

### **Part Numbers Affected**

| Part Number | Ordering Information |

|-------------|----------------------|

| CY8C24123A  | CY8C24123A-24PXI     |

|             | CY8C24123A-24SXI     |

|             | CY8C24123A-24SXIT    |

|             | CY8C24223A-24PXI     |

|             | CY8C24223A-24PVXI    |

|             | CY8C24223A-24PVXIT   |

|             | CY8C24223A-24SXI     |

|             | CY8C24223A-24SXIT    |

|             | CY8C24423A-24PXI     |

|             | CY8C24423A-24PVXI    |

|             | CY8C24423A-24PVXIT   |

|             | CY8C24423A-24SXI     |

|             | CY8C24423A-24SXIT    |

|             | CY8C24423A-24LFXI    |

|             | CY8C24423A-24LTXI    |

|             | CY8C24423A-24LTXIT   |

|             | CY8C24000A-24PVXI    |

## CY8C24123A Qualification Status

**Product Status: Production**

### CY8C24123A Errata Summary

The following table defines the errata applicability to available CY8C24123A family devices.

| Items                                                                            | Part Number | Silicon Revision | Fix Status                                            |

|----------------------------------------------------------------------------------|-------------|------------------|-------------------------------------------------------|

| [1.]. Internal Main Oscillator (IMO) Tolerance Deviation at Temperature Extremes | CY8C24123A  |                  | No silicon fix planned.<br>Workaround is<br>required. |

### 1. Internal Main Oscillator (IMO) Tolerance Deviation at Temperature Extremes

### ■ Problem Definition

Asynchronous Digital Communications Interfaces may fail framing beyond 0 to 70  $^{\circ}$ C. This problem does not affect end-product usage between 0 and 70  $^{\circ}$ C.

### ■ Parameters Affected

The IMO frequency tolerance. The worst case deviation when operated below  $0^{\circ}$ C and above +70  $^{\circ}$ C and within the upper and lower datasheet temperature range is  $\pm 5\%$ .

## ■ Trigger Condition(S)

The asynchronous Rx/Tx clock source IMO frequency tolerance may deviate beyond the data sheet limit of  $\pm 2.5\%$  when operated beyond the temperature range of 0 to  $\pm 70$  °C.

### ■ Scope of Impact

This problem may affect UART, IrDA, and FSK implementations.

### **■** Workaround

Implement a quartz crystal stabilized clock source on at least one end of the asynchronous digital communications interface.

### Fix Status

Silicon fix is not planned. The workaround mentioned above should be used.

# **Document History Page**

|          | Document Title: CY8C24123A/CY8C24223A/CY8C24423A, PSoC <sup>®</sup> Programmable System-on-Chip Document Number: 38-12028 |                    |                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

|----------|---------------------------------------------------------------------------------------------------------------------------|--------------------|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Revision | ECN                                                                                                                       | Orig. of<br>Change | Submission<br>Date | Description of Change                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| **       | 236409                                                                                                                    | SFV                | See ECN            | New silicon and new document – Preliminary datasheet.                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| *A       | 247589                                                                                                                    | SFV                | See ECN            | Changed the title to read "Final" datasheet. Updated Electrical Specifications chapter.                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

| *B       | 261711                                                                                                                    | HMT                | See ECN            | Input all SFV memo changes. Updated Electrical Specifications chapter.                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

| *C       | 279731                                                                                                                    | HMT                | See ECN            | Update Electrical Specifications chapter, including 2.7 VIL DC GPIO spec. Add Solder Reflow Peak Temperature table. Clean up pinouts and fine tune wording and format throughout.                                                                                                                                                                                                                                                                                  |  |  |  |

| *D       | 352614                                                                                                                    | HMT                | See ECN            | Add new color and CY logo. Add URL to preferred dimensions for mounting MLF packages. Update Transmitter and Receiver AC Digital Block Electrical Specifications. Re-add ISSP pinout identifier. Delete Electrical Specification sentence re: devices running at greater than 12 MHz. Update Solder Reflow Peak Temperature table. Fix CY.com URLs. Update CY copyright.                                                                                           |  |  |  |

| *E       | 424036                                                                                                                    | HMT                | See ECN            | Fix SMP 8-pin SOIC error in Feature and Order table. Update 32-pin QFN E-Pad dimensions and rev. *A. Add ISSP note to pinout tables. Update typical and recommended Storage Temperature per industrial specs. Add OCD non-production pinout and package diagram. Update CY branding and QFN convention. Update package diagram revisions.                                                                                                                          |  |  |  |

| *F       | 521439                                                                                                                    | HMT                | See ECN            | Add Low Power Comparator (LPC) AC/DC electrical spec. tables. Add new Dev. Tool section. Add CY8C20x34 to PSoC Device Characteristics table.                                                                                                                                                                                                                                                                                                                       |  |  |  |

| *G       | 2256806                                                                                                                   | UVS /<br>PYRS      | See ECN            | Added Sawn pin information.                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| *H       | 2425586                                                                                                                   | DSO /<br>AESA      | See ECN            | Corrected Ordering Information to include CY8C24423A-24LTXI and CY8C24423A-24LTXIT                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

| *        | 2619935                                                                                                                   | OGNE /<br>AESA     | 12/11/2008         | Changed title to "CY8C24123A, CY8C24223A, CY8C24423A PSoC <sup>®</sup> Programmable System-on-Chip™" Updated package diagram 001-30999 to *A. Added note on digital signaling in DC Analog Reference Specifications on page 28. Added Die Sales information note to Ordering Information on page 60.                                                                                                                                                               |  |  |  |

| *J       | 2692871                                                                                                                   | DPT /<br>PYRS      | 04/16/2009         | Updated Max package thickness for 32-pin QFN package Formatted Notes Updated "Getting Started" on page 7 Updated "Development Tools" on page 8 and "Designing with PSoC Designer" on page 9                                                                                                                                                                                                                                                                        |  |  |  |