# E·XFL

#### NXP USA Inc. - MKV31F128VLH10 Datasheet

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                 |

|----------------------------|------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4                                                        |

| Core Size                  | 32-Bit Single-Core                                                     |

| Speed                      | 100MHz                                                                 |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                      |

| Peripherals                | DMA, PWM, WDT                                                          |

| Number of I/O              | 46                                                                     |

| Program Memory Size        | 128KB (128K x 8)                                                       |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | · ·                                                                    |

| RAM Size                   | 24K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 1.71V ~ 3.6V                                                           |

| Data Converters            | A/D 2x16b; D/A 1x12b                                                   |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 64-LQFP                                                                |

| Supplier Device Package    | 64-LQFP (10x10)                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mkv31f128vlh10 |

|                            |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

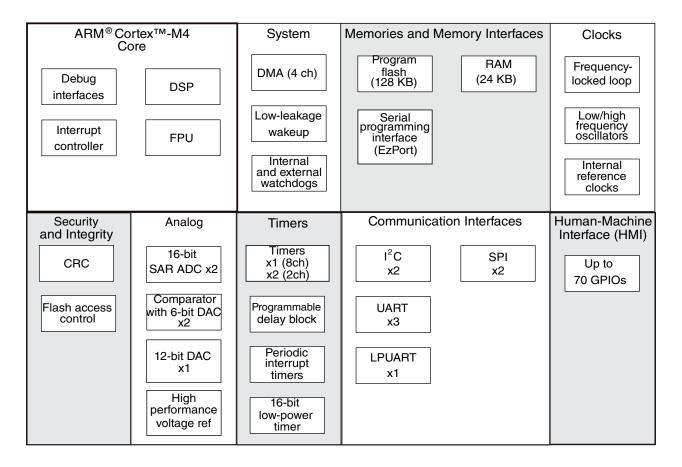

Figure 1. Functional block diagram

| Symbol                | Description                                                                    | Min. | Тур. | Max. | Unit | Notes |

|-----------------------|--------------------------------------------------------------------------------|------|------|------|------|-------|

|                       | @ 70°C                                                                         | —    | 1.78 | 2.09 | μA   |       |

|                       | @ 85°C                                                                         | _    | 2.8  | 3.25 | μA   |       |

|                       | @ 105°C                                                                        | _    | 4.0  | 6.15 | μA   |       |

| I <sub>DD_VLLS0</sub> | Very low-leakage stop mode 0 current at 3.0 V with POR detect circuit enabled  |      |      |      |      |       |

|                       | @ -40°C to 25°C                                                                | _    | 0.40 | 0.49 | μA   |       |

|                       | @ 70°C                                                                         | _    | 1.38 | 1.49 | μA   |       |

|                       | @ 85°C                                                                         | _    | 2.40 | 2.70 | μA   |       |

|                       | @ 105°C                                                                        | _    | 3.6  | 5.65 | μA   |       |

| I <sub>DD_VLLS0</sub> | Very low-leakage stop mode 0 current at 3.0 V with POR detect circuit disabled |      |      |      |      |       |

|                       | @ -40°C to 25°C                                                                | _    | 0.12 | 0.19 | μA   |       |

|                       | @ 70°C                                                                         | _    | 1.05 | 1.13 | μA   |       |

|                       | @ 85°C                                                                         | _    | 2.1  | 2.45 | μA   |       |

|                       | @ 105°C                                                                        | —    | 3.3  | 5.35 | μA   |       |

Table 5. Power consumption operating behaviors (continued)

- 1. The analog supply current is the sum of the active or disabled current for each of the analog modules on the device. See each module's specification for its supply current.

- 2. Cache on and prefetch on, low compiler optimization.

- 3. Coremark benchmark compiled using IAR 7.2 withs optimization level low.

- 4. 100 MHz core and system clock, 50 MHz bus clock, and 25 MHz flash clock. MCG configured for FEE mode. All peripheral clocks disabled.

- 100MHz core and system clock, 50MHz bus clock, and 25MHz flash clock. MCG configured for FEI mode. All peripheral clocks disabled.

- 6. 100MHz core and system clock, 50MHz bus clock, and 25MHz flash clock. MCG configured for FEI mode. All peripheral clocks enabled.

- 7. 72 MHz core and system clock, 36 MHz bus clock, and 24 MHz flash clock. MCG configured for FEE mode. All peripheral clocks disabled. Compute operation.

- 8. 72MHz core and system clock, 36MHz bus clock, and 24MHz flash clock. MCG configured for FEI mode. All peripheral clocks disabled.

- 9. 72MHz core and system clock, 36MHz bus clock, and 24MHz flash clock. MCG configured for FEI mode. All peripheral clocks enabled.

- 10. 72MHz core and system clock, 36MHz bus clock, and 24MHz flash clock. MCG configured for FEI mode. Compute Operation.

- 11. 25MHz core and system clock, 25MHz bus clock, and 25MHz flash clock. MCG configured for FEI mode.

- 12. 4 MHz core, system, and bus clock and 1MHz flash clock. MCG configured for BLPE mode. Compute Operation. Code executing from flash.

- 13. 4 MHz core, system, and bus clock and 1MHz flash clock. MCG configured for BLPE mode. All peripheral clocks disabled. Code executing from flash.

- 14. 4 MHz core, system, and bus clock and 1MHz flash clock. MCG configured for BLPE mode. All peripheral clocks enabled but peripherals are not in active operation. Code executing from flash.

- 15. 4 MHz core, system, and bus clock and 1MHz flash clock. MCG configured for BLPE mode. All peripheral clocks disabled.

#### General

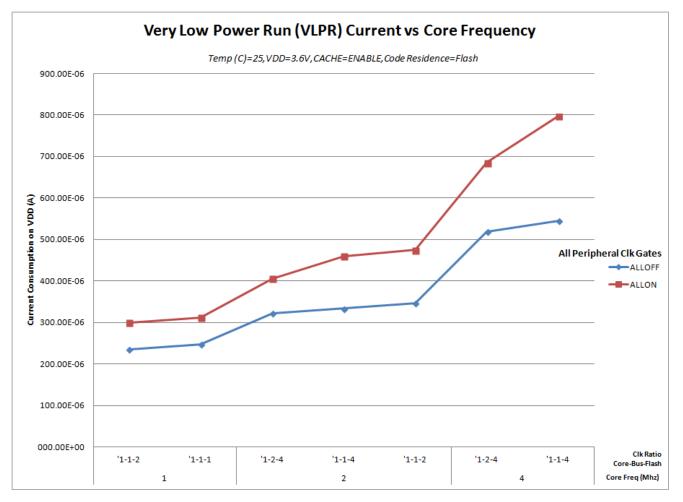

Figure 4. VLPR mode supply current vs. core frequency

# 2.2.6 EMC radiated emissions operating behaviors

### Table 7. EMC radiated emissions operating behaviors for 64 LQFP package

| Parame<br>ter    | Conditions                                 | Clocks                    | Frequency range | Level<br>(Typ.) | Unit | Notes   |

|------------------|--------------------------------------------|---------------------------|-----------------|-----------------|------|---------|

| V <sub>EME</sub> | Device configuration, test                 | FSYS = 100 MHz            | 150 kHz–50 MHz  | 13              | dBuV | 1, 2, 3 |

|                  | conditions and EM testing per standard IEC | FBUS = 50 MHz             | 50 MHz–150 MHz  | 24              |      |         |

|                  |                                            | External crystal = 10 MHz | 150 MHz–500 MHz | 23              |      |         |

|                  | Supply vollages.                           | 500 MHz–1000 MHz          | 7               |                 |      |         |

|                  |                                            | IEC level                 | L               |                 | 4    |         |

1. Measurements were made per IEC 61967-2 while the device was running typical application code.

2. Measurements were performed on a similar 64LQFP device.

3. The reported emission level is the value of the maximum measured emission, rounded up to the next whole number, from among the measured orientations in each frequency range.

4. IEC Level Maximums: M  $\leq$  18dBmV, L  $\leq$  24dBmV, K  $\leq$  30dBmV, I  $\leq$  36dBmV, H  $\leq$  42dBmV .

16

## 2.2.7 Designing with radiated emissions in mind

To find application notes that provide guidance on designing your system to minimize interference from radiated emissions:

- 1. Go to www.freescale.com.

- 2. Perform a keyword search for "EMC design."

### 2.2.8 Capacitance attributes

Table 8. Capacitance attributes

| Symbol            | Description                     | Min. | Max. | Unit |

|-------------------|---------------------------------|------|------|------|

| C <sub>IN_A</sub> | Input capacitance: analog pins  | —    | 7    | pF   |

| C <sub>IN_D</sub> | Input capacitance: digital pins | _    | 7    | pF   |

# 2.3 Switching specifications

### 2.3.1 Device clock specifications Table 9. Device clock specifications

| Symbol                   | Description                                 | Min.           | Max.           | Unit  | Notes |

|--------------------------|---------------------------------------------|----------------|----------------|-------|-------|

|                          | High Speed run mo                           | ode            |                |       |       |

| f <sub>SYS</sub>         | System and core clock                       | _              | 100            | MHz   |       |

| f <sub>BUS</sub>         | Bus clock                                   | —              | 50             | MHz   |       |

|                          | Normal run mode (and High Speed run mode ur | nless otherwis | se specified a | bove) |       |

| f <sub>SYS</sub>         | System and core clock                       | _              | 72             | MHz   |       |

| f <sub>BUS</sub>         | Bus clock                                   | _              | 50             | MHz   |       |

| f <sub>FLASH</sub>       | Flash clock                                 | _              | 25             | MHz   |       |

| f <sub>LPTMR</sub>       | LPTMR clock                                 | _              | 25             | MHz   |       |

|                          | VLPR mode <sup>1</sup>                      |                |                |       |       |

| f <sub>SYS</sub>         | System and core clock                       | _              | 4              | MHz   |       |

| f <sub>BUS</sub>         | Bus clock                                   |                | 4              | MHz   |       |

| f <sub>FLASH</sub>       | Flash clock                                 | _              | 1              | MHz   |       |

| f <sub>ERCLK</sub>       | External reference clock                    |                | 16             | MHz   |       |

| f <sub>LPTMR_pin</sub>   | LPTMR clock                                 | _              | 25             | MHz   |       |

| f <sub>LPTMR_ERCLK</sub> | LPTMR external reference clock              |                | 16             | MHz   |       |

### 2.4.1 Thermal operating requirements Table 11. Thermal operating requirements

| Symbol         | Description              | Min. | Max. | Unit | Notes |

|----------------|--------------------------|------|------|------|-------|

| TJ             | Die junction temperature | -40  | 125  | °C   |       |

| T <sub>A</sub> | Ambient temperature      | -40  | 105  | °C   | 1     |

1. Maximum  $T_A$  can be exceeded only if the user ensures that  $T_J$  does not exceed maximum  $T_J$ . The simplest method to determine  $T_J$  is:  $T_J = T_A + R_{\Theta JA} \times$  chip power dissipation.

### 2.4.2 Thermal attributes

| Board type           | Symbol            | Description                                                                     | 100 LQFP | 64 LQFP | Unit | Notes |

|----------------------|-------------------|---------------------------------------------------------------------------------|----------|---------|------|-------|

| Single-layer<br>(1s) | R <sub>0JA</sub>  | Thermal<br>resistance,<br>junction to<br>ambient<br>(natural<br>convection)     | 63       | 69      | °C/W | 1     |

| Four-layer<br>(2s2p) | R <sub>0JA</sub>  | Thermal<br>resistance,<br>junction to<br>ambient<br>(natural<br>convection)     | 50       | 51      | °C/W | 2     |

| Single-layer<br>(1s) | R <sub>eJMA</sub> | Thermal<br>resistance,<br>junction to<br>ambient (200<br>ft./min. air<br>speed) | 53       | 57      | °C/W | 3     |

| Four-layer<br>(2s2p) | R <sub>eJMA</sub> | Thermal<br>resistance,<br>junction to<br>ambient (200<br>ft./min. air<br>speed) | 44       | 44      | °C/W | 3     |

| _                    | R <sub>θJB</sub>  | Thermal<br>resistance,<br>junction to<br>board                                  | 36       | 33      | °C/W | 4     |

| —                    | R <sub>θJC</sub>  | Thermal<br>resistance,<br>junction to case                                      | 18       | 18      | °C/W | 5     |

| _                    | Ψ <sub>JT</sub>   | Thermal<br>characterizatio<br>n parameter,<br>junction to                       | 3        | 3       | °C/W | 6     |

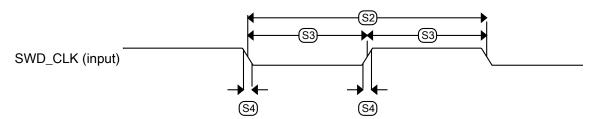

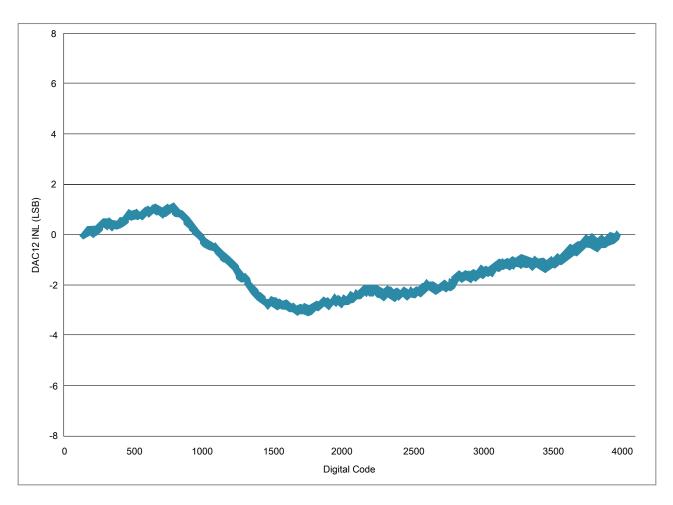

Figure 5. Serial wire clock input timing

### 3.1.2 JTAG electricals

### Table 13. JTAG limited voltage range electricals

| Symbol | Description                 | Min. | Max. | Unit |

|--------|-----------------------------|------|------|------|

|        | Operating voltage           | 2.7  | 3.6  | V    |

| J1     | TCLK frequency of operation |      |      | MHz  |

|        | Boundary Scan               | 0    | 10   |      |

|        | JTAG and CJTAG              | 0    | 20   |      |

| J2     | TCLK cycle period           | 1/J1 | _    | ns   |

| J3     | TCLK clock pulse width      |      |      |      |

|        |                             | 50   | _    | ns   |

Table continues on the next page...

| Symbol | Description                                        | Min. | Max. | Unit |

|--------|----------------------------------------------------|------|------|------|

|        | Boundary Scan                                      | 25   |      | ns   |

|        | JTAG and CJTAG                                     |      |      |      |

| J4     | TCLK rise and fall times                           | —    | 3    | ns   |

| J5     | Boundary scan input data setup time to TCLK rise   | 20   | _    | ns   |

| J6     | Boundary scan input data hold time after TCLK rise | 1    | _    | ns   |

| J7     | TCLK low to boundary scan output data valid        | —    | 25   | ns   |

| J8     | TCLK low to boundary scan output high-Z            | —    | 25   | ns   |

| J9     | TMS, TDI input data setup time to TCLK rise        | 8    | _    | ns   |

| J10    | TMS, TDI input data hold time after TCLK rise      | 1    | _    | ns   |

| J11    | TCLK low to TDO data valid                         | —    | 19   | ns   |

| J12    | TCLK low to TDO high-Z                             | —    | 19   | ns   |

| J13    | TRST assert time                                   | 100  | _    | ns   |

| J14    | TRST setup time (negation) to TCLK high            | 8    | _    | ns   |

Table 13. JTAG limited voltage range electricals (continued)

Table 14. JTAG full voltage range electricals

| Symbol | Description                                        | Min. | Max. | Unit |

|--------|----------------------------------------------------|------|------|------|

|        | Operating voltage                                  | 1.71 | 3.6  | V    |

| J1     | TCLK frequency of operation                        |      |      | MHz  |

|        | Boundary Scan                                      | 0    | 10   |      |

|        | JTAG and CJTAG                                     | 0    | 15   |      |

| J2     | TCLK cycle period                                  | 1/J1 |      | ns   |

| J3     | TCLK clock pulse width                             |      |      |      |

|        | Boundary Scan                                      | 50   | _    | ns   |

|        | JTAG and CJTAG                                     | 33   | _    | ns   |

| J4     | TCLK rise and fall times                           |      | 3    | ns   |

| J5     | Boundary scan input data setup time to TCLK rise   | 20   |      | ns   |

| J6     | Boundary scan input data hold time after TCLK rise | 1.4  | _    | ns   |

| J7     | TCLK low to boundary scan output data valid        | _    | 27   | ns   |

| J8     | TCLK low to boundary scan output high-Z            |      | 27   | ns   |

| J9     | TMS, TDI input data setup time to TCLK rise        | 8    | _    | ns   |

| J10    | TMS, TDI input data hold time after TCLK rise      | 1.4  | —    | ns   |

| J11    | TCLK low to TDO data valid                         |      | 26.2 | ns   |

| J12    | TCLK low to TDO high-Z                             | —    | 26.2 | ns   |

| J13    | TRST assert time                                   | 100  | —    | ns   |

| J14    | TRST setup time (negation) to TCLK high            | 8    |      | ns   |

| Symbol                       | Description                                                                                            | Min. | Тур.            | Max. | Unit | Notes |

|------------------------------|--------------------------------------------------------------------------------------------------------|------|-----------------|------|------|-------|

|                              |                                                                                                        | _    | 0               | —    | kΩ   |       |

| V <sub>pp</sub> <sup>5</sup> | Peak-to-peak amplitude of oscillation (oscillator<br>mode) — low-frequency, low-power mode<br>(HGO=0)  | _    | 0.6             | _    | V    |       |

|                              | Peak-to-peak amplitude of oscillation (oscillator<br>mode) — low-frequency, high-gain mode<br>(HGO=1)  | _    | V <sub>DD</sub> | _    | V    |       |

|                              | Peak-to-peak amplitude of oscillation (oscillator<br>mode) — high-frequency, low-power mode<br>(HGO=0) | _    | 0.6             | _    | V    |       |

|                              | Peak-to-peak amplitude of oscillation (oscillator<br>mode) — high-frequency, high-gain mode<br>(HGO=1) | _    | V <sub>DD</sub> | _    | V    |       |

Table 17. Oscillator DC electrical specifications (continued)

1.  $V_{DD}$ =3.3 V, Temperature =25 °C

2. See crystal or resonator manufacturer's recommendation

3.  $C_x$  and  $C_y$  can be provided by using either integrated capacitors or external components.

4. When low-power mode is selected,  $R_F$  is integrated and must not be attached externally.

5. The EXTAL and XTAL pins should only be connected to required oscillator components and must not be connected to any other device.

# 3.3.3.2 Oscillator frequency specifications

### Table 18. Oscillator frequency specifications

| Symbol                | Description                                                                                           | Min. | Тур. | Max. | Unit | Notes |

|-----------------------|-------------------------------------------------------------------------------------------------------|------|------|------|------|-------|

| f <sub>osc_lo</sub>   | Oscillator crystal or resonator frequency — low-<br>frequency mode (MCG_C2[RANGE]=00)                 | 32   | —    | 40   | kHz  |       |

| f <sub>osc_hi_1</sub> | Oscillator crystal or resonator frequency — high-<br>frequency mode (low range)<br>(MCG_C2[RANGE]=01) | 3    | _    | 8    | MHz  |       |

| f <sub>osc_hi_2</sub> | Oscillator crystal or resonator frequency — high<br>frequency mode (high range)<br>(MCG_C2[RANGE]=1x) | 8    | _    | 32   | MHz  |       |

| f <sub>ec_extal</sub> | Input clock frequency (external clock mode)                                                           |      | _    | 50   | MHz  | 1, 2  |

| t <sub>dc_extal</sub> | Input clock duty cycle (external clock mode)                                                          | 40   | 50   | 60   | %    |       |

| t <sub>cst</sub>      | Crystal startup time — 32 kHz low-frequency,<br>low-power mode (HGO=0)                                | —    | 750  | _    | ms   | 3, 4  |

|                       | Crystal startup time — 32 kHz low-frequency,<br>high-gain mode (HGO=1)                                | —    | 250  | _    | ms   |       |

|                       | Crystal startup time — 8 MHz high-frequency<br>(MCG_C2[RANGE]=01), low-power mode<br>(HGO=0)          | _    | 0.6  | _    | ms   |       |

|                       | Crystal startup time — 8 MHz high-frequency<br>(MCG_C2[RANGE]=01), high-gain mode<br>(HGO=1)          | _    | 1    | —    | ms   |       |

1. Other frequency limits may apply when external clock is being used as a reference for the FLL

| Symbol            | Description                               | Conditions                                                       | Min.      | Typ. <sup>1</sup> | Max.             | Unit | Notes |

|-------------------|-------------------------------------------|------------------------------------------------------------------|-----------|-------------------|------------------|------|-------|

| $\Delta V_{SSA}$  | Ground voltage                            | Delta to $V_{SS}$ ( $V_{SS} - V_{SSA}$ )                         | -100      | 0                 | +100             | mV   | 2     |

| V <sub>REFH</sub> | ADC reference voltage high                |                                                                  | 1.13      | V <sub>DDA</sub>  | V <sub>DDA</sub> | V    |       |

| V <sub>REFL</sub> | ADC reference voltage low                 |                                                                  | $V_{SSA}$ | V <sub>SSA</sub>  | V <sub>SSA</sub> | V    |       |

| V <sub>ADIN</sub> | Input voltage                             | 16-bit differential mode                                         | VREFL     |                   | 31/32 *<br>VREFH | V    |       |

|                   |                                           | All other modes                                                  | VREFL     | —                 | VREFH            |      |       |

| C <sub>ADIN</sub> | Input                                     | 16-bit mode                                                      | _         | 8                 | 10               | pF   |       |

|                   | capacitance                               | <ul> <li>8-bit / 10-bit / 12-bit<br/>modes</li> </ul>            | _         | 4                 | 5                |      |       |

| R <sub>ADIN</sub> | Input series resistance                   |                                                                  | _         | 2                 | 5                | kΩ   |       |

| R <sub>AS</sub>   | Analog source<br>resistance<br>(external) | 13-bit / 12-bit modes<br>f <sub>ADCK</sub> < 4 MHz               | _         | _                 | 5                | kΩ   | 3     |

| f <sub>ADCK</sub> | ADC conversion<br>clock frequency         | ≤ 13-bit mode                                                    | 1.0       |                   | 24.0             | MHz  | 4     |

| f <sub>ADCK</sub> | ADC conversion<br>clock frequency         | 16-bit mode                                                      | 2.0       | _                 | 12.0             | MHz  | 4     |

| C <sub>rate</sub> | ADC conversion                            | ≤ 13-bit modes                                                   |           |                   |                  |      | 5     |

|                   | rate                                      | No ADC hardware averaging                                        | 20        | —                 | 1200             | Ksps |       |

|                   |                                           | Continuous conversions<br>enabled, subsequent<br>conversion time |           |                   |                  |      |       |

| C <sub>rate</sub> | ADC conversion                            | 16-bit mode                                                      |           |                   |                  |      | 5     |

|                   | rate                                      | No ADC hardware averaging                                        | 37        | —                 | 461              | Ksps |       |

|                   |                                           | Continuous conversions<br>enabled, subsequent<br>conversion time |           |                   |                  |      |       |

Table 24.

16-bit ADC operating conditions (continued)

- 1. Typical values assume  $V_{DDA}$  = 3.0 V, Temp = 25 °C,  $f_{ADCK}$  = 1.0 MHz, unless otherwise stated. Typical values are for reference only, and are not tested in production.

- 2. DC potential difference.

- 3. This resistance is external to MCU. To achieve the best results, the analog source resistance must be kept as low as possible. The results in this data sheet were derived from a system that had < 8  $\Omega$  analog source resistance. The R<sub>AS</sub>/C<sub>AS</sub> time constant should be kept to < 1 ns.

- 4. To use the maximum ADC conversion clock frequency, CFG2[ADHSC] must be set and CFG1[ADLPC] must be clear.

- 5. For guidelines and examples of conversion rate calculation, download the ADC calculator tool.

### 3.6.2 CMP and 6-bit DAC electrical specifications Table 26. Comparator and 6-bit DAC electrical specifications

| Symbol             | Description                                         | Min.                  | Тур. | Max.            | Unit             |

|--------------------|-----------------------------------------------------|-----------------------|------|-----------------|------------------|

| $V_{DD}$           | Supply voltage                                      | 1.71                  | _    | 3.6             | V                |

| I <sub>DDHS</sub>  | Supply current, High-speed mode (EN=1, PMODE=1)     | —                     | -    | 200             | μA               |

| I <sub>DDLS</sub>  | Supply current, low-speed mode (EN=1, PMODE=0)      | —                     | _    | 20              | μA               |

| V <sub>AIN</sub>   | Analog input voltage                                | V <sub>SS</sub> – 0.3 | _    | V <sub>DD</sub> | V                |

| V <sub>AIO</sub>   | Analog input offset voltage                         | —                     | _    | 20              | mV               |

| V <sub>H</sub>     | Analog comparator hysteresis <sup>1</sup>           |                       |      |                 |                  |

|                    | • CR0[HYSTCTR] = 00                                 | _                     | 5    | _               | mV               |

|                    | • CR0[HYSTCTR] = 01                                 | _                     | 10   | _               | mV               |

|                    | • CR0[HYSTCTR] = 10                                 | _                     | 20   | _               | mV               |

|                    | • CR0[HYSTCTR] = 11                                 | _                     | 30   | _               | mV               |

| V <sub>CMPOh</sub> | Output high                                         | V <sub>DD</sub> – 0.5 |      |                 | V                |

| V <sub>CMPOI</sub> | Output low                                          | _                     | _    | 0.5             | V                |

| t <sub>DHS</sub>   | Propagation delay, high-speed mode (EN=1, PMODE=1)  | 20                    | 50   | 200             | ns               |

| t <sub>DLS</sub>   | Propagation delay, low-speed mode (EN=1, PMODE=0)   | 80                    | 250  | 600             | ns               |

|                    | Analog comparator initialization delay <sup>2</sup> | _                     | _    | 40              | μs               |

| I <sub>DAC6b</sub> | 6-bit DAC current adder (enabled)                   | —                     | 7    | —               | μA               |

| INL                | 6-bit DAC integral non-linearity                    | -0.5                  |      | 0.5             | LSB <sup>3</sup> |

| DNL                | 6-bit DAC differential non-linearity                | -0.3                  | _    | 0.3             | LSB              |

1. Typical hysteresis is measured with input voltage range limited to 0.6 to  $V_{DD}$ -0.6 V.

Comparator initialization delay is defined as the time between software writes to change control inputs (Writes to CMP\_DACCR[DACEN], CMP\_DACCR[VRSEL], CMP\_DACCR[VOSEL], CMP\_MUXCR[PSEL], and CMP\_MUXCR[MSEL]) and the comparator output settling to a stable level.

3. 1 LSB =  $V_{reference}/64$

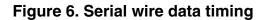

Figure 16. Typical hysteresis vs. Vin level (VDD = 3.3 V, PMODE = 1)

### 3.6.3 12-bit DAC electrical characteristics

### 3.6.3.1 12-bit DAC operating requirements Table 27. 12-bit DAC operating requirements

| Symbol           | Desciption              | Min. | Max. | Unit | Notes |

|------------------|-------------------------|------|------|------|-------|

| V <sub>DDA</sub> | Supply voltage          | 1.71 | 3.6  | V    |       |

| VDACR            | Reference voltage       | 1.13 | 3.6  | V    | 1     |

| CL               | Output load capacitance | —    | 100  | pF   | 2     |

| ۱ <sub>L</sub>   | Output load current     | —    | 1    | mA   |       |

1. The DAC reference can be selected to be  $V_{DDA}$  or  $V_{REFH}$ .

2. A small load capacitance (47 pF) can improve the bandwidth performance of the DAC.

### 3.6.3.2 12-bit DAC operating behaviors Table 28. 12-bit DAC operating behaviors

| Symbol                     | Description                                                                             | Min.                      | Тур.     | Max.              | Unit   | Notes |

|----------------------------|-----------------------------------------------------------------------------------------|---------------------------|----------|-------------------|--------|-------|

| I <sub>DDA_DACL</sub>      | Supply current — low-power mode                                                         |                           | —        | 330               | μΑ     |       |

| I <sub>DDA_DACH</sub><br>P | Supply current — high-speed mode                                                        | _                         | —        | 1200              | μA     |       |

| t <sub>DACLP</sub>         | Full-scale settling time (0x080 to 0xF7F) —<br>low-power mode                           | _                         | 100      | 200               | μs     | 1     |

| t <sub>DACHP</sub>         | Full-scale settling time (0x080 to 0xF7F) — high-power mode                             | _                         | 15       | 30                | μs     | 1     |

| t <sub>CCDACLP</sub>       | Code-to-code settling time (0xBF8 to<br>0xC08) — low-power mode and high-<br>speed mode | _                         | 0.7      | 1                 | μs     | 1     |

| V <sub>dacoutl</sub>       | DAC output voltage range low — high-<br>speed mode, no load, DAC set to 0x000           | —                         | —        | 100               | mV     |       |

| V <sub>dacouth</sub>       | DAC output voltage range high — high-<br>speed mode, no load, DAC set to 0xFFF          | V <sub>DACR</sub><br>-100 | —        | V <sub>DACR</sub> | mV     |       |

| INL                        | Integral non-linearity error — high speed mode                                          |                           | —        | ±8                | LSB    | 2     |

| DNL                        | Differential non-linearity error — V <sub>DACR</sub> > 2<br>V                           |                           | —        | ±1                | LSB    | 3     |

| DNL                        | Differential non-linearity error — V <sub>DACR</sub> = VREF_OUT                         |                           | —        | ±1                | LSB    | 4     |

| V <sub>OFFSET</sub>        | Offset error                                                                            | _                         | ±0.4     | ±0.8              | %FSR   | 5     |

| E <sub>G</sub>             | Gain error                                                                              | _                         | ±0.1     | ±0.6              | %FSR   | 5     |

| PSRR                       | Power supply rejection ratio, $V_{DDA} \ge 2.4 \text{ V}$                               | 60                        | —        | 90                | dB     |       |

| T <sub>CO</sub>            | Temperature coefficient offset voltage                                                  | _                         | 3.7      | _                 | μV/C   | 6     |

| $T_{GE}$                   | Temperature coefficient gain error                                                      | —                         | 0.000421 | _                 | %FSR/C |       |

| Rop                        | Output resistance (load = $3 \text{ k}\Omega$ )                                         | —                         |          | 250               | Ω      |       |

| SR                         | Slew rate -80h $\rightarrow$ F7Fh $\rightarrow$ 80h                                     |                           |          |                   | V/µs   |       |

|                            | <ul> <li>High power (SP<sub>HP</sub>)</li> </ul>                                        | 1.2                       | 1.7      | -                 |        |       |

|                            | Low power (SP <sub>LP</sub> )                                                           | 0.05                      | 0.12     | -                 |        |       |

| BW                         | 3dB bandwidth                                                                           |                           |          |                   | kHz    |       |

|                            | <ul> <li>High power (SP<sub>HP</sub>)</li> </ul>                                        | 550                       |          | _                 |        |       |

|                            | • Low power (SP <sub>LP</sub> )                                                         | 40                        | _        | -                 |        |       |

- 1. Settling within  $\pm 1$  LSB

- 2. The INL is measured for 0 + 100 mV to  $V_{DACR}$  –100 mV

- 3. The DNL is measured for 0 + 100 mV to  $V_{\text{DACR}}$  –100 mV

- 4. The DNL is measured for 0 + 100 mV to  $V_{DACR}$  –100 mV with  $V_{DDA}$  > 2.4 V

- 5. Calculated by a best fit curve from  $V_{SS}$  + 100 mV to  $V_{DACR}$  100 mV

- 6. V<sub>DDA</sub> = 3.0 V, reference select set for V<sub>DDA</sub> (DACx\_CO:DACRFS = 1), high power mode (DACx\_CO:LPEN = 0), DAC set to 0x800, temperature range is across the full range of the device

#### Peripheral operating requirements and behaviors

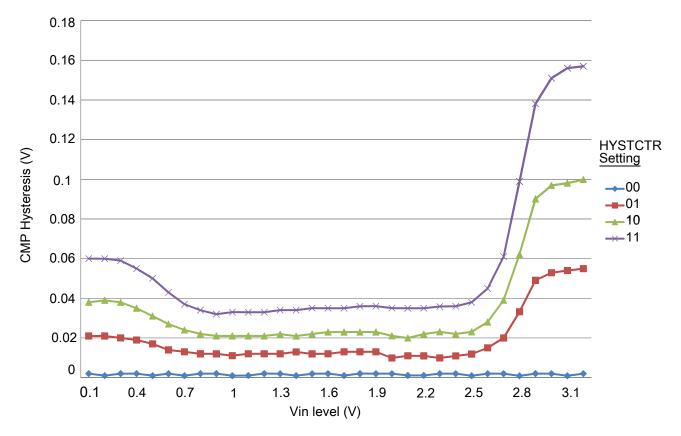

Figure 17. Typical INL error vs. digital code

| Symbol                   | Description                                                                          | Min.   | Тур.   | Max.   | Unit | Notes |

|--------------------------|--------------------------------------------------------------------------------------|--------|--------|--------|------|-------|

| V <sub>out</sub>         | Voltage reference output with factory trim at nominal $V_{DDA}$ and temperature=25°C | 1.1920 | 1.1950 | 1.1980 | V    | 1     |

| V <sub>out</sub>         | Voltage reference output with user trim at nominal $V_{DDA}$ and temperature=25°C    | 1.1945 | 1.1950 | 1.1955 | V    | 1     |

| V <sub>step</sub>        | Voltage reference trim step                                                          | —      | 0.5    | _      | mV   | 1     |

| V <sub>tdrift</sub>      | Temperature drift (Vmax -Vmin across the full temperature range)                     | _      |        | 15     | mV   | 1     |

| I <sub>bg</sub>          | Bandgap only current                                                                 | —      | —      | 80     | μA   |       |

| I <sub>lp</sub>          | Low-power buffer current                                                             | —      | —      | 360    | uA   | 1     |

| I <sub>hp</sub>          | High-power buffer current                                                            | _      | —      | 1      | mA   | 1     |

| $\Delta V_{LOAD}$        | Load regulation                                                                      |        |        |        | μV   | 1, 2  |

|                          | • current = ± 1.0 mA                                                                 | —      | 200    |        |      |       |

| T <sub>stup</sub>        | Buffer startup time                                                                  | —      | —      | 100    | μs   |       |

| T <sub>chop_osc_st</sub> | Internal bandgap start-up delay with chop oscillator enabled                         | —      | —      | 35     | ms   |       |

| V <sub>vdrift</sub>      | Voltage drift (Vmax -Vmin across the full voltage range)                             | —      | 2      | —      | mV   | 1     |

1. See the chip's Reference Manual for the appropriate settings of the VREF Status and Control register.

2. Load regulation voltage is the difference between the VREF\_OUT voltage with no load vs. voltage with defined load

### Table 31. VREF limited-range operating requirements

| Symbol         | Description | Min. | Max. | Unit | Notes |

|----------------|-------------|------|------|------|-------|

| T <sub>A</sub> | Temperature | 0    | 70   | °C   |       |

### Table 32. VREF limited-range operating behaviors

| Symbol              | Description                                                                     | Min. | Max. | Unit | Notes |

|---------------------|---------------------------------------------------------------------------------|------|------|------|-------|

| V <sub>tdrift</sub> | Temperature drift ( $V_{max}$ - $V_{min}$ across the limited temperature range) | —    | 10   | mV   |       |

# 3.7 Timers

See General switching specifications.

# 3.8 Communication interfaces

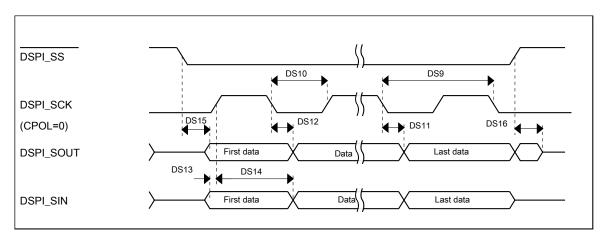

| Num  | Description                              | Min.                      | Max.                      | Unit | Notes |

|------|------------------------------------------|---------------------------|---------------------------|------|-------|

|      | Operating voltage                        | 2.7                       | 3.6                       | V    |       |

|      | Frequency of operation                   | —                         | 12.5                      | MHz  | 1     |

| DS9  | DSPI_SCK input cycle time                | 4 x t <sub>BUS</sub>      | —                         | ns   |       |

| DS10 | DSPI_SCK input high/low time             | (t <sub>SCK</sub> /2) – 2 | (t <sub>SCK</sub> /2) + 2 | ns   |       |

| DS11 | DSPI_SCK to DSPI_SOUT valid              | —                         | 21.4                      | ns   |       |

| DS12 | DSPI_SCK to DSPI_SOUT invalid            | 0                         | —                         | ns   |       |

| DS13 | DSPI_SIN to DSPI_SCK input setup         | 2.6                       | _                         | ns   |       |

| DS14 | DSPI_SCK to DSPI_SIN input hold          | 7                         | _                         | ns   |       |

| DS15 | DSPI_SS active to DSPI_SOUT driven       | —                         | 17                        | ns   |       |

| DS16 | DSPI_SS inactive to DSPI_SOUT not driven | _                         | 17                        | ns   |       |

Table 34. Slave mode DSPI timing (limited voltage range)

1. The maximum operating frequency is measured with noncontinuous CS and SCK. When DSPI is configured with continuous CS and SCK, the SPI clock must not be greater than 1/6 of the bus clock. For example, when the bus clock is 60 MHz, the SPI clock must not be greater than 10 MHz.

Figure 20. DSPI classic SPI timing — slave mode

#### Dimensions

2.  $C_b$  = total capacitance of the one bus line in pF.

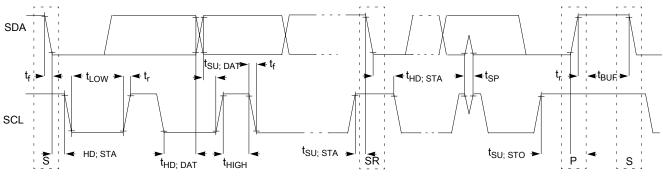

Figure 23. Timing definition for devices on the I<sup>2</sup>C bus

### 3.8.4 UART switching specifications

See General switching specifications.

### 3.9 Kinetis Motor Suite

Kinetis Motor Suite is a bundled software solution that enables the rapid configuration of motor drive systems, and accelerates development of the final motor drive application.

Several members of the KV3x family are enabled with Kinetis motor suite. The enabled devices can be identified within the orderable part numbers in this table. For more information refer to Kinetis Motor Suite User's Guide (KMS100UG) and Kinetis Motor Suite API Reference Manual (KMS100RM).

### NOTE

To find the associated resource, go to freescale.com and perform a search using Document ID.

# 4 Dimensions

### 4.1 Obtaining package dimensions

Package dimensions are provided in package drawings.

To find a package drawing, go to freescale.com and perform a keyword search for the drawing's document number:

| If you want the drawing for this package | Then use this document number |

|------------------------------------------|-------------------------------|

| 64-pin LQFP                              | 98ASS23234W                   |

| 100-pin LQFP                             | 98ASS23308W                   |

# 5 Pinout

# 5.1 KV31F Signal Multiplexing and Pin Assignments

The following table shows the signals available on each pin and the locations of these pins on the devices supported by this document. The Port Control Module is responsible for selecting which ALT functionality is available on each pin.

| 100<br>LQFP | 64<br>LQFP | Pin Name           | Default   | ALT0      | ALT1               | ALT2      | ALT3              | ALT4           | ALT5 | ALT6            | ALT7      | EzPort |

|-------------|------------|--------------------|-----------|-----------|--------------------|-----------|-------------------|----------------|------|-----------------|-----------|--------|

| 1           | 1          | PTE0/<br>CLKOUT32K | ADC1_SE4a | ADC1_SE4a | PTE0/<br>CLKOUT32K | SPI1_PCS1 | UART1_TX          |                |      | I2C1_SDA        |           |        |

| 2           | 2          | PTE1/<br>LLWU_P0   | ADC1_SE5a | ADC1_SE5a | PTE1/<br>LLWU_P0   | SPI1_SOUT | UART1_RX          |                |      | I2C1_SCL        | SPI1_SIN  |        |

| 3           | -          | PTE2/<br>LLWU_P1   | ADC1_SE6a | ADC1_SE6a | PTE2/<br>LLWU_P1   | SPI1_SCK  | UART1_<br>CTS_b   |                |      |                 |           |        |

| 4           | 1          | PTE3               | ADC1_SE7a | ADC1_SE7a | PTE3               | SPI1_SIN  | UART1_<br>RTS_b   |                |      |                 | SPI1_SOUT |        |

| 5           | -          | PTE4/<br>LLWU_P2   | DISABLED  |           | PTE4/<br>LLWU_P2   | SPI1_PCS0 | LPUART0_<br>TX    |                |      |                 |           |        |

| 6           | _          | PTE5               | DISABLED  |           | PTE5               | SPI1_PCS2 | LPUART0_<br>RX    |                |      |                 |           |        |

| 7           | -          | PTE6               | DISABLED  |           | PTE6               | SPI1_PCS3 | LPUART0_<br>CTS_b |                |      |                 |           |        |

| 8           | 3          | VDD                | VDD       | VDD       |                    |           |                   |                |      |                 |           |        |

| 9           | 4          | VSS                | VSS       | VSS       |                    |           |                   |                |      |                 |           |        |

| 10          | 5          | PTE16              | ADC0_SE4a | ADC0_SE4a | PTE16              | SPI0_PCS0 | UART2_TX          | FTM_<br>CLKIN0 |      | FTM0_FLT3       |           |        |

| 11          | 6          | PTE17              | ADC0_SE5a | ADC0_SE5a | PTE17              | SPI0_SCK  | UART2_RX          | FTM_<br>CLKIN1 |      | LPTMR0_<br>ALT3 |           |        |

| 12          | 7          | PTE18              | ADC0_SE6a | ADC0_SE6a | PTE18              | SPI0_SOUT | UART2_<br>CTS_b   | I2C0_SDA       |      |                 |           |        |

| 13          | 8          | PTE19              | ADC0_SE7a | ADC0_SE7a | PTE19              | SPI0_SIN  | UART2_<br>RTS_b   | I2C0_SCL       |      |                 |           |        |

| 14          | -          | ADC0_DP1           | ADC0_DP1  | ADC0_DP1  |                    |           |                   |                |      |                 |           |        |

| 100<br>LQFP | 64<br>LQFP | Pin Name          | Default               | ALT0                  | ALT1              | ALT2      | ALT3              | ALT4           | ALT5   | ALT6            | ALT7            | EzPort |

|-------------|------------|-------------------|-----------------------|-----------------------|-------------------|-----------|-------------------|----------------|--------|-----------------|-----------------|--------|

| 39          | 27         | PTA5              | DISABLED              |                       | PTA5              |           | FTM0_CH2          |                |        |                 | JTAG_<br>TRST_b |        |

| 40          | _          | VDD               | VDD                   | VDD                   |                   |           |                   |                |        |                 |                 |        |

| 41          | -          | VSS               | VSS                   | VSS                   |                   |           |                   |                |        |                 |                 |        |

| 42          | 28         | PTA12             | DISABLED              |                       | PTA12             |           | FTM1_CH0          |                |        |                 | FTM1_QD_<br>PHA |        |

| 43          | 29         | PTA13/<br>LLWU_P4 | DISABLED              |                       | PTA13/<br>LLWU_P4 |           | FTM1_CH1          |                |        |                 | FTM1_QD_<br>PHB |        |

| 44          | _          | PTA14             | DISABLED              |                       | PTA14             | SPI0_PCS0 | UART0_TX          |                |        |                 |                 |        |

| 45          | _          | PTA15             | DISABLED              |                       | PTA15             | SPI0_SCK  | UART0_RX          |                |        |                 |                 |        |

| 46          | -          | PTA16             | DISABLED              |                       | PTA16             | SPI0_SOUT | UARTO_<br>CTS_b   |                |        |                 |                 |        |

| 47          | -          | PTA17             | ADC1_SE17             | ADC1_SE17             | PTA17             | SPI0_SIN  | UART0_<br>RTS_b   |                |        |                 |                 |        |

| 48          | 30         | VDD               | VDD                   | VDD                   |                   |           |                   |                |        |                 |                 |        |

| 49          | 31         | VSS               | VSS                   | VSS                   |                   |           |                   |                |        |                 |                 |        |

| 50          | 32         | PTA18             | EXTAL0                | EXTAL0                | PTA18             |           | FTM0_FLT2         | FTM_<br>CLKIN0 |        |                 |                 |        |

| 51          | 33         | PTA19             | XTAL0                 | XTAL0                 | PTA19             | FTM0_FLT0 | FTM1_FLT0         | FTM_<br>CLKIN1 |        | LPTMR0_<br>ALT1 |                 |        |

| 52          | 34         | RESET_b           | RESET_b               | RESET_b               |                   |           |                   |                |        |                 |                 |        |

| 53          | 35         | PTB0/<br>LLWU_P5  | ADC0_SE8/<br>ADC1_SE8 | ADC0_SE8/<br>ADC1_SE8 | PTB0/<br>LLWU_P5  | I2C0_SCL  | FTM1_CH0          |                |        | FTM1_QD_<br>PHA | UART0_RX        |        |

| 54          | 36         | PTB1              | ADC0_SE9/<br>ADC1_SE9 | ADC0_SE9/<br>ADC1_SE9 | PTB1              | I2C0_SDA  | FTM1_CH1          | FTM0_FLT2      | EWM_IN | FTM1_QD_<br>PHB | UART0_TX        |        |

| 55          | 37         | PTB2              | ADC0_SE12             | ADC0_SE12             | PTB2              | I2C0_SCL  | UART0_<br>RTS_b   | FTM0_FLT1      |        | FTM0_FLT3       |                 |        |

| 56          | 38         | PTB3              | ADC0_SE13             | ADC0_SE13             | PTB3              | I2C0_SDA  | UART0_<br>CTS_b   |                |        | FTM0_FLT0       |                 |        |

| 57          | -          | PTB9              | DISABLED              |                       | PTB9              | SPI1_PCS1 | LPUART0_<br>CTS_b |                |        |                 |                 |        |

| 58          | -          | PTB10             | ADC1_SE14             | ADC1_SE14             | PTB10             | SPI1_PCS0 | LPUART0_<br>RX    |                |        | FTM0_FLT1       |                 |        |

| 59          | 1          | PTB11             | ADC1_SE15             | ADC1_SE15             | PTB11             | SPI1_SCK  | LPUART0_<br>TX    |                |        | FTM0_FLT2       |                 |        |

| 60          | -          | VSS               | VSS                   | VSS                   |                   |           |                   |                |        |                 |                 |        |

| 61          | -          | VDD               | VDD                   | VDD                   |                   |           |                   |                |        |                 |                 |        |

| 62          | 39         | PTB16             | DISABLED              |                       | PTB16             | SPI1_SOUT | UART0_RX          | FTM_<br>CLKIN0 |        | EWM_IN          |                 |        |

| 63          | 40         | PTB17             | DISABLED              |                       | PTB17             | SPI1_SIN  | UART0_TX          | FTM_<br>CLKIN1 |        | EWM_OUT_<br>b   |                 |        |

| 64          | 41         | PTB18             | DISABLED              |                       | PTB18             |           | FTM2_CH0          |                |        | FTM2_QD_<br>PHA |                 |        |

| 65          | 42         | PTB19             | DISABLED              |                       | PTB19             |           | FTM2_CH1          |                |        | FTM2_QD_<br>PHB |                 |        |

| Pin Type     |       | Short recommendation            | Detailed recommendation         |

|--------------|-------|---------------------------------|---------------------------------|

| GPIO/Digital | PTx   | Float                           | Float (default is disabled)     |

| VDDA         | VDDA  | Always connect to VDD potential | Always connect to VDD potential |

| VREFH        | VREFH | Always connect to VDD potential | Always connect to VDD potential |

| VREFL        | VREFL | Always connect to VSS potential | Always connect to VSS potential |

| VSSA         | VSSA  | Always connect to VSS potential | Always connect to VSS potential |

### Table 39. Recommended connection for unused analog interfaces (continued)

# 5.3 KV31F Pinouts

The below figure shows the pinout diagram for the devices supported by this document. Many signals may be multiplexed onto a single pin. To determine what signals can be used on which pin, see the previous section.

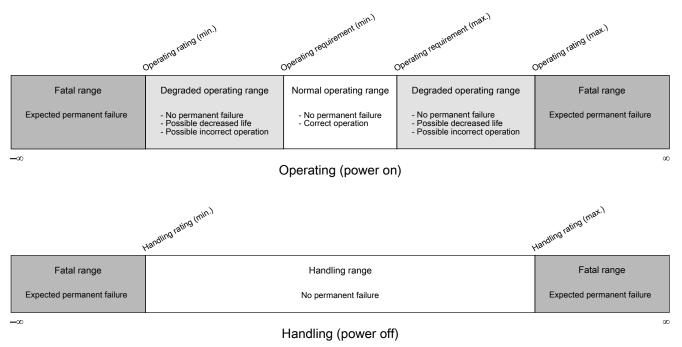

# 7.4 Relationship between ratings and operating requirements

# 7.5 Guidelines for ratings and operating requirements

Follow these guidelines for ratings and operating requirements:

- Never exceed any of the chip's ratings.

- During normal operation, don't exceed any of the chip's operating requirements.

- If you must exceed an operating requirement at times other than during normal operation (for example, during power sequencing), limit the duration as much as possible.

# 8 Revision History

The following table provides a revision history for this document.

| Rev. No.                         | Date    | Substantial Changes                                                                                                                                                                                                                                                 |  |

|----------------------------------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 7                                | 02/2016 | <ul> <li>Added Terminology and Guidelines section</li> <li>Updated the front matter section</li> <li>Added KMS related information in front matter</li> <li>Added Kinetis Motor Suite section</li> <li>Added "S" in Format and Part Identification table</li> </ul> |  |

| Table continues on the next next |         |                                                                                                                                                                                                                                                                     |  |

### Table 40. Revision History

Table continues on the next page...