Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | 8051                                                                    |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 7.3728MHz                                                               |

| Connectivity               | -                                                                       |

| Peripherals                | Brown-out Detect/Reset, LED, POR, WDT                                   |

| Number of I/O              | 6                                                                       |

| Program Memory Size        | 1KB (1K x 8)                                                            |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 128 x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 2.4V ~ 3.6V                                                             |

| Data Converters            | -                                                                       |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 8-SOIC (0.154", 3.90mm Width)                                           |

| Supplier Device Package    | 8-SO                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/p89lpc902fd-112 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

- Serial Flash In-Circuit Programming (ICP) allows simple production coding with commercial EPROM programmers. Flash security bits prevent reading of sensitive application programs.

- Watchdog timer with separate on-chip oscillator, requiring no external components. The watchdog prescaler is selectable from 8 values.

- Low voltage reset (Brownout detect) allows a graceful system shutdown when power fails. May optionally be configured as an interrupt.

- Idle and two different Power-down reduced power modes. Improved wake-up from Power-down mode (a low interrupt input starts execution). Typical Power-down current is 1 µA (total Power-down with voltage comparators disabled).

- Active-LOW reset. On-chip power-on reset allows operation without external reset components. A reset counter and reset glitch suppression circuitry prevent spurious and incomplete resets. A software reset function is also available.

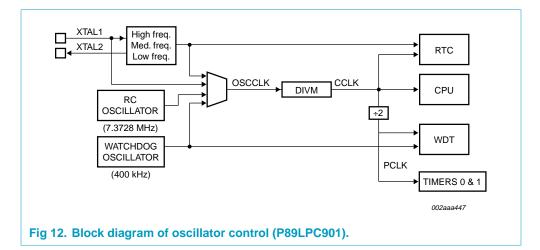

- Configurable on-chip oscillator with frequency range options selected by user programmed Flash configuration bits. Oscillator options support frequencies from 20 kHz to the maximum operating frequency of 18 MHz (P89LPC901).

- Watchdog timer with separate on-chip oscillator, requiring no external components. The watchdog prescaler is selectable from 8 values.

- Programmable port output configuration options: quasi-bidirectional, open drain, push-pull, input-only.

- Port 'input pattern match' detect. Port 0 may generate an interrupt when the value of the pins match or do not match a programmable pattern.

- LED drive capability (20 mA) on all port pins. A maximum limit is specified for the entire chip.

- Controlled slew rate port outputs to reduce EMI. Outputs have approximately 10 ns minimum ramp times.

- Only power and ground connections are required to operate the P89LPC901/902/903 when internal reset option is selected.

- Four interrupt priority levels.

- Two (P89LPC901), three (P89LPC903), or five (P89LPC902) keypad interrupt inputs.

- Second data pointer.

- Schmitt trigger port inputs.

- Emulation support.

## 3. Ordering information

| Table 1:         Ordering information |         |                                                              |         |  |  |  |  |  |  |

|---------------------------------------|---------|--------------------------------------------------------------|---------|--|--|--|--|--|--|

| Type number                           | Package |                                                              |         |  |  |  |  |  |  |

|                                       | Name    | Description                                                  | Version |  |  |  |  |  |  |

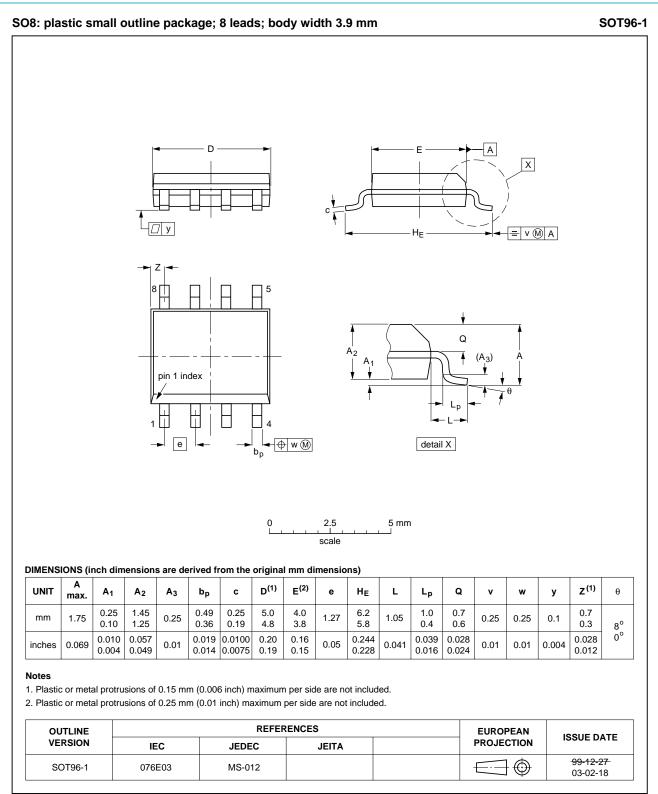

| P89LPC901FD                           | SO8     | plastic small outline package; 8 leads;<br>body width 7.5 mm | SOT96-1 |  |  |  |  |  |  |

| P89LPC902FD                           |         |                                                              |         |  |  |  |  |  |  |

| P89LPC903FD                           |         |                                                              |         |  |  |  |  |  |  |

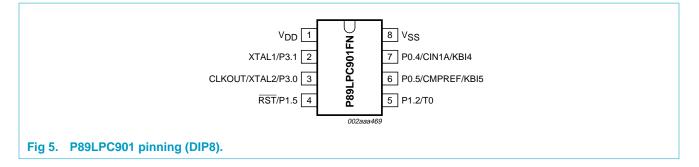

| P89LPC901FN                           | DIP8    | plastic dual in-line package; 8 leads (300 mil)              | SOT97-1 |  |  |  |  |  |  |

| P89LPC902FN                           |         |                                                              |         |  |  |  |  |  |  |

### 3.1 Ordering options

| Table 2:Part options |                   |                         |

|----------------------|-------------------|-------------------------|

| Type number          | Temperature range | Frequency               |

| P89LPC901xx          | –40 °C to +85 °C  | 0 MHz to 18 MHz         |

| P89LPC902xx          |                   | Internal RC or watchdog |

| P89LPC903xx          |                   | Internal RC or watchdog |

8-bit microcontrollers with two-clock 80C51 core

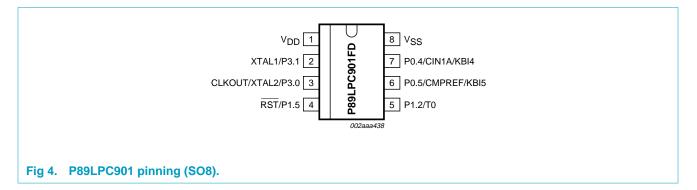

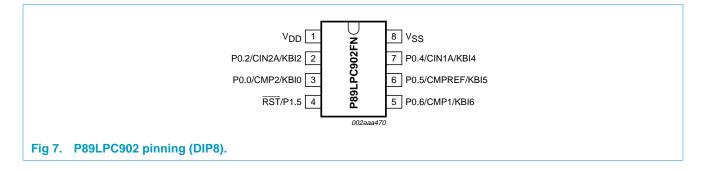

### 5. Pinning information

### 5.1 Pinning

| V <sub>DD</sub> 1<br>P0.2/CIN2A/KBI2 2 | 8 VSS<br>7 P0.4/CIN1A/KBI4<br>6 P0.5/CMPREF/KBI5 |

|----------------------------------------|--------------------------------------------------|

| P0.0/CMP2/KBI0 3                       | 6 P0.5/CMPREF/KBI5                               |

| RST/P1.5 4                             | 5 P0.6/CMP1/KBI6                                 |

|                                        | <i>002aaa439</i>                                 |

| Fig 6. P89LPC902 pinning (SO8).        |                                                  |

| Symbol          | Pin | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-----------------|-----|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P1.0 to P1.5    |     |      | <b>Port 1:</b> Port 1 is an I/O port with a user-configurable output type. During reset Port 1 latches are configured in the input only mode with the internal pull-up disabled. The operation of the configurable Port 1 pins as inputs and outputs depends upon the port configuration selected. Each of the configurable port pins are programmed independently. Refer to Section 8.12.1 "Port configurations" and Table 13 "DC electrical characteristics" for details. P1.5 is input only.                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                 |     |      | All pins have Schmitt triggered inputs.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                 |     |      | Port 1 also provides various special functions as described below:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                 | 5   | I/O  | P1.2 — Port 1 bit 2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                 |     | 0    | T0 — Timer/counter 0 external count input or overflow output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                 | 4   | I    | P1.5 — Port 1 bit 5 (input only).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                 |     | I    | <b>RST</b> — External Reset input during Power-on or if selected via UCFG1. When functioning as a reset input a LOW on this pin resets the microcontroller, causing I/O ports and peripherals to take on their default states, and the processor begins execution at address 0. When using an oscillator frequency above 12 MHz, the reset input function of P1.5 must be enabled. An external circuit is required to hold the device in reset at power-up until V <sub>DD</sub> has reached its specified level. When system power is removed V <sub>DD</sub> will fall below the minimum specified operating voltage. When using an oscillator frequency above 12 MHz, in some applications, an external brownout detect circuit may be required to hold the device in reset when V <sub>DD</sub> falls below the minimum specified operating voltage. Also used during a power-on sequence to force In-System Programming mode. |

| P3.0 to P3.1    |     | I/O  | <b>Port 3:</b> Port 3 is an I/O port with a user-configurable output types. During reset Port 3 latches are configured in the input only mode with the internal pull-up disabled. The operation of port 3 pins as inputs and outputs depends upon the port configuration selected. Each port pin is configured independently. Refer to Section 8.12.1 "Port configurations" and Table 13 "DC electrical characteristics" for details. All pins have Schmitt triggered inputs. Port 3 also provides various special functions as described below:                                                                                                                                                                                                                                                                                                                                                                                   |

|                 | 3   | I/O  | <b>P3.0</b> — Port 3 bit 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                 |     | 0    | <b>XTAL2</b> — Output from the oscillator amplifier (when a crystal oscillator option is selected via the FLASH configuration).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                 |     | 0    | <b>CLKOUT</b> — CPU clock divided by 2 when enabled via SFR bit (ENCLK to TRIM.6). It can be used if the CPU clock is the internal RC oscillator, Watchdog oscillator or external clock input, except when XTAL1/XTAL2 are used to generate clock source for the real time clock/system timer.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                 | 2   | I/O  | <b>P3.1</b> — Port 3 bit 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                 |     | Ι    | <b>XTAL1</b> — Input to the oscillator circuit and internal clock generator circuits (when selected via the FLASH configuration). It can be a port pin if internal RC oscillator or Watchdog oscillator is used as the CPU clock source, <b>and</b> if XTAL1/XTAL2 are not used to generate the clock for the real time clock/system timer.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| V <sub>SS</sub> | 8   | I    | Ground: 0 V reference.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| V <sub>DD</sub> | 1   | Ι    | <b>Power Supply:</b> This is the power supply voltage for normal operation as well as Idle and Power-down modes.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

#### Table 3: P89LPC901 pin description...continued

### 7. Special function registers

**Remark:** Special Function Registers (SFRs) accesses are restricted in the following ways:

- User must not attempt to access any SFR locations not defined.

- Accesses to any defined SFR locations must be strictly for the functions for the SFRs.

- SFR bits labeled '-', '0' or '1' can **only** be written and read as follows:

- '-' Unless otherwise specified, **must** be written with '0', but can return any value when read (even if it was written with '0'). It is a reserved bit and may be used in future derivatives.

- '0' **must** be written with '0', and will return a '0' when read.

- '1' must be written with '1', and will return a '1' when read.

# Table 7:P89LPC901 Special function registers\* indicates SFRs that are bit addressable.

| Name   | Description                      | SFR         |             |             | Bit         | functions   | and addres  | ses         |              |             | Reset value         |          |

|--------|----------------------------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|--------------|-------------|---------------------|----------|

|        |                                  | addr.       | MSB         |             |             |             |             |             |              | LSB         | Hex                 | Binary   |

|        | E                                | Bit address | E7          | <b>E6</b>   | E5          | E4          | E3          | E2          | E1           | <b>E0</b>   |                     |          |

| ACC*   | Accumulator                      | E0H         |             |             |             |             |             |             |              |             | 00                  | 0000000  |

| AUXR1  | Auxiliary function register      | A2H         | CLKLP       | -           | -           | ENT0        | SRST        | 0           | -            | DPS         | 00[1]               | 000000x0 |

|        | E                                | Bit address | <b>F7</b>   | <b>F6</b>   | F5          | F4          | F3          | F2          | F1           | <b>F0</b>   |                     |          |

| B*     | B register                       | F0H         |             |             |             |             |             |             |              |             | 00                  | 0000000  |

| CMP1   | Comparator 1 control regis       | ster ACH    | -           | -           | CE1         | -           | CN1         | -           | CO1          | CMF1        | 00 <sup>[1]</sup>   | xx000000 |

| DIVM   | CPU clock divide-by-M<br>control | 95H         |             |             |             |             |             |             |              |             | 00                  | 0000000  |

| DPTR   | Data pointer (2 bytes)           |             |             |             |             |             |             |             |              |             |                     |          |

| DPH    | Data pointer high                | 83H         |             |             |             |             |             |             |              |             | 00                  | 00000000 |

| DPL    | Data pointer low                 | 82H         |             |             |             |             |             |             |              |             | 00                  | 00000000 |

| FMADRH | Program Flash address hig        | gh E7H      |             |             |             |             |             |             |              |             | 00                  | 0000000  |

| FMADRL | Program Flash address lov        | w E6H       |             |             |             |             |             |             |              |             | 00                  | 0000000  |

| FMCON  | Program Flash Control<br>(Read)  | E4H         | BUSY        | -           | -           | -           | HVA         | HVE         | SV           | OI          | 70                  | 01110000 |

|        | Program Flash Control<br>(Write) |             | FMCMD.<br>7 | FMCMD.<br>6 | FMCMD.<br>5 | FMCMD.<br>4 | FMCMD.<br>3 | FMCMD.<br>2 | FMCMD.<br>1  | FMCMD.<br>0 | _                   |          |

| FMDATA | Program Flash data               | E5H         |             |             |             |             |             |             |              |             | 00                  | 0000000  |

| IEN0*  | Interrupt enable 0               | A8H         | EA          | EWDRT       | EBO         | -           | ET1         | -           | ET0          | -           | 00                  | 0000000  |

|        | B                                | Bit address | EF          | EE          | ED          | EC          | EB          | EA          | E9           | <b>E8</b>   |                     |          |

| IEN1*  | Interrupt enable 1               | E8H         | -           | -           | -           | -           | -           | EC          | EKBI         | -           | 00 <sup>[1]</sup>   | 00x00000 |

|        | E                                | Bit address | BF          | BE          | BD          | BC          | BB          | BA          | <b>B</b> 9   | <b>B</b> 8  |                     |          |

| IP0*   | Interrupt priority 0             | B8H         | -           | PWDRT       | PBO         | -           | PT1         | -           | PT0          | -           | 00 <sup>[1]</sup>   | x0000000 |

| IP0H   | Interrupt priority 0 high        | B7H         | -           | PWDRT<br>H  | PBOH        | -           | PT1H        | -           | PT0H         | -           | 00 <mark>[1]</mark> | x0000000 |

|        | B                                | Bit address | FF          | FE          | FD          | FC          | FB          | FA          | F9           | <b>F8</b>   |                     |          |

| IP1*   | Interrupt priority 1             | F8H         | -           | -           | -           | -           | -           | PC          | PKBI         | -           | 00 <sup>[1]</sup>   | 00x00000 |

| IP1H   | Interrupt priority 1 high        | F7H         | -           | -           | -           | -           | -           | PCH         | PKBIH        | -           | 00 <sup>[1]</sup>   | 00x0000  |

| KBCON  | Keypad control register          | 94H         | -           | -           | -           | -           | -           | -           | PATN<br>_SEL | KBIF        | 00 <sup>[1]</sup>   | xxxxxx00 |

8-bit microcontrollers with two-clock 80C51 core

P89LPC901/902/903

9397 750 14 Product data

# Table 8:P89LPC902 Special function registers...continued\* indicates SFRs that are bit addressable.

| 9397 750 14465                              | Name   | Description                            | SFR         |       |              | Bit            | functions a   | nd addre  | sses      |              |           | Reset                    | value    |

|---------------------------------------------|--------|----------------------------------------|-------------|-------|--------------|----------------|---------------|-----------|-----------|--------------|-----------|--------------------------|----------|

|                                             |        |                                        | addr.       | MSB   |              |                |               |           |           |              | LSB       | Hex                      | Binary   |

|                                             | KBCON  | Keypad control register                | 94H         | -     | -            | -              | -             | -         | -         | PATN<br>_SEL | KBIF      | 00 <sup>[1]</sup>        | xxxxxx00 |

|                                             | KBMASK | Keypad interrupt mask register         | 86H         |       |              |                |               |           |           |              |           | 00                       | 0000000  |

|                                             | KBPATN | Keypad pattern register                | 93H         |       |              |                |               |           |           |              |           | FF                       | 1111111  |

|                                             |        |                                        | Bit address | 87    | 86           | 85             | 84            | 83        | 82        | 81           | 80        |                          |          |

|                                             | P0*    | Port 0                                 | 80H         | -     | CMP1<br>/KB6 | CMPREF<br>/KB5 | CIN1A<br>/KB4 | -         | KB2       | -            | KB0       | [1]                      |          |

|                                             |        |                                        | Bit address | 97    | 96           | 95             | 94            | 93        | 92        | 91           | 90        |                          |          |

|                                             | P1*    | Port 1                                 | 90H         | -     | -            | RST            | -             | -         | -         | -            | -         |                          |          |

|                                             |        |                                        | Bit address | B7    | <b>B6</b>    | <b>B5</b>      | <b>B4</b>     | <b>B3</b> | <b>B2</b> | B1           | <b>B0</b> |                          |          |

|                                             | P0M1   | Port 0 output mode 1                   | 84H         | -     | (P0M1.6)     | (P0M1.5)       | (P0M1.4)      | -         | (P0M1.2)  | -            | (P0M1.0)  | FF                       | 1111111  |

|                                             | P0M2   | Port 0 output mode 2                   | 85H         | -     | (P0M2.6)     | (P0M2.5)       | (P0M2.4)      | -         | (P0M2.2)  | -            | (P0M2.0)  | 00                       | 0000000  |

|                                             | P1M1   | Port 1 output mode 1                   | 91H         | -     | -            | (P1M1.5)       | -             | -         | -         | -            | -         | FF <sup>[1]</sup>        | 1111111  |

|                                             | P1M2   | Port 1 output mode 2                   | 92H         | -     | -            | (P1M2.5)       | -             | -         | -         | -            | -         | 00 <sup>[1]</sup>        | 0000000  |

|                                             | PCON   | Power control register                 | 87H         | -     | -            | BOPD           | BOI           | GF1       | GF0       | PMOD1        | PMOD0     | 00                       | 0000000  |

|                                             | PCONA  | Power control register A               | B5H         | RTCPD |              | VCPD           |               |           | -         | -            |           | 00 <sup>[1]</sup>        | 0000000  |

|                                             | PCONB  | reserved for Power Contr<br>Register B | ol B6H      | -     | -            | -              | -             | -         | -         | -            | -         | 00 <sup>[1]</sup>        | XXXXXXXX |

|                                             |        |                                        | Bit address | D7    | <b>D</b> 6   | D5             | D4            | D3        | D2        | D1           | <b>D0</b> |                          |          |

|                                             | PSW*   | Program status word                    | D0H         | CY    | AC           | F0             | RS1           | RS0       | OV        | F1           | Р         | 00                       | 0000000  |

| ©<br>Ko                                     | PT0AD  | Port 0 digital input disable           | e F6H       | -     | -            | PT0AD.5        | PT0AD.4       | -         | PT0AD.2   | -            | -         | 00                       | xx00000  |

| ninklijk                                    | RSTSRC | Reset source register                  | DFH         | -     | -            | BOF            | POF           | -         | R_WD      | R_SF         | R_EX      | [3]                      |          |

| © Koninklijke Philips Electronics N.V. 2004 | RTCCON | Real-time clock control                | D1H         | RTCF  | RTCS1        | RTCS0          | -             | -         | -         | ERTC         | RTCEN     | 60 <sup>[1]</sup><br>[6] | 011xxx0  |

| ectronic                                    | RTCH   | Real-time clock register h             | nigh D2H    |       |              |                |               |           |           |              |           | 00 <mark>[6]</mark>      | 0000000  |

| cs N.V.                                     | RTCL   | Real-time clock register le            | ow D3H      |       |              |                |               |           |           |              |           | 00 <mark>[6]</mark>      | 0000000  |

| 2004                                        | SP     | Stack pointer                          | 81H         |       |              |                |               |           |           |              |           | 07                       | 0000011  |

P89LPC901/902/903

#### Table 8: P89LPC902 Special function registers...continued

| Table 8:<br>7 * indicates 3        | <b>P89LPC902 Special function</b><br>SFRs that are bit addressable. | registers | continued                   | d    |        |        |        |           |        |        |         |          |

|------------------------------------|---------------------------------------------------------------------|-----------|-----------------------------|------|--------|--------|--------|-----------|--------|--------|---------|----------|

| <sup>750</sup> * indicates<br>Name | Description                                                         | SFR       | Bit functions and addresses |      |        |        |        |           |        |        | Reset   | value    |

|                                    |                                                                     | addr.     | MSB                         |      |        |        |        |           |        | LSB    | Hex     | Binary   |

|                                    | Bit a                                                               | ddress    | 8F                          | 8E   | 8D     | 8C     | 8B     | <b>8A</b> | 89     | 88     |         |          |

| TCON*                              | Timer 0 and 1 control                                               | 88H       | TF1                         | TR1  | TF0    | TR0    | -      | -         | -      | -      | 00      | 0000000  |

| TH0                                | Timer 0 high                                                        | 8CH       |                             |      |        |        |        |           |        |        | 00      | 00000000 |

| TH1                                | Timer 1 high                                                        | 8DH       |                             |      |        |        |        |           |        |        | 00      | 00000000 |

| TL0                                | Timer 0 low                                                         | 8AH       |                             |      |        |        |        |           |        |        | 00      | 00000000 |

| TL1                                | Timer 1 low                                                         | 8BH       |                             |      |        |        |        |           |        |        | 00      | 00000000 |

| TMOD                               | Timer 0 and 1 mode                                                  | 89H       | -                           | -    | T1M1   | T1M0   | -      | -         | T0M1   | T0M0   | 00      | 00000000 |

| TRIM                               | Internal oscillator trim register                                   | 96H       | -                           | -    | TRIM.5 | TRIM.4 | TRIM.3 | TRIM.2    | TRIM.1 | TRIM.0 | [5] [6] |          |

| WDCON                              | Watchdog control register                                           | A7H       | PRE2                        | PRE1 | PRE0   | -      | -      | WDRUN     | WDTOF  | WDCLK  | [4] [6] |          |

| WDL                                | Watchdog load                                                       | C1H       |                             |      |        |        |        |           |        |        | FF      | 11111111 |

| WFEED1                             | Watchdog feed 1                                                     | C2H       |                             |      |        |        |        |           |        |        |         |          |

| WFEED2                             | Watchdog feed 2                                                     | СЗН       |                             |      |        |        |        |           |        |        |         |          |

[1] All ports are in input only (high impedance) state after power-up.

BRGR1 and BRGR0 must only be written if BRGEN in BRGCON SFR is '0'. If any are written while BRGEN = 1, the result is unpredictable. [2] Unimplemented bits in SFRs (labeled '-') are X (unknown) at all times. Unless otherwise specified, ones should not be written to these bits since they may be used for other purposes in future derivatives. The reset values shown for these bits are '0's although they are unknown when read.

- The RSTSRC register reflects the cause of the P89LPC901/902/903 reset. Upon a power-up reset, all reset source flags are cleared except POF and BOF; the power-on reset [3] value is xx110000.

- [4] After reset, the value is 111001x1, i.e., PRE2-PRE0 are all '1', WDRUN = 1 and WDCLK = 1. WDTOF bit is '1' after Watchdog reset and is '0' after power-on reset. Other resets will not affect WDTOF.

- On power-on reset, the TRIM SFR is initialized with a factory preprogrammed value. Other resets will not cause initialization of the TRIM register. [5]

- The only reset source that affects these SFRs is power-on reset. [6]

Product data

89LPC901/902/903

# Table 9:P89LPC903 Special function registers...continued\* indicates SFRs that are bit addressable.

| Name   | Description                            | SFR         |       |           | Bit            | functions a   | nd addre | sses     |              |           | Reset                    | value    |

|--------|----------------------------------------|-------------|-------|-----------|----------------|---------------|----------|----------|--------------|-----------|--------------------------|----------|

|        |                                        | addr.       | MSB   |           |                |               |          |          |              | LSB       | Hex                      | Binary   |

| IP1*   | Interrupt priority 1                   | F8H         | -     | PST       | -              | -             | -        | PC       | PKBI         | -         | 00 <sup>[1]</sup>        | 00x0000  |

| IP1H   | Interrupt priority 1 high              | F7H         | -     | PSTH      | -              | -             | -        | PCH      | PKBIH        | -         | 00 <sup>[1]</sup>        | 00x0000  |

| KBCON  | Keypad control register                | 94H         | -     | -         | -              | -             | -        | -        | PATN<br>_SEL | KBIF      | 00 <sup>[1]</sup>        | xxxxxx00 |

| KBMASK | Keypad interrupt mask register         | 86H         |       |           |                |               |          |          |              |           | 00                       | 0000000  |

| KBPATN | Keypad pattern register                | 93H         |       |           |                |               |          |          |              |           | FF                       | 1111111  |

|        |                                        | Bit address | 87    | 86        | 85             | 84            | 83       | 82       | 81           | 80        |                          |          |

| P0*    | Port 0                                 | 80H         | -     | -         | CMPREF<br>/KB5 | CIN1A<br>/KB4 | -        | KB2      | -            | -         | [1]                      |          |

|        |                                        | Bit address | 97    | 96        | 95             | 94            | 93       | 92       | 91           | 90        |                          |          |

| P1*    | Port 1                                 | 90H         | -     | -         | RST            | -             | -        | -        | RxD          | TxD       |                          |          |

| P0M1   | Port 0 output mode 1                   | 84H         | -     | -         | (P0M1.5)       | (P0M1.4)      | -        | (P0M1.2) | -            | -         | FF                       | 1111111  |

| P0M2   | Port 0 output mode 2                   | 85H         | -     | -         | (P0M2.5)       | (P0M2.4)      | -        | (P0M2.2) | -            | -         | 00                       | 000000   |

| P1M1   | Port 1 output mode 1                   | 91H         | -     | -         | (P1M1.5)       | -             | -        | -        | (P1M1.1)     | (P1M1.0)  | FF <sup>[1]</sup>        | 1111111  |

| P1M2   | Port 1 output mode 2                   | 92H         | -     | -         | (P1M2.5)       | -             | -        | -        | (P1M2.1)     | (P1M2.0)  | 00 <sup>[1]</sup>        | 000000   |

| PCON   | Power control register                 | 87H         | SMOD1 | SMOD0     | BOPD           | BOI           | GF1      | GF0      | PMOD1        | PMOD0     | 00                       | 0000000  |

| PCONA  | Power control register A               | B5H         | RTCPD |           | VCPD           |               |          | -        | SPD          |           | 00 <sup>[1]</sup>        | 000000   |

| PCONB  | reserved for Power Contr<br>Register B | rol B6H     | -     | -         | -              | -             | -        | -        | -            | -         | 00 <sup>[1]</sup>        | XXXXXXXX |

|        |                                        | Bit address | D7    | <b>D6</b> | D5             | <b>D4</b>     | D3       | D2       | D1           | <b>D0</b> |                          |          |

| PSW*   | Program status word                    | D0H         | CY    | AC        | F0             | RS1           | RS0      | OV       | F1           | Р         | 00                       | 0000000  |

| PT0AD  | Port 0 digital input disabl            | e F6H       | -     | -         | PT0AD.5        | PT0AD.4       | -        | PT0AD.2  | -            | -         | 00                       | xx00000  |

| RSTSRC | Reset source register                  | DFH         | -     | -         | BOF            | POF           | R_BK     | R_WD     | R_SF         | R_EX      | [3]                      |          |

| RTCCON | Real-time clock control                | D1H         | RTCF  | RTCS1     | RTCS0          | -             | -        | -        | ERTC         | RTCEN     | 60 <sup>[1]</sup><br>[6] | 011xxx0  |

| RTCH   | Real-time clock register l             | nigh D2H    |       |           |                |               |          |          |              |           | 00 <mark>[6]</mark>      | 000000   |

| RTCL   | Real-time clock register I             | ow D3H      |       |           |                |               |          |          |              |           | 00 <mark>[6]</mark>      | 000000   |

| SADDR  | Serial port address regis              | ter A9H     |       |           |                |               |          |          |              |           | 00                       | 0000000  |

| SADEN  | Serial port address enab               | le B9H      |       |           |                |               |          |          |              |           | 00                       | 0000000  |

8-bit microcontrollers with two-clock 80C51 core P89LPC901/902/903

Rev. 05 — 17 December 2004

Product data

#### 8-bit microcontrollers with two-clock 80C51 core

### 8.6 CPU CLock (CCLK) wake-up delay

The P89LPC901/902/903 has an internal wake-up timer that delays the clock until it stabilizes depending to the clock source used. If the clock source is any of the three crystal selections (P89LPC901) the delay is 992 OSCCLK cycles plus 60 to 100  $\mu$ s.

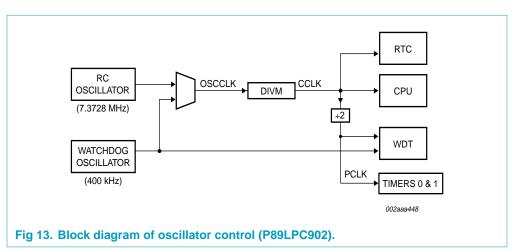

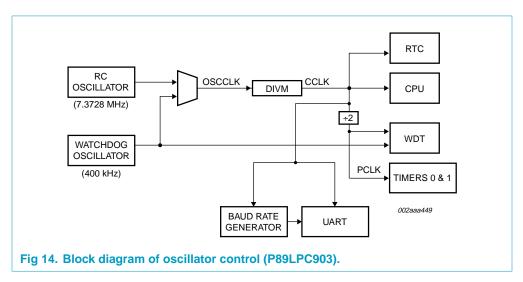

#### 8.7 CPU CLOCK (CCLK) modification: DIVM register

The OSCCLK frequency can be divided down up to 510 times by configuring a dividing register, DIVM, to generate CCLK. This feature makes it possible to temporarily run the CPU at a lower rate, reducing power consumption. By dividing the clock, the CPU can retain the ability to respond to events that would not exit Idle mode by executing its normal program at a lower rate. This can also allow bypassing the oscillator start-up time in cases where Power-down mode would otherwise be used. The value of DIVM may be changed by the program at any time without interrupting code execution.

#### 8.8 Low power select

The P89LPC901 is designed to run at 18 MHz (CCLK) maximum. However, if CCLK is 8 MHz or slower, the CLKLP SFR bit (AUXR1.7) can be set to '1' to lower the power consumption further. On any reset, CLKLP is '0' allowing highest performance access. This bit can then be set in software if CCLK is running at 8 MHz or slower.

#### 8.9 Memory organization

The various P89LPC901/902/903 memory spaces are as follows:

• DATA

128 bytes of internal data memory space (00h:7Fh) accessed via direct or indirect addressing, using instruction other than MOVX and MOVC. All or part of the Stack may be in this area.

SFR

Special Function Registers. Selected CPU registers and peripheral control and status registers, accessible only via direct addressing.

• CODE

64 kB of Code memory space, accessed as part of program execution and via the MOVC instruction. The P89LPC901/902/903 has 1 kB of on-chip Code memory.

#### 8.10 Data RAM arrangement

The 128 bytes of on-chip RAM is organized as follows:

Table 10:

On-chip data memory usages

| Туре | Data RAM                                             | Size (Bytes) |

|------|------------------------------------------------------|--------------|

| DATA | Memory that can be addressed directly and indirectly | 128          |

#### 8.11 Interrupts

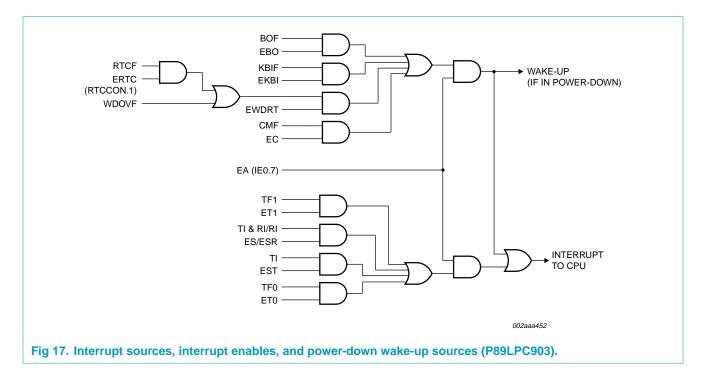

The P89LPC901/902/903 uses a four priority level interrupt structure. This allows great flexibility in controlling the handling of the many interrupt sources.

#### 8-bit microcontrollers with two-clock 80C51 core

#### 8.12 I/O ports

The P89LPC901 has between 3 and 6 I/O pins: P0.4, P0.5, P1.2, P1.5, P3.0, and P3.1 The exact number of I/O pins available depends on the clock and reset options chosen, as shown in Table 11.

| Clock source                              | Reset option                               | Number of I/O pins<br>(8-pin package) |

|-------------------------------------------|--------------------------------------------|---------------------------------------|

| On-chip oscillator or Watchdog oscillator | No external reset (except during power-up) | 6                                     |

|                                           | External RST pin supported                 | 5                                     |

| External clock input                      | No external reset (except during power-up) | 5                                     |

|                                           | External RST pin supported <sup>[1]</sup>  | 4                                     |

| Low/medium/high speed oscillator          | No external reset (except during power-up) | 4                                     |

| (external crystal or resonator)           | External RST pin supported <sup>[1]</sup>  | 3                                     |

#### Table 11: Number of I/O pins available

[1] Required for operation above 12 MHz.

The P89LPC902 and P89LPC903 devices have either 5 or 6 I/O pins depending on the reset pin option chosen.

#### 8.12.1 Port configurations

All but one I/O port pin on the P89LPC901/902/903 may be configured by software to one of four types on a bit-by-bit basis. These are: quasi-bidirectional (standard 80C51 port outputs), push-pull, open drain, and input-only. Two configuration registers for each port select the output type for each port pin.

P1.5 (RST) can only be an input and cannot be configured.

#### 8.12.7 Additional port features

After power-up, all pins are in Input-Only mode. Please note that this is different from the LPC76x series of devices.

- After power-up all I/O pins, except P1.5, may be configured by software.

- Pin P1.5 is input only.

Every output on the P89LPC901/902/903 has been designed to sink typical LED drive current. However, there is a maximum total output current for all ports which must not be exceeded. Please refer to Table 13 "DC electrical characteristics" for detailed specifications.

All ports pins that can function as an output have slew rate controlled outputs to limit noise generated by quickly switching output signals. The slew rate is factory-set to approximately 10 ns rise and fall times.

#### 8.13 Power monitoring functions

The P89LPC901/902/903 incorporates power monitoring functions designed to prevent incorrect operation during initial power-up and power loss or reduction during operation. This is accomplished with two hardware functions: Power-on Detect and Brownout detect.

#### 8.13.1 Brownout detection

The Brownout detect function determines if the power supply voltage drops below a certain level. The default operation is for a Brownout detection to cause a processor reset, however, it may alternatively be configured to generate an interrupt.

Brownout detection may be enabled or disabled in software.

If Brownout detection is enabled, the operating voltage range for  $V_{DD}$  is 2.7 V to 3.6 V, and the brownout condition occurs when  $V_{DD}$  falls below the brownout trip voltage,  $V_{BO}$  (see Table 13 "DC electrical characteristics"), and is negated when  $V_{DD}$  rises above  $V_{BO}$ . If brownout detection is disabled, the operating voltage range for  $V_{DD}$  is 2.4 V to 3.6 V. If the P89LPC901/902/903 device is to operate with a power supply that can be below 2.7 V, BOE should be left in the unprogrammed state so that the device can operate at 2.4 V, otherwise continuous brownout reset may prevent the device from operating.

For correct activation of Brownout detect, the  $V_{DD}$  rise and fall times must be observed. Please see Table 13 "DC electrical characteristics" for specifications.

#### 8.13.2 Power-on detection

The Power-on Detect has a function similar to the Brownout detect, but is designed to work as power comes up initially, before the power supply voltage reaches a level where Brownout detect can work. The POF flag in the RSTSRC register is set to indicate an initial power-up condition. The POF flag will remain set until cleared by software.

#### 8.14 Power reduction modes

The P89LPC901/902/903 supports three different power reduction modes. These modes are Idle mode, Power-down mode, and total Power-down mode.

#### 8.14.1 Idle mode

Idle mode leaves peripherals running in order to allow them to activate the processor when an interrupt is generated. Any enabled interrupt source or reset may terminate Idle mode.

#### 8.14.2 Power-down mode

The Power-down mode stops the oscillator in order to minimize power consumption. The P89LPC901/902/903 exits Power-down mode via any reset, or certain interrupts. In Power-down mode, the power supply voltage may be reduced to the RAM keep-alive voltage V<sub>RAM</sub>. This retains the RAM contents at the point where Power-down mode was entered. SFR contents are not guaranteed after V<sub>DD</sub> has been lowered to V<sub>RAM</sub>, therefore it is highly recommended to wake up the processor via reset in this case. V<sub>DD</sub> must be raised to within the operating range before the Power-down mode is exited.

Some chip functions continue to operate and draw power during Power-down mode, increasing the total power used during Power-down. These include: Brownout detect, Watchdog Timer, Comparators (note that Comparators can be powered-down separately), and Real-Time Clock (RTC)/System Timer. The internal RC oscillator is disabled unless both the RC oscillator has been selected as the system clock **and** the RTC is enabled.

#### 8.14.3 Total Power-down mode

This is the same as Power-down mode except that the brownout detection circuitry and the voltage comparators are also disabled to conserve additional power. The internal RC oscillator is disabled unless both the RC oscillator has been selected as the system clock **and** the RTC is enabled. If the internal RC oscillator is used to clock the RTC during Power-down, there will be high power consumption. Please use an external low frequency clock to achieve low power with the Real-Time Clock running during Power-down.

#### 8.15 Reset

The P1.5/RST pin can function as either an active-LOW reset input or as a digital input, P1.5. The RPE (Reset Pin Enable) bit in UCFG1, when set to '1', enables the external reset input function on P1.5. When cleared, P1.5 may be used as an input pin.

**Remark:** During a power-up sequence, the RPE selection is overridden and this pin will always function as a reset input. **An external circuit connected to this pin should not hold this pin LOW during a power-on sequence as this will keep the device in reset.** After power-up this input will function either as an external reset input or as a digital input as defined by the RPE bit. Only a power-up reset will temporarily override the selection defined by RPE bit. Other sources of reset will not override the RPE bit.

**Remark:** During a power cycle, V<sub>DD</sub> must fall below V<sub>POR</sub> (see Table 13 "DC electrical characteristics") before power is reapplied, in order to ensure a power-on reset.

Reset can be triggered from the following sources:

- External reset pin (during power-up or if user configured via UCFG1. This option must be used for an oscillator frequency above 12 MHz.)

- Power-on detect

- Brownout detect

- Watchdog Timer

- Software reset

- UART break character detect reset (P80LPC903).

For every reset source, there is a flag in the Reset Register, RSTSRC. The user can read this register to determine the most recent reset source. These flag bits can be cleared in software by writing a '0' to the corresponding bit. More than one flag bit may be set:

- During a power-on reset, both POF and BOF are set but the other flag bits are cleared.

- For any other reset, previously set flag bits that have not been cleared will remain set.

#### 8.16 Timers/counters 0 and 1

The P89LPC901/902/903 has two general purpose timers which are similar to the standard 80C51 Timer 0 and Timer 1. These timers have four operating modes (modes 0, 1, 2, and 3). Modes 0, 1, and 2 are the same for both Timers. Mode 3 is different.

#### 8.16.1 Mode 0

Putting either Timer into Mode 0 makes it look like an 8048 Timer, which is an 8-bit Counter with a divide-by-32 prescaler. In this mode, the Timer register is configured as a 13-bit register. Mode 0 operation is the same for Timer 0 and Timer 1.

#### 8.16.2 Mode 1

Mode 1 is the same as Mode 0, except that all 16 bits of the timer register are used.

#### 8.16.3 Mode 2

Mode 2 configures the Timer register as an 8-bit Counter with automatic reload. Mode 2 operation is the same for Timer 0 and Timer 1.

#### 8.16.4 Mode 3

When Timer 1 is in Mode 3 it is stopped. Timer 0 in Mode 3 forms two separate 8-bit counters and is provided for applications that require an extra 8-bit timer. When Timer 1 is in Mode 3 it can still be used by the serial port as a baud rate generator.

#### 8.16.5 Mode 6 (P89LPC901)

In this mode, the corresponding timer can be changed to a PWM with a full period of 256 timer clocks.

#### 8-bit microcontrollers with two-clock 80C51 core

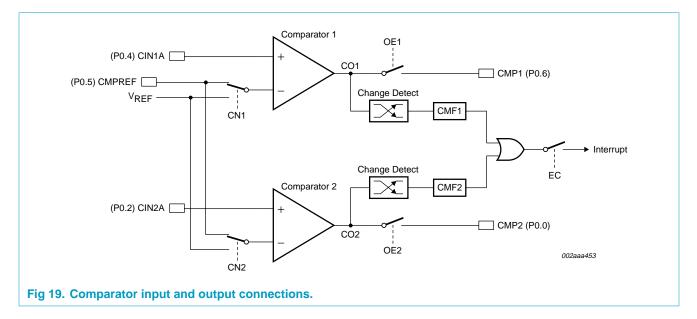

#### 8.20 Internal reference voltage

An internal reference voltage generator may supply a default reference when a single comparator input pin is used. The value of the internal reference voltage, referred to as  $V_{REF}$ , is 1.23 V ±10%.

#### 8.21 Comparator interrupt

Each comparator has an interrupt flag contained in its configuration register. This flag is set whenever the comparator output changes state. The flag may be polled by software or may be used to generate an interrupt.

#### 8.22 Comparator and power reduction modes

The comparators may remain enabled when Power-down or Idle mode is activated, but the comparators are disabled automatically in Total Power-down mode.

If the comparator interrupt is enabled (except in Total Power-down mode), a change of the comparator output state will generate an interrupt and wake up the processor. If the comparator output to a pin is enabled, the pin should be configured in the push-pull mode in order to obtain fast switching times while in Power-down mode. The reason is that with the oscillator stopped, the temporary strong pull-up that normally occurs during switching on a quasi-bidirectional port pin does not take place.

The comparator consumes power in Power-down and Idle modes, as well as in the normal operating mode. This fact should be taken into account when system power consumption is an issue. To minimize power consumption, the user can disable the comparator via PCONA.5 or put the device in Total Power-down mode.

#### 8.26.6 In-application programming

In-Application Programming is performed in the application under the control of the microcontroller's firmware. The IAP facility consists of internal hardware resources to facilitate programming and erasing. The Philips In-Application Programming has made in-application programming in an embedded application possible without additional components. This is accomplished through the use of four SFRs consisting of a control/status register, a data register, and two address registers. Additional details may be found in the *P89LPC901/902/903 User's Manual*.

#### 8.26.7 Using flash as data storage

The Flash code memory array of this device supports individual byte erasing and programming. Any byte in the code memory array may be read using the MOVC instruction, provided that the sector containing the byte has not been secured (a MOVC instruction is not allowed to read code memory contents of a secured sector). Thus any byte in a non-secured sector may be used for non-volatile data storage.

#### 8.26.8 User configuration bytes

Some user-configurable features of the P89LPC901/902/903 must be defined at power-up and therefore cannot be set by the program after start of execution. These features are configured through the use of the Flash byte UCFG1. Please see the *P89LPC901/902/903 User's Manual* for additional details.

#### 8.26.9 User sector security bytes

There are four User Sector Security Bytes, each corresponding to one sector. Please see the *P89LPC901/902/903 User's Manual* for additional details.

### 9. Limiting values

#### Table 12: Limiting values

In accordance with the Absolute Maximum Rating System (IEC 60134).<sup>[1]</sup>

|                                                         | · · ·                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                           |

|---------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Parameter                                               | Conditions                                                                                                                                                                                                                                                                                        | Min                                                                                                                                                                                                                                                                                                                                                              | Max                                                                                                                                                                                                                                                                                                                                                                            | Unit                                                                                                                                                                                                                                                                                                                                                                                                                      |

| operating bias ambient temperature                      |                                                                                                                                                                                                                                                                                                   | -55                                                                                                                                                                                                                                                                                                                                                              | +125                                                                                                                                                                                                                                                                                                                                                                           | °C                                                                                                                                                                                                                                                                                                                                                                                                                        |

| storage temperature range                               |                                                                                                                                                                                                                                                                                                   | -65                                                                                                                                                                                                                                                                                                                                                              | +150                                                                                                                                                                                                                                                                                                                                                                           | °C                                                                                                                                                                                                                                                                                                                                                                                                                        |

| voltage on XTAL1, XTAL2 pin to $V_{SS}$ , as applicable |                                                                                                                                                                                                                                                                                                   | -                                                                                                                                                                                                                                                                                                                                                                | V <sub>DD</sub> + 0.5                                                                                                                                                                                                                                                                                                                                                          | V                                                                                                                                                                                                                                                                                                                                                                                                                         |

| voltage on any other pin to $V_{SS}$                    |                                                                                                                                                                                                                                                                                                   | -0.5                                                                                                                                                                                                                                                                                                                                                             | +5.5                                                                                                                                                                                                                                                                                                                                                                           | V                                                                                                                                                                                                                                                                                                                                                                                                                         |

| HIGH-level output current per I/O pin                   |                                                                                                                                                                                                                                                                                                   | -                                                                                                                                                                                                                                                                                                                                                                | 8                                                                                                                                                                                                                                                                                                                                                                              | mA                                                                                                                                                                                                                                                                                                                                                                                                                        |

| LOW-level output current per I/O pin                    |                                                                                                                                                                                                                                                                                                   | -                                                                                                                                                                                                                                                                                                                                                                | 20                                                                                                                                                                                                                                                                                                                                                                             | mA                                                                                                                                                                                                                                                                                                                                                                                                                        |

| maximum total I/O current                               |                                                                                                                                                                                                                                                                                                   | -                                                                                                                                                                                                                                                                                                                                                                | 120                                                                                                                                                                                                                                                                                                                                                                            | mA                                                                                                                                                                                                                                                                                                                                                                                                                        |