Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                                              |

|--------------------------------|------------------------------------------------------------------------------|

| Product Status                 | Obsolete                                                                     |

| Number of LABs/CLBs            | 8375                                                                         |

| Number of Logic Elements/Cells | 67000                                                                        |

| Total RAM Bits                 | 4526080                                                                      |

| Number of I/O                  | 490                                                                          |

| Number of Gates                | -                                                                            |

| Voltage - Supply               | 1.14V ~ 1.26V                                                                |

| Mounting Type                  | Surface Mount                                                                |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                                              |

| Package / Case                 | 1156-BBGA                                                                    |

| Supplier Device Package        | 1156-FPBGA (35x35)                                                           |

| Purchase URL                   | https://www.e-xfl.com/product-detail/lattice-semiconductor/lfe3-70e-7fn1156c |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

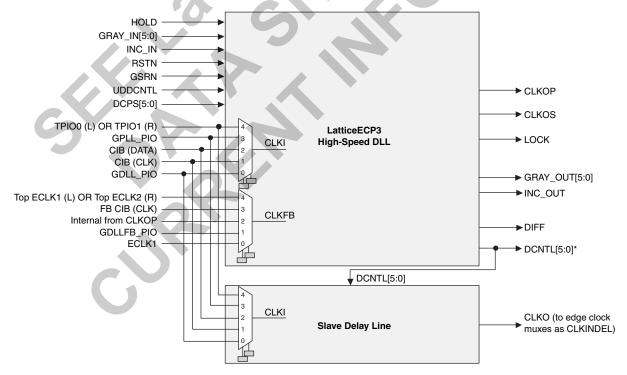

chain in order to better match the reference and feedback signals. This digital code from the ALU is also transmitted via the Digital Control bus (DCNTL) bus to its associated Slave Delay lines (two per DLL). The ALUHOLD input allows the user to suspend the ALU output at its current value. The UDDCNTL signal allows the user to latch the current value on the DCNTL bus.

The DLL has two clock outputs, CLKOP and CLKOS. These outputs can individually select one of the outputs from the tapped delay line. The CLKOS has optional fine delay shift and divider blocks to allow this output to be further modified, if required. The fine delay shift block allows the CLKOS output to phase shifted a further 45, 22.5 or 11.25 degrees relative to its normal position. Both the CLKOS and CLKOP outputs are available with optional duty cycle correction. Divide by two and divide by four frequencies are available at CLKOS. The LOCK output signal is asserted when the DLL is locked. Figure 2-5 shows the DLL block diagram and Table 2-5 provides a description of the DLL inputs and outputs.

The user can configure the DLL for many common functions such as time reference delay mode and clock injection removal mode. Lattice provides primitives in its design tools for these functions.

**Delay Chain** ALUHOLD □ Delav0 CLKOP Cycle Delay1 Output ÷4 Muxes Delay2 ÷2 Duty Cycle 50% (from routing Reference **CLKOS** Delay3 <u>÷4</u> Phase ÷2 Arithmetic Logic Unit Detector from CLKOP (DLL internal), from clock net (CLKOP) or from a use clock (pin or logic) LOCK CLKFB [ Lock Detect DCNTL[5:0]\* Digital DIFF UDDCNTL \_\_\_ Control Output RSTN === INCO INCI = GRAYO[5:0] GRAYI[5:0]

Figure 2-5. Delay Locked Loop Diagram (DLL)

Table 2-5. DLL Signals

| Signal     | I/O | Description                                                                                   |

|------------|-----|-----------------------------------------------------------------------------------------------|

| CLKI       | I   | Clock input from external pin or routing                                                      |

| CLKFB      | I   | DLL feed input from DLL output, clock net, routing or external pin                            |

| RSTN       | I   | Active low synchronous reset                                                                  |

| ALUHOLD    | I   | Active high freezes the ALU                                                                   |

| UDDCNTL    | I   | Synchronous enable signal (hold high for two cycles) from routing                             |

| CLKOP      | 0   | The primary clock output                                                                      |

| CLKOS      | 0   | The secondary clock output with fine delay shift and/or division by 2 or by 4                 |

| LOCK       | 0   | Active high phase lock indicator                                                              |

| INCI       | I   | Incremental indicator from another DLL via CIB.                                               |

| GRAYI[5:0] | I   | Gray-coded digital control bus from another DLL in time reference mode.                       |

| DIFF       | 0   | Difference indicator when DCNTL is difference than the internal setting and update is needed. |

| INCO       | 0   | Incremental indicator to other DLLs via CIB.                                                  |

| GRAYO[5:0] | 0   | Gray-coded digital control bus to other DLLs via CIB                                          |

LatticeECP3 devices have two general DLLs and four Slave Delay lines, two per DLL. The DLLs are in the lowest EBR row and located adjacent to the EBR. Each DLL replaces one EBR block. One Slave Delay line is placed adjacent to the DLL and the duplicate Slave Delay line (in Figure 2-6) for the DLL is placed in the I/O ring between Banks 6 and 7 and Banks 2 and 3.

The outputs from the DLL and Slave Delay lines are fed to the clock distribution network.

For more information, please see TN1178, LatticeECP3 sysCLOCK PLL/DLL Design and Usage Guide.

Figure 2-6. Top-Level Block Diagram, High-Speed DLL and Slave Delay Line

<sup>\*</sup> This signal is not user accessible. It can only be used to feed the slave delay line.

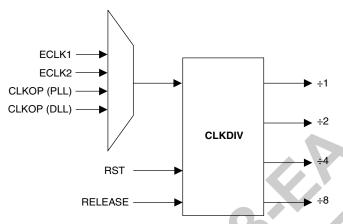

Figure 2-8. Clock Divider Connections

#### **Clock Distribution Network**

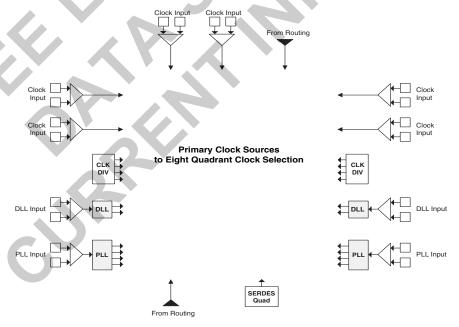

LatticeECP3 devices have eight quadrant-based primary clocks and eight secondary clock/control sources. Two high performance edge clocks are available on the top, left, and right edges of the device to support high speed interfaces. These clock sources are selected from external I/Os, the sysCLOCK PLLs, DLLs or routing. These clock sources are fed throughout the chip via a clock distribution system.

### **Primary Clock Sources**

LatticeECP3 devices derive clocks from six primary source types: PLL outputs, DLL outputs, CLKDIV outputs, dedicated clock inputs, routing and SERDES Quads. LatticeECP3 devices have two to ten sysCLOCK PLLs and two DLLs, located on the left and right sides of the device. There are six dedicated clock inputs: two on the top side, two on the left side and two on the right side of the device. Figures 2-9, 2-10 and 2-11 show the primary clock sources for LatticeECP3 devices.

Figure 2-9. Primary Clock Sources for LatticeECP3-17

Note: Clock inputs can be configured in differential or single-ended mode.

#### Single, Dual and Pseudo-Dual Port Modes

In all the sysMEM RAM modes the input data and address for the ports are registered at the input of the memory array. The output data of the memory is optionally registered at the output.

EBR memory supports the following forms of write behavior for single port or dual port operation:

- 1. **Normal** Data on the output appears only during a read cycle. During a write cycle, the data (at the current address) does not appear on the output. This mode is supported for all data widths.

- 2. **Write Through** A copy of the input data appears at the output of the same port during a write cycle. This mode is supported for all data widths.

- 3. **Read-Before-Write (EA devices only)** When new data is written, the old content of the address appears at the output. This mode is supported for x9, x18, and x36 data widths.

#### **Memory Core Reset**

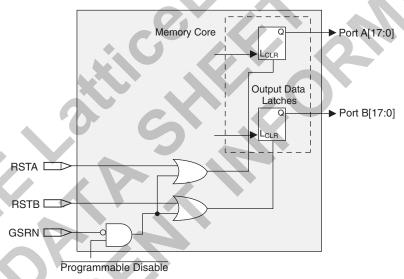

The memory array in the EBR utilizes latches at the A and B output ports. These latches can be reset asynchronously or synchronously. RSTA and RSTB are local signals, which reset the output latches associated with Port A and Port B, respectively. The Global Reset (GSRN) signal can reset both ports. The output data latches and associated resets for both ports are as shown in Figure 2-22.

Figure 2-22. Memory Core Reset

For further information on the sysMEM EBR block, please see the list of technical documentation at the end of this data sheet.

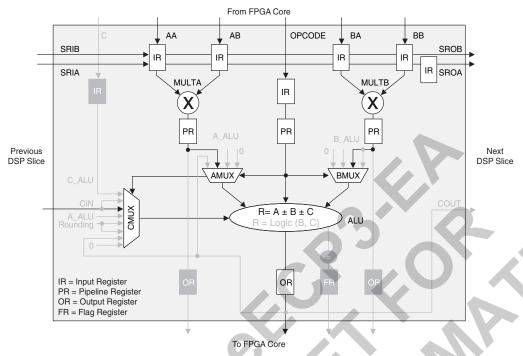

## sysDSP™ Slice

The LatticeECP3 family provides an enhanced sysDSP architecture, making it ideally suited for low-cost, high-performance Digital Signal Processing (DSP) applications. Typical functions used in these applications are Finite Impulse Response (FIR) filters, Fast Fourier Transforms (FFT) functions, Correlators, Reed-Solomon/Turbo/Convolution encoders and decoders. These complex signal processing functions use similar building blocks such as multiply-adders and multiply-accumulators.

#### sysDSP Slice Approach Compared to General DSP

Conventional general-purpose DSP chips typically contain one to four (Multiply and Accumulate) MAC units with fixed data-width multipliers; this leads to limited parallelism and limited throughput. Their throughput is increased by higher clock speeds. The LatticeECP3, on the other hand, has many DSP slices that support different data widths.

Figure 2-31. MULTADDSUBSUM Slice 1

# **Advanced sysDSP Slice Features**

## Cascading

The LatticeECP3 sysDSP slice has been enhanced to allow cascading. Adder trees are implemented fully in sys-DSP slices, improving the performance. Cascading of slices uses the signals CIN, COUT and C Mux of the slice.

#### **Addition**

The LatticeECP3 sysDSP slice allows for the bypassing of multipliers and cascading of adder logic. High performance adder functions are implemented without the use of LUTs. The maximum width adders that can be implemented are 54-bit.

#### Rounding

The rounding operation is implemented in the ALU and is done by adding a constant followed by a truncation operation. The rounding methods supported are:

- Rounding to zero (RTZ)

- · Rounding to infinity (RTI)

- · Dynamic rounding

- Random rounding

- Convergent rounding

Two adjacent PIOs can be joined to provide a differential I/O pair (labeled as "T" and "C") as shown in Figure 2-32. The PAD Labels "T" and "C" distinguish the two PIOs. Approximately 50% of the PIO pairs on the left and right edges of the device can be configured as true LVDS outputs. All I/O pairs can operate as LVDS inputs.

Table 2-11. PIO Signal List

| Туре                          | Description                                                                                                                                                                                                                                                                         |

|-------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Input Data                    | Register bypassed input. This is not the same port as INCK.                                                                                                                                                                                                                         |

| Input Data                    | Ports to core for input data                                                                                                                                                                                                                                                        |

| Output Data                   | Output signals from core. An exception is the ONEGB port, used for tristate logic at the DQS pad.                                                                                                                                                                                   |

| PIO Control                   | Clock enables for input and output block flip-flops.                                                                                                                                                                                                                                |

| PIO Control                   | System Clock (PCLK) for input and output/TS blocks. Connected from clock ISB.                                                                                                                                                                                                       |

| PIO Control                   | Local Set/Reset                                                                                                                                                                                                                                                                     |

| PIO Control                   | Edge clock sources. Entire PIO selects one of two sources using mux.                                                                                                                                                                                                                |

| Read Control                  | From DQS_STROBE, shifted strobe for memory interfaces only.                                                                                                                                                                                                                         |

| Read Control                  | Ensures transfer from DQS domain to SCLK domain.                                                                                                                                                                                                                                    |

| Read Control                  | Used to guarantee INDDRX2 gearing by selectively enabling a D-Flip-Flop in datapath.                                                                                                                                                                                                |

| Read Control                  | Dynamic input delay control bits.                                                                                                                                                                                                                                                   |

| To Clock Distribution and PLL | PIO treated as clock PIO, path to distribute to primary clocks and PLL.                                                                                                                                                                                                             |

| Tristate Data                 | Tristate signal from core (SDR)                                                                                                                                                                                                                                                     |

| Write Control                 | Two clocks edges, 90 degrees out of phase, used in output gearing.                                                                                                                                                                                                                  |

| Write Control                 | Used for output and tristate logic at DQS only.                                                                                                                                                                                                                                     |

| Write Control                 | Shifting of write clocks for specific DQS group, using 6:0 each step is approximately 25ps, 128 steps. Bit 7 is an invert (timing depends on input frequency). There is also a static control for this 8-bit setting, enabled with a memory cell.                                   |

| PIO Control                   | Original delay code from DDR DLL                                                                                                                                                                                                                                                    |

| Output Data                   | Status flag from DATAVALID logic, used to indicate when input data is captured in IOLOGIC and valid to core.                                                                                                                                                                        |

| For DQS_Strobe                | Read signal for DDR memory interface                                                                                                                                                                                                                                                |

| For DQS_Strobe                | Unshifted DQS strobe from input pad                                                                                                                                                                                                                                                 |

| For DQS_Strobe                | DQSI biased to go high when DQSI is tristate, goes to input logic block as well as core logic.                                                                                                                                                                                      |

| Control from routing          | Global Set/Reset                                                                                                                                                                                                                                                                    |

|                               | Input Data Input Data Output Data Output Data PIO Control PIO Control PIO Control PIO Control Read Control Read Control Read Control To Clock Distribution and PLL Tristate Data Write Control Write Control Write Control Output Data For DQS_Strobe For DQS_Strobe For DQS_Strobe |

<sup>1.</sup> Signals available on left/right/top edges only.

#### PIO

The PIO contains four blocks: an input register block, output register block, tristate register block and a control logic block. These blocks contain registers for operating in a variety of modes along with the necessary clock and selection logic.

#### Input Register Block

The input register blocks for the PIOs, in the left, right and top edges, contain delay elements and registers that can be used to condition high-speed interface signals, such as DDR memory interfaces and source synchronous interfaces, before they are passed to the device core. Figure 2-33 shows the input register block for the left, right and top edges. The input register block for the bottom edge contains one element to register the input signal and no DDR registers. The following description applies to the input register block for PIOs in the left, right and top edges only.

<sup>2.</sup> Selected PIO.

#### **Lattice Semiconductor**

To accomplish write leveling in DDR3, each DQS group has a slightly different delay that is set by DYN DELAY[7:0] in the DQS Write Control logic block. The DYN DELAY can set 128 possible delay step settings. In addition, the most significant bit will invert the clock for a 180-degree shift of the incoming clock.

LatticeECP3 input and output registers can also support DDR gearing that is used to receive and transmit the high speed DDR data from and to the DDR3 Memory.

LatticeECP3 supports the 1.5V SSTL I/O standard required for the DDR3 memory interface. In addition, it supports on-chip termination to VTT on the DDR3 memory input pins. For more information, refer to the sysIO section of this data sheet.

Please see TN1180, <u>LatticeECP3 High-Speed I/O Interface</u> for more information on DDR Memory interface implementation in LatticeECP3.

## sysI/O Buffer

Each I/O is associated with a flexible buffer referred to as a sysI/O buffer. These buffers are arranged around the periphery of the device in groups referred to as banks. The sysI/O buffers allow users to implement the wide variety of standards that are found in today's systems including LVDS, BLVDS, HSTL, SSTL Class I & II, LVCMOS, LVTTL, LVPECL, PCI.

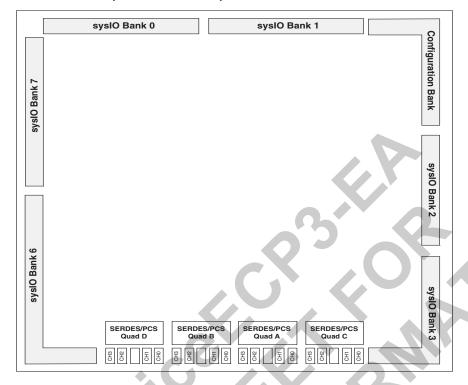

#### sysI/O Buffer Banks

LatticeECP3 devices have six sysl/O buffer banks: six banks for user I/Os arranged two per side. The banks on the bottom side are wraparounds of the banks on the lower right and left sides. The seventh sysl/O buffer bank (Configuration Bank) is located adjacent to Bank 2 and has dedicated/shared I/Os for configuration. When a shared pin is not used for configuration it is available as a user I/O. Each bank is capable of supporting multiple I/O standards. Each sysl/O bank has its own I/O supply voltage ( $V_{\rm CCIO}$ ). In addition, each bank, except the Configuration Bank, has voltage references,  $V_{\rm REF1}$  and  $V_{\rm REF2}$ , which allow it to be completely independent from the others. The Configuration Bank top side shares  $V_{\rm REF1}$  and  $V_{\rm REF2}$  from sysl/O bank 1 and right side shares  $V_{\rm REF1}$  and  $V_{\rm REF2}$  from sysl/O bank 2. Figure 2-38 shows the seven banks and their associated supplies.

In LatticeECP3 devices, single-ended output buffers and ratioed input buffers (LVTTL, LVCMOS and PCI) are powered using  $V_{CCIO}$ . LVTTL, LVCMOS33, LVCMOS25 and LVCMOS12 can also be set as fixed threshold inputs independent of  $V_{CCIO}$ .

Each bank can support up to two separate  $V_{REF}$  voltages,  $V_{REF1}$  and  $V_{REF2}$ , that set the threshold for the referenced input buffers. Some dedicated I/O pins in a bank can be configured to be a reference voltage supply pin. Each I/O is individually configurable based on the bank's supply and reference voltages.

Figure 2-40. SERDES/PCS Quads (LatticeECP3-150)

Table 2-13. LatticeECP3 SERDES Standard Support

| Standard                                                                     | Data Rate<br>(Mbps)                                             | Number of<br>General/Link Width | Encoding Style |

|------------------------------------------------------------------------------|-----------------------------------------------------------------|---------------------------------|----------------|

| PCI Express 1.1                                                              | 2500                                                            | x1, x2, x4                      | 8b10b          |

| Gigabit Ethernet                                                             | 1250, 2500                                                      | x1                              | 8b10b          |

| SGMII                                                                        | 1250                                                            | x1                              | 8b10b          |

| XAUI                                                                         | 3125                                                            | x4                              | 8b10b          |

| Serial RapidIO Type I,<br>Serial RapidIO Type II,<br>Serial RapidIO Type III | 1250,<br>2500,<br>3125                                          | x1, x4                          | 8b10b          |

| CPRI-1,<br>CPRI-2,<br>CPRI-3,<br>CPRI-4                                      | 614.4,<br>1228.8,<br>2457.6,<br>3072.0                          | x1                              | 8b10b          |

| SD-SDI<br>(259M, 344M)                                                       | 143 <sup>1</sup> ,<br>177 <sup>1</sup> ,<br>270,<br>360,<br>540 | x1                              | NRZI/Scrambled |

| HD-SDI<br>(292M)                                                             | 1483.5,<br>1485                                                 | x1                              | NRZI/Scrambled |

| 3G-SDI<br>(424M)                                                             | 2967,<br>2970                                                   | x1                              | NRZI/Scrambled |

| SONET-STS-3 <sup>2</sup>                                                     | 155.52                                                          | x1                              | N/A            |

| SONET-STS-12 <sup>2</sup>                                                    | 622.08                                                          | x1                              | N/A            |

| SONET-STS-48 <sup>2</sup>                                                    | 2488                                                            | x1                              | N/A            |

<sup>1.</sup> For slower rates, the SERDES are bypassed and CML signals are directly connected to the FPGA routing.

<sup>2.</sup> The SONET protocol is supported in 8-bit SERDES mode. See TN1176 Lattice ECP3 SERDES/PCS Usage Guide for more information.

Table 2-14. Available SERDES Quads per LatticeECP3 Devices

| Package    | ECP3-17 | ECP3-35 | ECP3-70 | ECP3-95 | ECP3-150 |

|------------|---------|---------|---------|---------|----------|

| 256 ftBGA  | 1       | 1       | _       | _       | _        |

| 484 ftBGA  | 1       | 1       | 1       | 1       |          |

| 672 ftBGA  | _       | 1       | 2       | 2       | 2        |

| 1156 ftBGA | _       | _       | 3       | 3       | 4        |

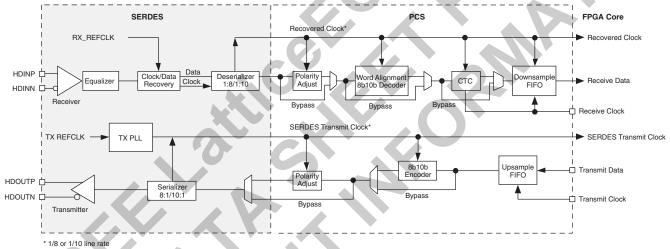

#### **SERDES Block**

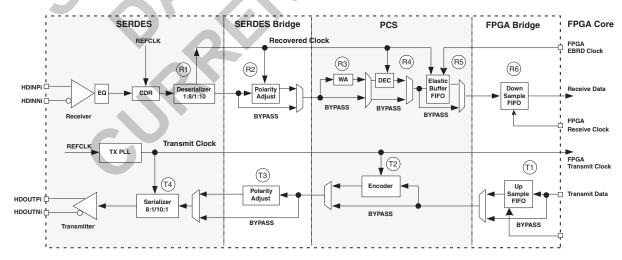

A SERDES receiver channel may receive the serial differential data stream, equalize the signal, perform Clock and Data Recovery (CDR) and de-serialize the data stream before passing the 8- or 10-bit data to the PCS logic. The SERDES transmitter channel may receive the parallel 8- or 10-bit data, serialize the data and transmit the serial bit stream through the differential drivers. Figure 2-41 shows a single-channel SERDES/PCS block. Each SERDES channel provides a recovered clock and a SERDES transmit clock to the PCS block and to the FPGA core logic.

Each transmit channel, receiver channel, and SERDES PLL shares the same power supply (VCCA). The output and input buffers of each channel have their own independent power supplies (VCCOB and VCCIB).

Figure 2-41. Simplified Channel Block Diagram for SERDES/PCS Block

#### **PCS**

As shown in Figure 2-41, the PCS receives the parallel digital data from the deserializer and selects the polarity, performs word alignment, decodes (8b/10b), provides Clock Tolerance Compensation and transfers the clock domain from the recovered clock to the FPGA clock via the Down Sample FIFO.

For the transmit channel, the PCS block receives the parallel data from the FPGA core, encodes it with 8b/10b, selects the polarity and passes the 8/10 bit data to the transmit SERDES channel.

The PCS also provides bypass modes that allow a direct 8-bit or 10-bit interface from the SERDES to the FPGA logic. The PCS interface to the FPGA can also be programmed to run at 1/2 speed for a 16-bit or 20-bit interface to the FPGA logic.

### SCI (SERDES Client Interface) Bus

The SERDES Client Interface (SCI) is an IP interface that allows the SERDES/PCS Quad block to be controlled by registers rather than the configuration memory cells. It is a simple register configuration interface that allows SERDES/PCS configuration without power cycling the device.

#### **BLVDS25**

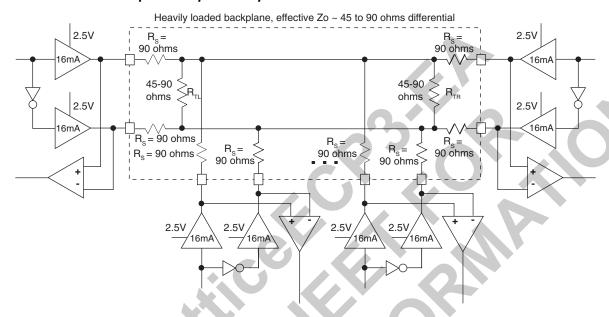

The LatticeECP3 devices support the BLVDS standard. This standard is emulated using complementary LVCMOS outputs in conjunction with a parallel external resistor across the driver outputs. BLVDS is intended for use when multi-drop and bi-directional multi-point differential signaling is required. The scheme shown in Figure 3-2 is one possible solution for bi-directional multi-point differential signals.

Figure 3-2. BLVDS25 Multi-point Output Example

Table 3-2. BLVDS25 DC Conditions<sup>1</sup>

|                   | V 2 6                             | Typical          |                  |       |

|-------------------|-----------------------------------|------------------|------------------|-------|

| Parameter         | Description                       | <b>Zo = 45</b> Ω | <b>Zo = 90</b> Ω | Units |

| V <sub>CCIO</sub> | Output Driver Supply (+/- 5%)     | 2.50             | 2.50             | V     |

| Z <sub>OUT</sub>  | Driver Impedance                  | 10.00            | 10.00            | Ω     |

| R <sub>S</sub>    | Driver Series Resistor (+/- 1%)   | 90.00            | 90.00            | Ω     |

| R <sub>TL</sub>   | Driver Parallel Resistor (+/- 1%) | 45.00            | 90.00            | Ω     |

| R <sub>TR</sub>   | Receiver Termination (+/- 1%)     | 45.00            | 90.00            | Ω     |

| V <sub>OH</sub>   | Output High Voltage               | 1.38             | 1.48             | V     |

| $V_{OL}$          | Output Low Voltage                | 1.12             | 1.02             | V     |

| $V_{OD}$          | Output Differential Voltage       | 0.25             | 0.46             | V     |

| V <sub>CM</sub>   | Output Common Mode Voltage        | 1.25             | 1.25             | V     |

| I <sub>DC</sub>   | DC Output Current                 | 11.24            | 10.20            | mA    |

<sup>1.</sup> For input buffer, see LVDS table.

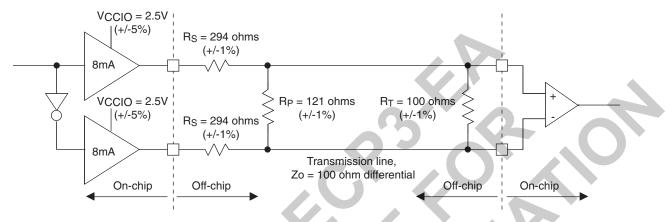

#### RSDS25E

The LatticeECP3 devices support differential RSDS and RSDSE standards. This standard is emulated using complementary LVCMOS outputs in conjunction with a parallel resistor across the driver outputs. The RSDS input standard is supported by the LVDS differential input buffer. The scheme shown in Figure 3-4 is one possible solution for RSDS standard implementation. Resistor values in Figure 3-4 are industry standard values for 1% resistors.

Figure 3-4. RSDS25E (Reduced Swing Differential Signaling)

Table 3-4. RSDS25E DC Conditions1

| Parameter         | Description                      | Typical | Units |

|-------------------|----------------------------------|---------|-------|

| V <sub>CCIO</sub> | Output Driver Supply (+/-5%)     | 2.50    | V     |

| Z <sub>OUT</sub>  | Driver Impedance                 | 20      | Ω     |

| $R_S$             | Driver Series Resistor (+/-1%)   | 294     | Ω     |

| R <sub>P</sub>    | Driver Parallel Resistor (+/-1%) | 121     | Ω     |

| R <sub>T</sub>    | Receiver Termination (+/-1%)     | 100     | Ω     |

| V <sub>OH</sub>   | Output High Voltage              | 1.35    | V     |

| V <sub>OL</sub>   | Output Low Voltage               | 1.15    | V     |

| V <sub>OD</sub>   | Output Differential Voltage      | 0.20    | V     |

| $V_{CM}$          | Output Common Mode Voltage       | 1.25    | V     |

| Z <sub>BACK</sub> | Back Impedance                   | 101.5   | Ω     |

| I <sub>DC</sub>   | DC Output Current                | 3.66    | mA    |

<sup>1.</sup> For input buffer, see LVDS table.

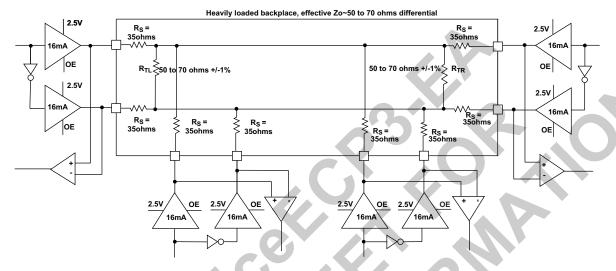

#### MLVDS25

The LatticeECP3 devices support the differential MLVDS standard. This standard is emulated using complementary LVCMOS outputs in conjunction with a parallel resistor across the driver outputs. The MLVDS input standard is supported by the LVDS differential input buffer. The scheme shown in Figure 3-5 is one possible solution for MLVDS standard implementation. Resistor values in Figure 3-5 are industry standard values for 1% resistors.

Figure 3-5. MLVDS25 (Multipoint Low Voltage Differential Signaling)

Table 3-5. MLVDS25 DC Conditions<sup>1</sup>

|                   | X V                              | Тур            |                |       |

|-------------------|----------------------------------|----------------|----------------|-------|

| Parameter         | Description                      | <b>Zo=50</b> Ω | <b>Z</b> o=70Ω | Units |

| V <sub>CCIO</sub> | Output Driver Supply (+/-5%)     | 2.50           | 2.50           | V     |

| Z <sub>OUT</sub>  | Driver Impedance                 | 10.00          | 10.00          | Ω     |

| R <sub>S</sub>    | Driver Series Resistor (+/-1%)   | 35.00          | 35.00          | Ω     |

| R <sub>TL</sub>   | Driver Parallel Resistor (+/-1%) | 50.00          | 70.00          | Ω     |

| R <sub>TR</sub>   | Receiver Termination (+/-1%)     | 50.00          | 70.00          | Ω     |

| V <sub>OH</sub>   | Output High Voltage              | 1.52           | 1.60           | V     |

| V <sub>OL</sub>   | Output Low Voltage               | 0.98           | 0.90           | V     |

| $V_{OD}$          | Output Differential Voltage      | 0.54           | 0.70           | V     |

| V <sub>CM</sub>   | Output Common Mode Voltage       | 1.25           | 1.25           | V     |

| I <sub>DC</sub>   | DC Output Current                | 21.74          | 20.00          | mA    |

<sup>1.</sup> For input buffer, see LVDS table.

# LatticeECP3 External Switching Characteristics (Continued)<sup>1, 2</sup>

**Over Recommended Commercial Operating Conditions**

|                                   |                                                          |                   | -8        |               | -7       |             | -6      |        |       |

|-----------------------------------|----------------------------------------------------------|-------------------|-----------|---------------|----------|-------------|---------|--------|-------|

| Parameter                         | Description                                              | Device            | Min.      | Max.          | Min.     | Max.        | Min.    | Max.   | Units |

| t <sub>DVECLKGDDR</sub>           | Data Hold After CLK                                      | ECP3-70E/95E      | 0.765     | _             | 0.765    | _           | 0.765   | _      | UI    |

| f <sub>MAX_GDDR</sub>             | DDR/DDRX2 Clock Frequency <sup>8</sup>                   | ECP3-70E/95E      | _         | 500           | _        | 420         | _       | 375    | MHz   |

| Generic DDRX2<br>Pin for Clock In | 2 Inputs with Clock and Data (<10 Bits                   | Wide) Centered    | at Pin (  | GDDRX         | 2_RX.[   | OQS.Ce      | ntered) | using  | DQS   |

| Left and Right                    | Sides                                                    |                   |           | -             |          | <b>&gt;</b> |         |        |       |

| t <sub>SUGDDR</sub>               | Data Setup Before CLK                                    | ECP3-150EA        |           | 7             |          | _           |         | _      | ns    |

| t <sub>HGDDR</sub>                | Data Hold After CLK                                      | ECP3-150EA        |           | Y             |          | _           |         | _      | ns    |

| f <sub>MAX_GDDR</sub>             | DDRX2 Clock Frequency                                    | ECP3-150EA        |           |               | _        |             | _       |        | ns    |

| Generic DDRX2 for Clock Input     | 2 Inputs with Clock and Data (<10 Bits                   | Side) Aligned at  | Pin (GI   | DRX2          | RX.DC    | S.Alig      | ned) Us | ing DC | S Pin |

| Left and Right                    | Sides                                                    |                   |           |               |          |             |         |        |       |

| t <sub>DVACLKGDDR</sub>           | Data Setup Before CLK (Left and Right Side)              | ECP3-150EA        | - (       |               |          |             |         |        |       |

| † <sub>DVECLKGDDR</sub>           | Data Hold After CLK (Left and Right Side)                | ECP3-150EA        | 2         | 7             |          | A           |         | _      |       |

| f <sub>MAX_GDDR</sub>             | DDRX2 Clock Frequency (Left and Right Side)              | ECP3-150EA        |           |               | ~        |             | _       |        |       |

| Generic DDRX1                     | 1 Output with Clock and Data (>10 Bits                   | Wide) Centered    | at Pin (  | (GDDR         | X1_TX.   | SCLK.C      | Centere | d)     |       |

| Left, Right and                   | Top Sides                                                |                   |           |               |          |             |         |        |       |

| t <sub>DVBGDDR</sub>              | Data Valid Before CLK                                    | ECP3-150EA        |           |               |          | _           |         | _      |       |

| t <sub>DVAGDDR</sub>              | Data Valid After CLK                                     | ECP3-150EA        |           | $\mathcal{F}$ |          | _           |         | _      |       |

| f <sub>MAX_GDDR</sub>             | DDRX1 Clock Frequency                                    | ECP3-150EA        | ( )       |               | _        |             | _       |        |       |

|                                   | I Outputs with clock in the center of d<br>CLK.Centered) | ata window, with  | PLL 90    | -degre        | e shifte | d clock     | ouput   |        |       |

| t <sub>DIBGDDR</sub>              | Data Invalid Before CLK                                  | ECP3-70E/95E      | 670       | _             | 670      | _           | 670     | _      | ps    |

| t <sub>DIAGDDR</sub>              | Data Invalid After CLK                                   | ECP3-70E/95E      | 670       | _             | 670      | _           | 670     | _      | ps    |

| fMAX_GDDR                         | DDRX1 Clock Frequency                                    | ECP3-70E/95E      | _         | 250           | _        | 250         | _       | 250    | MHz   |

| Generic DDRX1                     | Output with Clock and Data (> 10 Bit                     | s Wide) Aligned a | at Pin (0 | GDDRX         | 1_TX.S   | CLK.A       | ligned) |        |       |

| Left, Right and                   | Top Sides                                                |                   |           |               |          |             |         |        |       |

| t <sub>DIBGDDR</sub>              | Data Hold After CLK                                      | ECP3-150EA        | _         |               | _        |             | _       |        |       |

| t <sub>DIAGDDR</sub>              | Data Setup Before CLK                                    | ECP3-150EA        | _         |               | _        |             | _       |        |       |

| f <sub>MAX_GDDR</sub>             | DDRX1 Clock Frequency                                    | ECP3-150EA        | _         |               | _        |             | _       |        |       |

| Generic DDRX1                     | Outputs with clock and data edge ali                     | gned, without PL  | L         |               |          |             |         |        |       |

| t <sub>DIBGDDR</sub>              | Data Invalid Before CLK                                  | ECP3-70E/95E      | _         | 330           | _        | 330         | _       | 330    | ps    |

| t <sub>DIAGDDR</sub>              | Data Invalid After CLK                                   | ECP3-70E/95E      | _         | 330           | _        | 330         | _       | 330    | ps    |

| f <sub>MAX_GDDR</sub>             | DDRX1 Clock Frequency                                    | ECP3-70E/95E      | _         | 250           | _        | 250         | _       | 250    | MHz   |

|                                   | Output with Clock and Data (<10 Bits                     | Wide) Centered    | at Pin (  | (GDDR         | X1_TX.   | DQS.C       | entered | )      | 1     |

| Left, Right and                   | Top Sides                                                |                   |           |               |          |             |         |        |       |

| t <sub>DVBGDDR</sub>              | Data Valid Before CLK                                    | ECP3-150EA        | _         |               | _        |             | _       |        |       |

| t <sub>DVAGDDR</sub>              | Data Valid After CLK                                     | ECP3-150EA        | _         |               | _        |             | _       |        |       |

| f <sub>MAX_GDDR</sub>             | DDRX1 Clock Frequency                                    | ECP3-150EA        |           |               |          |             |         |        |       |

CLKA CSA WEA Three consecultive writes to A0 ADA Á0 A0 t<sub>SU</sub> t<sub>H</sub> Dο DΪ DIA tACCESS tACCESS TACCESS tACCESS Data from Prev Read Þο DOA D2 D4 or Write

Figure 3-11. Write Through (SP Read/Write on Port A, Input Registers Only)

Note: Input data and address are registered at the positive edge of the clock and output data appears after the positive edge of the clock.

## **SERDES/PCS Block Latency**

Table 3-8 describes the latency of each functional block in the transmitter and receiver. Latency is given in parallel clock cycles. Figure 3-12 shows the location of each block.

Table 3-8. SERDES/PCS Latency Breakdown

| Item    | Description                                          | Min.     | Avg.          | Max.          | Fixed   | Bypass        | Units    |

|---------|------------------------------------------------------|----------|---------------|---------------|---------|---------------|----------|

| Transmi | t Data Latency¹                                      |          |               |               | •       | •             |          |

|         | FPGA Bridge - Gearing disabled with different clocks | 1        | 3             | 5             | _       | 1             | word clk |

| T1      | FPGA Bridge - Gearing disabled with same clocks      | _        | _             | -             | 3       | 1             | word clk |

|         | FPGA Bridge - Gearing enabled                        | 1        | 3             | 5             | _       | _             | word clk |

| T2      | 8b10b Encoder                                        | _        | -             |               | 2       | 1             | word clk |

| T3      | SERDES Bridge transmit                               | _        |               | 7             | 2       | 1             | word clk |

| T4      | Serializer: 8-bit mode                               | _        | 7-            | - 4           | 15 + ∆1 | _             | UI + ps  |

| 14      | Serializer: 10-bit mode                              | 70       |               |               | 18 + ∆1 | - C           | UI + ps  |

| T5      | Pre-emphasis ON                                      |          | _             | -             | 1 + Δ2  | 7-            | UI + ps  |

| 15      | Pre-emphasis OFF                                     |          | · — /         |               | 0 + Δ3  | 7-7           | UI + ps  |

| Receive | Data Latency <sup>2</sup>                            |          |               |               |         |               |          |

| R1      | Equalization ON                                      |          | _             | <b>&gt;</b> - | Δ1      | <b>&gt;</b> - | UI + ps  |

| n i     | Equalization OFF                                     |          | 7             |               | Δ2      | _             | UI + ps  |

| R2      | Deserializer: 8-bit mode                             |          |               | -             | 10 + ∆3 | _             | UI + ps  |

| ΠZ      | Deserializer: 10-bit mode                            |          |               |               | 12 + ∆3 | _             | UI + ps  |

| R3      | SERDES Bridge receive                                | <b>/</b> | _             | 1             | 2       | _             | word clk |

| R4      | Word alignment                                       | 3.1      | -             | 4             | —       | _             | word clk |

| R5      | 8b10b decoder                                        | \ -      | <i>&gt;</i> + | 7-            | 1       | _             | word clk |

| R6      | Clock Tolerance Compensation                         | 7        | 15            | 23            | 1       | 1             | word clk |

|         | FPGA Bridge - Gearing disabled with different clocks | 1        | 3             | 5             | _       | 1             | word clk |

| R7      | FPGA Bridge - Gearing disabled with same clocks      |          | <u> </u>      | _             | 3       | 1             | word clk |

|         | FPGA Bridge - Gearing enabled                        | 1        | 3             | 5             | _       | _             | word clk |

<sup>1.</sup>  $\Delta 1 = -245$ ps,  $\Delta 2 = +88$ ps,  $\Delta 3 = +112$ ps.

Figure 3-12. Transmitter and Receiver Latency Block Diagram

<sup>2.</sup>  $\Delta 1 = +118$ ps,  $\Delta 2 = +132$ ps,  $\Delta 3 = +700$ ps.

# **XAUI/Serial Rapid I/O Type 3 Electrical and Timing Characteristics AC and DC Characteristics**

Table 3-13. Transmit

#### **Over Recommended Operating Conditions**

| Symbol                                   | Description                      | Test Conditions | Min. | Тур. | Max. | Units |

|------------------------------------------|----------------------------------|-----------------|------|------|------|-------|

| T <sub>RF</sub>                          | Differential rise/fall time      | 20%-80%         | _    | 80   | _    | ps    |

| Z <sub>TX_DIFF_DC</sub>                  | Differential impedance           |                 | 80   | 100  | 120  | Ohms  |

| J <sub>TX_DDJ</sub> <sup>2, 3, 4</sup>   | Output data deterministic jitter |                 |      |      | 0.17 | UI    |

| J <sub>TX_TJ</sub> <sup>1, 2, 3, 4</sup> | Total output data jitter         |                 |      | _    | 0.35 | UI    |

- 1. Total jitter includes both deterministic jitter and random jitter.

- 2. Jitter values are measured with each CML output AC coupled into a 50-ohm impedance (100-ohm differential impedance).

- 3. Jitter and skew are specified between differential crossings of the 50% threshold of the reference signal.

- 4. Values are measured at 2.5 Gbps.

Table 3-14. Receive and Jitter Tolerance

| Symbol                                | Description                                   | Test Conditions              | Min. | Тур. | Max. | Units |

|---------------------------------------|-----------------------------------------------|------------------------------|------|------|------|-------|

| RL <sub>RX_DIFF</sub>                 | Differential return loss                      | From 100 MHz<br>to 3.125 GHz | 10   | V-L  | _    | dB    |

| RL <sub>RX_CM</sub>                   | Common mode return loss                       | From 100 MHz<br>to 3.125 GHz | 6    |      | _    | dB    |

| Z <sub>RX_DIFF</sub>                  | Differential termination resistance           |                              | 80   | 100  | 120  | Ohms  |

| J <sub>RX_DJ</sub> <sup>1, 2, 3</sup> | Deterministic jitter tolerance (peak-to-peak) |                              | 1    | _    | 0.37 | UI    |

| J <sub>RX_RJ</sub> <sup>1, 2, 3</sup> | Random jitter tolerance (peak-to-peak)        |                              | )-   | _    | 0.18 | UI    |

| J <sub>RX_SJ</sub> <sup>1, 2, 3</sup> | Sinusoidal jitter tolerance (peak-to-peak)    |                              |      | _    | 0.10 | UI    |

| J <sub>RX_TJ</sub> <sup>1, 2, 3</sup> | Total jitter tolerance (peak-to-peak)         |                              |      | _    | 0.65 | UI    |

| T <sub>RX_EYE</sub>                   | Receiver eye opening                          |                              | 0.35 | _    | _    | UI    |

- 1. Total jitter includes deterministic jitter, random jitter and sinusoidal jitter. The sinusoidal jitter tolerance mask is shown in Figure 3-14.

- 2. Jitter values are measured with each high-speed input AC coupled into a 50-ohm impedance.

- 3. Jitter and skew are specified between differential crossings of the 50% threshold of the reference signal.

- 4. Jitter tolerance parameters are characterized when Full Rx Equalization is enabled.

- 5. Values are measured at 2.5 Gbps.

# Gigabit Ethernet/Serial Rapid I/O Type 1/SGMII Electrical and Timing Characteristics

#### **AC and DC Characteristics**

#### Table 3-17. Transmit

| Symbol                                   | Description                      | Test Conditions | Min. | Тур. | Max. | Units |

|------------------------------------------|----------------------------------|-----------------|------|------|------|-------|

| T <sub>RF</sub>                          | Differential rise/fall time      | 20%-80%         | _    | 80   | _    | ps    |

| Z <sub>TX_DIFF_DC</sub>                  | Differential impedance           |                 | 80   | 100  | 120  | Ohms  |

| J <sub>TX_DDJ</sub> <sup>3, 4, 5</sup>   | Output data deterministic jitter |                 |      | _    | 0.10 | UI    |

| J <sub>TX_TJ</sub> <sup>2, 3, 4, 5</sup> | Total output data jitter         |                 | /- V | _    | 0.24 | UI    |

- 1. Rise and fall times measured with board trace, connector and approximately 2.5pf load.

- 2. Total jitter includes both deterministic jitter and random jitter. The random jitter is the total jitter minus the actual deterministic jitter.

- 3. Jitter values are measured with each CML output AC coupled into a 50-ohm impedance (100-ohm differential impedance).

- 4. Jitter and skew are specified between differential crossings of the 50% threshold of the reference signal.

- 5. Values are measured at 1.25 Gbps.

#### Table 3-18. Receive and Jitter Tolerance

| Symbol                                      | Description                                   | Test Conditions          | Min. | Тур.       | Max. | Units |

|---------------------------------------------|-----------------------------------------------|--------------------------|------|------------|------|-------|

| RL <sub>RX_DIFF</sub>                       | Differential return loss                      | From 100 MHz to 1.25 GHz | 10   |            | _    | dB    |

| RL <sub>RX_CM</sub>                         | Common mode return loss                       | From 100 MHz to 1.25 GHz | 6    | \ <u> </u> | _    | dB    |

| Z <sub>RX_DIFF</sub>                        | Differential termination resistance           |                          | 80   | 100        | 120  | Ohms  |

|                                             | Deterministic jitter tolerance (peak-to-peak) |                          | 7    | _          | 0.34 | UI    |

|                                             | Random jitter tolerance (peak-to-peak)        |                          |      | _          | 0.26 | UI    |

|                                             | Sinusoidal jitter tolerance (peak-to-peak)    |                          | _    | _          | 0.11 | UI    |

| J <sub>RX_TJ</sub> <sup>1, 2, 3, 4, 5</sup> | Total jitter tolerance (peak-to-peak)         |                          | _    | —          | 0.71 | UI    |

| T <sub>RX EYE</sub>                         | Receiver eye opening                          |                          | 0.29 | _          | _    | UI    |

- 1. Total jitter includes deterministic jitter, random jitter and sinusoidal jitter. The sinusoidal jitter tolerance mask is shown in Figure 3-14.

- 2. Jitter values are measured with each high-speed input AC coupled into a 50-ohm impedance.

- 3. Jitter and skew are specified between differential crossings of the 50% threshold of the reference signal.

- 4. Jitter tolerance, Differential Input Sensitivity and Receiver Eye Opening parameters are characterized when Full Rx Equalization is enabled.

- 5. Values are measured at 1.25 Gbps.

# **LatticeECP3 sysCONFIG Port Timing Specifications**

| Parameter            | Description                                                                                                                                    |                    |     | Max.     | Units  |

|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-----|----------|--------|

| POR, Confi           | guration Initialization, and Wakeup                                                                                                            |                    |     |          |        |

|                      | Time from the Application of $V_{CC}$ , $V_{CCAUX}$ or $V_{CCIO8}^*$ (Whichever is the Last to Cross the POR Trip Point) to the Rising Edge of | Master mode        | _   | 23       | ms     |

| t <sub>ICFG</sub>    | is the Last to Cross the POR Trip Point) to the Rising Edge of INITN                                                                           | Slave mode         |     | 6        | ms     |

| t <sub>VMC</sub>     | Time from t <sub>ICFG</sub> to the Valid Master MCLK                                                                                           |                    | _   | 5        | μs     |

| t <sub>PRGM</sub>    | PROGRAMN Low Time to Start Configuration                                                                                                       |                    | 25  | _        | ns     |

| t <sub>PRGMRJ</sub>  | PROGRAMN Pin Pulse Rejection                                                                                                                   |                    | _   | 10       | ns     |

| t <sub>DPPINIT</sub> | Delay Time from PROGRAMN Low to INITN Low                                                                                                      |                    | _   | 37       | ns     |

| t <sub>DPPDONE</sub> | Delay Time from PROGRAMN Low to DONE Low                                                                                                       |                    | _   | 37       | ns     |

| t <sub>DINIT</sub>   | PROGRAMN High to INITN High Delay                                                                                                              | 5                  |     | 1        | ms     |

| t <sub>MWC</sub>     | Additional Wake Master Clock Signals After DONE Pin is High                                                                                    |                    | 100 | 500      | cycles |

| t <sub>CZ</sub>      | MCLK From Active To Low To High-Z                                                                                                              |                    |     | 300      | ns     |

| All Configu          | ration Modes                                                                                                                                   |                    |     |          |        |

| t <sub>SUCDI</sub>   | Data Setup Time to CCLK/MCLK                                                                                                                   |                    | 5   | <u> </u> | ns     |

| t <sub>HCDI</sub>    | Data Hold Time to CCLK/MCLK                                                                                                                    |                    | 1   | -        | ns     |

| t <sub>CODO</sub>    | CCLK/MCLK to DOUT in Flowthrough Mode                                                                                                          |                    | -   | 12       | ns     |

| Slave Seria          |                                                                                                                                                |                    |     |          | ı      |

| t <sub>SSCH</sub>    | CCLK Minimum High Pulse                                                                                                                        |                    |     | _        | ns     |

| t <sub>SSCL</sub>    | CCLK Minimum Low Pulse                                                                                                                         |                    | 5   | _        | ns     |

| JOOL                 |                                                                                                                                                | Without encryption |     | 33       | MHz    |

| f <sub>CCLK</sub>    | CCLK Frequency                                                                                                                                 | With encryption    | _   | 20       | MHz    |

| Master and           | Slave Parallel                                                                                                                                 | 71                 |     | <u> </u> |        |

| t <sub>SUCS</sub>    | CSN[1:0] Setup Time to CCLK/MCLK                                                                                                               |                    | 7   | _        | ns     |

| t <sub>HCS</sub>     | CSN[1:0] Hold Time to CCLK/MCLK                                                                                                                |                    | 1   | _        | ns     |

| t <sub>SUWD</sub>    | WRITEN Setup Time to CCLK/MCLK                                                                                                                 |                    | 7   | _        | ns     |

| t <sub>HWD</sub>     | WRITEN Hold Time to CCLK/MCLK                                                                                                                  |                    |     | _        | ns     |

| t <sub>DCB</sub>     | CCLK/MCLK to BUSY Delay Time                                                                                                                   |                    |     | 12       | ns     |

| t <sub>CORD</sub>    | CCLK to Out for Read Data                                                                                                                      |                    | _   | 12       | ns     |

| t <sub>BSCH</sub>    | CCLK Minimum High Pulse                                                                                                                        |                    | 6   | <u> </u> | ns     |

| t <sub>BSCL</sub>    | CCLK Minimum Low Pulse                                                                                                                         |                    | 6   | _        | ns     |

| t <sub>BSCYC</sub>   | Byte Slave Cycle Time                                                                                                                          |                    | 30  | <u> </u> | ns     |

|                      |                                                                                                                                                | Without encryption | _   | 33       | MHz    |

| f <sub>CCLK</sub>    | CCLK/MCLK Frequency                                                                                                                            | With encryption    | _   | 20       | MHz    |

| Master and           | Slave SPI                                                                                                                                      |                    |     | 1        | ı      |

| t <sub>CFGX</sub>    | INITN High to MCLK Low                                                                                                                         |                    | _   | 80       | ns     |

| t <sub>CSSPI</sub>   | INITN High to CSSPIN Low                                                                                                                       |                    |     | 2        | μs     |

| t <sub>SOCDO</sub>   | MCLK Low to Output Valid                                                                                                                       |                    |     | 15       | ns     |

| t <sub>CSPID</sub>   | CSSPIN[0:1] Low to First MCLK Edge Setup Time                                                                                                  |                    |     |          | μs     |

|                      | 20145                                                                                                                                          | Without encryption | _   | 33       | MHz    |

| f <sub>CCLK</sub>    | CCLK Frequency                                                                                                                                 | With encryption    |     | 20       | MHz    |

| t <sub>SSCH</sub>    | CCLK Minimum High Pulse                                                                                                                        |                    |     | <u> </u> | ns     |

| t <sub>SSCL</sub>    | CCLK Minimum Low Pulse                                                                                                                         |                    |     | <u> </u> | ns     |

| t <sub>HLCH</sub>    | HOLDN Low Setup Time (Relative to CCLK)                                                                                                        |                    |     | _        | ns     |

# **Signal Descriptions (Cont.)**

| I/O                                                                                                       | Description                                                                                                                                                                                                                                                                                                                                                  |

|-----------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| I/O                                                                                                       | DQ input/output pads: T (top), R (right), B (bottom), L (left), DQS, num = ball function number.                                                                                                                                                                                                                                                             |

| I/O                                                                                                       | DQ input/output pads: T (top), R (right), B (bottom), L (left), DQ, associated DQS number.                                                                                                                                                                                                                                                                   |

| ns)                                                                                                       |                                                                                                                                                                                                                                                                                                                                                              |

| I                                                                                                         | Test Mode Select input, used to control the 1149.1 state machine. Pull-up is enabled during configuration.                                                                                                                                                                                                                                                   |

| I                                                                                                         | Test Clock input pin, used to clock the 1149.1 state machine. No pull-up enabled.                                                                                                                                                                                                                                                                            |

| I                                                                                                         | Test Data in pin. Used to load data into device using 1149.1 state machine. After power-up, this TAP port can be activated for configuration by sending appropriate command. (Note: once a configuration port is selected it is locked. Another configuration port cannot be selected until the power-up sequence). Pull-up is enabled during configuration. |

| 0                                                                                                         | Output pin. Test Data Out pin used to shift data out of a device using 1149.1.                                                                                                                                                                                                                                                                               |

| _                                                                                                         | Power supply pin for JTAG Test Access Port.                                                                                                                                                                                                                                                                                                                  |

| CONFIG                                                                                                    |                                                                                                                                                                                                                                                                                                                                                              |

| CFG[2:0] Mode pins used to specify configuration mod of INITN. During configuration, a pull-up is expins. |                                                                                                                                                                                                                                                                                                                                                              |

| I/O                                                                                                       | Open Drain pin. Indicates the FPGA is ready to be configured. During configuration, a pull-up is enabled. It is a dedicated pin.                                                                                                                                                                                                                             |

| _                                                                                                         | Initiates configuration sequence when asserted low. This pin always has an active pull-up. It is a dedicated pin.                                                                                                                                                                                                                                            |

| 1/0                                                                                                       | Open Drain pin. Indicates that the configuration sequence is complete, and the startup sequence is in progress. It is a dedicated pin.                                                                                                                                                                                                                       |

| _                                                                                                         | Input Configuration Clock for configuring an FPGA in Slave SPI, Serial, and CPU modes. It is a dedicated pin.                                                                                                                                                                                                                                                |

| 1/0                                                                                                       | Output Configuration Clock for configuring an FPGA in SPI, SPIm, and Master configuration modes.                                                                                                                                                                                                                                                             |

| 0                                                                                                         | Parallel configuration mode busy indicator. SPI/SPIm mode data output.                                                                                                                                                                                                                                                                                       |

| 1/0                                                                                                       | Parallel configuration mode active-low chip select. Slave SPI chip select. Parallel burst Flash output enable.                                                                                                                                                                                                                                               |

| _                                                                                                         | Parallel configuration mode active-low chip select. Slave SPI hold input.                                                                                                                                                                                                                                                                                    |

| I                                                                                                         | Write enable for parallel configuration modes.                                                                                                                                                                                                                                                                                                               |

| 0                                                                                                         | Serial data output. Chip select output. SPI/SPIm mode chip select.                                                                                                                                                                                                                                                                                           |

| 1                                                                                                         | sysCONFIG Port Data I/O for Parallel mode. Open drain during configuration.                                                                                                                                                                                                                                                                                  |

| 1/0                                                                                                       | sysCONFIG Port Data I/O for SPI or SPIm. When using the SPI or SPIm mode, this pin should either be tied high or low, must not be left floating. Open drain during configuration.                                                                                                                                                                            |

| I/O                                                                                                       | Parallel configuration I/O. Open drain during configuration.                                                                                                                                                                                                                                                                                                 |

| I/O                                                                                                       | Parallel configuration I/O. Open drain during configuration.                                                                                                                                                                                                                                                                                                 |

| I/O                                                                                                       | Parallel configuration I/O. Slave SPI data input. Open drain during configuration.                                                                                                                                                                                                                                                                           |

| I/O                                                                                                       | Parallel configuration I/O. Slave SPI data output. Open drain during configuration.                                                                                                                                                                                                                                                                          |

| I/O                                                                                                       | Parallel configuration I/O. Open drain during configuration.                                                                                                                                                                                                                                                                                                 |

| I/O                                                                                                       | Parallel configuration I/O. SPI/SPIm data input. Open drain during configuration.                                                                                                                                                                                                                                                                            |

|                                                                                                           | I/O                                                                                                                                                                                                                                                                                                                                                          |

# **Signal Descriptions (Cont.)**

| Signal Name                           | I/O                                   | Description                                                                       |  |  |  |  |

|---------------------------------------|---------------------------------------|-----------------------------------------------------------------------------------|--|--|--|--|

| D7/SPID0                              |                                       | Parallel configuration I/O. SPI/SPIm data input. Open drain during configuration. |  |  |  |  |

| DI/CSSPI0N/CEN                        | I/O                                   | Serial data input for slave serial mode. SPI/SPIm mode chip select.               |  |  |  |  |

| Dedicated SERDES Signals <sup>2</sup> | Dedicated SERDES Signals <sup>2</sup> |                                                                                   |  |  |  |  |