Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                                             |

|--------------------------------|-----------------------------------------------------------------------------|

| Product Status                 | Obsolete                                                                    |

| Number of LABs/CLBs            | 8375                                                                        |

| Number of Logic Elements/Cells | 67000                                                                       |

| Total RAM Bits                 | 4526080                                                                     |

| Number of I/O                  | 295                                                                         |

| Number of Gates                | -                                                                           |

| Voltage - Supply               | 1.14V ~ 1.26V                                                               |

| Mounting Type                  | Surface Mount                                                               |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                                             |

| Package / Case                 | 484-BBGA                                                                    |

| Supplier Device Package        | 484-FPBGA (23x23)                                                           |

| Purchase URL                   | https://www.e-xfl.com/product-detail/lattice-semiconductor/lfe3-70e-7fn484c |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

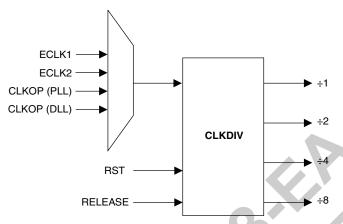

Figure 2-8. Clock Divider Connections

### **Clock Distribution Network**

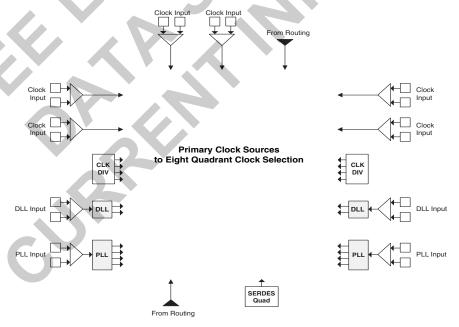

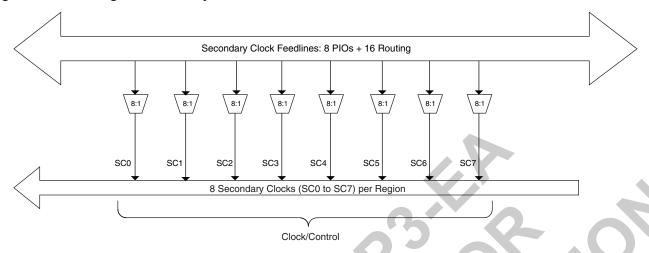

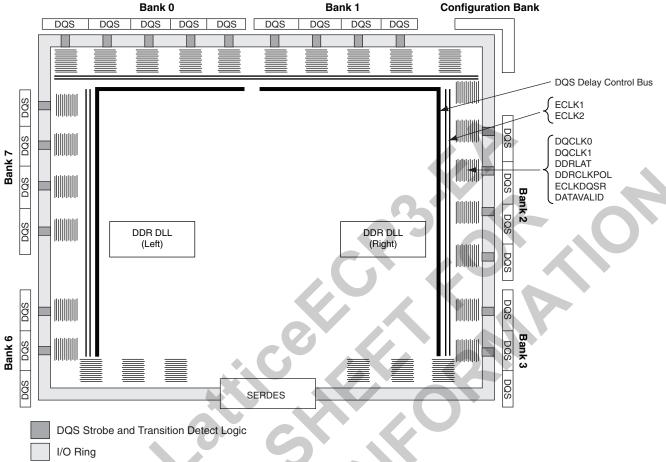

LatticeECP3 devices have eight quadrant-based primary clocks and eight secondary clock/control sources. Two high performance edge clocks are available on the top, left, and right edges of the device to support high speed interfaces. These clock sources are selected from external I/Os, the sysCLOCK PLLs, DLLs or routing. These clock sources are fed throughout the chip via a clock distribution system.

### **Primary Clock Sources**

LatticeECP3 devices derive clocks from six primary source types: PLL outputs, DLL outputs, CLKDIV outputs, dedicated clock inputs, routing and SERDES Quads. LatticeECP3 devices have two to ten sysCLOCK PLLs and two DLLs, located on the left and right sides of the device. There are six dedicated clock inputs: two on the top side, two on the left side and two on the right side of the device. Figures 2-9, 2-10 and 2-11 show the primary clock sources for LatticeECP3 devices.

Figure 2-9. Primary Clock Sources for LatticeECP3-17

Note: Clock inputs can be configured in differential or single-ended mode.

Figure 2-16. Per Region Secondary Clock Selection

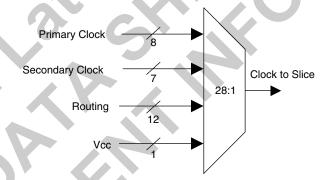

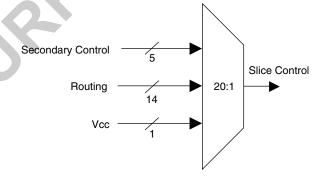

#### Slice Clock Selection

Figure 2-17 shows the clock selections and Figure 2-18 shows the control selections for Slice0 through Slice2. All the primary clocks and seven secondary clocks are routed to this clock selection mux. Other signals can be used as a clock input to the slices via routing. Slice controls are generated from the secondary clocks/controls or other signals connected via routing.

If none of the signals are selected for both clock and control then the default value of the mux output is 1. Slice 3 does not have any registers; therefore it does not have the clock or control muxes.

Figure 2-17. Slice0 through Slice2 Clock Selection

Figure 2-18. Slice0 through Slice2 Control Selection

The edge clocks on the top, left, and right sides of the device can drive the secondary clocks or general routing resources of the device. The left and right side edge clocks also can drive the primary clock network through the clock dividers (CLKDIV).

### sysMEM Memory

LatticeECP3 devices contain a number of sysMEM Embedded Block RAM (EBR). The EBR consists of an 18-Kbit RAM with memory core, dedicated input registers and output registers with separate clock and clock enable. Each EBR includes functionality to support true dual-port, pseudo dual-port, single-port RAM, ROM and FIFO buffers (via external PFUs).

### sysMEM Memory Block

The sysMEM block can implement single port, dual port or pseudo dual port memories. Each block can be used in a variety of depths and widths as shown in Table 2-7. FIFOs can be implemented in sysMEM EBR blocks by implementing support logic with PFUs. The EBR block facilitates parity checking by supporting an optional parity bit for each data byte. EBR blocks provide byte-enable support for configurations with 18-bit and 36-bit data widths. For more information, please see TN1179, <u>LatticeECP3 Memory Usage Guide</u>.

Table 2-7. sysMEM Block Configurations

| Memory Mode      | Configurations                                                              |

|------------------|-----------------------------------------------------------------------------|

| Single Port      | 16,384 x 1<br>8,192 x 2<br>4,096 x 4<br>2,048 x 9<br>1,024 x 18<br>512 x 36 |

| True Dual Port   | 16,384 x 1<br>8,192 x 2<br>4,096 x 4<br>2,048 x 9<br>1,024 x 18             |

| Pseudo Dual Port | 16,384 x 1<br>8,192 x 2<br>4,096 x 4<br>2,048 x 9<br>1,024 x 18<br>512 x 36 |

### **Bus Size Matching**

All of the multi-port memory modes support different widths on each of the ports. The RAM bits are mapped LSB word 0 to MSB word 0, LSB word 1 to MSB word 1, and so on. Although the word size and number of words for each port varies, this mapping scheme applies to each port.

### **RAM Initialization and ROM Operation**

If desired, the contents of the RAM can be pre-loaded during device configuration. By preloading the RAM block during the chip configuration cycle and disabling the write controls, the sysMEM block can also be utilized as a ROM

### **Memory Cascading**

Larger and deeper blocks of RAM can be created using EBR sysMEM Blocks. Typically, the Lattice design tools cascade memory transparently, based on specific design inputs.

#### Single, Dual and Pseudo-Dual Port Modes

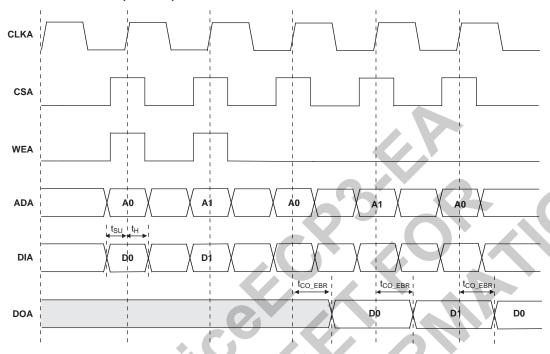

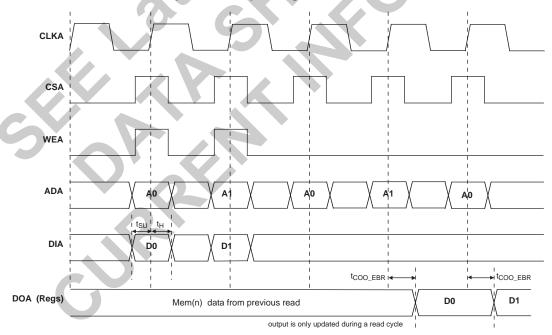

In all the sysMEM RAM modes the input data and address for the ports are registered at the input of the memory array. The output data of the memory is optionally registered at the output.

EBR memory supports the following forms of write behavior for single port or dual port operation:

- 1. **Normal** Data on the output appears only during a read cycle. During a write cycle, the data (at the current address) does not appear on the output. This mode is supported for all data widths.

- 2. **Write Through** A copy of the input data appears at the output of the same port during a write cycle. This mode is supported for all data widths.

- 3. **Read-Before-Write (EA devices only)** When new data is written, the old content of the address appears at the output. This mode is supported for x9, x18, and x36 data widths.

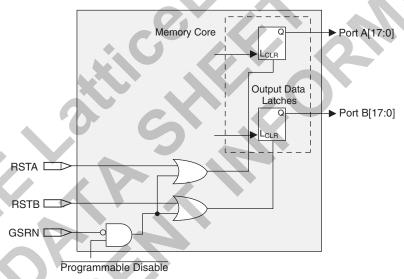

### **Memory Core Reset**

The memory array in the EBR utilizes latches at the A and B output ports. These latches can be reset asynchronously or synchronously. RSTA and RSTB are local signals, which reset the output latches associated with Port A and Port B, respectively. The Global Reset (GSRN) signal can reset both ports. The output data latches and associated resets for both ports are as shown in Figure 2-22.

Figure 2-22. Memory Core Reset

For further information on the sysMEM EBR block, please see the list of technical documentation at the end of this data sheet.

### sysDSP™ Slice

The LatticeECP3 family provides an enhanced sysDSP architecture, making it ideally suited for low-cost, high-performance Digital Signal Processing (DSP) applications. Typical functions used in these applications are Finite Impulse Response (FIR) filters, Fast Fourier Transforms (FFT) functions, Correlators, Reed-Solomon/Turbo/Convolution encoders and decoders. These complex signal processing functions use similar building blocks such as multiply-adders and multiply-accumulators.

### sysDSP Slice Approach Compared to General DSP

Conventional general-purpose DSP chips typically contain one to four (Multiply and Accumulate) MAC units with fixed data-width multipliers; this leads to limited parallelism and limited throughput. Their throughput is increased by higher clock speeds. The LatticeECP3, on the other hand, has many DSP slices that support different data widths.

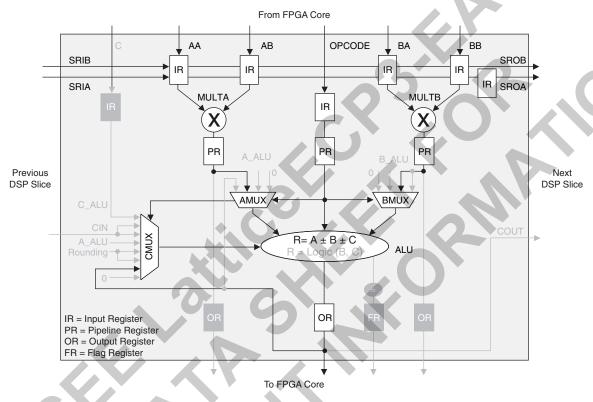

#### **MMAC DSP Element**

The LatticeECP3 supports a MAC with two multipliers. This is called Multiply Multiply Accumulate or MMAC. In this case, the two operands, AA and AB, are multiplied and the result is added with the previous accumulated value and with the result of the multiplier operation of operands BA and BB. This accumulated value is available at the output. The user can enable the input and pipeline registers, but the output register is always enabled. The output register is used to store the accumulated value. The ALU is configured as the accumulator in the sysDSP slice. A registered overflow signal is also available. The overflow conditions are provided later in this document. Figure 2-28 shows the MMAC sysDSP element.

Figure 2-28. MMAC sysDSP Element

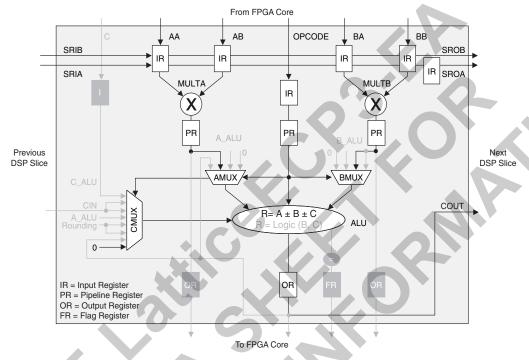

### **MULTADDSUBSUM DSP Element**

In this case, the operands AA and AB are multiplied and the result is added/subtracted with the result of the multiplier operation of operands BA and BB of Slice 0. Additionally, the operands AA and AB are multiplied and the result is added/subtracted with the result of the multiplier operation of operands BA and BB of Slice 1. The results of both addition/subtractions are added by the second ALU following the slice cascade path. The user can enable the input, output and pipeline registers. Figure 2-30 and Figure 2-31 show the MULTADDSUBSUM sysDSP element

Figure 2-30. MULTADDSUBSUM Slice 0

Figure 2-36. Edge Clock, DLL Calibration and DQS Local Bus Distribution

<sup>\*</sup>Includes shared configuration I/Os and dedicated configuration I/Os.

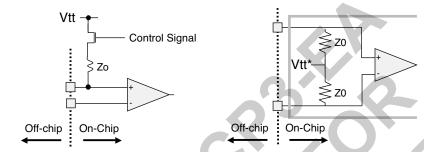

### **On-Chip Programmable Termination**

The LatticeECP3 supports a variety of programmable on-chip terminations options, including:

- Dynamically switchable Single Ended Termination for SSTL15 inputs with programmable resistor values of 40, 50, or 60 ohms. This is particularly useful for low power JEDEC compliant DDR3 memory controller implementations. External termination to Vtt should be used for DDR2 memory controller implementation.

- Common mode termination of 80, 100, 120 ohms for differential inputs

Figure 2-39. On-Chip Termination

Programmable resistance (40, 50 and 60 Ohms)

Parallel Single-Ended Input

Differential Input

\*Vtt must be left floating for this termination

See Table 2-12 for termination options for input modes.

Table 2-12. On-Chip Termination Options for Input Modes

| IO_TYPE    | TERMINATE to VTT <sup>1, 2</sup> | DIFFRENTIAL TERMINATION RESISTOR <sup>1</sup> |

|------------|----------------------------------|-----------------------------------------------|

| LVDS25     | þ                                | 80, 100, 120                                  |

| BLVDS25    | þ                                | 80, 100, 120                                  |

| MLVDS      | þ                                | 80, 100, 120                                  |

| HSTL18_I   | 40, 50, 60                       | þ                                             |

| HSTL18_II  | 40, 50, 60                       | þ                                             |

| HSTL18D_I  | 40, 50, 60                       | þ                                             |

| HSTL18D_II | 40, 50, 60                       | þ                                             |

| HSTL15_I   | 40, 50, 60                       | þ                                             |

| HSTL15D_I  | 40, 50, 60                       | þ                                             |

| SSTL25_I   | 40, 50, 60                       | þ                                             |

| SSTL25_II  | 40, 50, 60                       | þ                                             |

| SSTL25D_I  | 40, 50, 60                       | þ                                             |

| SSTL25D_II | 40, 50, 60                       | þ                                             |

| SSTL18_I   | 40, 50, 60                       | þ                                             |

| SSTL18_II  | 40, 50, 60                       | þ                                             |

| SSTL18D_I  | 40, 50, 60                       | þ                                             |

| SSTL18D_II | 40, 50, 60                       | þ                                             |

| SSTL15     | 40, 50, 60                       | þ                                             |

| SSTL15D    | 40, 50, 60                       | þ                                             |

TERMINATE to VTT and DIFFRENTIAL TERMINATION RESISTOR when turn on can only have one setting per bank. Only left and right banks have this feature.

Use of TERMINATE to VTT and DIFFRENTIAL TERMINATION RESISTOR are mutually exclusive in an I/O bank.

On-chip termination tolerance +/- 20%

<sup>2.</sup> External termination to VTT should be used when implementing DDR2 memory controller.

### sysl/O Single-Ended DC Electrical Characteristics

| Input/Output               | ,        | V <sub>IL</sub>          | V <sub>II</sub>          | 1        | V <sub>OL</sub>       | V <sub>OH</sub>          |                        |                                   |

|----------------------------|----------|--------------------------|--------------------------|----------|-----------------------|--------------------------|------------------------|-----------------------------------|

| Standard                   | Min. (V) | Max. (V)                 | Min. (V)                 | Max. (V) | Max. (V)              | Min. (V)                 | I <sub>OL</sub> 1 (mA) | I <sub>OH</sub> <sup>1</sup> (mA) |

| LVCMOS33                   | -0.3     | 0.8                      | 2.0                      | 3.6      | 0.4                   | V <sub>CCIO</sub> - 0.4  | 20, 16,<br>12, 8, 4    | -20, -16,<br>-12, -8, -4          |

|                            |          |                          |                          |          | 0.2                   | V <sub>CCIO</sub> - 0.2  | 0.1                    | -0.1                              |

| LVCMOS25                   | -0.3     | 0.7                      | 1.7                      | 3.6      | 0.4                   | V <sub>CCIO</sub> - 0.4  | 20, 16,<br>12, 8, 4    | -20, -16,<br>-12, -8, -4          |

|                            |          |                          |                          |          | 0.2                   | V <sub>CCIO</sub> - 0.2  | 0.1                    | -0.1                              |

| LVCMOS18                   | -0.3     | 0.35 V <sub>CCIO</sub>   | 0.65 V <sub>CCIO</sub>   | 3.6      | 0.4                   | V <sub>CCIO</sub> - 0.4  | 16, 12,<br>8, 4        | -16, -12,<br>-8, -4               |

|                            |          |                          |                          |          | 0.2                   | V <sub>CCIO</sub> - 0.2  | 0.1                    | -0.1                              |

| LVCMOS15                   | -0.3     | 0.35 V <sub>CCIO</sub>   | 0.65 V <sub>CCIO</sub>   | 3.6      | 0.4                   | V <sub>CCIO</sub> - 0.4  | 8, 4                   | -8, -4                            |

| 2701110010                 | 0.0      | 0.00 10010               | 0.00 10010               | 0.0      | 0.2                   | V <sub>CCIO</sub> - 0.2  | 0.1                    | -0.1                              |

| LVCMOS12                   | -0.3     | 0.35 V <sub>CC</sub>     | 0.65 V <sub>CC</sub>     | 3.6      | 0.4                   | V <sub>CCIO</sub> - 0.4  | 6, 2                   | -6, -2                            |

| 2701110012                 | 0.0      | 0.00 100                 | 0.00 100                 | 0.0      | 0.2                   | V <sub>CCIO</sub> - 0.2  | 0.1                    | -0.1                              |

| LVTTL33                    | -0.3     | 0.8                      | 2.0                      | 3.6      | 0.4                   | V <sub>CCIO</sub> - 0.4  | 20, 16,<br>12, 8, 4    | -20, -16,<br>-12, -8, -4          |

|                            |          |                          |                          |          | 0.2                   | V <sub>CCIO</sub> - 0.2  | 0.1                    | -0.1                              |

| PCI33                      | -0.3     | 0.3 V <sub>CCIO</sub>    | 0.5 V <sub>CCIO</sub>    | 3.6      | 0.1 V <sub>CCIO</sub> | 0.9 V <sub>CCIO</sub>    | 1.5                    | -0.5                              |

| SSTL18_I                   | -0.3     | V <sub>REF</sub> - 0.125 | V <sub>REF</sub> + 0.125 | 3.6      | 0.4                   | V <sub>CCIO</sub> - 0.4  | 6.7                    | -6.7                              |

| SSTL18_II<br>(DDR2 Memory) | -0.3     | V <sub>REF</sub> - 0.125 | V <sub>REF</sub> + 0.125 | 3.6      | 0.28                  | V <sub>CCIO</sub> - 0.28 | 8<br>11                | -8<br>-11                         |

|                            |          |                          |                          |          |                       |                          | 7.6                    | -7.6                              |

| SSTL2_I                    | -0.3     | V <sub>REF</sub> - 0.18  | V <sub>REF</sub> + 0.18  | 3.6      | 0.54                  | V <sub>CCIO</sub> - 0.62 | 12                     | -12                               |

| SSTL2_II                   |          | '07                      |                          |          |                       |                          | 15.2                   | -15.2                             |

| (DDR2 Memory)              | -0.3     | V <sub>REF</sub> - 0.18  | V <sub>REF</sub> + 0.18  | 3.6      | 0.35                  | V <sub>CCIO</sub> - 0.43 | 20                     | -20                               |

| SSTL3_I                    | -0.3     | V <sub>REF</sub> - 0.2   | V <sub>REF</sub> + 0.2   | 3.6      | 0.7                   | V <sub>CCIO</sub> - 1.1  | 8                      | -8                                |

| SSTL3_II                   | -0.3     | V <sub>REF</sub> - 0.2   | V <sub>REF</sub> + 0.2   | 3.6      | 0.5                   | V <sub>CCIO</sub> - 0.9  | 16                     | -16                               |

| SSTL15                     | -0.3     | V 0.1                    |                          | 3.6      | 0.3                   | V <sub>CCIO</sub> - 0.3  | 7.5                    | -7.5                              |

| (DDR3 Memory)              | -0.3     | V <sub>REF</sub> - 0.1   | V <sub>REF</sub> + 0.1   | 3.0      | 0.3                   | V <sub>CCIO</sub> * 0.8  | 9                      | -9                                |

| HSTL15_I                   | -0.3     | V <sub>REF</sub> - 0.1   | V <sub>REF</sub> + 0.1   | 3.6      | 0.4                   | V 0.4                    | 4                      | -4                                |

|                            | -0.3     | VREF - U. I              | VREF + 0.1               | 3.0      | 0.4                   | V <sub>CCIO</sub> - 0.4  | 8                      | -8                                |

| HSTL18_I                   | -0.3     | V <sub>REF</sub> - 0.1   | V <sub>REF</sub> + 0.1   | 3.6      | 0.4                   | V <sub>CCIO</sub> - 0.4  | 8                      | -8                                |

| 1101210_1                  | -0.0     | HEF - U.1                |                          | 0.0      | 0.4                   | CCIO - 0.4               | 12                     | -12                               |

| HSTL18_II                  | -0.3     | V <sub>REF</sub> - 0.1   | V <sub>REF</sub> + 0.1   | 3.6      | 0.4                   | V <sub>CCIO</sub> - 0.4  | 16                     | -16                               |

<sup>1.</sup> The average DC current drawn by I/Os between GND connections, or between the last GND in an I/O bank and the end of an I/O bank, as shown in the logic signal connections table shall not exceed n \* 8mA, where n is the number of I/Os between bank GND connections or between the last GND in a bank and the end of a bank.

### **Timing Diagrams**

Figure 3-9. Read/Write Mode (Normal)

Note: Input data and address are registered at the positive edge of the clock and output data appears after the positive edge of the clock.

Figure 3-10. Read/Write Mode with Input and Output Registers

# LatticeECP3 Family Timing Adders<sup>1, 2, 3, 4, 5</sup>

### **Over Recommended Commercial Operating Conditions**

| Buffer Type      | Description                    | -8    | -7    | -6     | Units |

|------------------|--------------------------------|-------|-------|--------|-------|

| Input Adjusters  |                                | ı     | I.    | ı      | ı     |

| LVDS25E          | LVDS, Emulated, VCCIO = 2.5V   | 0.03  | -0.01 | -0.03  | ns    |

| LVDS25           | LVDS, VCCIO = 2.5V             | 0.03  | 0.00  | -0.04  | ns    |

| BLVDS25          | BLVDS, Emulated, VCCIO = 2.5V  | 0.03  | 0.00  | -0.04  | ns    |

| MLVDS25          | MLVDS, Emulated, VCCIO = 2.5V  | 0.03  | 0.00  | -0.04  | ns    |

| RSDS25           | RSDS, VCCIO = 2.5V             | 0.03  | 0.00  | -0.03  | ns    |

| PPLVDS           | Point-to-Point LVDS            | 0.03  | -0.01 | -0.03  | ns    |

| TRLVDS           | Transition-Reduced LVDS        | 0.03  | 0.00  | -0.04  | ns    |

| Mini MLVDS       | Mini LVDS                      | 0.03  | -0.01 | -0.03  | ns    |

| LVPECL33         | LVPECL, Emulated, VCCIO = 3.0V | 0.17  | 0.07  | -0.04  | ns    |

| HSTL18_I         | HSTL_18 class I, VCCIO = 1.8V  | 0.20  | 0.17  | 0.13   | ns    |

| HSTL18_II        | HSTL_18 class II, VCCIO = 1.8V | 0.20  | 0.17  | 0.13   | ns    |

| HSTL18D_I        | Differential HSTL 18 class I   | 0.20  | 0.17  | 0.13   | ns    |

| HSTL18D_II       | Differential HSTL 18 class II  | 0.20  | 0.17  | 0.13   | ns    |

| HSTL15_I         | HSTL_15 class I, VCCIO = 1.5V  | 0.10  | 0.12  | 0.13   | ns    |

| HSTL15D_I        | Differential HSTL 15 class I   | 0.10  | 0.12  | 0.13   | ns    |

| SSTL33_I         | SSTL_3 class I, VCCIO = 3.0V   | 0.17  | 0.23  | 0.28   | ns    |

| SSTL33_II        | SSTL_3 class II, VCCIO = 3.0V  | 0.17  | 0.23  | 0.28   | ns    |

| SSTL33D_I        | Differential SSTL_3 class I    | 0.17  | 0.23  | 0.28   | ns    |

| SSTL33D_II       | Differential SSTL_3 class II   | 0.17  | 0.23  | 0.28   | ns    |

| SSTL25_I         | SSTL_2 class I, VCCIO = 2.5V   | 0.12  | 0.14  | 0.16   | ns    |

| SSTL25_II        | SSTL_2 class II, VCCIO = 2.5V  | 0.12  | 0.14  | 0.16   | ns    |

| SSTL25D_I        | Differential SSTL_2 class I    | 0.12  | 0.14  | 0.16   | ns    |

| SSTL25D_II       | Differential SSTL_2 class II   | 0.12  | 0.14  | 0.16   | ns    |

| SSTL18_I         | SSTL_18 class I, VCCIO = 1.8V  | 0.08  | 0.06  | 0.04   | ns    |

| SSTL18_II        | SSTL_18 class II, VCCIO = 1.8V | 0.08  | 0.06  | 0.04   | ns    |

| SSTL18D_I        | Differential SSTL_18 class I   | 0.08  | 0.06  | 0.04   | ns    |

| SSTL18D_II       | Differential SSTL_18 class II  | 0.08  | 0.06  | 0.04   | ns    |

| SSTL15           | SSTL_15, VCCIO = 1.5V          | 0.087 | 0.059 | 0.032  | ns    |

| SSTL15D          | Differential SSTL_15           | 0.087 | 0.025 | -0.036 | ns    |

| LVTTL33          | LVTTL, VCCIO = 3.0V            | 0.05  | 0.05  | 0.05   | ns    |

| LVCMOS33         | LVCMOS, VCCIO = 3.0V           | 0.05  | 0.05  | 0.05   | ns    |

| LVCMOS25         | LVCMOS, VCCIO = 2.5V           | 0.00  | 0.00  | 0.00   | ns    |

| LVCMOS18         | LVCMOS, VCCIO = 1.8V           | 0.06  | 0.08  | 0.11   | ns    |

| LVCMOS15         | LVCMOS, VCCIO = 1.5V           | 0.17  | 0.21  | 0.25   | ns    |

| LVCMOS12         | LVCMOS, VCCIO = 1.2V           | 0.01  | 0.05  | 0.08   | ns    |

| PCl33            | PCI, VCCIO = 3.0V              | 0.05  | 0.05  | 0.05   | ns    |

| Output Adjusters |                                |       |       |        |       |

| LVDS25E          | LVDS, Emulated, VCCIO = 2.5V   | 0.15  | 0.15  | 0.16   | ns    |

| LVDS25           | LVDS, VCCIO = 2.5V             | 0.02  | 0.08  | 0.13   | ns    |

| BLVDS25          | BLVDS, Emulated, VCCIO = 2.5V  | 0.00  | -0.02 | -0.04  | ns    |

| MLVDS25          | MLVDS, Emulated, VCCIO = 2.5V  | 0.00  | -0.01 | -0.03  | ns    |

# LatticeECP3 Family Timing Adders<sup>1, 2, 3, 4, 5</sup> (Continued)

### **Over Recommended Commercial Operating Conditions**

| Buffer Type   | Description                           | -8    | -7    | -6    | Units |

|---------------|---------------------------------------|-------|-------|-------|-------|

| LVCMOS15_4mA  | LVCMOS 1.5 4mA drive, fast slew rate  | 0.09  | 0.10  | 0.10  | ns    |

| LVCMOS15_8mA  | LVCMOS 1.5 8mA drive, fast slew rate  | 0.01  | 0.01  | 0.00  | ns    |

| LVCMOS12_2mA  | LVCMOS 1.2 2mA drive, fast slew rate  | 0.08  | 0.08  | 0.08  | ns    |

| LVCMOS12_6mA  | LVCMOS 1.2 6mA drive, fast slew rate  | -0.02 | -0.02 | -0.02 | ns    |

| LVCMOS33_4mA  | LVCMOS 3.3 4mA drive, slow slew rate  | 1.64  | 1.71  | 1.77  | ns    |

| LVCMOS33_8mA  | LVCMOS 3.3 8mA drive, slow slew rate  | 1.39  | 1.45  | 1.51  | ns    |

| LVCMOS33_12mA | LVCMOS 3.3 12mA drive, slow slew rate | 1.21  | 1.27  | 1.33  | ns    |

| LVCMOS33_16mA | LVCMOS 3.3 16mA drive, slow slew rate | 1.43  | 1.49  | 1.55  | ns    |

| LVCMOS33_20mA | LVCMOS 3.3 20mA drive, slow slew rate | 1.23  | 1.28  | 1.34  | ns    |

| LVCMOS25_4mA  | LVCMOS 2.5 4mA drive, slow slew rate  | 1.66  | 1.70  | 1.74  | ns    |

| LVCMOS25_8mA  | LVCMOS 2.5 8mA drive, slow slew rate  | 1.39  | 1.43  | 1.46  | ns    |

| LVCMOS25_12mA | LVCMOS 2.5 12mA drive, slow slew rate | 1.20  | 1.24  | 1.28  | ns    |

| LVCMOS25_16mA | LVCMOS 2.5 16mA drive, slow slew rate | 1.42  | 1.45  | 1.49  | ns    |

| LVCMOS25_20mA | LVCMOS 2.5 20mA drive, slow slew rate | 1.22  | 1.26  | 1.29  | ns    |

| LVCMOS18_4mA  | LVCMOS 1.8 4mA drive, slow slew rate  | 1.61  | 1.65  | 1.68  | ns    |

| LVCMOS18_8mA  | LVCMOS 1.8 8mA drive, slow slew rate  | 1.32  | 1.36  | 1.39  | ns    |

| LVCMOS18_12mA | LVCMOS 1.8 12mA drive, slow slew rate | 1.14  | 1.17  | 1.21  | ns    |

| LVCMOS18_16mA | LVCMOS 1.8 16mA drive, slow slew rate | 1.35  | 1.38  | 1.42  | ns    |

| LVCMOS15_4mA  | LVCMOS 1.5 4mA drive, slow slew rate  | 1.57  | 1.60  | 1.64  | ns    |

| LVCMOS15_8mA  | LVCMOS 1.5 8mA drive, slow slew rate  | 0.01  | 0.01  | 0.00  | ns    |

| LVCMOS12_2mA  | LVCMOS 1.2 2mA drive, slow slew rate  | 1.51  | 1.54  | 1.58  | ns    |

| LVCMOS12_6mA  | LVCMOS 1.2 6mA drive, slow slew rate  | -0.02 | -0.02 | -0.02 | ns    |

| PCI33         | PCI, VCCIO = 3.0V                     | 0.19  | 0.21  | 0.24  | ns    |

<sup>1.</sup> Timing adders are characterized but not tested on every device.

<sup>2.</sup> LVCMOS timing measured with the load specified in Switching Test Condition table.

<sup>3.</sup> All other standards tested according to the appropriate specifications.

<sup>4.</sup> Not all I/O standards and drive strengths are supported for all banks. See the Architecture section of this data sheet for details.

<sup>5.</sup> Commercial timing numbers are shown. Industrial numbers are typically slower and can be extracted from the ispLEVER software.

## sysCLOCK PLL Timing

### **Over Recommended Operating Conditions**

| Parameter                      | Descriptions                                        | Conditions                         | Clock         | Min.    | Тур. | Max.  | Units       |

|--------------------------------|-----------------------------------------------------|------------------------------------|---------------|---------|------|-------|-------------|

| 4                              | Input clock frequency (CLKI,                        |                                    | Edge clock    | 2       | _    | 500   | MHz         |

| f <sub>IN</sub>                | CLKFB)                                              |                                    | Primary clock | 2       | _    | 420   | MHz         |

| f.                             | Output clock frequency (CLKOP,                      |                                    | Edge clock    | 4       | _    | 500   | MHz         |

| TOUT                           | CLKOS)                                              |                                    | Primary clock | 4       | _    | 420   | MHz         |

| f <sub>OUT1</sub>              | K-Divider output frequency                          | CLKOK                              |               | 0.03125 | _    | 250   | MHz         |

| f <sub>OUT2</sub>              | K2-Divider output frequency                         | CLKOK2                             |               | 0.667   | _    | 166   | MHz         |

| $f_{VCO}$                      | PLL VCO frequency                                   |                                    |               | 500     | _    | 1000  | MHz         |

| f <sub>PFD</sub> <sup>3</sup>  | Phase detector input frequency                      |                                    | Edge clock    | 2       | _    | 500   | MHz         |

|                                |                                                     |                                    | Primary clock | 2       | _    | 420   | MHz         |

| AC Charac                      | teristics                                           |                                    |               | 1       |      |       |             |

| t <sub>PA</sub>                | Programmable delay unit                             |                                    |               | 65      | 130  | 260   | ps          |

|                                | 0                                                   |                                    | Edge clock    | 45      | 50   | 55    | %           |

| t <sub>DT</sub>                | Output clock duty cycle (CLKOS, at 50% setting)     | f <sub>OUT</sub> ≤ 250 MHz         | Primary clock | 45      | 50   | 55    | %           |

|                                | (02:100, at 00 /0 001g)                             | f <sub>OUT</sub> > 250MHz          | Primary clock | 30      | 50   | 70    | %           |

| t <sub>CPA</sub>               | Coarse phase shift error (CLKOS, at all settings)   |                                    |               | -5      | 0    | +5    | % of period |

| t <sub>OPW</sub>               | Output clock pulse width high or low (CLKOS)        | CON                                | 10            | 1.8     | _    | _     | ns          |

|                                |                                                     | f <sub>OUT</sub> ≥ 420MHz          |               | _       | _    | 200   | р-р         |

| t <sub>OPJIT</sub> 1           | Output clock period jitter                          | 420MHz > f <sub>OUT</sub> ≥ 100MHz |               | _       | _    | 250   | р-р         |

|                                |                                                     | f <sub>OUT</sub> < 100MHz          |               | _       | _    | 0.025 | UIPP        |

| t <sub>SK</sub>                | Input clock to output clock skew when N/M = integer | 2                                  |               | _       | _    | 500   | р-р         |

| <b>.</b> 2                     | Lock time                                           | 2 to 25 MHz                        |               | _       | _    | 200   | us          |

| t <sub>LOCK</sub> <sup>2</sup> | Lock time                                           | 25 to 500 MHz                      |               | _       | _    | 50    | us          |

| t <sub>UNLOCK</sub>            | Reset to PLL unlock time to ensure fast reset       |                                    |               | _       | _    | 50    | ns          |

| t <sub>HI</sub>                | Input clock high time                               | 90% to 90%                         |               | 0.5     | _    | _     | ns          |

| t <sub>LO</sub>                | Input clock low time                                | 10% to 10%                         |               | 0.5     | _    | _     | ns          |

| t <sub>IPJIT</sub>             | Input clock period jitter                           |                                    |               | _       | _    | 400   | р-р         |

| t <sub>RST</sub>               | Reset signal pulse width high,<br>RESETM,<br>RESETK |                                    |               | 10      | _    | _     | ns          |

|                                | Reset signal pulse width high, CNTRST               |                                    |               | 500     | _    | _     | ns          |

<sup>1.</sup> Jitter sample is taken over 10,000 samples of the primary PLL output with clean reference clock with no additional I/O toggling.

Output clock is valid after t<sub>LOCK</sub> for PLL reset and dynamic delay adjustment.

Period jitter and cycle-to-cycle jitter numbers are guaranteed for f<sub>PFD</sub> > 4MHz. For f<sub>PFD</sub> < 4MHz, the jitter numbers may not be met in certain conditions. Please contact the factory for f<sub>PFD</sub> < 4MHz.</li>

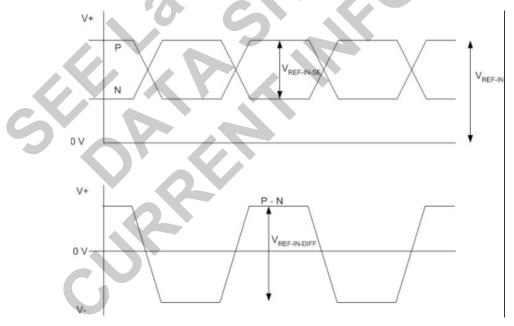

#### **SERDES External Reference Clock**

The external reference clock selection and its interface are a critical part of system applications for this product. Table 3-12 specifies reference clock requirements, over the full range of operating conditions.

Table 3-12. External Reference Clock Specification (refclkp/refclkn)

| Symbol                        | Description                                       | Min.  | Тур.     | Max.                   | Units                   |

|-------------------------------|---------------------------------------------------|-------|----------|------------------------|-------------------------|

| F <sub>REF</sub>              | Frequency range                                   | 15    | _        | 320                    | MHz                     |

| F <sub>REF-PPM</sub>          | Frequency tolerance <sup>4</sup>                  | -1000 | _        | 1000                   | ppm                     |

| V <sub>REF-IN-SE</sub>        | Input swing, single-ended clock <sup>1</sup>      | 200   | - 4      | V <sub>CCA</sub>       | mV, p-p                 |

| V <sub>REF-IN-DIFF</sub>      | Input swing, differential clock                   | 200   |          | 2*V <sub>CCA</sub>     | mV, p-p<br>differential |

| V <sub>REF-IN</sub>           | Input levels                                      | 0     |          | V <sub>CCA</sub> + 0.3 | V                       |

| V <sub>REF-CM-AC</sub>        | Input common mode range (AC coupled) <sup>2</sup> | 0.125 | <i>→</i> | V <sub>CCA</sub>       | V                       |

| D <sub>REF</sub>              | Duty cycle <sup>3</sup>                           | 40    | _        | 60                     | %                       |

| T <sub>REF-R</sub>            | Rise time (20% to 80%)                            | 200   | 500      | 1000                   | ps                      |

| T <sub>REF-F</sub>            | Fall time (80% to 20%)                            | 200   | 500      | 1000                   | ps                      |

| Z <sub>REF-IN-TERM-DIFF</sub> | Differential input termination                    | -20%  | 100/2K   | +20%                   | Ohms                    |

| C <sub>REF-IN-CAP</sub>       | Input capacitance                                 |       |          | 7                      | pF                      |

<sup>1.</sup> The signal swing for a single-ended input clock must be as large as the p-p differential swing of a differential input clock to get the same gain at the input receiver. Lower swings for the clock may be possible, but will tend to increase jitter.

Figure 3-13. SERDES External Reference Clock Waveforms

When AC coupled, the input common mode range is determined by: (Min input level) + (Peak-to-peak input swing)/2 ≤ (Input common mode voltage) ≤ (Max input level) - (Peak-to-peak input swing)/2

<sup>3.</sup> Measured at 50% amplitude.

<sup>4.</sup> Depending on the application, the PLL\_LOL\_SET and CDR\_LOL\_SET control registers may be adjusted for other tolerance values as described in TN1176, <u>LatticeECP3 SERDES/PCS Usage Guide</u>.

# **XAUI/Serial Rapid I/O Type 3 Electrical and Timing Characteristics AC and DC Characteristics**

Table 3-13. Transmit

#### **Over Recommended Operating Conditions**

| Symbol                                   | Description                      | Test Conditions | Min.           | Тур. | Max. | Units |

|------------------------------------------|----------------------------------|-----------------|----------------|------|------|-------|

| T <sub>RF</sub>                          | Differential rise/fall time      | 20%-80%         | _              | 80   | _    | ps    |

| Z <sub>TX_DIFF_DC</sub>                  | Differential impedance           |                 | 80             | 100  | 120  | Ohms  |

| J <sub>TX_DDJ</sub> <sup>2, 3, 4</sup>   | Output data deterministic jitter |                 | <del>-</del> \ | 35   | 0.17 | UI    |

| J <sub>TX_TJ</sub> <sup>1, 2, 3, 4</sup> | Total output data jitter         |                 |                | _    | 0.35 | UI    |

- 1. Total jitter includes both deterministic jitter and random jitter.

- 2. Jitter values are measured with each CML output AC coupled into a 50-ohm impedance (100-ohm differential impedance).

- 3. Jitter and skew are specified between differential crossings of the 50% threshold of the reference signal.

- 4. Values are measured at 2.5 Gbps.

Table 3-14. Receive and Jitter Tolerance

### **Over Recommended Operating Conditions**

| Symbol                                | Description                                   | Test Conditions              | Min. | Тур. | Max. | Units |

|---------------------------------------|-----------------------------------------------|------------------------------|------|------|------|-------|

| RL <sub>RX_DIFF</sub>                 | Differential return loss                      | From 100 MHz<br>to 3.125 GHz | 10   | V-L  | _    | dB    |

| RL <sub>RX_CM</sub>                   | Common mode return loss                       | From 100 MHz<br>to 3.125 GHz | 6    |      | _    | dB    |

| Z <sub>RX_DIFF</sub>                  | Differential termination resistance           |                              | 80   | 100  | 120  | Ohms  |

| J <sub>RX_DJ</sub> <sup>1, 2, 3</sup> | Deterministic jitter tolerance (peak-to-peak) |                              | 1    | _    | 0.37 | UI    |

| J <sub>RX_RJ</sub> <sup>1, 2, 3</sup> | Random jitter tolerance (peak-to-peak)        |                              | )-   | _    | 0.18 | UI    |

| J <sub>RX_SJ</sub> <sup>1, 2, 3</sup> | Sinusoidal jitter tolerance (peak-to-peak)    |                              |      | _    | 0.10 | UI    |

| J <sub>RX_TJ</sub> <sup>1, 2, 3</sup> | Total jitter tolerance (peak-to-peak)         |                              |      | _    | 0.65 | UI    |

| T <sub>RX_EYE</sub>                   | Receiver eye opening                          |                              | 0.35 | _    | _    | UI    |

- 1. Total jitter includes deterministic jitter, random jitter and sinusoidal jitter. The sinusoidal jitter tolerance mask is shown in Figure 3-14.

- 2. Jitter values are measured with each high-speed input AC coupled into a 50-ohm impedance.

- 3. Jitter and skew are specified between differential crossings of the 50% threshold of the reference signal.

- 4. Jitter tolerance parameters are characterized when Full Rx Equalization is enabled.

- 5. Values are measured at 2.5 Gbps.

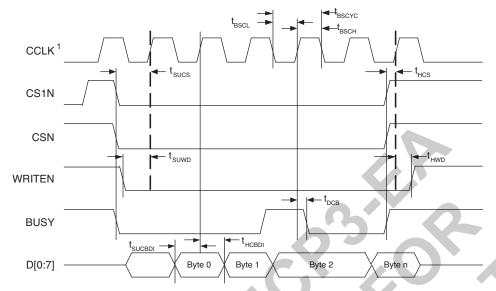

Figure 3-17. sysCONFIG Parallel Port Write Cycle

1. In Master Parallel Mode the FPGA provides CCLK (MCLK). In Slave Parallel Mode the external device provides CCLK.

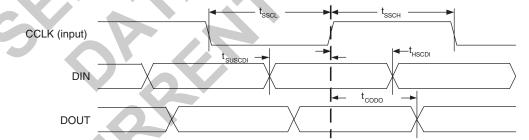

Figure 3-18. sysCONFIG Master Serial Port Timing

Figure 3-19. sysCONFIG Slave Serial Port Timing

### **Logic Signal Connections**

Package pinout information can be found under "Data Sheets" on the LatticeECP3 product pages on the Lattice website at <a href="www.latticesemi.com/products/fpga/ecp3">www.latticesemi.com/products/fpga/ecp3</a> and in the Lattice ispLEVER Design Planner software. To create pinout information from within Design Planner, select View -> Package View. Then select Select File -> Export and choose a type of output file. See Design Planner help for more information.

### **Thermal Management**

Thermal management is recommended as part of any sound FPGA design methodology. To assess the thermal characteristics of a system, Lattice specifies a maximum allowable junction temperature in all device data sheets. Designers must complete a thermal analysis of their specific design to ensure that the device and package do not exceed the junction temperature limits. Refer to the Thermal Management document to find the device/package specific thermal values.

### For Further Information

For further information regarding Thermal Management, refer to the following:

- Thermal Management document

- TN1181, Power Consumption and Management for LatticeECP3 Devices

- Power Calculator tool included with the Lattice ispLEVER design tool, or as a standalone download from www.latticesemi.com/software

| Part Number                    | Voltage | Grade | Package         | Pins | Temp. | LUTs (K) |

|--------------------------------|---------|-------|-----------------|------|-------|----------|

| LFE3-70E-6FN484C <sup>1</sup>  | 1.2V    | -6    | Lead-Free fpBGA | 484  | COM   | 67       |

| LFE3-70E-7FN484C <sup>1</sup>  | 1.2V    | -7    | Lead-Free fpBGA | 484  | COM   | 67       |

| LFE3-70E-8FN484C <sup>1</sup>  | 1.2V    | -8    | Lead-Free fpBGA | 484  | COM   | 67       |

| LFE3-70E-6FN672C <sup>1</sup>  | 1.2V    | -6    | Lead-Free fpBGA | 672  | COM   | 67       |

| LFE3-70E-7FN672C <sup>1</sup>  | 1.2V    | -7    | Lead-Free fpBGA | 672  | COM   | 67       |

| LFE3-70E-8FN672C <sup>1</sup>  | 1.2V    | -8    | Lead-Free fpBGA | 672  | COM   | 67       |

| LFE3-70E-6FN1156C <sup>1</sup> | 1.2V    | -6    | Lead-Free fpBGA | 1156 | COM   | 67       |

| LFE3-70E-7FN1156C <sup>1</sup> | 1.2V    | -7    | Lead-Free fpBGA | 1156 | COM   | 67       |

| LFE3-70E-8FN1156C <sup>1</sup> | 1.2V    | -8    | Lead-Free fpBGA | 1156 | COM   | 67       |

<sup>1.</sup> This device has associated errata. View <a href="https://www.latticesemi.com/documents/ds1021.zip">www.latticesemi.com/documents/ds1021.zip</a> for a description of the errata.

| Part Number        | Voltage | Grade | Package         | Pins | Temp. | LUTs (K) |

|--------------------|---------|-------|-----------------|------|-------|----------|

| LFE3-95EA-6FN484C  | 1.2V    | -6    | Lead-Free fpBGA | 484  | COM   | 92       |

| LFE3-95EA-7FN484C  | 1.2V    | -7    | Lead-Free fpBGA | 484  | COM   | 92       |

| LFE3-95EA-8FN484C  | 1.2V    | -8    | Lead-Free fpBGA | 484  | COM   | 92       |

| LFE3-95EA-6FN672C  | 1.2V    | -6    | Lead-Free fpBGA | 672  | COM   | 92       |

| LFE3-95EA-7FN672C  | 1.2V    | -7    | Lead-Free fpBGA | 672  | СОМ   | 92       |

| LFE3-95EA-8FN672C  | 1.2V    | -8    | Lead-Free fpBGA | 672  | COM   | 92       |

| LFE3-95EA-6FN1156C | 1.2V    | -6    | Lead-Free fpBGA | 1156 | COM   | 92       |

| LFE3-95EA-7FN1156C | 1.2V    | -7    | Lead-Free fpBGA | 1156 | COM   | 92       |

| LFE3-95EA-8FN1156C | 1.2V    | -8    | Lead-Free fpBGA | 1156 | COM   | 92       |

| Part Number                    | Voltage | Grade | Package         | Pins | Temp. | LUTs (K) |

|--------------------------------|---------|-------|-----------------|------|-------|----------|

| LFE3-95E-6FN484C <sup>1</sup>  | 1.2V    | -6    | Lead-Free fpBGA | 484  | COM   | 92       |

| LFE3-95E-7FN484C <sup>1</sup>  | 1.2V    | -7    | Lead-Free fpBGA | 484  | COM   | 92       |

| LFE3-95E-8FN484C <sup>1</sup>  | 1.2V    | -8    | Lead-Free fpBGA | 484  | COM   | 92       |

| LFE3-95E-6FN672C <sup>1</sup>  | 1.2V    | -6    | Lead-Free fpBGA | 672  | COM   | 92       |

| LFE3-95E-7FN672C <sup>1</sup>  | 1.2V    | -7    | Lead-Free fpBGA | 672  | COM   | 92       |

| LFE3-95E-8FN672C <sup>1</sup>  | 1.2V    | -8    | Lead-Free fpBGA | 672  | COM   | 92       |

| LFE3-95E-6FN1156C <sup>1</sup> | 1.2V    | -6    | Lead-Free fpBGA | 1156 | COM   | 92       |

| LFE3-95E-7FN1156C1             | 1.2V    | -7    | Lead-Free fpBGA | 1156 | COM   | 92       |

| LFE3-95E-8FN1156C <sup>1</sup> | 1.2V    | -8    | Lead-Free fpBGA | 1156 | COM   | 92       |

$<sup>1.</sup> This device \ has \ associated \ errata. \ View \ \underline{www.latticesemi.com/documents/ds1021.zip} \ for \ a \ description \ of \ the \ errata.$

| Part Number         | Voltage | Grade | Package         | Pins | Temp. | LUTs (K) |

|---------------------|---------|-------|-----------------|------|-------|----------|

| LFE3-150EA-6FN672C  | 1.2V    | -6    | Lead-Free fpBGA | 672  | COM   | 149      |

| LFE3-150EA-7FN672C  | 1.2V    | -7    | Lead-Free fpBGA | 672  | COM   | 149      |

| LFE3-150EA-8FN672C  | 1.2V    | -8    | Lead-Free fpBGA | 672  | COM   | 149      |

| LFE3-150EA-6FN1156C | 1.2V    | -6    | Lead-Free fpBGA | 1156 | COM   | 149      |

| LFE3-150EA-7FN1156C | 1.2V    | -7    | Lead-Free fpBGA | 1156 | COM   | 149      |

| LFE3-150EA-8FN1156C | 1.2V    | -8    | Lead-Free fpBGA | 1156 | COM   | 149      |

| Part Number            | Voltage | Grade | Package         | Pins | Temp. | LUTs (K) |

|------------------------|---------|-------|-----------------|------|-------|----------|

| LFE3-150EA-6FN672CTW*  | 1.2V    | -6    | Lead-Free fpBGA | 672  | COM   | 149      |

| LFE3-150EA-7FN672CTW*  | 1.2V    | -7    | Lead-Free fpBGA | 672  | COM   | 149      |

| LFE3-150EA-8FN672CTW*  | 1.2V    | -8    | Lead-Free fpBGA | 672  | COM   | 149      |

| LFE3-150EA-6FN1156CTW* | 1.2V    | -6    | Lead-Free fpBGA | 1156 | COM   | 149      |

| LFE3-150EA-7FN1156CTW* | 1.2V    | -7    | Lead-Free fpBGA | 1156 | COM   | 149      |

| LFE3-150EA-8FN1156CTW* | 1.2V    | -8    | Lead-Free fpBGA | 1156 | COM   | 149      |

\*Note: Specifications for the LFE3-150EA-*sp*FN*pkg*CTW and LFE3-150EA-*sp*FN*pkg*ITW devices, (where *sp* is the speed and *pkg* is the package), are the same as the LFE3-150EA-*sp*FN*pkg*C and LFE3-150EA-*sp*FN*pkg*I devices respectively, except as specified below.

- The CTC (Clock Tolerance Circuit) inside the SERDES hard PCS in the TW device is not functional but it can be bypassed and implemented in soft IP.

- The SERDES XRES pin on the TW device passes CDM testing at 250V.

| Part Number                    | Voltage | Grade | Package         | Pins | Temp. | LUTs (K) |

|--------------------------------|---------|-------|-----------------|------|-------|----------|

| LFE3-70E-6FN484I <sup>1</sup>  | 1.2V    | -6    | Lead-Free fpBGA | 484  | IND   | 67       |

| LFE3-70E-7FN484I <sup>1</sup>  | 1.2V    | -7    | Lead-Free fpBGA | 484  | IND   | 67       |

| LFE3-70E-8FN484I <sup>1</sup>  | 1.2V    | -8    | Lead-Free fpBGA | 484  | IND   | 67       |

| LFE3-70E-6FN672I <sup>1</sup>  | 1.2V    | -6    | Lead-Free fpBGA | 672  | IND   | 67       |

| LFE3-70E-7FN672I <sup>1</sup>  | 1.2V    | -7    | Lead-Free fpBGA | 672  | IND   | 67       |

| LFE3-70E-8FN672I <sup>1</sup>  | 1.2V    | -8    | Lead-Free fpBGA | 672  | IND   | 67       |

| LFE3-70E-6FN1156I <sup>1</sup> | 1.2V    | -6    | Lead-Free fpBGA | 1156 | IND   | 67       |

| LFE3-70E-7FN1156I <sup>1</sup> | 1.2V    | -7    | Lead-Free fpBGA | 1156 | IND   | 67       |

| LFE3-70E-8FN1156I <sup>1</sup> | 1.2V    | -8    | Lead-Free fpBGA | 1156 | IND   | 67       |

<sup>1.</sup> This device has associated errata. View <a href="https://www.latticesemi.com/documents/ds1021.zip">www.latticesemi.com/documents/ds1021.zip</a> for a description of the errata.

| Part Number        | Voltage | Grade | Package         | Pins | Temp. | LUTs (K) |

|--------------------|---------|-------|-----------------|------|-------|----------|

| LFE3-95EA-6FN484I  | 1.2V    | -6    | Lead-Free fpBGA | 484  | IND   | 92       |

| LFE3-95EA-7FN484I  | 1.2V    | -7    | Lead-Free fpBGA | 484  | IND   | 92       |

| LFE3-95EA-8FN484I  | 1.2V    | -8    | Lead-Free fpBGA | 484  | IND   | 92       |

| LFE3-95EA-6FN672I  | 1.2V    | -6    | Lead-Free fpBGA | 672  | IND   | 92       |

| LFE3-95EA-7FN672I  | 1.2V    | -7    | Lead-Free fpBGA | 672  | IND   | 92       |

| LFE3-95EA-8FN672I  | 1.2V    | -8    | Lead-Free fpBGA | 672  | IND   | 92       |

| LFE3-95EA-6FN1156I | 1.2V    | -6    | Lead-Free fpBGA | 1156 | IND   | 92       |

| LFE3-95EA-7FN1156I | 1.2V    | -7    | Lead-Free fpBGA | 1156 | IND   | 92       |

| LFE3-95EA-8FN1156I | 1.2V    | -8    | Lead-Free fpBGA | 1156 | IND   | 92       |

| Part Number                    | Voltage | Grade | Package         | Pins | Temp. | LUTs (K) |

|--------------------------------|---------|-------|-----------------|------|-------|----------|

| LFE3-95E-6FN484I <sup>1</sup>  | 1.2V    | -6    | Lead-Free fpBGA | 484  | IND   | 92       |

| LFE3-95E-7FN484I <sup>1</sup>  | 1.2V    | -7    | Lead-Free fpBGA | 484  | IND   | 92       |

| LFE3-95E-8FN484I <sup>1</sup>  | 1.2V    | -8    | Lead-Free fpBGA | 484  | IND   | 92       |

| LFE3-95E-6FN672I <sup>1</sup>  | 1.2V    | -6    | Lead-Free fpBGA | 672  | IND   | 92       |

| LFE3-95E-7FN672I <sup>1</sup>  | 1.2V    | -7    | Lead-Free fpBGA | 672  | IND   | 92       |

| LFE3-95E-8FN672I <sup>1</sup>  | 1.2V    | -8    | Lead-Free fpBGA | 672  | IND   | 92       |

| LFE3-95E-6FN1156I <sup>1</sup> | 1.2V    | -6    | Lead-Free fpBGA | 1156 | IND   | 92       |

| LFE3-95E-7FN1156I <sup>1</sup> | 1.2V    | -7    | Lead-Free fpBGA | 1156 | IND   | 92       |

| LFE3-95E-8FN1156I <sup>1</sup> | 1.2V    | -8    | Lead-Free fpBGA | 1156 | IND   | 92       |

<sup>1.</sup> This device has associated errata. View <a href="https://www.latticesemi.com/documents/ds1021.zip">www.latticesemi.com/documents/ds1021.zip</a> for a description of the errata.