Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

## **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                                             |

|--------------------------------|-----------------------------------------------------------------------------|

| Product Status                 | Obsolete                                                                    |

| Number of LABs/CLBs            | 8375                                                                        |

| Number of Logic Elements/Cells | 67000                                                                       |

| Total RAM Bits                 | 4526080                                                                     |

| Number of I/O                  | 380                                                                         |

| Number of Gates                | -                                                                           |

| Voltage - Supply               | 1.14V ~ 1.26V                                                               |

| Mounting Type                  | Surface Mount                                                               |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                                             |

| Package / Case                 | 672-BBGA                                                                    |

| Supplier Device Package        | 672-FPBGA (27x27)                                                           |

| Purchase URL                   | https://www.e-xfl.com/product-detail/lattice-semiconductor/lfe3-70e-7fn672c |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# LatticeECP3 Family Data Sheet Architecture

March 2010 Preliminary Data Sheet DS1021

## **Architecture Overview**

Each LatticeECP3 device contains an array of logic blocks surrounded by Programmable I/O Cells (PIC). Interspersed between the rows of logic blocks are rows of sysMEM™ Embedded Block RAM (EBR) and rows of sysDSP™ Digital Signal Processing slices, as shown in Figure 2-1. In addition, the LatticeECP3 family contains SERDES Quads on the bottom of the device.

There are two kinds of logic blocks, the Programmable Functional Unit (PFU) and Programmable Functional Unit without RAM (PFF). The PFU contains the building blocks for logic, arithmetic, RAM and ROM functions. The PFF block contains building blocks for logic, arithmetic and ROM functions. Both PFU and PFF blocks are optimized for flexibility, allowing complex designs to be implemented quickly and efficiently. Logic Blocks are arranged in a two-dimensional array. Only one type of block is used per row.

The LatticeECP3 devices contain one or more rows of sysMEM EBR blocks. sysMEM EBRs are large, dedicated 18Kbit fast memory blocks. Each sysMEM block can be configured in a variety of depths and widths as RAM or ROM. In addition, LatticeECP3 devices contain up to two rows of DSP slices. Each DSP slice has multipliers and adder/accumulators, which are the building blocks for complex signal processing capabilities.

The LatticeECP3 devices feature up to 16 embedded 3.2Gbps SERDES (Serializer / Deserializer) channels. Each SERDES channel contains independent 8b/10b encoding / decoding, polarity adjust and elastic buffer logic. Each group of four SERDES channels, along with its Physical Coding Sub-layer (PCS) block, creates a quad. The functionality of the SERDES/PCS quads can be controlled by memory cells set during device configuration or by registers that are addressable during device operation. The registers in every quad can be programmed via the SERDES Client Interface (SCI). These quads (up to four) are located at the bottom of the devices.

Each PIC block encompasses two PIOs (PIO pairs) with their respective sysl/O buffers. The sysl/O buffers of the LatticeECP3 devices are arranged in seven banks, allowing the implementation of a wide variety of I/O standards. In addition, a separate I/O bank is provided for the programming interfaces. 50% of the PIO pairs on the left and right edges of the device can be configured as LVDS transmit/receive pairs. The PIC logic also includes pre-engineered support to aid in the implementation of high speed source synchronous standards such as XGMII, 7:1 LVDS, along with memory interfaces including DDR3.

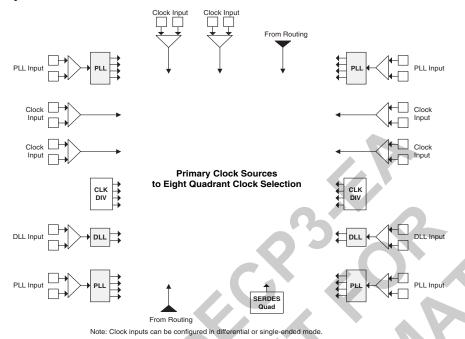

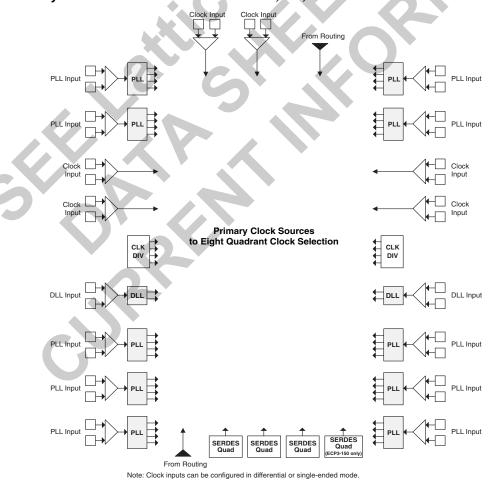

Other blocks provided include PLLs, DLLs and configuration functions. The LatticeECP3 architecture provides two Delay Locked Loops (DLLs) and up to ten Phase Locked Loops (PLLs). In addition, each LatticeECP3 family member provides two DLLs per device. The PLL and DLL blocks are located at the end of the EBR/DSP rows.

The configuration block that supports features such as configuration bit-stream decryption, transparent updates and dual-boot support is located toward the center of this EBR row. Every device in the LatticeECP3 family supports a sysCONFIG™ port located in the corner between banks one and two, which allows for serial or parallel device configuration.

In addition, every device in the family has a JTAG port. This family also provides an on-chip oscillator and soft error detect capability. The LatticeECP3 devices use 1.2V as their core voltage.

Figure 2-10. Primary Clock Sources for LatticeECP3-35

Figure 2-11. Primary Clock Sources for LatticeECP3-70, -95, -150

## **Secondary Clock/Control Sources**

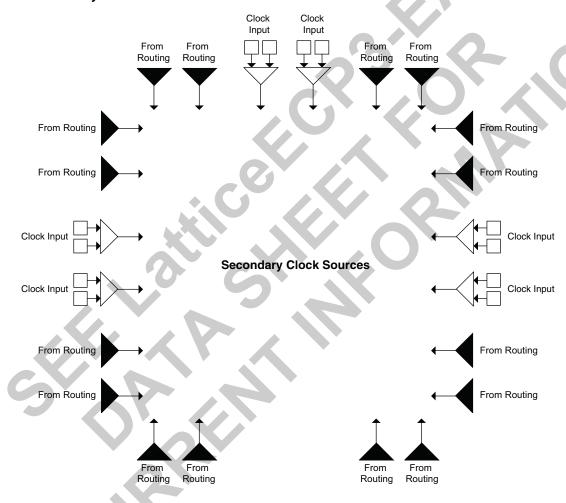

LatticeECP3 devices derive eight secondary clock sources (SC0 through SC7) from six dedicated clock input pads and the rest from routing. Figure 2-14 shows the secondary clock sources. All eight secondary clock sources are defined as inputs to a per-region mux SC0-SC7. SC0-SC3 are primary for control signals (CE and/or LSR), and SC4-SC7 are for clock and high fanout data.

In an actual implementation, there is some overlap to maximize routability. In addition to SC0-SC3, SC7 is also an input to the control signals (LSR or CE). SC0-SC2 are also inputs to clocks along with SC4-SC7. High fanout logic signals (LUT inputs) will utilize the X2 and X0 switches where SC0-SC7 are inputs to X2 switches, and SC4-SC7 are inputs to X0 switches. Note that through X0 switches, SC4-SC7 can also access control signals CE/LSR.

Figure 2-14. Secondary Clock Sources

Note: Clock inputs can be configured in differential or single-ended mode.

# **Secondary Clock/Control Routing**

Global secondary clock is a secondary clock that is distributed to all regions. The purpose of the secondary clock routing is to distribute the secondary clock sources to the secondary clock regions. Secondary clocks in the LatticeECP3 devices are region-based resources. Certain EBR rows and special vertical routing channels bind the secondary clock regions. This special vertical routing channel aligns with either the left edge of the center DSP slice in the DSP row or the center of the DSP row. Figure 2-15 shows this special vertical routing channel and the 20 secondary clock regions for the LatticeECP3 family of devices. All devices in the LatticeECP3 family have eight

- as, overflow, underflow and convergent rounding, etc.

- Flexible cascading across slices to get larger functions

- RTL Synthesis friendly synchronous reset on all registers, while still supporting asynchronous reset for legacy users

- Dynamic MUX selection to allow Time Division Multiplexing (TDM) of resources for applications that require processor-like flexibility that enables different functions for each clock cycle

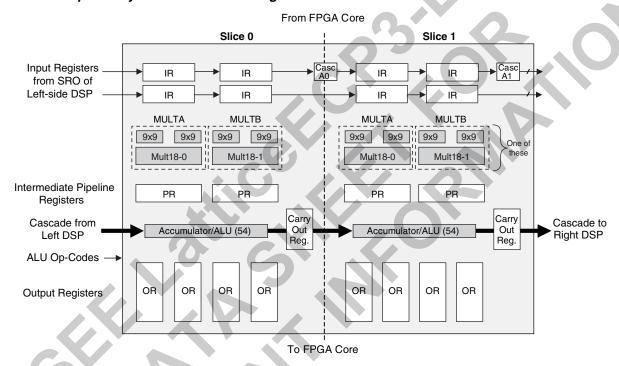

For most cases, as shown in Figure 2-24, the LatticeECP3 DSP slice is backwards-compatible with the LatticeECP2™ sysDSP block, such that, legacy applications can be targeted to the LatticeECP3 sysDSP slice. The functionality of one LatticeECP2 sysDSP Block can be mapped into two adjacent LatticeECP3 sysDSP slices, as shown in Figure 2-25.

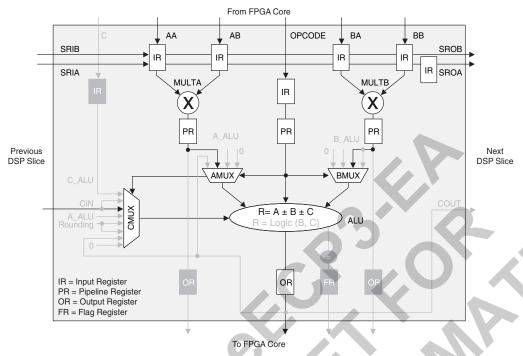

Figure 2-24. Simplified sysDSP Slice Block Diagram

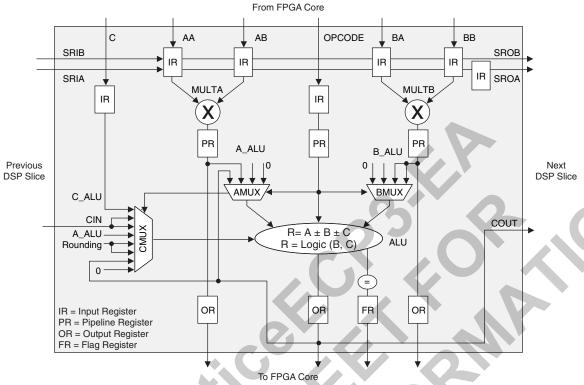

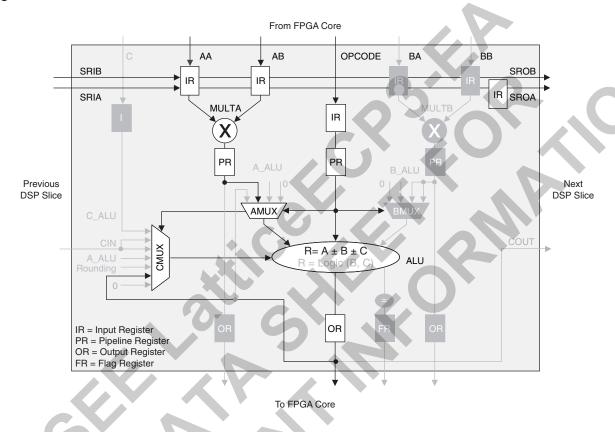

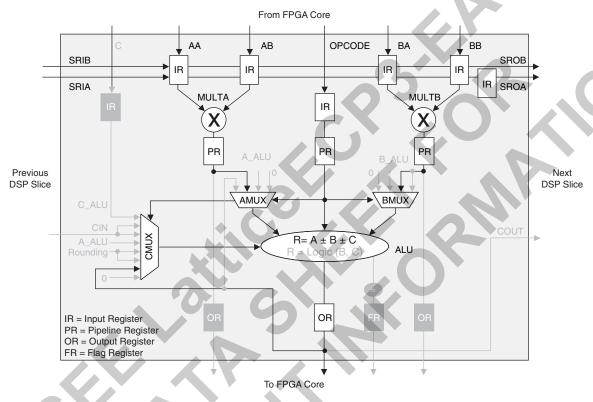

Figure 2-25. Detailed sysDSP Slice Diagram

Note: A\_ALU, B\_ALU and C\_ALU are internal signals generated by combining bits from AA, AB, BA BB and C inputs. See TN1182, LatticeECP3 sysDSP Usage Guide, for further information.

The LatticeECP2 sysDSP block supports the following basic elements.

- MULT (Multiply)

- MAC (Multiply, Accumulate)

- MULTADDSUB (Multiply, Addition/Subtraction)

- MULTADDSUBSUM (Multiply, Addition/Subtraction, Summation)

Table 2-8 shows the capabilities of each of the LatticeECP3 slices versus the above functions.

Table 2-8. Maximum Number of Elements in a Slice

| Width of Multiply | х9             | x18 | x36 |

|-------------------|----------------|-----|-----|

| MULT              | 4              | 2   | 1/2 |

| MAC               | 1              | 1   | _   |

| MULTADDSUB        | 2              | 1   | _   |

| MULTADDSUBSUM     | 1 <sup>1</sup> | 1/2 | _   |

<sup>1.</sup> One slice can implement 1/2 9x9 m9x9addsubsum and two m9x9addsubsum with two slices.

Some options are available in the four elements. The input register in all the elements can be directly loaded or can be loaded as a shift register from previous operand registers. By selecting "dynamic operation" the following operations are possible:

- In the Add/Sub option the Accumulator can be switched between addition and subtraction on every cycle.

- The loading of operands can switch between parallel and serial operations.

### **MAC DSP Element**

In this case, the two operands, AA and AB, are multiplied and the result is added with the previous accumulated value. This accumulated value is available at the output. The user can enable the input and pipeline registers, but the output register is always enabled. The output register is used to store the accumulated value. The ALU is configured as the accumulator in the sysDSP slice in the LatticeECP3 family can be initialized dynamically. A registered overflow signal is also available. The overflow conditions are provided later in this document. Figure 2-27 shows the MAC sysDSP element.

Figure 2-27. MAC DSP Element

#### **MMAC DSP Element**

The LatticeECP3 supports a MAC with two multipliers. This is called Multiply Multiply Accumulate or MMAC. In this case, the two operands, AA and AB, are multiplied and the result is added with the previous accumulated value and with the result of the multiplier operation of operands BA and BB. This accumulated value is available at the output. The user can enable the input and pipeline registers, but the output register is always enabled. The output register is used to store the accumulated value. The ALU is configured as the accumulator in the sysDSP slice. A registered overflow signal is also available. The overflow conditions are provided later in this document. Figure 2-28 shows the MMAC sysDSP element.

Figure 2-28. MMAC sysDSP Element

Figure 2-31. MULTADDSUBSUM Slice 1

# **Advanced sysDSP Slice Features**

## Cascading

The LatticeECP3 sysDSP slice has been enhanced to allow cascading. Adder trees are implemented fully in sys-DSP slices, improving the performance. Cascading of slices uses the signals CIN, COUT and C Mux of the slice.

#### **Addition**

The LatticeECP3 sysDSP slice allows for the bypassing of multipliers and cascading of adder logic. High performance adder functions are implemented without the use of LUTs. The maximum width adders that can be implemented are 54-bit.

#### Rounding

The rounding operation is implemented in the ALU and is done by adding a constant followed by a truncation operation. The rounding methods supported are:

- Rounding to zero (RTZ)

- · Rounding to infinity (RTI)

- · Dynamic rounding

- Random rounding

- Convergent rounding

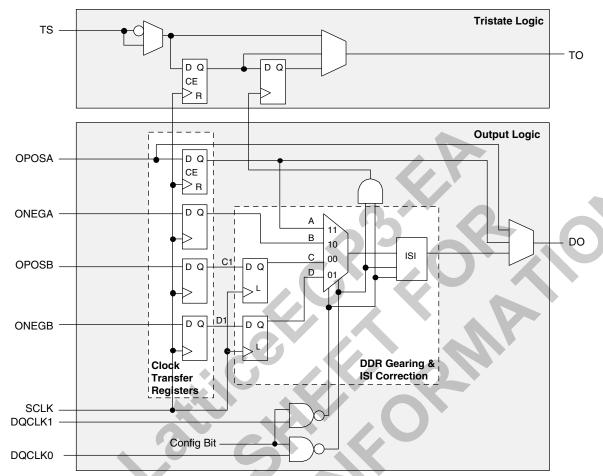

Figure 2-34. ECP3-70/95 (E or EA) Output and Tristate Block for Left and Right Edges

## **Tristate Register Block**

The tristate register block registers tri-state control signals from the core of the device before they are passed to the sysl/O buffers. The block contains a register for SDR operation and an additional register for DDR operation.

In SDR and non-gearing DDR modes, TS input feeds one of the flip-flops that then feeds the output. In DDRX2 mode, the register TS input is fed into another register that is clocked using the DQCLK0 and DQCLK1 signals. The output of this register is used as a tristate control.

#### ISI Calibration

The setting for Inter-Symbol Interference (ISI) cancellation occurs in the output register block. ISI correction is only available in the DDRX2 modes. ISI calibration settings exist once per output register block, so each I/O in a DQS-12 group may have a different ISI calibration setting.

The ISI block extends output signals at certain times, as a function of recent signal history. So, if the output pattern consists of a long strings of 0's to long strings of 1's, there are no delays on output signals. However, if there are quick, successive transitions from 010, the block will stretch out the binary 1. This is because the long trail of 0's will cause these symbols to interfere with the logic 1. Likewise, if there are quick, successive transitions from 101, the block will stretch out the binary 0. This block is controlled by a 3-bit delay control that can be set in the DQS control logic block.

For more information about this topic, please see the list of technical documentation at the end of this data sheet.

# **Typical Building Block Function Performance**

Pin-to-Pin Performance (LVCMOS25 12mA Drive)<sup>1, 2</sup>

| Function        | -8 Timing | Units |

|-----------------|-----------|-------|

| Basic Functions |           |       |

| 16-bit Decoder  | 4.7       | ns    |

| 32-bit Decoder  | 4.7       | ns    |

| 64-bit Decoder  | 5.7       | ns    |

| 4:1 MUX         | 4.1       | ns    |

| 8:1 MUX         | 4.3       | ns    |

| 16:1 MUX        | 4.7       | ns    |

| 32:1 MUX        | 4.8       | ns    |

<sup>1.</sup> These functions were generated using the ispLEVER design tool. Exact performance may vary with device and tool version. The tool uses internal parameters that have been characterized but are not tested on every device.

## Register-to-Register Performance<sup>1, 2</sup>

| Function                                                                              | -8 Timing | Units |

|---------------------------------------------------------------------------------------|-----------|-------|

| Basic Functions                                                                       |           |       |

| 16-bit Decoder                                                                        | 500       | MHz   |

| 32-bit Decoder                                                                        | 500       | MHz   |

| 64-bit Decoder                                                                        | 475       | MHz   |

| 4:1 MUX                                                                               | 500       | MHz   |

| 8:1 MUX                                                                               | 500       | MHz   |

| 16:1 MUX                                                                              | 500       | MHz   |

| 32:1 MUX                                                                              | 445       | MHz   |

| 8-bit adder                                                                           | 500       | MHz   |

| 16-bit adder                                                                          | 500       | MHz   |

| 64-bit adder                                                                          | 305       | MHz   |

| 16-bit counter                                                                        | 500       | MHz   |

| 32-bit counter                                                                        | 460       | MHz   |

| 64-bit counter                                                                        | 320       | MHz   |

| 64-bit accumulator                                                                    | 315       | MHz   |

| Embedded Memory Functions                                                             |           |       |

| 512x36 Single Port RAM, EBR Output Registers                                          | 340       | MHz   |

| 1024x18 True-Dual Port RAM (Write Through or Normal, EBR Output Registers)            | 340       | MHz   |

| 1024x18 True-Dual Port RAM (Read-Before-Write, EBR Output Registers; EA devices only) | 130       | MHz   |

| 1024x18 True-Dual Port RAM (Write Through or Normal, PLC Output Registers)            | 245       | MHz   |

| Distributed Memory Functions                                                          | 1         | I     |

| 16x4 Pseudo-Dual Port RAM (One PFU)                                                   | 500       | MHz   |

| 32x4 Pseudo-Dual Port RAM                                                             | 500       | MHz   |

| 64x8 Pseudo-Dual Port RAM                                                             | 380       | MHz   |

| DSP Function                                                                          | •         | L     |

| 18x18 Multiplier (All Registers)                                                      | 400       | MHz   |

| 9x9 Multiplier (All Registers)                                                        | 400       | MHz   |

| 36x36 Multiply (All Registers)                                                        | 245       | MHz   |

<sup>2.</sup> Commercial timing numbers are shown. Industrial numbers are typically slower and can be extracted from the ispLEVER software.

# LatticeECP3 External Switching Characteristics (Continued)<sup>1, 2</sup>

## **Over Recommended Commercial Operating Conditions**

|                                                                                                                                 |                                                     |                   | -        | 8      | -7       |          | -6      |        |       |  |

|---------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|-------------------|----------|--------|----------|----------|---------|--------|-------|--|

| Parameter                                                                                                                       | Description                                         | Device            | Min.     | Max.   | Min.     | Max.     | Min.    | Max.   | Units |  |

| t <sub>DVECLKGDDR</sub>                                                                                                         | Data Hold After CLK                                 | ECP3-70E/95E      | 0.765    | _      | 0.765    | _        | 0.765   | _      | UI    |  |

| f <sub>MAX_GDDR</sub>                                                                                                           | DDR/DDRX2 Clock Frequency <sup>8</sup>              | ECP3-70E/95E      | _        | 500    | _        | 420      | _       | 375    | MHz   |  |

| Generic DDRX2 Inputs with Clock and Data (<10 Bits Wide) Centered at Pin (GDDRX2_RX.DQS.Centered) using DQS Pin for Clock Input |                                                     |                   |          |        |          |          |         |        |       |  |

| Left and Right S                                                                                                                | Bides                                               |                   |          |        |          | <b>—</b> |         |        |       |  |

| t <sub>SUGDDR</sub>                                                                                                             | Data Setup Before CLK                               | ECP3-150EA        |          | /PA    |          | _        |         |        | ns    |  |

| t <sub>HGDDR</sub>                                                                                                              | Data Hold After CLK                                 | ECP3-150EA        | ,        | Y      | <b>^</b> | _        |         | _      | ns    |  |

| f <sub>MAX_GDDR</sub>                                                                                                           | DDRX2 Clock Frequency                               | ECP3-150EA        |          |        |          |          | _       |        | ns    |  |

|                                                                                                                                 | Inputs with Clock and Data (<10 Bits                | Side) Aligned at  | Pin (GI  | DDRX2  | RX.DQ    | S.Aligı  | ned) Us | ing DQ | S Pin |  |

| Left and Right S                                                                                                                | Bides                                               |                   |          |        |          |          |         |        |       |  |

| <sup>†</sup> DVACLKGDDR                                                                                                         | Data Setup Before CLK (Left and Right Side)         | ECP3-150EA        | - (      |        |          |          | 1       |        |       |  |

| t <sub>DVECLKGDDR</sub>                                                                                                         | Data Hold After CLK (Left and Right Side)           | ECP3-150EA        | <i>\</i> | 7      |          | A        |         | _      |       |  |

| f <sub>MAX_GDDR</sub>                                                                                                           | DDRX2 Clock Frequency (Left and Right Side)         | ECP3-150EA        |          |        | R        |          | _       |        |       |  |

| Generic DDRX1                                                                                                                   | Output with Clock and Data (>10 Bits                | Wide) Centered    | at Pin ( | (GDDR  | X1_TX.   | SCLK.C   | entere  | d)     |       |  |

| Left, Right and                                                                                                                 | Top Sides                                           |                   |          |        |          |          |         |        |       |  |

| t <sub>DVBGDDR</sub>                                                                                                            | Data Valid Before CLK                               | ECP3-150EA        |          |        |          | _        |         | _      |       |  |

| t <sub>DVAGDDR</sub>                                                                                                            | Data Valid After CLK                                | ECP3-150EA        |          | 7      |          | _        |         | _      |       |  |

| f <sub>MAX_GDDR</sub>                                                                                                           | DDRX1 Clock Frequency                               | ECP3-150EA        |          |        | _        |          | _       |        |       |  |

| Generic DDRX1 (GDDRX1_TX.E                                                                                                      | Outputs with clock in the center of d CLK.Centered) | ata window, with  | PLL 90   | -degre | e shifte | d clock  | ouput   |        |       |  |

| t <sub>DIBGDDR</sub>                                                                                                            | Data Invalid Before CLK                             | ECP3-70E/95E      | 670      | _      | 670      | _        | 670     | _      | ps    |  |

| t <sub>DIAGDDR</sub>                                                                                                            | Data Invalid After CLK                              | ECP3-70E/95E      | 670      | _      | 670      | _        | 670     | _      | ps    |  |

| fMAX_GDDR                                                                                                                       | DDRX1 Clock Frequency                               | ECP3-70E/95E      | _        | 250    | _        | 250      | _       | 250    | MHz   |  |

| Generic DDRX1                                                                                                                   | Output with Clock and Data (> 10 Bit                | s Wide) Aligned a | at Pin ( | GDDRX  | 1_TX.S   | CLK.A    | ligned) |        |       |  |

| Left, Right and                                                                                                                 | Top Sides                                           |                   |          |        |          |          |         |        |       |  |

| t <sub>DIBGDDR</sub>                                                                                                            | Data Hold After CLK                                 | ECP3-150EA        | _        |        | _        |          | _       |        |       |  |

| t <sub>DIAGDDR</sub>                                                                                                            | Data Setup Before CLK                               | ECP3-150EA        | _        |        | _        |          | _       |        |       |  |

| f <sub>MAX_GDDR</sub>                                                                                                           | DDRX1 Clock Frequency                               | ECP3-150EA        | _        |        | _        |          | _       |        |       |  |

| Generic DDRX1                                                                                                                   | Outputs with clock and data edge ali                | gned, without PL  | L        | •      |          | •        | •       |        |       |  |

| t <sub>DIBGDDR</sub>                                                                                                            | Data Invalid Before CLK                             | ECP3-70E/95E      | _        | 330    | _        | 330      | _       | 330    | ps    |  |

| t <sub>DIAGDDR</sub>                                                                                                            | Data Invalid After CLK                              | ECP3-70E/95E      | _        | 330    | _        | 330      | _       | 330    | ps    |  |

| f <sub>MAX_GDDR</sub>                                                                                                           | DDRX1 Clock Frequency                               | ECP3-70E/95E      | _        | 250    | _        | 250      | _       | 250    | MHz   |  |

| Generic DDRX1                                                                                                                   | Output with Clock and Data (<10 Bits                | Wide) Centered    | at Pin ( | (GDDR  | K1_TX.I  | DQS.C    | entered | )      |       |  |

| Left, Right and                                                                                                                 | Top Sides                                           |                   |          |        |          |          |         |        |       |  |

| t <sub>DVBGDDR</sub>                                                                                                            | Data Valid Before CLK                               | ECP3-150EA        | _        |        | _        |          | _       |        |       |  |

| t <sub>DVAGDDR</sub>                                                                                                            | Data Valid After CLK                                | ECP3-150EA        | _        |        | _        |          | _       |        |       |  |

| f <sub>MAX_GDDR</sub>                                                                                                           | DDRX1 Clock Frequency                               | ECP3-150EA        | _        |        | _        |          | _       |        |       |  |

# LatticeECP3 External Switching Characteristics (Continued)<sup>1, 2</sup>

**Over Recommended Commercial Operating Conditions**

|                                                                                                   |                                                   |                    | -       | 8       | -      | 7        | -       | 6      |                 |

|---------------------------------------------------------------------------------------------------|---------------------------------------------------|--------------------|---------|---------|--------|----------|---------|--------|-----------------|

| Parameter                                                                                         | Description                                       | Device             | Min.    | Max.    | Min.   | Max.     | Min.    | Max.   | Units           |

| Generic DDRX2 Output with Clock and Data (> 10 Bits Wide) Aligned at Pin (GDDRX2_TX.ECLK.Aligned) |                                                   |                    |         |         |        |          |         |        |                 |

| Left and Right Si                                                                                 | des                                               |                    |         |         |        |          |         |        |                 |

| t <sub>DIBGDDR</sub>                                                                              | Data Setup Before CLK                             | ECP3-150EA         | _       |         | _      |          | _       |        | ps              |

| t <sub>DIAGDDR</sub>                                                                              | Data Hold After CLK                               | ECP3-150EA         | _       |         |        |          | _       |        | ps              |

| f <sub>MAX_GDDR</sub>                                                                             | DDRX2 Clock Frequency                             | ECP3-150EA         | _       |         | -      |          | _       |        | MHz             |

| Generic DDRX2 (GDDRX2_TX.Ali                                                                      | Outputs with Clock and Data Edges gned)           | Aligned, Without   | PLL 90  | -degree | shifte | d clock  | output  | 5      |                 |

| t <sub>DIBGDDR</sub>                                                                              | Data Invalid Before Clock                         | ECP3-70E/95E       |         | 200     | _      | 225      |         | 250    | ps              |

| t <sub>DIAGDDR</sub>                                                                              | Data Invalid After Clock                          | ECP3-70E/95E       | 1+1     | 200     | -<     | 225      | _       | 250    | ps              |

| f <sub>MAX_GDDR</sub>                                                                             | DDR/DDRX2 Clock Frequency8                        | ECP3-70E/95E       | ) 4     | 500     |        | 420      |         | 375    | MHz             |

| Generic DDRX2 (<br>DLL.Centered)                                                                  | Output with Clock and Data (> 10 B                | its Wide) Centered | at Pin  | Using I | DQSDL  | L (GDD   | RX2_T   | X.DQS  |                 |

| Left and Right Si                                                                                 | des                                               |                    |         | V       |        |          |         | >      |                 |

| t <sub>DVBGDDR</sub>                                                                              | Data Valid Before CLK                             | ECP3-150EA         |         |         |        |          | 1       | _      | ns              |

| t <sub>DVAGDDR</sub>                                                                              | Data Valid After CLK                              | ECP3-150EA         |         | _       |        | 1        |         | _      | ns              |

| f <sub>MAX_GDDR</sub>                                                                             | DDRX2 Clock Frequency                             | ECP3-150EA         |         |         | 1      |          | _       |        | ns              |

| Generic DDRX2                                                                                     | Output with Clock and Data (> 10 B                | its Wide) Centered | at Pin  | Using I | PLL (G | DDRX2    | _TX.PL  | L.Cent | ered)           |

| Left and Right Si                                                                                 | ides                                              |                    |         |         |        |          |         |        |                 |

| t <sub>DVBGDDR</sub>                                                                              | Data Valid Before CLK                             | ECP3-150EA         |         | 1       |        | _        |         | _      | ns              |

| t <sub>DVAGDDR</sub>                                                                              | Data Valid After CLK                              | ECP3-150EA         |         |         |        | _        |         | _      | ns              |

| f <sub>MAX_GDDR</sub>                                                                             | DDRX2 Clock Frequency                             | ECP3-150EA         |         |         | _      |          | _       |        | ns              |

| Generic DDRX2 (GDDRX2_TX.PL                                                                       | Outputs with Clock Edge in the Cer<br>L.Centered) | iter of Data Windo | w, with | PLL 90  | -degre | e Shifte | ed Cloc | k Outp | ut <sup>6</sup> |

| t <sub>DVBGDDR</sub>                                                                              | Data Valid Before CLK                             | ECP3-70E/95E       | 300     |         | 370    |          | 417     | _      | ps              |

| t <sub>DVAGDDR</sub>                                                                              | Data Valid After CLK                              | ECP3-70E/95E       | 300     | _       | 370    | _        | 417     | _      | ps              |

| f <sub>MAX_GDDR</sub>                                                                             | DDR/DDRX2 Clock Frequency8                        | ECP3-70E/95E       | _       | 500     | _      | 420      | _       | 375    | MHz             |

|                                                                                                   |                                                   |                    | ·       | •       | •      | •        | •       |        |                 |

|                       |                                     |                   | -      | 8      | -      | 7      | -      | 6      |                  |

|-----------------------|-------------------------------------|-------------------|--------|--------|--------|--------|--------|--------|------------------|

| Parameter             | Description                         | Device            | Min.   | Max.   | Min.   | Max.   | Min.   | Max.   | Units            |

| Memory Interfac       | ce                                  | · •               | l      |        |        |        | ı      |        |                  |

| DDR/DDR2 SDR          | AM I/O Pin Parameters (Input Data a | re Strobe Edge Al | igned, | Output | Strobe | Edge i | s Data | Center | ed) <sup>4</sup> |

| t <sub>DVADQ</sub>    | Data Valid After DQS (DDR Read)     | ECP3-150EA        | _      | 0.225  | _      | 0.225  | _      | 0.225  | UI               |

| t <sub>DVEDQ</sub>    | Data Hold After DQS (DDR Read)      | ECP3-150EA        | 0.64   | _      | 0.64   | _      | 0.64   | _      | UI               |

| t <sub>DQVBS</sub>    | Data Valid Before DQS               | ECP3-150EA        | 0.25   | _      | 0.25   | _      | 0.25   | _      | UI               |

| t <sub>DQVAS</sub>    | Data Valid After DQS                | ECP3-150EA        | 0.25   | _      | 0.25   | _      | 0.25   | _      | UI               |

| f <sub>MAX_DDR</sub>  | DDR Clock Frequency                 | ECP3-150EA        | 95     | 200    | 95     | 200    | 95     | 166    | MHz              |

| f <sub>MAX_DDR2</sub> | DDR2 clock frequency                | ECP3-150EA        | 133    | 266    | 133    | 200    | 133    | 166    | MHz              |

| t <sub>DVADQ</sub>    | Data Valid After DQS (DDR Read)     | ECP3-70E/95E      | _      | 0.225  | _      | 0.225  | _      | 0.225  | UI               |

| t <sub>DVEDQ</sub>    | Data Hold After DQS (DDR Read)      | ECP3-70E/95E      | 0.64   | _      | 0.64   | _      | 0.64   | _      | UI               |

| t <sub>DQVBS</sub>    | Data Valid Before DQS               | ECP3-70E/95E      | 0.25   | _      | 0.25   | _      | 0.25   | _      | UI               |

| t <sub>DQVAS</sub>    | Data Valid After DQS                | ECP3-70E/95E      | 0.25   | _      | 0.25   | _      | 0.25   | _      | UI               |

| f <sub>MAX_DDR</sub>  | DDR Clock Frequency                 | ECP3-70E/95E      | 95     | 200    | 95     | 200    | 95     | 133    | MHz              |

CLKA CSA WEA Three consecultive writes to A0 ADA Á0 A0 t<sub>SU</sub> t<sub>H</sub> Dο DΪ DIA tACCESS tACCESS TACCESS tACCESS Data from Prev Read Þο DOA D2 D4 or Write

Figure 3-11. Write Through (SP Read/Write on Port A, Input Registers Only)

Note: Input data and address are registered at the positive edge of the clock and output data appears after the positive edge of the clock.

# **DLL Timing**

## **Over Recommended Operating Conditions**

| Parameter                       | Description                                                                                    | Condition              | Min. | Тур.           | Max.   | Units  |

|---------------------------------|------------------------------------------------------------------------------------------------|------------------------|------|----------------|--------|--------|

| f <sub>REF</sub>                | Input reference clock frequency (on-chip or off-chip)                                          |                        | 133  | _              | 500    | MHz    |

| f <sub>FB</sub>                 | Feedback clock frequency (on-chip or off-chip)                                                 |                        | 133  | _              | 500    | MHz    |

| f <sub>CLKOP</sub> <sup>1</sup> | Output clock frequency, CLKOP                                                                  |                        | 133  | _              | 500    | MHz    |

| f <sub>CLKOS</sub> <sup>2</sup> | Output clock frequency, CLKOS                                                                  |                        | 33.3 | _              | 500    | MHz    |

| t <sub>PJIT</sub>               | Output clock period jitter (clean input)                                                       |                        |      | _              | 200    | ps p-p |

| _                               | Output clock duty cycle (at 50% levels, 50% duty                                               | Edge Clock             | 40   |                | 60     | %      |

| t <sub>DUTY</sub>               | cycle input clock, 50% duty cycle circuit turned off, time reference delay mode)               | Primary Clock          | 30   |                | 70     | %      |

|                                 | Output clock duty cycle (at 50% levels, arbitrary                                              | Primary Clock < 250MHz | 45   |                | 55     | %      |

| t <sub>DUTYTRD</sub>            | duty cycle input clock, 50% duty cycle circuit                                                 | Primary Clock ≥ 250MHz | 30   |                | 70     | %      |

|                                 | enabled, time reference delay mode)                                                            | Edge Clock             | 45   |                | 55     | %      |

|                                 | Output clock duty cycle (at 50% levels, arbitrary                                              | Primary Clock < 250MHz | 40   |                | 60     | %      |

| t <sub>DUTYCIR</sub>            | duty cycle input clock, 50% duty cycle circuit enabled, clock injection removal mode) with DLL | Primary Clock ≥ 250MHz | 30   |                | 70     | %      |

|                                 | cascading                                                                                      | Edge Clock             | 45   |                | 55     | %      |

| t <sub>SKEW</sub> <sup>3</sup>  | Output clock to clock skew between two outputs with the same phase setting                     |                        |      | \ <del>-</del> | 100    | ps     |

| t <sub>PHASE</sub>              | Phase error measured at device pads between off-chip reference clock and feedback clocks       | 18/ 0                  |      | _              | +/-400 | ps     |

| t <sub>PWH</sub>                | Input clock minimum pulse width high (at 80% level)                                            |                        | 550  | _              | _      | ps     |

| t <sub>PWL</sub>                | Input clock minimum pulse width low (at 20% level)                                             | 7,0                    | 550  | _              | _      | ps     |

| t <sub>INSTB</sub>              | Input clock period jitter                                                                      |                        |      | _              | 500    | р-р    |

| t <sub>LOCK</sub>               | DLL lock time                                                                                  |                        | 8    | _              | 8200   | cycles |

| t <sub>RSWD</sub>               | Digital reset minimum pulse width (at 80% level)                                               |                        | 3    |                |        | ns     |

| t <sub>DEL</sub>                | Delay step size                                                                                |                        | 27   | 45             | 70     | ps     |

| t <sub>RANGE1</sub>             | Max. delay setting for single delay block (64 taps)                                            |                        | 1.9  | 3.1            | 4.4    | ns     |

| t <sub>RANGE4</sub>             | Max. delay setting for four chained delay blocks                                               |                        | 7.6  | 12.4           | 17.6   | ns     |

CLKOP runs at the same frequency as the input clock.

CLKOS minimum frequency is obtained with divide by 4.

<sup>3.</sup> This is intended to be a "path-matching" design guideline and is not a measurable specification.

# Gigabit Ethernet/Serial Rapid I/O Type 1/SGMII Electrical and Timing Characteristics

#### **AC and DC Characteristics**

## Table 3-17. Transmit

| Symbol                                   | Description                      | Test Conditions | Min. | Тур. | Max. | Units |

|------------------------------------------|----------------------------------|-----------------|------|------|------|-------|

| T <sub>RF</sub>                          | Differential rise/fall time      | 20%-80%         | _    | 80   | _    | ps    |

| Z <sub>TX_DIFF_DC</sub>                  | Differential impedance           |                 | 80   | 100  | 120  | Ohms  |

| J <sub>TX_DDJ</sub> <sup>3, 4, 5</sup>   | Output data deterministic jitter |                 |      | 1    | 0.10 | UI    |

| J <sub>TX_TJ</sub> <sup>2, 3, 4, 5</sup> | Total output data jitter         |                 | /- V | _    | 0.24 | UI    |

- 1. Rise and fall times measured with board trace, connector and approximately 2.5pf load.

- 2. Total jitter includes both deterministic jitter and random jitter. The random jitter is the total jitter minus the actual deterministic jitter.

- 3. Jitter values are measured with each CML output AC coupled into a 50-ohm impedance (100-ohm differential impedance).

- 4. Jitter and skew are specified between differential crossings of the 50% threshold of the reference signal.

- 5. Values are measured at 1.25 Gbps.

#### Table 3-18. Receive and Jitter Tolerance

| Symbol                                      | Description                                   | Test Conditions          | Min. | Тур.       | Max. | Units |

|---------------------------------------------|-----------------------------------------------|--------------------------|------|------------|------|-------|

| RL <sub>RX_DIFF</sub>                       | Differential return loss                      | From 100 MHz to 1.25 GHz | 10   |            | _    | dB    |

| RL <sub>RX_CM</sub>                         | Common mode return loss                       | From 100 MHz to 1.25 GHz | 6    | \ <u> </u> | _    | dB    |

| Z <sub>RX_DIFF</sub>                        | Differential termination resistance           |                          | 80   | 100        | 120  | Ohms  |

|                                             | Deterministic jitter tolerance (peak-to-peak) |                          | 7    | _          | 0.34 | UI    |

|                                             | Random jitter tolerance (peak-to-peak)        |                          |      | _          | 0.26 | UI    |

|                                             | Sinusoidal jitter tolerance (peak-to-peak)    |                          | _    | _          | 0.11 | UI    |

| J <sub>RX_TJ</sub> <sup>1, 2, 3, 4, 5</sup> | Total jitter tolerance (peak-to-peak)         |                          | _    | _          | 0.71 | UI    |

| T <sub>RX EYE</sub>                         | Receiver eye opening                          |                          | 0.29 | _          | _    | UI    |

- 1. Total jitter includes deterministic jitter, random jitter and sinusoidal jitter. The sinusoidal jitter tolerance mask is shown in Figure 3-14.

- 2. Jitter values are measured with each high-speed input AC coupled into a 50-ohm impedance.

- 3. Jitter and skew are specified between differential crossings of the 50% threshold of the reference signal.

- 4. Jitter tolerance, Differential Input Sensitivity and Receiver Eye Opening parameters are characterized when Full Rx Equalization is enabled.

- 5. Values are measured at 1.25 Gbps.

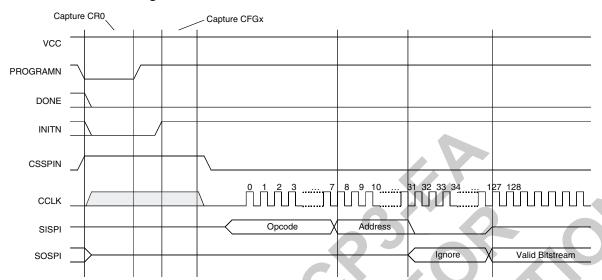

Figure 3-24. Master SPI Configuration Waveforms

## Point-to-Point LVDS (PPLVDS)

## **Over Recommended Operating Conditions**

| Description                   | Min. | Тур. | Max. | Units |

|-------------------------------|------|------|------|-------|

| Output driver supply (+/- 5%) | 3.14 | 3.3  | 3.47 | V     |

| Output driver supply (+/- 5%) | 2.25 | 2.5  | 2.75 | V     |

| Input differential voltage    | 100  |      | 400  | mV    |

| Input common mode voltage     | 0.2  |      | 2.3  | V     |

| Output differential voltage   | 130  |      | 400  | mV    |

| Output common mode voltage    | 0.5  | 0.8  | 1.4  | V     |

## **RSDS**

## **Over Recommended Operating Conditions**

| Parameter Symbol   | Description                                             | Min. | Тур. | Max.          | Units |

|--------------------|---------------------------------------------------------|------|------|---------------|-------|

| V <sub>OD</sub>    | Output voltage, differential, R <sub>T</sub> = 100 ohms | 100  | 200  | 600           | mV    |

| V <sub>OS</sub>    | Output voltage, common mode                             | 0.5  | 1.2  | 1.5           | V     |

| I <sub>RSDS</sub>  | Differential driver output current                      | 1    | 2    | 6             | mA    |

| $V_{THD}$          | Input voltage differential                              | 100  | _    | _             | mV    |

| V <sub>CM</sub>    | Input common mode voltage                               | 0.3  |      | 1.5           | V     |

| $T_R$ , $T_F$      | Output rise and fall times, 20% to 80%                  | _    | 500  | <b>&gt;</b> – | ps    |

| T <sub>ODUTY</sub> | Output clock duty cycle                                 | 35   | 50   | 65            | %     |

Note: Data is for 2mA drive. Other differential driver current options are available.

# LatticeECP3 Family Data Sheet Ordering Information

March 2010 Preliminary Data Sheet DS1021

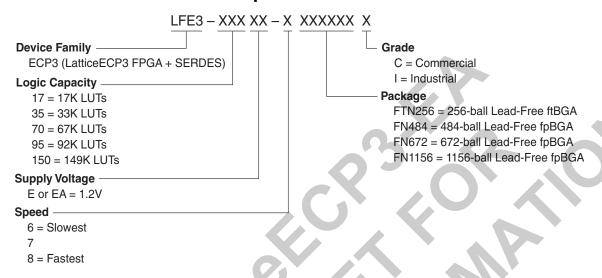

## **LatticeECP3 Part Number Description**

# **Ordering Information**

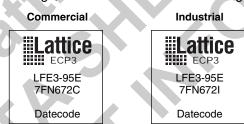

LatticeECP3 devices have top-side markings, for commercial and industrial grades, as shown below:

## Industrial

The following devices may have associated errata. Specific devices with associated errata will be notated with a footnote.

| Part Number        | Voltage | Grade | Package         | Pins | Temp. | LUTs (K) |

|--------------------|---------|-------|-----------------|------|-------|----------|

| LFE3-17EA-6FTN256I | 1.2V    | -6    | Lead-Free ftBGA | 256  | IND   | 17       |

| LFE3-17EA-7FTN256I | 1.2V    | -7    | Lead-Free ftBGA | 256  | IND   | 17       |

| LFE3-17EA-8FTN256I | 1.2V    | -8    | Lead-Free ftBGA | 256  | IND   | 17       |

| LFE3-17EA-6FN484I  | 1.2V    | -6    | Lead-Free fpBGA | 484  | IND   | 17       |

| LFE3-17EA-7FN484I  | 1.2V    | -7    | Lead-Free fpBGA | 484  | IND   | 17       |

| LFE3-17EA-8FN484I  | 1.2V    | -8    | Lead-Free fpBGA | 484  | IND   | 17       |

| Part Number        | Voltage | Grade | Package         | Pins | Temp. | LUTs (K) |

|--------------------|---------|-------|-----------------|------|-------|----------|

| LFE3-35EA-6FTN256I | 1.2V    | -6    | Lead-Free ftBGA | 256  | IND   | 33       |

| LFE3-35EA-7FTN256I | 1.2V    | -7    | Lead-Free ftBGA | 256  | IND   | 33       |

| LFE3-35EA-8FTN256I | 1.2V    | -8    | Lead-Free ftBGA | 256  | IND   | 33       |

| LFE3-35EA-6FN484I  | 1.2V    | -6    | Lead-Free fpBGA | 484  | IND   | 33       |

| LFE3-35EA-7FN484I  | 1.2V    | -7    | Lead-Free fpBGA | 484  | IND   | 33       |

| LFE3-35EA-8FN484I  | 1.2V    | -8    | Lead-Free fpBGA | 484  | IND   | 33       |

| LFE3-35EA-6FN672I  | 1.2V    | -6    | Lead-Free fpBGA | 672  | IND   | 33       |

| LFE3-35EA-7FN672I  | 1.2V    | -7    | Lead-Free fpBGA | 672  | IND   | 33       |

| LFE3-35EA-8FN672I  | 1.2V    | -7    | Lead-Free fpBGA | 672  | IND   | 33       |

| Part Number        | Voltage | Grade | Package         | Pins | Temp. | LUTs (K) |

|--------------------|---------|-------|-----------------|------|-------|----------|

| LFE3-70EA-6FN484I  | 1.2V    | -6    | Lead-Free fpBGA | 484  | IND   | 67       |

| LFE3-70EA-7FN484I  | 1.2V    | -7    | Lead-Free fpBGA | 484  | IND   | 67       |

| LFE3-70EA-8FN484I  | 1.2V    | -8    | Lead-Free fpBGA | 484  | IND   | 67       |

| LFE3-70EA-6FN672I  | 1.2V    | -6    | Lead-Free fpBGA | 672  | IND   | 67       |

| LFE3-70EA-7FN672I  | 1.2V    | -7    | Lead-Free fpBGA | 672  | IND   | 67       |

| LFE3-70EA-8FN672I  | 1.2V    | -8    | Lead-Free fpBGA | 672  | IND   | 67       |

| LFE3-70EA-6FN1156I | 1.2V    | -6    | Lead-Free fpBGA | 1156 | IND   | 67       |

| LFE3-70EA-7FN1156I | 1.2V    | -7    | Lead-Free fpBGA | 1156 | IND   | 67       |

| LFE3-70EA-8FN1156I | 1.2V    | -8    | Lead-Free fpBGA | 1156 | IND   | 67       |

# LatticeECP3 Family Data Sheet Supplemental Information

February 2009

**Preliminary Data Sheet DS1021**

## For Further Information

A variety of technical notes for the LatticeECP3 family are available on the Lattice website at www.latticesemi.com.

- TN1169, LatticeECP3 sysCONFIG Usage Guide

- TN1176, LatticeECP3 SERDES/PCS Usage Guide

- TN1177, LatticeECP3 sysIO Usage Guide

- TN1178, LatticeECP3 sysCLOCK PLL/DLL Design and Usage Guide

- TN1179, LatticeECP3 Memory Usage Guide

- TN1180, LatticeECP3 High-Speed I/O Interface

- TN1181, Power Consumption and Management for LatticeECP3 Devices

- TN1182, LatticeECP3 sysDSP Usage Guide

- TN1184, LatticeECP3 Soft Error Detection (SED) Usage Guide

- TN1189, LatticeECP3 Hardware Checklist

For further information on interface standards refer to the following websites:

- JEDEC Standards (LVTTL, LVCMOS, SSTL, HSTL): www.jedec.org

- PCI: www.pcisig.com