Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                                              |

|--------------------------------|------------------------------------------------------------------------------|

| Product Status                 | Obsolete                                                                     |

| Number of LABs/CLBs            | 8375                                                                         |

| Number of Logic Elements/Cells | 67000                                                                        |

| Total RAM Bits                 | 4526080                                                                      |

| Number of I/O                  | 490                                                                          |

| Number of Gates                | -                                                                            |

| Voltage - Supply               | 1.14V ~ 1.26V                                                                |

| Mounting Type                  | Surface Mount                                                                |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                                           |

| Package / Case                 | 1156-BBGA                                                                    |

| Supplier Device Package        | 1156-FPBGA (35x35)                                                           |

| Purchase URL                   | https://www.e-xfl.com/product-detail/lattice-semiconductor/lfe3-70e-8fn1156i |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

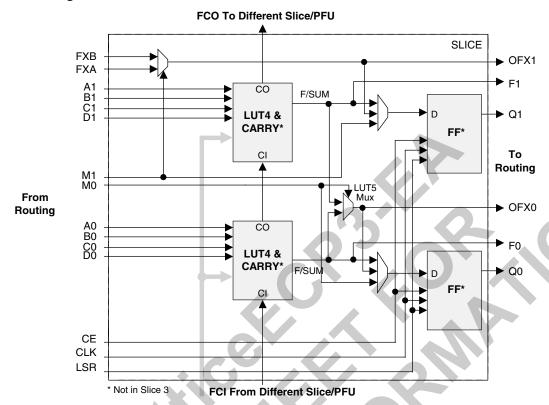

Figure 2-3. Slice Diagram

For Slices 0 and 1, memory control signals are generated from Slice 2 as follows:

WCK is CLK

WRE is from LSR

DI[3:2] for Slice 1 and DI[1:0] for Slice 0 data from Slice 2

WAD [A:D] is a 4-bit address from slice 2 LUT input

Table 2-2. Slice Signal Descriptions

| Function | Туре               | Signal Names   | Description                                                          |

|----------|--------------------|----------------|----------------------------------------------------------------------|

| Input    | Data signal        | A0, B0, C0, D0 | Inputs to LUT4                                                       |

| Input    | Data signal        | A1, B1, C1, D1 | Inputs to LUT4                                                       |

| Input    | Multi-purpose      | MO             | Multipurpose Input                                                   |

| Input    | Multi-purpose      | M1             | Multipurpose Input                                                   |

| Input    | Control signal     | CE             | Clock Enable                                                         |

| Input    | Control signal     | LSR            | Local Set/Reset                                                      |

| Input    | Control signal     | CLK            | System Clock                                                         |

| Input    | Inter-PFU signal   | FC             | Fast Carry-in <sup>1</sup>                                           |

| Input    | Inter-slice signal | FXA            | Intermediate signal to generate LUT6 and LUT7                        |

| Input    | Inter-slice signal | FXB            | Intermediate signal to generate LUT6 and LUT7                        |

| Output   | Data signals       | F0, F1         | LUT4 output register bypass signals                                  |

| Output   | Data signals       | Q0, Q1         | Register outputs                                                     |

| Output   | Data signals       | OFX0           | Output of a LUT5 MUX                                                 |

| Output   | Data signals       | OFX1           | Output of a LUT6, LUT7, LUT8 <sup>2</sup> MUX depending on the slice |

| Output   | Inter-PFU signal   | FCO            | Slice 2 of each PFU is the fast carry chain output <sup>1</sup>      |

<sup>1.</sup> See Figure 2-3 for connection details.

<sup>2.</sup> Requires two PFUs.

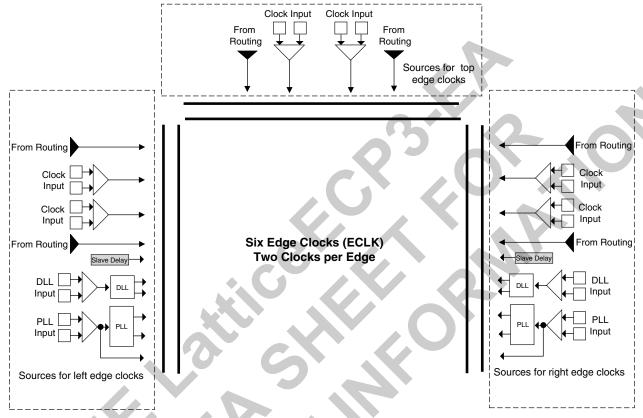

### **Edge Clock Sources**

Edge clock resources can be driven from a variety of sources at the same edge. Edge clock resources can be driven from adjacent edge clock PIOs, primary clock PIOs, PLLs, DLLs, Slave Delay and clock dividers as shown in Figure 2-19.

Figure 2-19. Edge Clock Sources

Notes:

- 1. Clock inputs can be configured in differential or single ended mode.

- 2. The two DLLs can also drive the two top edge clocks.

- 3. The top left and top right PLL can also drive the two top edge clocks.

### **Edge Clock Routing**

LatticeECP3 devices have a number of high-speed edge clocks that are intended for use with the PIOs in the implementation of high-speed interfaces. There are six edge clocks per device: two edge clocks on each of the top, left, and right edges. Different PLL and DLL outputs are routed to the two muxes on the left and right sides of the device. In addition, the CLKINDEL signal (generated from the DLL Slave Delay Line block) is routed to all the edge clock muxes on the left and right sides of the device. Figure 2-20 shows the selection muxes for these clocks.

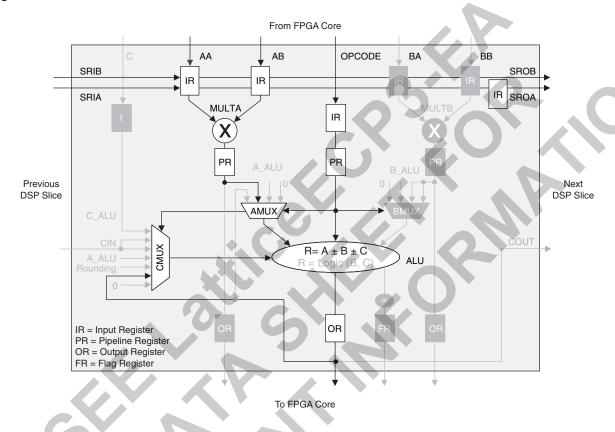

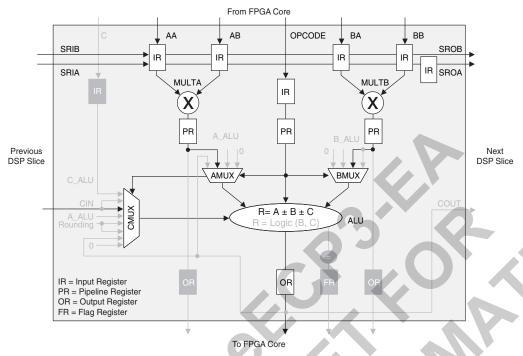

### **MAC DSP Element**

In this case, the two operands, AA and AB, are multiplied and the result is added with the previous accumulated value. This accumulated value is available at the output. The user can enable the input and pipeline registers, but the output register is always enabled. The output register is used to store the accumulated value. The ALU is configured as the accumulator in the sysDSP slice in the LatticeECP3 family can be initialized dynamically. A registered overflow signal is also available. The overflow conditions are provided later in this document. Figure 2-27 shows the MAC sysDSP element.

Figure 2-27. MAC DSP Element

Figure 2-31. MULTADDSUBSUM Slice 1

# **Advanced sysDSP Slice Features**

### Cascading

The LatticeECP3 sysDSP slice has been enhanced to allow cascading. Adder trees are implemented fully in sys-DSP slices, improving the performance. Cascading of slices uses the signals CIN, COUT and C Mux of the slice.

### **Addition**

The LatticeECP3 sysDSP slice allows for the bypassing of multipliers and cascading of adder logic. High performance adder functions are implemented without the use of LUTs. The maximum width adders that can be implemented are 54-bit.

#### Rounding

The rounding operation is implemented in the ALU and is done by adding a constant followed by a truncation operation. The rounding methods supported are:

- Rounding to zero (RTZ)

- · Rounding to infinity (RTI)

- · Dynamic rounding

- Random rounding

- Convergent rounding

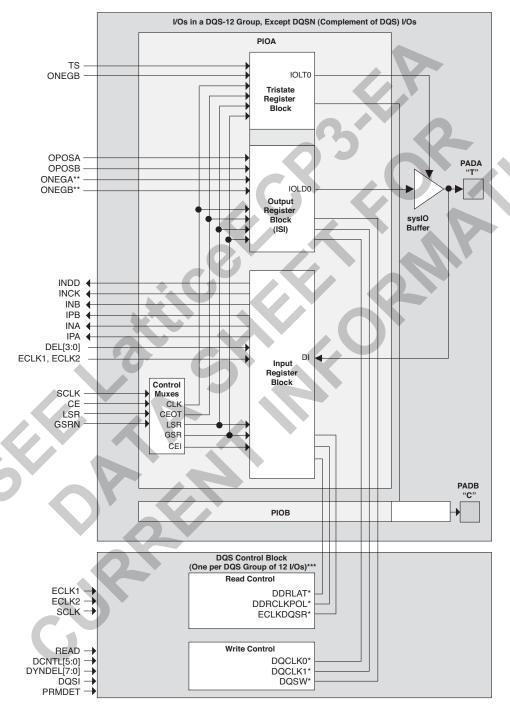

# Programmable I/O Cells (PIC)

Each PIC contains two PIOs connected to their respective sysl/O buffers as shown in Figure 2-32. The PIO Block supplies the output data (DO) and the tri-state control signal (TO) to the sysl/O buffer and receives input from the buffer. Table 2-11 provides the PIO signal list.

Figure 2-32. PIC Diagram

<sup>\*</sup> Signals are available on left/right/top edges only.

<sup>\*\*</sup> Signals are available on the left and right sides only

\*\*\* Selected PIO.

Please see TN1177, LatticeECP3 sysIO Usage Guide for on-chip termination usage and value ranges.

### **Equalization Filter**

Equalization filtering is available for single-ended inputs on both true and complementary I/Os, and for differential inputs on the true I/Os on the left, right, and top sides. Equalization is required to compensate for the difficulty of sampling alternating logic transitions with a relatively slow slew rate. It is considered the most useful for the Input DDRX2 modes, used in DDR3 memory, LVDS, or TRLVDS signaling. Equalization filter acts as a tunable filter with settings to determine the level of correction. In the LatticeECP3 devices, there are four settings available: 0 (none), 1, 2 and 3. The default setting is 0. The equalization logic resides in the sysI/O buffers, the two bits of setting is set uniquely in each input IOLOGIC block. Therefore, each sysI/O can have a unique equalization setting within a DQS-12 group.

### **Hot Socketing**

LatticeECP3 devices have been carefully designed to ensure predictable behavior during power-up and power-down. During power-up and power-down sequences, the I/Os remain in tri-state until the power supply voltage is high enough to ensure reliable operation. In addition, leakage into I/O pins is controlled within specified limits. Please refer to the Hot Socketing Specifications in the DC and Switching Characteristics in this data sheet.

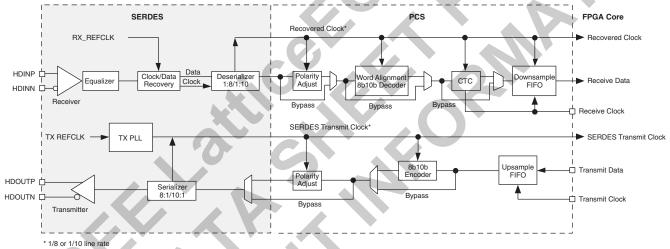

# **SERDES and PCS (Physical Coding Sublayer)**

LatticeECP3 devices feature up to 16 channels of embedded SERDES/PCS arranged in quads at the bottom of the devices supporting up to 3.2Gbps data rate. Figure 2-40 shows the position of the quad blocks for the LatticeECP3-150 devices. Table 2-14 shows the location of available SERDES Quads for all devices.

The LatticeECP3 SERDES/PCS supports a range of popular serial protocols, including:

- PCI Express 1.1

- Ethernet (XAUI, GbE 1000 Base CS/SX/LX and SGMII)

- · Serial RapidIO

- SMPTE SDI (3G, HD, SD)

- CPRI

- SONET/SDH (STS-3, STS-12, STS-48)

Each quad contains four dedicated SERDES for high speed, full duplex serial data transfer. Each quad also has a PCS block that interfaces to the SERDES channels and contains protocol specific digital logic to support the standards listed above. The PCS block also contains interface logic to the FPGA fabric. All PCS logic for dedicated protocol support can also be bypassed to allow raw 8-bit or 10-bit interfaces to the FPGA fabric.

Even though the SERDES/PCS blocks are arranged in quads, multiple baud rates can be supported within a quad with the use of dedicated, per channel ÷1, ÷2 and ÷11 rate dividers. Additionally, multiple quads can be arranged together to form larger data pipes.

For information on how to use the SERDES/PCS blocks to support specific protocols, as well on how to combine multiple protocols and baud rates within a device, please refer to TN1176, <u>LatticeECP3 SERDES/PCS Usage Guide</u>.

Table 2-14. Available SERDES Quads per LatticeECP3 Devices

| Package    | ECP3-17 | ECP3-35 | ECP3-70 | ECP3-95 | ECP3-150 |

|------------|---------|---------|---------|---------|----------|

| 256 ftBGA  | 1       | 1       | _       | _       | _        |

| 484 ftBGA  | 1       | 1       | 1       | 1       |          |

| 672 ftBGA  | _       | 1       | 2       | 2       | 2        |

| 1156 ftBGA | _       | _       | 3       | 3       | 4        |

#### **SERDES Block**

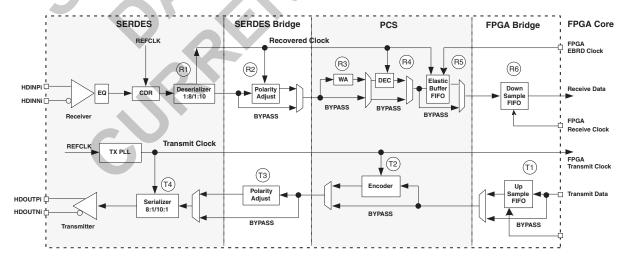

A SERDES receiver channel may receive the serial differential data stream, equalize the signal, perform Clock and Data Recovery (CDR) and de-serialize the data stream before passing the 8- or 10-bit data to the PCS logic. The SERDES transmitter channel may receive the parallel 8- or 10-bit data, serialize the data and transmit the serial bit stream through the differential drivers. Figure 2-41 shows a single-channel SERDES/PCS block. Each SERDES channel provides a recovered clock and a SERDES transmit clock to the PCS block and to the FPGA core logic.

Each transmit channel, receiver channel, and SERDES PLL shares the same power supply (VCCA). The output and input buffers of each channel have their own independent power supplies (VCCOB and VCCIB).

Figure 2-41. Simplified Channel Block Diagram for SERDES/PCS Block

#### **PCS**

As shown in Figure 2-41, the PCS receives the parallel digital data from the deserializer and selects the polarity, performs word alignment, decodes (8b/10b), provides Clock Tolerance Compensation and transfers the clock domain from the recovered clock to the FPGA clock via the Down Sample FIFO.

For the transmit channel, the PCS block receives the parallel data from the FPGA core, encodes it with 8b/10b, selects the polarity and passes the 8/10 bit data to the transmit SERDES channel.

The PCS also provides bypass modes that allow a direct 8-bit or 10-bit interface from the SERDES to the FPGA logic. The PCS interface to the FPGA can also be programmed to run at 1/2 speed for a 16-bit or 20-bit interface to the FPGA logic.

### SCI (SERDES Client Interface) Bus

The SERDES Client Interface (SCI) is an IP interface that allows the SERDES/PCS Quad block to be controlled by registers rather than the configuration memory cells. It is a simple register configuration interface that allows SERDES/PCS configuration without power cycling the device.

# SERDES Power Supply Requirements<sup>1, 2, 3</sup>

## **Over Recommended Operating Conditions**

| Symbol               | Description                            | Тур. | Max. | Units    |

|----------------------|----------------------------------------|------|------|----------|

| Standby (Power D     | Down)                                  | •    |      | <b>.</b> |

| I <sub>CCA-SB</sub>  | V <sub>CCA</sub> current (per channel) | 3    | 5    | mA       |

| I <sub>CCIB-SB</sub> | Input buffer current (per channel)     | _    | _    | mA       |

| I <sub>CCOB-SB</sub> | Output buffer current (per channel)    | _    | _    | mA       |

| Operating (Data F    | Rate = 3.2 Gbps)                       |      |      |          |

| I <sub>CCA-OP</sub>  | V <sub>CCA</sub> current (per channel) | 68   | 77   | mA       |

| I <sub>CCIB-OP</sub> | Input buffer current (per channel)     | 5    | 7    | mA       |

| I <sub>CCOB-OP</sub> | Output buffer current (per channel)    | 19   | 25   | mA       |

| Operating (Data F    | Rate = 2.5 Gbps)                       | 0-/- |      |          |

| I <sub>CCA-OP</sub>  | V <sub>CCA</sub> current (per channel) | 66   | 76   | mA       |

| I <sub>CCIB-OP</sub> | Input buffer current (per channel)     | 4    | 5    | mA       |

| I <sub>CCOB-OP</sub> | Output buffer current (per channel)    | 15   | 18   | mA       |

| Operating (Data F    | Rate = 1.25 Gbps)                      |      |      |          |

| I <sub>CCA-OP</sub>  | V <sub>CCA</sub> current (per channel) | 62   | 72   | mA       |

| I <sub>CCIB-OP</sub> | Input buffer current (per channel)     | 4    | 5    | mA       |

| I <sub>CCOB-OP</sub> | Output buffer current (per channel)    | 15   | 18   | mA       |

| Operating (Data F    | Rate = 250 Mbps)                       |      |      | •        |

| I <sub>CCA-OP</sub>  | V <sub>CCA</sub> current (per channel) | 55   | 65   | mA       |

| I <sub>CCIB-OP</sub> | Input buffer current (per channel)     | 4    | 5    | mA       |

| I <sub>CCOB-OP</sub> | Output buffer current (per channel)    | 14   | 17   | mA       |

Equalization enabled, pre-emphasis disabled.

<sup>2.</sup> One quarter of the total quad power (includes contribution from common circuits, all channels in the quad operating, pre-emphasis disabled, equalization enabled).

<sup>3.</sup> Pre-emphasis adds 20mA to ICCA-OP data.

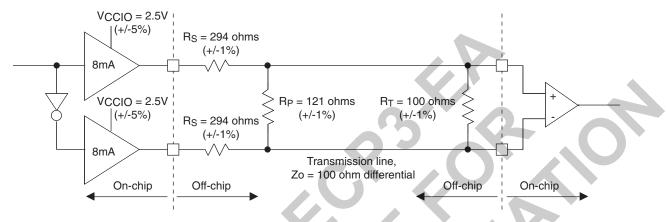

#### RSDS25E

The LatticeECP3 devices support differential RSDS and RSDSE standards. This standard is emulated using complementary LVCMOS outputs in conjunction with a parallel resistor across the driver outputs. The RSDS input standard is supported by the LVDS differential input buffer. The scheme shown in Figure 3-4 is one possible solution for RSDS standard implementation. Resistor values in Figure 3-4 are industry standard values for 1% resistors.

Figure 3-4. RSDS25E (Reduced Swing Differential Signaling)

Table 3-4. RSDS25E DC Conditions1

### **Over Recommended Operating Conditions**

| Parameter         | Description                      | Typical | Units |

|-------------------|----------------------------------|---------|-------|

| V <sub>CCIO</sub> | Output Driver Supply (+/-5%)     | 2.50    | V     |

| Z <sub>OUT</sub>  | Driver Impedance                 | 20      | Ω     |

| $R_S$             | Driver Series Resistor (+/-1%)   | 294     | Ω     |

| R <sub>P</sub>    | Driver Parallel Resistor (+/-1%) | 121     | Ω     |

| R <sub>T</sub>    | Receiver Termination (+/-1%)     | 100     | Ω     |

| V <sub>OH</sub>   | Output High Voltage              | 1.35    | V     |

| V <sub>OL</sub>   | Output Low Voltage               | 1.15    | V     |

| V <sub>OD</sub>   | Output Differential Voltage      | 0.20    | V     |

| $V_{CM}$          | Output Common Mode Voltage       | 1.25    | V     |

| Z <sub>BACK</sub> | Back Impedance                   | 101.5   | Ω     |

| I <sub>DC</sub>   | DC Output Current                | 3.66    | mA    |

<sup>1.</sup> For input buffer, see LVDS table.

# LatticeECP3 External Switching Characteristics 1,2

# **Over Recommended Commercial Operating Conditions**

|                            |                                              |              | -    | 8    | -        | 7    | -    | 6    |       |

|----------------------------|----------------------------------------------|--------------|------|------|----------|------|------|------|-------|

| Parameter                  | Description                                  | Device       | Min. | Max. | Min.     | Max. | Min. | Max. | Units |

| Clocks                     |                                              |              | •    |      | •        | •    | •    | •    |       |

| Primary Clock <sup>6</sup> |                                              |              |      |      |          |      |      |      |       |

| f <sub>MAX_PRI</sub>       | Frequency for Primary Clock Tree             | ECP3-150EA   | _    | 500  | _        | 420  | _    | 375  | MHz   |

| t <sub>W_PRI</sub>         | Clock Pulse Width for Primary Clock          | ECP3-150EA   | 0.8  |      | 0.9      | >-   | 1.0  | _    | ns    |

| t <sub>SKEW_PRI</sub>      | Primary Clock Skew Within a Device           | ECP3-150EA   |      | 300  | +        | 330  | _    | 360  | ps    |

| t <sub>SKEW_PRIB</sub>     | Primary Clock Skew Within a Bank             | ECP3-150EA   | _    | 250  | <b>/</b> | 280  | _    | 300  | ps    |

| t <sub>W_PRI</sub>         | Frequency for Primary Clock Tree             | ECP3-70E/95E | 6    | 500  | _        | 420  | _    | 375  | MHz   |

| f <sub>MAX_PRI</sub>       | Frequency for Primary Clock Tree             | ECP3-70E/95E | 0.8  | _    | 0.9      | 4    | 1.0  |      | ns    |

| t <sub>SKEW_PRI</sub>      | Primary Clock Skew Within a Device           | ECP3-70E/95E |      | 300  |          | 330  |      | 360  | ps    |

| t <sub>SKEW_PRIB</sub>     | Primary Clock Skew Within a Bank             | ECP3-70E/95E | _    | 250  |          | 280  | -    | 300  | ps    |

| Edge Clock <sup>6</sup>    |                                              | . (1)        |      |      |          |      |      |      |       |

| f <sub>MAX_EDGE</sub>      | Frequency for Edge Clock                     | ECP3-150EA   | _    | 500  | _        | 420  |      | 375  | MHz   |

| t <sub>W_EDGE</sub>        | Clock Pulse Width for Edge Clock             | ECP3-150EA   | 0.9  |      | 1.0      | 4    | 1.2  | _    | ns    |

| t <sub>SKEW_EDGE_DQS</sub> | Edge Clock Skew Within an Edge of the Device | ECP3-150EA   |      | 200  | 4        | 210  | _    | 220  | ps    |

| f <sub>MAX_EDGE</sub>      | Frequency for Edge Clock                     | ECP3-70E/95E | _    | 500  |          | 420  | _    | 375  | MHz   |

| t <sub>W_EDGE</sub>        | Clock Pulse Width for Edge Clock             | ECP3-70E/95E | 0.9  | -    | 1.0      | _    | 1.2  | _    | ns    |

| t <sub>SKEW_EDGE_DQS</sub> | Edge Clock Skew Within an Edge of the Device | ECP3-70E/95E | (    | 200  | _        | 225  | _    | 250  | ps    |

|                     |                                                                |                  |        | ·8      | -    | 7    | -    | 6    |       |

|---------------------|----------------------------------------------------------------|------------------|--------|---------|------|------|------|------|-------|

| Parameter           | Description                                                    | Device           | Min.   | Max.    | Min. | Max. | Min. | Max. | Units |

| Generic SDR         |                                                                |                  |        |         | •    | •    |      |      |       |

| General I/O Pin     | Parameters Using Dedicated Clock In                            | out Primary Cloc | k With | out PLL | 2    |      |      |      |       |

| t <sub>CO</sub>     | Clock to Output - PIO Output Register                          |                  | _      | 4.0     | _    | 4.4  | _    | 4.8  | ns    |

| tsu                 | Clock to Data Setup - PIO Input Register                       | ECP3-150EA       | 0.0    | _       | 0.0  | _    | 0.0  | _    | ns    |

| t <sub>H</sub>      | Clock to Data Hold - PIO Input Register                        | ECP3-150EA       | 1.6    | _       | 1.8  | _    | 2.1  | _    | ns    |

| t <sub>SU_DEL</sub> | Clock to Data Setup - PIO Input Register with Data Input Delay | ECP3-150EA       | 1.2    | _       | 1.3  | _    | 1.5  | _    | ns    |

| t <sub>H_DEL</sub>  | Clock to Data Hold - PIO Input Register with Input Data Delay  | ECP3-150EA       | 0.1    | _       | 0.1  | _    | 0.1  | _    | ns    |

| f <sub>MAX_IO</sub> | Clock Frequency of I/O and PFU Register                        | ECP3-150EA       | _      | 500     | _    | 420  | _    | 375  | MHz   |

| t <sub>CO</sub>     | Clock to Output - PIO Output Register                          | ECP3-70E/95E     | _      | 3.9     | _    | 4.3  |      | 4.7  | ns    |

| t <sub>SU</sub>     | Clock to Data Setup - PIO Input Register                       | ECP3-70E/95E     | 0.0    | _       | 0.0  | _    | 0.0  | _    | ns    |

| t <sub>H</sub>      | Clock to Data Hold - PIO Input Register                        | ECP3-70E/95E     | 1.5    | _       | 1.8  | _    | 2.0  | _    | ns    |

| t <sub>SU_DEL</sub> | Clock to Data Setup - PIO Input Register with Data Input Delay | ECP3-70E/95E     | 1.3    | _       | 1.5  | _    | 1.8  | _    | ns    |

| t <sub>H_DEL</sub>  | Clock to Data Hold - PIO Input Register with Input Data Delay  | ECP3-70E/95E     | 0.0    | _       | 0.0  | _    | 0.0  | _    | ns    |

# LatticeECP3 Internal Switching Characteristics<sup>1, 2</sup> (Continued)

# **Over Recommended Commercial Operating Conditions**

|                         |                                                        | -        | 8    | -      | 7    | -      | 6    |        |

|-------------------------|--------------------------------------------------------|----------|------|--------|------|--------|------|--------|

| Parameter               | Description                                            | Min.     | Max. | Min.   | Max. | Min.   | Max. | Units. |

| t <sub>HWREN_EBR</sub>  | Hold Write/Read Enable to PFU Memory                   | 0.141    | _    | 0.145  | _    | 0.149  | _    | ns     |

| t <sub>SUCE_EBR</sub>   | Clock Enable Setup Time to EBR Output<br>Register      | 0.087    |      | 0.096  |      | 0.104  |      | ns     |

| t <sub>HCE_EBR</sub>    | Clock Enable Hold Time to EBR Output<br>Register       | -0.066   |      | -0.080 |      | -0.094 |      | ns     |

| t <sub>SUBE_EBR</sub>   | Byte Enable Set-Up Time to EBR Output<br>Register      | -0.071   |      | -0.070 |      | -0.068 |      | ns     |

| t <sub>HBE_EBR</sub>    | Byte Enable Hold Time to EBR Output<br>Register        | 0.118    |      | 0.098  |      | 0.077  |      | ns     |

| DSP Block Tin           | ning <sup>3</sup>                                      |          |      |        |      |        |      |        |

| t <sub>SUI_DSP</sub>    | Input Register Setup Time                              | 0.32     |      | 0.36   | 7    | 0.39   |      | ns     |

| t <sub>HI_DSP</sub>     | Input Register Hold Time                               | -0.17    | K-   | -0.19  | 7    | -0.21  | 1    | ns     |

| t <sub>SUP_DSP</sub>    | Pipeline Register Setup Time                           | 2.23     | _    | 2.30   |      | 2.37   |      | ns     |

| t <sub>HP_DSP</sub>     | Pipeline Register Hold Time                            | -1.02    | _    | -1.09  | _    | -1.15  |      | ns     |

| t <sub>SUO_DSP</sub>    | Output Register Setup Time                             | 3.09     |      | 3.22   |      | 3.34   | _    | ns     |

| t <sub>HO_DSP</sub>     | Output Register Hold Time                              | -1.67    | V-   | -1.76  | -    | -1.84  | —    | ns     |

| t <sub>COI_DSP</sub>    | Input Register Clock to Output Time                    | -<       | 3.68 |        | 4.03 | _      | 4.38 | ns     |

| t <sub>COP_DSP</sub>    | Pipeline Register Clock to Output Time                 |          | 1.30 | -0     | 1.47 | _      | 1.64 | ns     |

| t <sub>COO_DSP</sub>    | Output Register Clock to Output Time                   | <b>(</b> | 0.58 | -7     | 0.60 | _      | 0.62 | ns     |

| t <sub>SUOPT_DSP</sub>  | Opcode Register Setup Time                             | 0.31     | - (  | 0.35   | _    | 0.39   | _    | ns     |

| t <sub>HOPT_DSP</sub>   | Opcode Register Hold Time                              | -0.20    |      | -0.24  | _    | -0.27  | _    | ns     |

| t <sub>SUDATA_DSP</sub> | Cascade_data through ALU to Output Register Setup Time | 1.55     | X    | 1.67   | _    | 1.78   | _    | ns     |

| t <sub>HPDATA_DSP</sub> | Cascade_data through ALU to Output Register Hold Time  | -0.44    |      | -0.53  | _    | -0.61  | _    | ns     |

<sup>1.</sup> Internal parameters are characterized but not tested on every device.

<sup>2.</sup> Commercial timing numbers are shown. Industrial timing numbers are typically slower and can be extracted from the ispLEVER software.

<sup>3.</sup> DSP slice is configured in Multiply Add/Sub 18x18 mode.

<sup>4.</sup> The output register is in Flip-flop mode.

# **SERDES/PCS Block Latency**

Table 3-8 describes the latency of each functional block in the transmitter and receiver. Latency is given in parallel clock cycles. Figure 3-12 shows the location of each block.

Table 3-8. SERDES/PCS Latency Breakdown

| Item    | Description                                          | Min.     | Avg.          | Max.          | Fixed   | Bypass        | Units    |

|---------|------------------------------------------------------|----------|---------------|---------------|---------|---------------|----------|

| Transmi | t Data Latency¹                                      |          |               |               | •       | •             |          |

|         | FPGA Bridge - Gearing disabled with different clocks | 1        | 3             | 5             | _       | 1             | word clk |

| T1      | FPGA Bridge - Gearing disabled with same clocks      | _        | _             | -             | 3       | 1             | word clk |

|         | FPGA Bridge - Gearing enabled                        | 1        | 3             | 5             | _       | _             | word clk |

| T2      | 8b10b Encoder                                        | _        | -             |               | 2       | 1             | word clk |

| T3      | SERDES Bridge transmit                               | _        |               | <b>X</b>      | 2       | 1             | word clk |

| T4      | Serializer: 8-bit mode                               | _        | 7-            | - 4           | 15 + ∆1 | _             | UI + ps  |

| 14      | Serializer: 10-bit mode                              | 70       |               |               | 18 + ∆1 | - C           | UI + ps  |

| T5      | Pre-emphasis ON                                      |          | _             | -             | 1 + Δ2  | 7-            | UI + ps  |

| 15      | Pre-emphasis OFF                                     |          | · — /         |               | 0 + Δ3  | 7-7           | UI + ps  |

| Receive | Data Latency <sup>2</sup>                            |          |               |               |         |               |          |

| R1      | Equalization ON                                      |          | _             | <b>&gt;</b> - | Δ1      | <b>&gt;</b> - | UI + ps  |

| n i     | Equalization OFF                                     |          | 7             |               | Δ2      | _             | UI + ps  |

| R2      | Deserializer: 8-bit mode                             |          |               | -             | 10 + ∆3 | _             | UI + ps  |

| ΠZ      | Deserializer: 10-bit mode                            | <b>/</b> |               |               | 12 + ∆3 | _             | UI + ps  |

| R3      | SERDES Bridge receive                                | <b>/</b> | _             | 1             | 2       | _             | word clk |

| R4      | Word alignment                                       | 3.1      | -             | 4             | —       | _             | word clk |

| R5      | 8b10b decoder                                        | \ -      | <i>&gt;</i> + | 7-            | 1       | _             | word clk |

| R6      | Clock Tolerance Compensation                         | 7        | 15            | 23            | 1       | 1             | word clk |

|         | FPGA Bridge - Gearing disabled with different clocks | 1        | 3             | 5             | _       | 1             | word clk |

| R7      | FPGA Bridge - Gearing disabled with same clocks      |          | <u> </u>      | _             | 3       | 1             | word clk |

|         | FPGA Bridge - Gearing enabled                        | 1        | 3             | 5             | _       | _             | word clk |

<sup>1.</sup>  $\Delta 1 = -245$ ps,  $\Delta 2 = +88$ ps,  $\Delta 3 = +112$ ps.

Figure 3-12. Transmitter and Receiver Latency Block Diagram

<sup>2.</sup>  $\Delta 1 = +118$ ps,  $\Delta 2 = +132$ ps,  $\Delta 3 = +700$ ps.

#### **SERDES External Reference Clock**

The external reference clock selection and its interface are a critical part of system applications for this product. Table 3-12 specifies reference clock requirements, over the full range of operating conditions.

Table 3-12. External Reference Clock Specification (refclkp/refclkn)

| Symbol                        | Description                                       | Min.  | Тур.     | Max.                   | Units                   |

|-------------------------------|---------------------------------------------------|-------|----------|------------------------|-------------------------|

| F <sub>REF</sub>              | Frequency range                                   | 15    | _        | 320                    | MHz                     |

| F <sub>REF-PPM</sub>          | Frequency tolerance <sup>4</sup>                  | -1000 | _        | 1000                   | ppm                     |

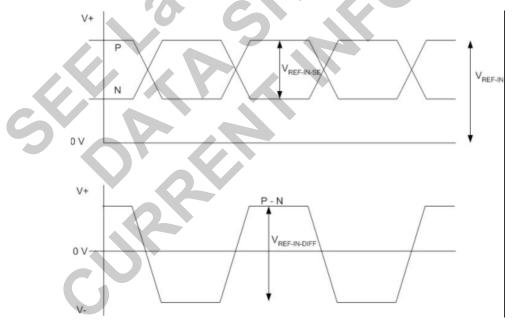

| V <sub>REF-IN-SE</sub>        | Input swing, single-ended clock <sup>1</sup>      | 200   | - 4      | V <sub>CCA</sub>       | mV, p-p                 |

| V <sub>REF-IN-DIFF</sub>      | Input swing, differential clock                   | 200   |          | 2*V <sub>CCA</sub>     | mV, p-p<br>differential |

| V <sub>REF-IN</sub>           | Input levels                                      | 0     |          | V <sub>CCA</sub> + 0.3 | V                       |

| V <sub>REF-CM-AC</sub>        | Input common mode range (AC coupled) <sup>2</sup> | 0.125 | <i>→</i> | V <sub>CCA</sub>       | V                       |

| D <sub>REF</sub>              | Duty cycle <sup>3</sup>                           | 40    | _        | 60                     | %                       |

| T <sub>REF-R</sub>            | Rise time (20% to 80%)                            | 200   | 500      | 1000                   | ps                      |

| T <sub>REF-F</sub>            | Fall time (80% to 20%)                            | 200   | 500      | 1000                   | ps                      |

| Z <sub>REF-IN-TERM-DIFF</sub> | Differential input termination                    | -20%  | 100/2K   | +20%                   | Ohms                    |

| C <sub>REF-IN-CAP</sub>       | Input capacitance                                 |       |          | 7                      | pF                      |

<sup>1.</sup> The signal swing for a single-ended input clock must be as large as the p-p differential swing of a differential input clock to get the same gain at the input receiver. Lower swings for the clock may be possible, but will tend to increase jitter.

Figure 3-13. SERDES External Reference Clock Waveforms

When AC coupled, the input common mode range is determined by: (Min input level) + (Peak-to-peak input swing)/2 ≤ (Input common mode voltage) ≤ (Max input level) - (Peak-to-peak input swing)/2

<sup>3.</sup> Measured at 50% amplitude.

<sup>4.</sup> Depending on the application, the PLL\_LOL\_SET and CDR\_LOL\_SET control registers may be adjusted for other tolerance values as described in TN1176, <u>LatticeECP3 SERDES/PCS Usage Guide</u>.

# Gigabit Ethernet/Serial Rapid I/O Type 1/SGMII Electrical and Timing Characteristics

#### **AC and DC Characteristics**

### Table 3-17. Transmit

| Symbol                                   | Description                      | Test Conditions | Min. | Тур. | Max. | Units |

|------------------------------------------|----------------------------------|-----------------|------|------|------|-------|

| T <sub>RF</sub>                          | Differential rise/fall time      | 20%-80%         | _    | 80   | _    | ps    |

| Z <sub>TX_DIFF_DC</sub>                  | Differential impedance           |                 | 80   | 100  | 120  | Ohms  |

| J <sub>TX_DDJ</sub> <sup>3, 4, 5</sup>   | Output data deterministic jitter |                 |      | 1    | 0.10 | UI    |

| J <sub>TX_TJ</sub> <sup>2, 3, 4, 5</sup> | Total output data jitter         |                 | /- V | _    | 0.24 | UI    |

- 1. Rise and fall times measured with board trace, connector and approximately 2.5pf load.

- 2. Total jitter includes both deterministic jitter and random jitter. The random jitter is the total jitter minus the actual deterministic jitter.

- 3. Jitter values are measured with each CML output AC coupled into a 50-ohm impedance (100-ohm differential impedance).

- 4. Jitter and skew are specified between differential crossings of the 50% threshold of the reference signal.

- 5. Values are measured at 1.25 Gbps.

#### Table 3-18. Receive and Jitter Tolerance

| Symbol                                      | Description                                   | Test Conditions          | Min. | Тур.      | Max. | Units |

|---------------------------------------------|-----------------------------------------------|--------------------------|------|-----------|------|-------|

| RL <sub>RX_DIFF</sub>                       | Differential return loss                      | From 100 MHz to 1.25 GHz | 10   |           | _    | dB    |

| RL <sub>RX_CM</sub>                         | Common mode return loss                       | From 100 MHz to 1.25 GHz | 6    | \ <u></u> | _    | dB    |

| Z <sub>RX_DIFF</sub>                        | Differential termination resistance           |                          | 80   | 100       | 120  | Ohms  |

|                                             | Deterministic jitter tolerance (peak-to-peak) |                          | 7    | _         | 0.34 | UI    |

|                                             | Random jitter tolerance (peak-to-peak)        |                          |      | _         | 0.26 | UI    |

|                                             | Sinusoidal jitter tolerance (peak-to-peak)    |                          | _    | _         | 0.11 | UI    |

| J <sub>RX_TJ</sub> <sup>1, 2, 3, 4, 5</sup> | Total jitter tolerance (peak-to-peak)         |                          | _    | —         | 0.71 | UI    |

| T <sub>RX EYE</sub>                         | Receiver eye opening                          |                          | 0.29 | _         | _    | UI    |

- 1. Total jitter includes deterministic jitter, random jitter and sinusoidal jitter. The sinusoidal jitter tolerance mask is shown in Figure 3-14.

- 2. Jitter values are measured with each high-speed input AC coupled into a 50-ohm impedance.

- 3. Jitter and skew are specified between differential crossings of the 50% threshold of the reference signal.

- 4. Jitter tolerance, Differential Input Sensitivity and Receiver Eye Opening parameters are characterized when Full Rx Equalization is enabled.

- 5. Values are measured at 1.25 Gbps.

# **LatticeECP3 sysCONFIG Port Timing Specifications (Continued)**

# **Over Recommended Operating Conditions**

| Parameter         | Description                              | Min. | Max. | Units |  |  |  |

|-------------------|------------------------------------------|------|------|-------|--|--|--|

| t <sub>CHHH</sub> | HOLDN Low Hold Time (Relative to CCLK)   | 5    | _    | ns    |  |  |  |

| Master and        | Master and Slave SPI (Continued)         |      |      |       |  |  |  |

| t <sub>CHHL</sub> | HOLDN High Hold Time (Relative to CCLK)  | 5    |      | ns    |  |  |  |

| t <sub>HHCH</sub> | HOLDN High Setup Time (Relative to CCLK) | 5    | _    | ns    |  |  |  |

| t <sub>HLQZ</sub> | HOLDN to Output High-Z                   | _    | 9    | ns    |  |  |  |

| t <sub>HHQX</sub> | HOLDN to Output Low-Z                    | _    | 9    | ns    |  |  |  |

| Parameter              | Min.                 | Max.                 | Units |

|------------------------|----------------------|----------------------|-------|

| Master Clock Frequency | Selected value - 15% | Selected value + 15% | MHz   |

| Duty Cycle             | 40                   | 60                   | %     |

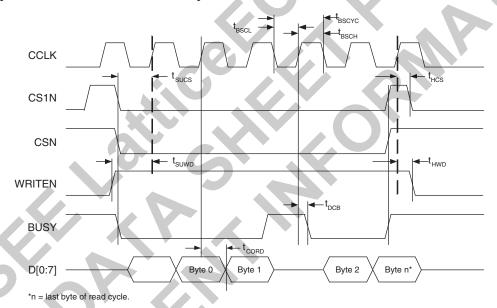

Figure 3-16. sysCONFIG Parallel Port Read Cycle

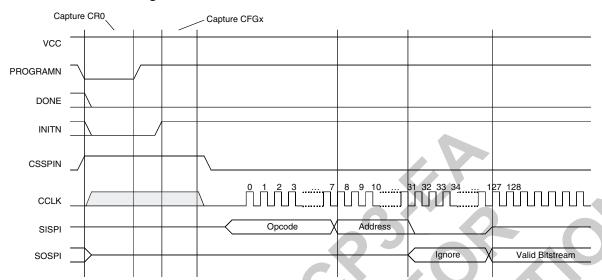

Figure 3-24. Master SPI Configuration Waveforms

# **Pin Information Summary (Cont.)**

| Pin Informati                        |                      | ECP3-70E  |               | ECP3-70EA |           |               |       |

|--------------------------------------|----------------------|-----------|---------------|-----------|-----------|---------------|-------|

| Pin <sup>-</sup>                     | 484 fpBGA            | 672 fpBGA | 1156<br>fpBGA | 484 fpBGA | 672 fpBGA | 1156<br>fpBGA |       |

|                                      | Bank 0               | 21        | 30            | 43        | 21        | 30            | 43    |

|                                      | Bank 1               | 18        | 24            | 39        | 18        | 24            | 39    |

| Facilities of Differential           | Bank 2               | 10        | 15            | 16        | 8         | 12            | 13    |

| Emulated Differential I/O per Bank   | Bank 3               | 23        | 27            | 39        | 20        | 23            | 33    |

| n o por Barne                        | Bank 6               | 26        | 30            | 39        | 22        | 25            | 33    |

|                                      | Bank 7               | 14        | 20            | 22        | 11        | 16            | 18    |

|                                      | Bank 8               | 12        | 12            | 12        | 12        | 12            | 12    |

|                                      | Bank 0               | 0         | 0             | 0         | 0         | 0             | 0     |

|                                      | Bank 1               | 0         | 0             | 0         | 0         | 0             | 0     |

|                                      | Bank 2               | 4         | 6             | 6         | 6         | 9             | 9     |

| High-Speed Differential I/O per Bank | Bank 3               | 6         | -8            | 10        | 9         | 12            | 16    |

| no por Barik                         | Bank 6               | 7         | 9             | 10        | -11       | 14            | 16    |

|                                      | Bank 7               | 6         | 8             | 9         | 9         | 12            | 13    |

|                                      | Bank 8               | 0         | 0             | 0         | 0         | 0             | 0     |

|                                      | Bank 0               | 42/21     | 60/30         | 86/43     | 42/21     | 60/30         | 86/43 |

|                                      | Bank 1               | 36/18     | 48/24         | 78/39     | 36/18     | 48/24         | 78/39 |

| Total Single-Ended/                  | Bank 2               | 28/14     | 42/21         | 44/22     | 28/14     | 42/21         | 44/22 |

| Total Differential I/O               | Bank 3               | 58/29     | 71/35         | 98/49     | 58/29     | 71/35         | 98/49 |

| per Bank                             | Bank 6               | 67/33     | 79/38         | 98/49     | 67/33     | 78/39         | 98/49 |

|                                      | Bank 7               | 40/20     | 56/28         | 62/31     | 40/20     | 56/28         | 62/31 |

|                                      | Bank 8               | 24/12     | 24/12         | 24/12     | 24/12     | 24/12         | 24/12 |

|                                      | Bank 0               | 3         | 5             | 7         | 3         | 5             | 7     |

|                                      | Bank 1               | 3         | 4             | 7         | 3         | 4             | 7     |

|                                      | Bank 2               | 2         | 3             | 3         | 2         | 3             | 3     |

| DDR Groups Bonded per Bank           | Bank 3               | 3         | 4             | 5         | 3         | 4             | 5     |

| por burnt                            | Bank 6               | 4         | 4             | 5         | 4         | 4             | 5     |

|                                      | Bank 7               | 3         | 4             | 4         | 3         | 4             | 4     |

|                                      | Configuration Bank 8 | 0         | 0             | 0         | 0         | 0             | 0     |

| SERDES Quads                         |                      | 1         | 2             | 3         | 1         | 2             | 3     |

# **Pin Information Summary (Cont.)**

| Pin Information                            |              | ECP3-95E/EA  | ECP3-150EA    |              |               |      |

|--------------------------------------------|--------------|--------------|---------------|--------------|---------------|------|

| Pin Typ                                    | 484<br>fpBGA | 672<br>fpBGA | 1156<br>fpBGA | 672<br>fpBGA | 1156<br>fpBGA |      |

|                                            | Bank 0       | 42           | 60            | 86           | 60            | 94   |

|                                            | Bank 1       | 36           | 48            | 78           | 48            | 86   |

|                                            | Bank 2       | 24           | 34            | 36           | 34            | 58   |

| General Purpose<br>Inputs/Outputs per bank | Bank 3       | 54           | 59            | 86           | 59            | 104  |

| mpato/Outputo per bank                     | Bank 6       | 63           | 67            | 86           | 67            | 104  |

|                                            | Bank 7       | 36           | 48            | 54           | 48            | 76   |

|                                            | Bank 8       | 24           | 24            | 24           | 24            | 24   |

|                                            | Bank 0       | 0            | 0             | 0            | 0             | 0    |

|                                            | Bank 1       | 0            | 0             | 0            | 0             | 0    |

|                                            | Bank 2       | 4            | 8             | 8            | 8             | 8    |

| General Purpose Inputs per<br>Bank         | Bank 3       | 4            | 12            | 12           | 12            | 12   |

| Dalik                                      | Bank 6       | 4            | 12            | 12           | 12            | 12   |

|                                            | Bank 7       | 4            | 8             | 8            | 8             | 8    |

|                                            | Bank 8       | 0            | 0             | 0            | 0             | 0    |

|                                            | Bank 0       | 0            | 0             | 0            | 0             | 0    |

|                                            | Bank 1       | 0            | 0             | 0            | 0             | 0    |

|                                            | Bank 2       | 0            | 0             | 0            | 0             | 0    |

| General Purpose Outputs per<br>Bank        | Bank 3       | 0            | 0             | 0            | 0             | 0    |

| Dalik                                      | Bank 6       | 0            | 0             | 0            | 0             | 0    |

|                                            | Bank 7       | 0            | 0             | 0            | 0             | 0    |

|                                            | Bank 8       | 0            | 0             | 0            | 0             | 0    |

| Total Single-Ended User I/O                |              | 295          | 380           | 490          | 380           | 586  |

| VCC                                        |              | 16           | 32            | 32           | 32            | 32   |

| VCCAUX                                     |              | 8            | 12            | 16           | 12            | 16   |

| VTT                                        |              | 4            | 4             | 8            | 4             | 8    |

| VCCA                                       | 4            | 8            | 16            | 8            | 16            |      |

| VCCPLL                                     | 4            | 4            | 4             | 4            | 4             |      |

|                                            | Bank 0       | 2            | 4             | 4            | 4             | 4    |

|                                            | Bank 1       | 2            | 4             | 4            | 4             | 4    |

|                                            | Bank 2       | 2            | 4             | 4            | 4             | 4    |

| VCCIO                                      | Bank 3       | 2            | 4             | 4            | 4             | 4    |

|                                            | Bank 6       | 2            | 4             | 4            | 4             | 4    |

|                                            | Bank 7       | 2            | 4             | 4            | 4             | 4    |

|                                            | Bank 8       | 2            | 2             | 2            | 2             | 2    |

| VCCJ                                       |              | 1            | 1             | 1            | 1             | 1    |

| TAP                                        |              | 4            | 4             | 4            | 4             | 4    |

| GND, GNDIO                                 | 98           | 139          | 233           | 139          | 233           |      |

| NC                                         | 0            | 0            | 238           | 0            | 116           |      |

| Reserved <sup>1</sup>                      | 2            | 2            | 2             | 2            | 2             |      |

| SERDES                                     | 26           | 52           | 78            | 52           | 104           |      |

| Miscellaneous Pins                         | 8            | 8            | 8             | 8            | 8             |      |

| Total Bonded Pins                          |              | 484          | 672           | 1156         | 672           | 1156 |

## **Logic Signal Connections**

Package pinout information can be found under "Data Sheets" on the LatticeECP3 product pages on the Lattice website at <a href="www.latticesemi.com/products/fpga/ecp3">www.latticesemi.com/products/fpga/ecp3</a> and in the Lattice ispLEVER Design Planner software. To create pinout information from within Design Planner, select View -> Package View. Then select Select File -> Export and choose a type of output file. See Design Planner help for more information.

## **Thermal Management**

Thermal management is recommended as part of any sound FPGA design methodology. To assess the thermal characteristics of a system, Lattice specifies a maximum allowable junction temperature in all device data sheets. Designers must complete a thermal analysis of their specific design to ensure that the device and package do not exceed the junction temperature limits. Refer to the Thermal Management document to find the device/package specific thermal values.

### For Further Information

For further information regarding Thermal Management, refer to the following:

- Thermal Management document

- TN1181, Power Consumption and Management for LatticeECP3 Devices

- Power Calculator tool included with the Lattice ispLEVER design tool, or as a standalone download from www.latticesemi.com/software

# LatticeECP3 Family Data Sheet Revision History

March 2010 Preliminary Data Sheet DS1021

| Date          | Version | Section                             | Change Summary                                                                                                                                                  |  |  |

|---------------|---------|-------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| February 2009 | 01.0    | _                                   | Initial release.                                                                                                                                                |  |  |

| May 2009      | 01.1    | All                                 | Removed references to Parallel burst mode Flash.                                                                                                                |  |  |

|               |         | Introduction                        | Features - Changed 250 Mbps to 230 Mbps in Embedded SERDES bulleted section and added a footnote to indicate 230 Mbps applies to 8b10b and 10b12b applications. |  |  |

|               |         |                                     | Updated data for ECP3-17 in LatticeECP3 Family Selection Guide table.                                                                                           |  |  |

|               |         |                                     | Changed embedded memory from 552 to 700 Kbits in LatticeECP3 Family Selection Guide table.                                                                      |  |  |

|               |         | Architecture                        | Updated description for CLKFB in General Purpose PLL Diagram.                                                                                                   |  |  |

|               |         |                                     | Corrected Primary Clock Sources text section.                                                                                                                   |  |  |

|               |         |                                     | Corrected Secondary Clock/Control Sources text section.                                                                                                         |  |  |

|               |         |                                     | Corrected Secondary Clock Regions table.                                                                                                                        |  |  |

|               |         |                                     | Corrected note below Detailed sysDSP Slice Diagram.                                                                                                             |  |  |

|               |         |                                     | Corrected Clock, Clock Enable, and Reset Resources text section.                                                                                                |  |  |

|               |         |                                     | Corrected ECP3-17 EBR number in Embedded SRAM in the LatticeECP3 Family table.                                                                                  |  |  |

|               |         |                                     | Added On-Chip Termination Options for Input Modes table.                                                                                                        |  |  |

|               |         |                                     | Updated Available SERDES Quads per LatticeECP3 Devices table.                                                                                                   |  |  |

|               |         |                                     | Updated Simplified Channel Block Diagram for SERDES/PCS Block diagram.                                                                                          |  |  |

|               |         | . '0' (                             | Updated Device Configuration text section.                                                                                                                      |  |  |

|               |         |                                     | Corrected software default value of MCLK to be 2.5 MHz.                                                                                                         |  |  |

|               |         | DC and Switching<br>Characteristics | Updated VCCOB Min/Max data in Recommended Operating Conditions table.                                                                                           |  |  |

|               |         |                                     | Corrected footnote 2 in sysIO Recommended Operating Conditions table.                                                                                           |  |  |

| G             |         |                                     | Added added footnote 7 for t <sub>SKEW_PRIB</sub> to External Switching Characteristics table.                                                                  |  |  |

|               |         |                                     | Added 2-to-1 Gearing text section and table.                                                                                                                    |  |  |

|               |         |                                     | Updated External Reference Clock Specification (refclkp/refclkn) table.                                                                                         |  |  |

|               |         |                                     | LatticeECP3 sysCONFIG Port Timing Specifications - updated t <sub>DINIT</sub> information.                                                                      |  |  |

|               |         |                                     | Added sysCONFIG Port Timing waveform.                                                                                                                           |  |  |

|               |         |                                     | Serial Input Data Specifications table, delete Typ data for V <sub>RX-DIFF-S</sub> .                                                                            |  |  |

|               |         |                                     | Added footnote 4 to sysCLOCK PLL Timing table for t <sub>PFD</sub> .                                                                                            |  |  |

|               |         |                                     | Added SERDES/PCS Block Latency Breakdown table.                                                                                                                 |  |  |

|               | G       |                                     | External Reference Clock Specifications table, added footnote 4, add symbol name vREF-IN-DIFF.                                                                  |  |  |

|               |         |                                     | Added SERDES External Reference Clock Waveforms.                                                                                                                |  |  |

|               |         |                                     | Updated Serial Output Timing and Levels table.                                                                                                                  |  |  |

|               |         |                                     | Pin-to-pin performance table, changed "typically 3% slower" to "typically slower".                                                                              |  |  |

© 2010 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.