Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                                             |

|--------------------------------|-----------------------------------------------------------------------------|

| Product Status                 | Obsolete                                                                    |

| Number of LABs/CLBs            | 8375                                                                        |

| Number of Logic Elements/Cells | 67000                                                                       |

| Total RAM Bits                 | 4526080                                                                     |

| Number of I/O                  | 295                                                                         |

| Number of Gates                | -                                                                           |

| Voltage - Supply               | 1.14V ~ 1.26V                                                               |

| Mounting Type                  | Surface Mount                                                               |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                                             |

| Package / Case                 | 484-BBGA                                                                    |

| Supplier Device Package        | 484-FPBGA (23x23)                                                           |

| Purchase URL                   | https://www.e-xfl.com/product-detail/lattice-semiconductor/lfe3-70e-8fn484c |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

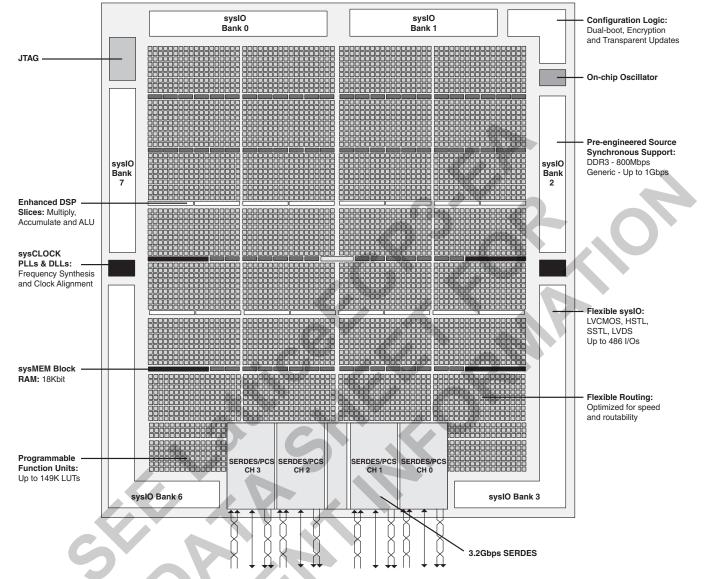

Figure 2-1. Simplified Block Diagram, LatticeECP3-35 Device (Top Level)

Note: There is no Bank 4 or Bank 5 in LatticeECP3 devices

#### **PFU Blocks**

The core of the LatticeECP3 device consists of PFU blocks, which are provided in two forms, the PFU and PFF. The PFUs can be programmed to perform Logic, Arithmetic, Distributed RAM and Distributed ROM functions. PFF blocks can be programmed to perform Logic, Arithmetic and ROM functions. Except where necessary, the remainder of this data sheet will use the term PFU to refer to both PFU and PFF blocks.

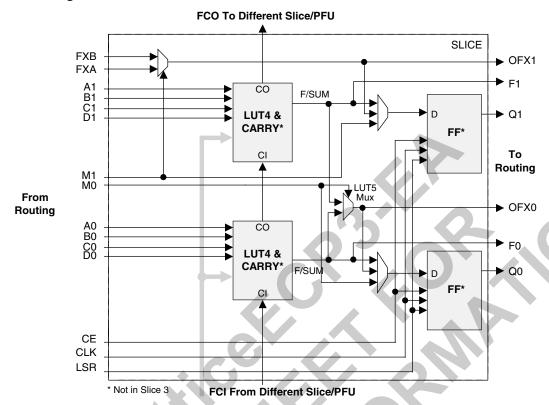

Each PFU block consists of four interconnected slices numbered 0-3 as shown in Figure 2-2. Each slice contains two LUTs. All the interconnections to and from PFU blocks are from routing. There are 50 inputs and 23 outputs associated with each PFU block.

Figure 2-3. Slice Diagram

For Slices 0 and 1, memory control signals are generated from Slice 2 as follows:

WCK is CLK

WRE is from LSR

DI[3:2] for Slice 1 and DI[1:0] for Slice 0 data from Slice 2

WAD [A:D] is a 4-bit address from slice 2 LUT input

Table 2-2. Slice Signal Descriptions

| Function | Туре               | Signal Names   | Description                                                          |

|----------|--------------------|----------------|----------------------------------------------------------------------|

| Input    | Data signal        | A0, B0, C0, D0 | Inputs to LUT4                                                       |

| Input    | Data signal        | A1, B1, C1, D1 | Inputs to LUT4                                                       |

| Input    | Multi-purpose      | MO             | Multipurpose Input                                                   |

| Input    | Multi-purpose      | M1             | Multipurpose Input                                                   |

| Input    | Control signal     | CE             | Clock Enable                                                         |

| Input    | Control signal     | LSR            | Local Set/Reset                                                      |

| Input    | Control signal     | CLK            | System Clock                                                         |

| Input    | Inter-PFU signal   | FC             | Fast Carry-in <sup>1</sup>                                           |

| Input    | Inter-slice signal | FXA            | Intermediate signal to generate LUT6 and LUT7                        |

| Input    | Inter-slice signal | FXB            | Intermediate signal to generate LUT6 and LUT7                        |

| Output   | Data signals       | F0, F1         | LUT4 output register bypass signals                                  |

| Output   | Data signals       | Q0, Q1         | Register outputs                                                     |

| Output   | Data signals       | OFX0           | Output of a LUT5 MUX                                                 |

| Output   | Data signals       | OFX1           | Output of a LUT6, LUT7, LUT8 <sup>2</sup> MUX depending on the slice |

| Output   | Inter-PFU signal   | FCO            | Slice 2 of each PFU is the fast carry chain output <sup>1</sup>      |

<sup>1.</sup> See Figure 2-3 for connection details.

<sup>2.</sup> Requires two PFUs.

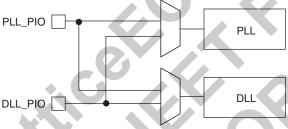

#### **PLL/DLL Cascading**

LatticeECP3 devices have been designed to allow certain combinations of PLL and DLL cascading. The allowable combinations are:

- PLL to PLL supported

- · PLL to DLL supported

The DLLs in the LatticeECP3 are used to shift the clock in relation to the data for source synchronous inputs. PLLs are used for frequency synthesis and clock generation for source synchronous interfaces. Cascading PLL and DLL blocks allows applications to utilize the unique benefits of both DLLs and PLLs.

For further information about the DLL, please see the list of technical documentation at the end of this data sheet.

#### PLL/DLL PIO Input Pin Connections

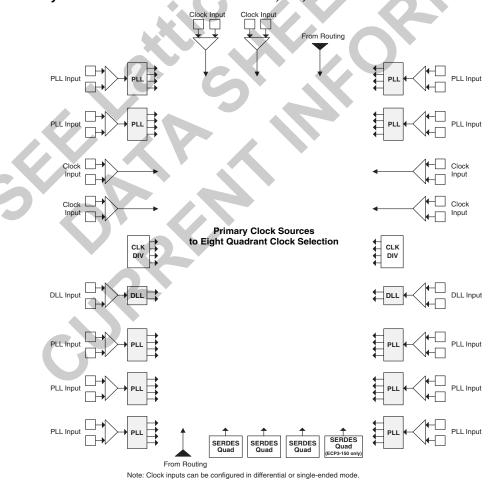

All LatticeECP3 devices contains two DLLs and up to ten PLLs, arranged in quadrants. If a PLL and a DLL are next to each other, they share input pins as shown in the Figure 2-7.

Figure 2-7. Sharing of PIO Pins by PLLs and DLLs in LatticeECP3 Devices

Note: Not every PLL has an associated DLL.

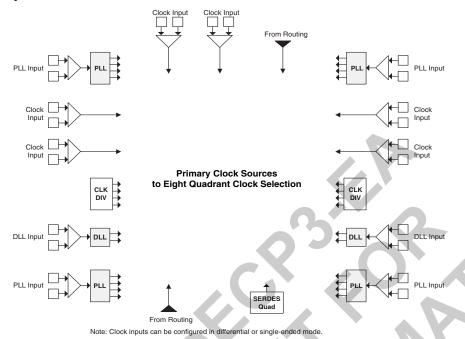

#### **Clock Dividers**

LatticeECP3 devices have two clock dividers, one on the left side and one on the right side of the device. These are intended to generate a slower-speed system clock from a high-speed edge clock. The block operates in a ÷2, ÷4 or ÷8 mode and maintains a known phase relationship between the divided down clock and the high-speed clock based on the release of its reset signal. The clock dividers can be fed from selected PLL/DLL outputs, the Slave Delay lines, routing or from an external clock input. The clock divider outputs serve as primary clock sources and feed into the clock distribution network. The Reset (RST) control signal resets input and asynchronously forces all outputs to low. The RELEASE signal releases outputs synchronously to the input clock. For further information on clock dividers, please see TN1178, LatticeECP3 sysCLOCK PLL/DLL Design and Usage Guide. Figure 2-8 shows the clock divider connections.

Figure 2-10. Primary Clock Sources for LatticeECP3-35

Figure 2-11. Primary Clock Sources for LatticeECP3-70, -95, -150

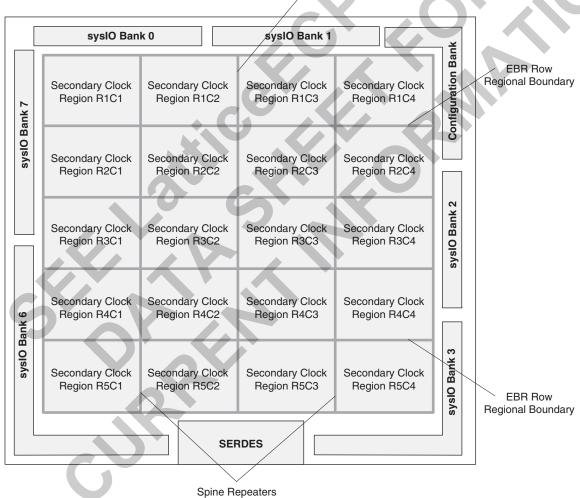

secondary clock resources per region (SC0 to SC7). The same secondary clock routing can be used for control signals.

Table 2-6. Secondary Clock Regions

| Device   | Number of Secondary Clock<br>Regions |

|----------|--------------------------------------|

| ECP3-17  | 16                                   |

| ECP3-35  | 16                                   |

| ECP3-70  | 20                                   |

| ECP3-95  | 20                                   |

| ECP3-150 | 36                                   |

Figure 2-15. LatticeECP3-70 and LatticeECP3-95 Secondary Clock Regions

Vertical Routing Channel Regional Boundary

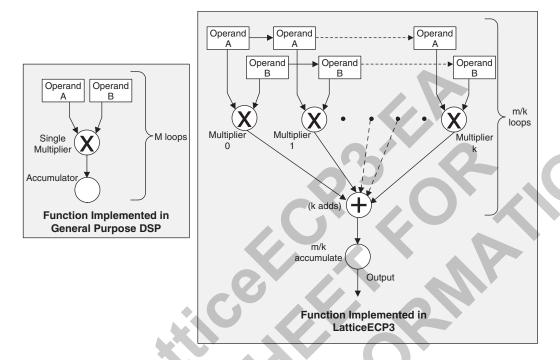

This allows designers to use highly parallel implementations of DSP functions. Designers can optimize DSP performance vs. area by choosing appropriate levels of parallelism. Figure 2-23 compares the fully serial implementation to the mixed parallel and serial implementation.

Figure 2-23. Comparison of General DSP and LatticeECP3 Approaches

#### LatticeECP3 sysDSP Slice Architecture Features

The LatticeECP3 sysDSP Slice has been significantly enhanced to provide functions needed for advanced processing applications. These enhancements provide improved flexibility and resource utilization.

The LatticeECP3 sysDSP Slice supports many functions that include the following:

- Multiply (one 18x36, two 18x18 or four 9x9 Multiplies per Slice)

- Multiply (36x36 by cascading across two sysDSP slices)

- Multiply Accumulate (up to 18x36 Multipliers feeding an Accumulator that can have up to 54-bit resolution)

- Two Multiplies feeding one Accumulate per cycle for increased processing with lower latency (two 18x18 Multiplies feed into an accumulator that can accumulate up to 52 bits)

- Flexible saturation and rounding options to satisfy a diverse set of applications situations

- Flexible cascading across DSP slices

- Minimizes fabric use for common DSP and ALU functions

- Enables implementation of FIR Filter or similar structures using dedicated sysDSP slice resources only

- Provides matching pipeline registers

- Can be configured to continue cascading from one row of sysDSP slices to another for longer cascade chains

- Flexible and Powerful Arithmetic Logic Unit (ALU) Supports:

- Dynamically selectable ALU OPCODE

- Ternary arithmetic (addition/subtraction of three inputs)

- Bit-wise two-input logic operations (AND, OR, NAND, NOR, XOR and XNOR)

- Eight flexible and programmable ALU flags that can be used for multiple pattern detection scenarios, such

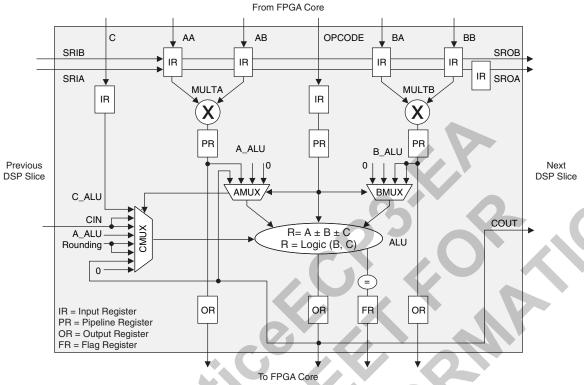

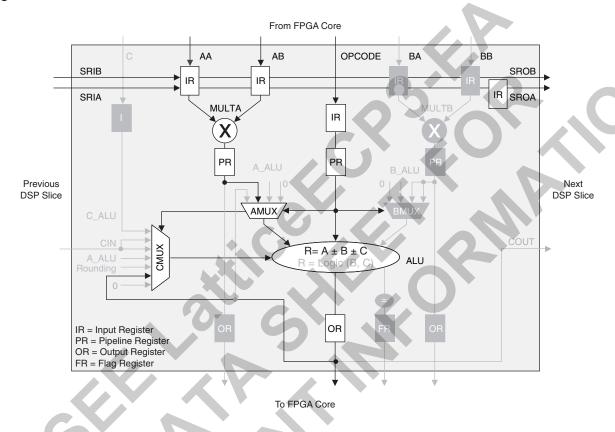

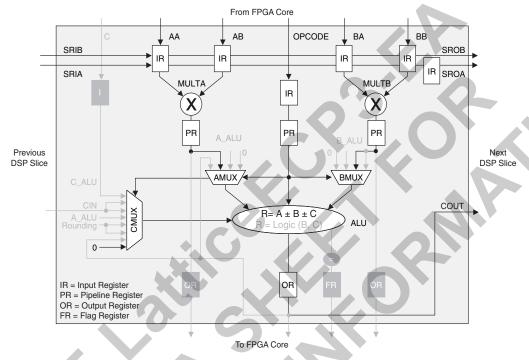

Figure 2-25. Detailed sysDSP Slice Diagram

Note: A\_ALU, B\_ALU and C\_ALU are internal signals generated by combining bits from AA, AB, BA BB and C inputs. See TN1182, LatticeECP3 sysDSP Usage Guide, for further information.

The LatticeECP2 sysDSP block supports the following basic elements.

- MULT (Multiply)

- MAC (Multiply, Accumulate)

- MULTADDSUB (Multiply, Addition/Subtraction)

- MULTADDSUBSUM (Multiply, Addition/Subtraction, Summation)

Table 2-8 shows the capabilities of each of the LatticeECP3 slices versus the above functions.

Table 2-8. Maximum Number of Elements in a Slice

| Width of Multiply | х9             | x18 | x36 |

|-------------------|----------------|-----|-----|

| MULT              | 4              | 2   | 1/2 |

| MAC               | 1              | 1   | _   |

| MULTADDSUB        | 2              | 1   | _   |

| MULTADDSUBSUM     | 1 <sup>1</sup> | 1/2 | _   |

<sup>1.</sup> One slice can implement 1/2 9x9 m9x9addsubsum and two m9x9addsubsum with two slices.

Some options are available in the four elements. The input register in all the elements can be directly loaded or can be loaded as a shift register from previous operand registers. By selecting "dynamic operation" the following operations are possible:

- In the Add/Sub option the Accumulator can be switched between addition and subtraction on every cycle.

- The loading of operands can switch between parallel and serial operations.

#### **MAC DSP Element**

In this case, the two operands, AA and AB, are multiplied and the result is added with the previous accumulated value. This accumulated value is available at the output. The user can enable the input and pipeline registers, but the output register is always enabled. The output register is used to store the accumulated value. The ALU is configured as the accumulator in the sysDSP slice in the LatticeECP3 family can be initialized dynamically. A registered overflow signal is also available. The overflow conditions are provided later in this document. Figure 2-27 shows the MAC sysDSP element.

Figure 2-27. MAC DSP Element

#### **MULTADDSUBSUM DSP Element**

In this case, the operands AA and AB are multiplied and the result is added/subtracted with the result of the multiplier operation of operands BA and BB of Slice 0. Additionally, the operands AA and AB are multiplied and the result is added/subtracted with the result of the multiplier operation of operands BA and BB of Slice 1. The results of both addition/subtractions are added by the second ALU following the slice cascade path. The user can enable the input, output and pipeline registers. Figure 2-30 and Figure 2-31 show the MULTADDSUBSUM sysDSP element

Figure 2-30. MULTADDSUBSUM Slice 0

Please see TN1177, LatticeECP3 sysIO Usage Guide for on-chip termination usage and value ranges.

#### **Equalization Filter**

Equalization filtering is available for single-ended inputs on both true and complementary I/Os, and for differential inputs on the true I/Os on the left, right, and top sides. Equalization is required to compensate for the difficulty of sampling alternating logic transitions with a relatively slow slew rate. It is considered the most useful for the Input DDRX2 modes, used in DDR3 memory, LVDS, or TRLVDS signaling. Equalization filter acts as a tunable filter with settings to determine the level of correction. In the LatticeECP3 devices, there are four settings available: 0 (none), 1, 2 and 3. The default setting is 0. The equalization logic resides in the sysI/O buffers, the two bits of setting is set uniquely in each input IOLOGIC block. Therefore, each sysI/O can have a unique equalization setting within a DQS-12 group.

#### **Hot Socketing**

LatticeECP3 devices have been carefully designed to ensure predictable behavior during power-up and power-down. During power-up and power-down sequences, the I/Os remain in tri-state until the power supply voltage is high enough to ensure reliable operation. In addition, leakage into I/O pins is controlled within specified limits. Please refer to the Hot Socketing Specifications in the DC and Switching Characteristics in this data sheet.

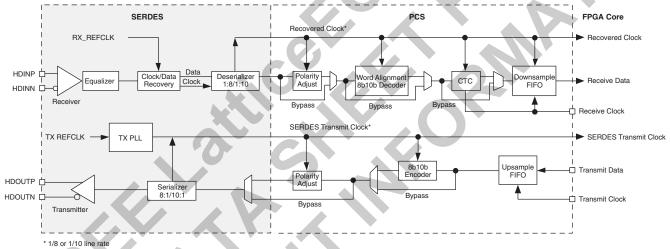

#### **SERDES and PCS (Physical Coding Sublayer)**

LatticeECP3 devices feature up to 16 channels of embedded SERDES/PCS arranged in quads at the bottom of the devices supporting up to 3.2Gbps data rate. Figure 2-40 shows the position of the quad blocks for the LatticeECP3-150 devices. Table 2-14 shows the location of available SERDES Quads for all devices.

The LatticeECP3 SERDES/PCS supports a range of popular serial protocols, including:

- PCI Express 1.1

- Ethernet (XAUI, GbE 1000 Base CS/SX/LX and SGMII)

- · Serial RapidIO

- SMPTE SDI (3G, HD, SD)

- CPRI

- SONET/SDH (STS-3, STS-12, STS-48)

Each quad contains four dedicated SERDES for high speed, full duplex serial data transfer. Each quad also has a PCS block that interfaces to the SERDES channels and contains protocol specific digital logic to support the standards listed above. The PCS block also contains interface logic to the FPGA fabric. All PCS logic for dedicated protocol support can also be bypassed to allow raw 8-bit or 10-bit interfaces to the FPGA fabric.

Even though the SERDES/PCS blocks are arranged in quads, multiple baud rates can be supported within a quad with the use of dedicated, per channel ÷1, ÷2 and ÷11 rate dividers. Additionally, multiple quads can be arranged together to form larger data pipes.

For information on how to use the SERDES/PCS blocks to support specific protocols, as well on how to combine multiple protocols and baud rates within a device, please refer to TN1176, <u>LatticeECP3 SERDES/PCS Usage Guide</u>.

Table 2-14. Available SERDES Quads per LatticeECP3 Devices

| Package    | ECP3-17 | ECP3-35 | ECP3-70 | ECP3-95 | ECP3-150 |

|------------|---------|---------|---------|---------|----------|

| 256 ftBGA  | 1       | 1       | _       | _       | _        |

| 484 ftBGA  | 1       | 1       | 1       | 1       |          |

| 672 ftBGA  | _       | 1       | 2       | 2       | 2        |

| 1156 ftBGA | _       | _       | 3       | 3       | 4        |

#### **SERDES Block**

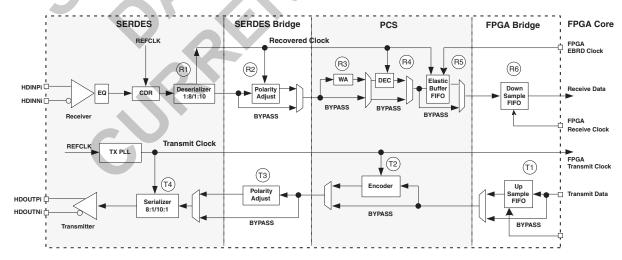

A SERDES receiver channel may receive the serial differential data stream, equalize the signal, perform Clock and Data Recovery (CDR) and de-serialize the data stream before passing the 8- or 10-bit data to the PCS logic. The SERDES transmitter channel may receive the parallel 8- or 10-bit data, serialize the data and transmit the serial bit stream through the differential drivers. Figure 2-41 shows a single-channel SERDES/PCS block. Each SERDES channel provides a recovered clock and a SERDES transmit clock to the PCS block and to the FPGA core logic.

Each transmit channel, receiver channel, and SERDES PLL shares the same power supply (VCCA). The output and input buffers of each channel have their own independent power supplies (VCCOB and VCCIB).

Figure 2-41. Simplified Channel Block Diagram for SERDES/PCS Block

#### **PCS**

As shown in Figure 2-41, the PCS receives the parallel digital data from the deserializer and selects the polarity, performs word alignment, decodes (8b/10b), provides Clock Tolerance Compensation and transfers the clock domain from the recovered clock to the FPGA clock via the Down Sample FIFO.

For the transmit channel, the PCS block receives the parallel data from the FPGA core, encodes it with 8b/10b, selects the polarity and passes the 8/10 bit data to the transmit SERDES channel.

The PCS also provides bypass modes that allow a direct 8-bit or 10-bit interface from the SERDES to the FPGA logic. The PCS interface to the FPGA can also be programmed to run at 1/2 speed for a 16-bit or 20-bit interface to the FPGA logic.

#### SCI (SERDES Client Interface) Bus

The SERDES Client Interface (SCI) is an IP interface that allows the SERDES/PCS Quad block to be controlled by registers rather than the configuration memory cells. It is a simple register configuration interface that allows SERDES/PCS configuration without power cycling the device.

CLKA CSA WEA Three consecultive writes to A0 ADA Á0 A0 t<sub>SU</sub> t<sub>H</sub> Dο DΪ DIA tACCESS tACCESS TACCESS tACCESS Data from Prev Read Þο DOA D2 D4 or Write

Figure 3-11. Write Through (SP Read/Write on Port A, Input Registers Only)

Note: Input data and address are registered at the positive edge of the clock and output data appears after the positive edge of the clock.

#### **SERDES/PCS Block Latency**

Table 3-8 describes the latency of each functional block in the transmitter and receiver. Latency is given in parallel clock cycles. Figure 3-12 shows the location of each block.

Table 3-8. SERDES/PCS Latency Breakdown

| Item                               | Description                                          | Min.      | Avg.          | Max.          | Fixed   | Bypass        | Units    |  |

|------------------------------------|------------------------------------------------------|-----------|---------------|---------------|---------|---------------|----------|--|

| Transmit Data Latency <sup>1</sup> |                                                      |           |               |               |         |               |          |  |

|                                    | FPGA Bridge - Gearing disabled with different clocks | 1         | 3             | 5             | _       | 1             | word clk |  |

| T1                                 | FPGA Bridge - Gearing disabled with same clocks      | _         | _             | -             | 3       | 1             | word clk |  |

|                                    | FPGA Bridge - Gearing enabled                        | 1         | 3             | 5             | _       | _             | word clk |  |

| T2                                 | 8b10b Encoder                                        | _         | -             |               | 2       | 1             | word clk |  |

| T3                                 | SERDES Bridge transmit                               | _         |               | 7             | 2       | 1             | word clk |  |

| T4                                 | Serializer: 8-bit mode                               | _         | 7-            | - 4           | 15 + ∆1 | _             | UI + ps  |  |

| 14                                 | Serializer: 10-bit mode                              | 70        |               |               | 18 + ∆1 | - C           | UI + ps  |  |

| T5                                 | Pre-emphasis ON                                      |           | _             | -             | 1 + Δ2  | 7-            | UI + ps  |  |

| 15                                 | Pre-emphasis OFF                                     |           | · — /         |               | 0 + Δ3  | 7-7           | UI + ps  |  |

| Receive                            | Data Latency <sup>2</sup>                            |           |               |               |         |               |          |  |

| R1                                 | Equalization ON                                      |           | _             | <b>&gt;</b> - | Δ1      | <b>&gt;</b> - | UI + ps  |  |

| n i                                | Equalization OFF                                     |           | 7             |               | Δ2      | _             | UI + ps  |  |

| R2                                 | Deserializer: 8-bit mode                             |           |               | -             | 10 + ∆3 | _             | UI + ps  |  |

| ΠZ                                 | Deserializer: 10-bit mode                            | <b>/</b>  |               |               | 12 + ∆3 | _             | UI + ps  |  |

| R3                                 | SERDES Bridge receive                                | <b>/</b>  | _             | 1             | 2       | _             | word clk |  |

| R4                                 | Word alignment                                       | 3.1       | -             | 4             | —       | _             | word clk |  |

| R5                                 | 8b10b decoder                                        | \ <u></u> | <i>&gt;</i> + | 7-            | 1       | _             | word clk |  |

| R6                                 | Clock Tolerance Compensation                         | 7         | 15            | 23            | 1       | 1             | word clk |  |

|                                    | FPGA Bridge - Gearing disabled with different clocks | 1         | 3             | 5             | _       | 1             | word clk |  |

| R7                                 | FPGA Bridge - Gearing disabled with same clocks      |           | <u> </u>      | _             | 3       | 1             | word clk |  |

|                                    | FPGA Bridge - Gearing enabled                        | 1         | 3             | 5             | _       | _             | word clk |  |

<sup>1.</sup>  $\Delta 1 = -245$ ps,  $\Delta 2 = +88$ ps,  $\Delta 3 = +112$ ps.

Figure 3-12. Transmitter and Receiver Latency Block Diagram

<sup>2.</sup>  $\Delta 1 = +118$ ps,  $\Delta 2 = +132$ ps,  $\Delta 3 = +700$ ps.

Table 3-11. Periodic Receiver Jitter Tolerance Specification

| Description | Frequency  | Condition               | Min. | Тур. | Max. | Units   |

|-------------|------------|-------------------------|------|------|------|---------|

| Periodic    | 2.97 Gbps  | 600 mV differential eye | _    | _    | 0.24 | UI, p-p |

| Periodic    | 2.5 Gbps   | 600 mV differential eye | _    | _    | 0.22 | UI, p-p |

| Periodic    | 1.485 Gbps | 600 mV differential eye | _    | _    | 0.24 | UI, p-p |

| Periodic    | 622 Mbps   | 600 mV differential eye | _    | _    | 0.15 | UI, p-p |

| Periodic    | 155 Mbps   | 600 mV differential eye | _    | _    | 0.5  | UI, p-p |

Note: Values are measured with PRBS 2<sup>7</sup>-1, all channels operating, FPGA Logic active, I/Os around SERDES pins quiet, voltages are nominal, room temperature.

# Serial Rapid I/O Type 2 Electrical and Timing Characteristics AC and DC Characteristics

#### Table 3-15. Transmit

| Symbol                                   | Description                      | Test Conditions | Min. | Тур. | Max. | Units |

|------------------------------------------|----------------------------------|-----------------|------|------|------|-------|

| T <sub>RF</sub> <sup>1</sup>             | Differential rise/fall time      | 20%-80%         | _    | 80   | _    | ps    |

| Z <sub>TX_DIFF_DC</sub>                  | Differential impedance           |                 | 80   | 100  | 120  | Ohms  |

| J <sub>TX_DDJ</sub> <sup>3, 4, 5</sup>   | Output data deterministic jitter |                 | _    |      | 0.17 | UI    |

| J <sub>TX_TJ</sub> <sup>2, 3, 4, 5</sup> | Total output data jitter         |                 | - (  | 1    | 0.35 | UI    |

- 1. Rise and Fall times measured with board trace, connector and approximately 2.5pf load.

- 2. Total jitter includes both deterministic jitter and random jitter. The random jitter is the total jitter minus the actual deterministic jitter.

- 3. Jitter values are measured with each CML output AC coupled into a 50-ohm impedance (100-ohm differential impedance).

- 4. Jitter and skew are specified between differential crossings of the 50% threshold of the reference signal.

- 5. Values are measured at 2.5 Gbps.

#### Table 3-16. Receive and Jitter Tolerance

| Symbol                                      | Description                                   | Test Conditions         | Min.     | Тур. | Max. | Units |

|---------------------------------------------|-----------------------------------------------|-------------------------|----------|------|------|-------|

| RL <sub>RX_DIFF</sub>                       | Differential return loss                      | From 100 MHz to 2.5 GHz | 10       | _    |      | dB    |

| RL <sub>RX_CM</sub>                         | Common mode return loss                       | From 100 MHz to 2.5 GHz | 6        |      | _    | dB    |

| Z <sub>RX_DIFF</sub>                        | Differential termination resistance           |                         | 80       | 100  | 120  | Ohms  |

| J <sub>RX_DJ</sub> <sup>2, 3, 4, 5</sup>    | Deterministic jitter tolerance (peak-to-peak) |                         | (-1)     | _    | 0.37 | UI    |

| J <sub>RX_RJ</sub> <sup>2, 3, 4, 5</sup>    | Random jitter tolerance (peak-to-peak)        |                         | 7        | _    | 0.18 | UI    |

| J <sub>RX_SJ</sub> <sup>2, 3, 4, 5</sup>    | Sinusoidal jitter tolerance (peak-to-peak)    |                         |          | _    | 0.10 | UI    |

| J <sub>RX_TJ</sub> <sup>1, 2, 3, 4, 5</sup> | Total jitter tolerance (peak-to-peak)         |                         | <u> </u> | _    | 0.65 | UI    |

| T <sub>RX_EYE</sub>                         | Receiver eye opening                          |                         | 0.35     | _    | _    | UI    |

- 1. Total jitter includes deterministic jitter, random jitter and sinusoidal jitter. The sinusoidal jitter tolerance mask is shown in Figure 3-14.

- 2. Jitter values are measured with each high-speed input AC coupled into a 50-ohm impedance.

- 3. Jitter and skew are specified between differential crossings of the 50% threshold of the reference signal.

- 4. Jitter tolerance, Differential Input Sensitivity and Receiver Eye Opening parameters are characterized when Full Rx Equalization is enabled.

- 5. Values are measured at 2.5 Gbps.

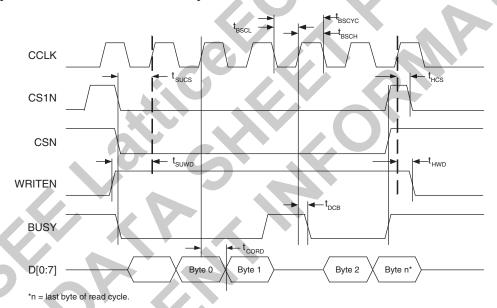

## **LatticeECP3 sysCONFIG Port Timing Specifications**

#### **Over Recommended Operating Conditions**

| Parameter            | Description                                                                                                                                    |                    | Min. | Max.     | Units  |

|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|------|----------|--------|

| POR, Confi           | guration Initialization, and Wakeup                                                                                                            |                    |      |          |        |

|                      | Time from the Application of $V_{CC}$ , $V_{CCAUX}$ or $V_{CCIO8}^*$ (Whichever is the Last to Cross the POR Trip Point) to the Rising Edge of | Master mode        | _    | 23       | ms     |

| t <sub>ICFG</sub>    | is the Last to Cross the POR Trip Point) to the Rising Edge of INITN                                                                           | Slave mode         |      | 6        | ms     |

| t <sub>VMC</sub>     | Time from t <sub>ICFG</sub> to the Valid Master MCLK                                                                                           |                    | _    | 5        | μs     |

| t <sub>PRGM</sub>    | PROGRAMN Low Time to Start Configuration                                                                                                       |                    | 25   | _        | ns     |

| t <sub>PRGMRJ</sub>  | PROGRAMN Pin Pulse Rejection                                                                                                                   |                    | _    | 10       | ns     |

| t <sub>DPPINIT</sub> | Delay Time from PROGRAMN Low to INITN Low                                                                                                      |                    | _    | 37       | ns     |

| t <sub>DPPDONE</sub> | Delay Time from PROGRAMN Low to DONE Low                                                                                                       |                    | _    | 37       | ns     |

| t <sub>DINIT</sub>   | PROGRAMN High to INITN High Delay                                                                                                              | 5                  |      | 1        | ms     |

| t <sub>MWC</sub>     | Additional Wake Master Clock Signals After DONE Pin is High                                                                                    |                    | 100  | 500      | cycles |

| t <sub>CZ</sub>      | MCLK From Active To Low To High-Z                                                                                                              |                    |      | 300      | ns     |

| All Configu          | ration Modes                                                                                                                                   |                    |      |          |        |

| t <sub>SUCDI</sub>   | Data Setup Time to CCLK/MCLK                                                                                                                   |                    | 5    | <u> </u> | ns     |

| t <sub>HCDI</sub>    | Data Hold Time to CCLK/MCLK                                                                                                                    |                    | 1    | -        | ns     |

| t <sub>CODO</sub>    | CCLK/MCLK to DOUT in Flowthrough Mode                                                                                                          |                    | -    | 12       | ns     |

| Slave Seria          |                                                                                                                                                |                    |      |          | ı      |

| t <sub>SSCH</sub>    | CCLK Minimum High Pulse                                                                                                                        |                    | 5    | _        | ns     |

| t <sub>SSCL</sub>    | CCLK Minimum Low Pulse                                                                                                                         |                    | 5    | _        | ns     |

| JOOL                 |                                                                                                                                                | Without encryption |      | 33       | MHz    |

| f <sub>CCLK</sub>    |                                                                                                                                                |                    |      | 20       | MHz    |

| Master and           | Slave Parallel                                                                                                                                 | 71                 |      | <u> </u> |        |

| t <sub>SUCS</sub>    | CSN[1:0] Setup Time to CCLK/MCLK                                                                                                               |                    | 7    | _        | ns     |

| t <sub>HCS</sub>     | CSN[1:0] Hold Time to CCLK/MCLK                                                                                                                |                    | 1    | _        | ns     |

| t <sub>SUWD</sub>    | WRITEN Setup Time to CCLK/MCLK                                                                                                                 |                    | 7    | _        | ns     |

| t <sub>HWD</sub>     | WRITEN Hold Time to CCLK/MCLK                                                                                                                  |                    | 1    | _        | ns     |

| t <sub>DCB</sub>     | CCLK/MCLK to BUSY Delay Time                                                                                                                   |                    | _    | 12       | ns     |

| t <sub>CORD</sub>    | CCLK to Out for Read Data                                                                                                                      |                    | _    | 12       | ns     |

| t <sub>BSCH</sub>    | CCLK Minimum High Pulse                                                                                                                        |                    | 6    | <u> </u> | ns     |

| t <sub>BSCL</sub>    | CCLK Minimum Low Pulse                                                                                                                         |                    | 6    | _        | ns     |

| t <sub>BSCYC</sub>   | Byte Slave Cycle Time                                                                                                                          |                    | 30   | <u> </u> | ns     |

|                      |                                                                                                                                                | Without encryption | _    | 33       | MHz    |

| f <sub>CCLK</sub>    | CCLK/MCLK Frequency                                                                                                                            | With encryption    | _    | 20       | MHz    |

| Master and           | Slave SPI                                                                                                                                      |                    |      | 1        | ı      |

| t <sub>CFGX</sub>    | INITN High to MCLK Low                                                                                                                         |                    | _    | 80       | ns     |

| t <sub>CSSPI</sub>   | INITN High to CSSPIN Low                                                                                                                       |                    | 0.2  | 2        | μs     |

| t <sub>SOCDO</sub>   | MCLK Low to Output Valid                                                                                                                       |                    | _    | 15       | ns     |

| t <sub>CSPID</sub>   | CSSPIN[0:1] Low to First MCLK Edge Setup Time                                                                                                  |                    |      |          | μs     |

|                      | CCLK Frequency  Without encryption  With encryption                                                                                            |                    | _    | 33       | MHz    |

| f <sub>CCLK</sub>    |                                                                                                                                                |                    | _    | 20       | MHz    |

| t <sub>SSCH</sub>    | CCLK Minimum High Pulse                                                                                                                        | 1                  | 5    | <u> </u> | ns     |

| t <sub>SSCL</sub>    | CCLK Minimum Low Pulse                                                                                                                         |                    | 5    | <u> </u> | ns     |

| t <sub>HLCH</sub>    | HOLDN Low Setup Time (Relative to CCLK)                                                                                                        |                    | 5    | _        | ns     |

## **LatticeECP3 sysCONFIG Port Timing Specifications (Continued)**

#### **Over Recommended Operating Conditions**

| Parameter         | Description                              | Min. | Max. | Units |

|-------------------|------------------------------------------|------|------|-------|

| t <sub>CHHH</sub> | HOLDN Low Hold Time (Relative to CCLK)   | 5    | _    | ns    |

| Master and        | Slave SPI (Continued)                    |      |      |       |

| t <sub>CHHL</sub> | HOLDN High Hold Time (Relative to CCLK)  | 5    |      | ns    |

| t <sub>HHCH</sub> | HOLDN High Setup Time (Relative to CCLK) | 5    | _    | ns    |

| t <sub>HLQZ</sub> | HOLDN to Output High-Z                   | _    | 9    | ns    |

| t <sub>HHQX</sub> | HOLDN to Output Low-Z                    | _    | 9    | ns    |

| Parameter              | Min.                 | Max.                 | Units |

|------------------------|----------------------|----------------------|-------|

| Master Clock Frequency | Selected value - 15% | Selected value + 15% | MHz   |

| Duty Cycle             | 40                   | 60                   | %     |

Figure 3-16. sysCONFIG Parallel Port Read Cycle

# **Pin Information Summary (Cont.)**

| Pin Information Summary                                |                      | ECP3-17EA |           | ECP3-35EA |           |           |  |

|--------------------------------------------------------|----------------------|-----------|-----------|-----------|-----------|-----------|--|

| Pin Typ                                                | Pin Type             |           | 484 fpBGA | 256 ftBGA | 484 fpBGA | 672 fpBGA |  |

| Emulated Differential I/O per Bank                     | Bank 0               | 13        | 18        | 13        | 21        | 24        |  |

|                                                        | Bank 1               | 7         | 12        | 7         | 18        | 18        |  |

|                                                        | Bank 2               | 2         | 4         | 1         | 8         | 8         |  |

|                                                        | Bank 3               | 4         | 13        | 5         | 20        | 19        |  |

| Barne                                                  | Bank 6               | 5         | 13        | 6         | 22        | 20        |  |

|                                                        | Bank 7               | 6         | 10        | 6         | <b>11</b> | 13        |  |

|                                                        | Bank 8               | 12        | 12        | 12        | 12        | 12        |  |

|                                                        | Bank 0               | 0         | 0         | 0         | 0         | 0         |  |

|                                                        | Bank 1               | 0         | 0         | 0         | 0         | 0         |  |

| 15:4                                                   | Bank 2               | 2         | 3         | 3         | 6         | 6         |  |

| Highspeed Differential I/O per Bank                    | Bank 3               | 5         | 9         | 4         | 9         | 12        |  |

|                                                        | Bank 6               | 5         | 9         | 4         | 11        | 12        |  |

|                                                        | Bank 7               | 5         | 8         | 5         | 9         | 10        |  |

|                                                        | Bank 8               | 0         | 0         | 0         | 0         | 0         |  |

|                                                        | Bank 0               | 26/13     | 36/18     | 26/13     | 42/21     | 48/24     |  |

|                                                        | Bank 1               | 14/7      | 24/12     | 14/7      | 36/18     | 36/18     |  |

| T. 10: 1 F 1 1/T. 1                                    | Bank 2               | 8/4       | 14/7      | 8/4       | 28/14     | 28/14     |  |

| Total Single Ended/ Total<br>Differential I/O per Bank | Bank 3               | 18/9      | 44/22     | 18/9      | 58/29     | 63/31     |  |

|                                                        | Bank 6               | 20/10     | 44/22     | 20/10     | 67/33     | 65/32     |  |

|                                                        | Bank 7               | 23/11     | 36/18     | 23/11     | 40/20     | 46/23     |  |

|                                                        | Bank 8               | 24/12     | 24/12     | 24/12     | 24/12     | 24/12     |  |

|                                                        | Bank 0               | 2         | 3         | 2         | 3         | 4         |  |

|                                                        | Bank 1               | 1         | 2         | 1         | 3         | 3         |  |

| DDR Groups Bonded per<br>Bank                          | Bank 2               | 0         | 1         | 0         | 2         | 2         |  |

|                                                        | Bank 3               | 1         | 3         | 1         | 3         | 4         |  |

|                                                        | Bank 6               | 1         | 3         | 1         | 4         | 4         |  |

|                                                        | Bank 7               | 1         | 2         | 1         | 3         | 3         |  |

|                                                        | Configuration Bank 8 | 0         | 0         | 0         | 0         | 0         |  |

| SERDES Quads                                           |                      | 1         | 1         | 1         | 1         | 1         |  |

<sup>1.</sup> These pins must remain floating on the board.

| Part Number                    | Voltage | Grade | Package         | Pins | Temp. | LUTs (K) |

|--------------------------------|---------|-------|-----------------|------|-------|----------|

| LFE3-70E-6FN484I <sup>1</sup>  | 1.2V    | -6    | Lead-Free fpBGA | 484  | IND   | 67       |

| LFE3-70E-7FN484I <sup>1</sup>  | 1.2V    | -7    | Lead-Free fpBGA | 484  | IND   | 67       |

| LFE3-70E-8FN484I <sup>1</sup>  | 1.2V    | -8    | Lead-Free fpBGA | 484  | IND   | 67       |

| LFE3-70E-6FN672I <sup>1</sup>  | 1.2V    | -6    | Lead-Free fpBGA | 672  | IND   | 67       |

| LFE3-70E-7FN672I <sup>1</sup>  | 1.2V    | -7    | Lead-Free fpBGA | 672  | IND   | 67       |

| LFE3-70E-8FN672I <sup>1</sup>  | 1.2V    | -8    | Lead-Free fpBGA | 672  | IND   | 67       |

| LFE3-70E-6FN1156I <sup>1</sup> | 1.2V    | -6    | Lead-Free fpBGA | 1156 | IND   | 67       |

| LFE3-70E-7FN1156I <sup>1</sup> | 1.2V    | -7    | Lead-Free fpBGA | 1156 | IND   | 67       |

| LFE3-70E-8FN1156I <sup>1</sup> | 1.2V    | -8    | Lead-Free fpBGA | 1156 | IND   | 67       |

<sup>1.</sup> This device has associated errata. View <a href="https://www.latticesemi.com/documents/ds1021.zip">www.latticesemi.com/documents/ds1021.zip</a> for a description of the errata.

| Part Number        | Voltage | Grade | Package         | Pins | Temp. | LUTs (K) |

|--------------------|---------|-------|-----------------|------|-------|----------|

| LFE3-95EA-6FN484I  | 1.2V    | -6    | Lead-Free fpBGA | 484  | IND   | 92       |

| LFE3-95EA-7FN484I  | 1.2V    | -7    | Lead-Free fpBGA | 484  | IND   | 92       |

| LFE3-95EA-8FN484I  | 1.2V    | -8    | Lead-Free fpBGA | 484  | IND   | 92       |

| LFE3-95EA-6FN672I  | 1.2V    | -6    | Lead-Free fpBGA | 672  | IND   | 92       |

| LFE3-95EA-7FN672I  | 1.2V    | -7    | Lead-Free fpBGA | 672  | IND   | 92       |

| LFE3-95EA-8FN672I  | 1.2V    | -8    | Lead-Free fpBGA | 672  | IND   | 92       |

| LFE3-95EA-6FN1156I | 1.2V    | -6    | Lead-Free fpBGA | 1156 | IND   | 92       |

| LFE3-95EA-7FN1156I | 1.2V    | -7    | Lead-Free fpBGA | 1156 | IND   | 92       |

| LFE3-95EA-8FN1156I | 1.2V    | -8    | Lead-Free fpBGA | 1156 | IND   | 92       |

| Part Number                    | Voltage | Grade | Package         | Pins | Temp. | LUTs (K) |

|--------------------------------|---------|-------|-----------------|------|-------|----------|

| LFE3-95E-6FN484I <sup>1</sup>  | 1.2V    | -6    | Lead-Free fpBGA | 484  | IND   | 92       |

| LFE3-95E-7FN484I <sup>1</sup>  | 1.2V    | -7    | Lead-Free fpBGA | 484  | IND   | 92       |

| LFE3-95E-8FN484I <sup>1</sup>  | 1.2V    | -8    | Lead-Free fpBGA | 484  | IND   | 92       |

| LFE3-95E-6FN672I <sup>1</sup>  | 1.2V    | -6    | Lead-Free fpBGA | 672  | IND   | 92       |

| LFE3-95E-7FN672I <sup>1</sup>  | 1.2V    | -7    | Lead-Free fpBGA | 672  | IND   | 92       |

| LFE3-95E-8FN672I <sup>1</sup>  | 1.2V    | -8    | Lead-Free fpBGA | 672  | IND   | 92       |

| LFE3-95E-6FN1156I <sup>1</sup> | 1.2V    | -6    | Lead-Free fpBGA | 1156 | IND   | 92       |

| LFE3-95E-7FN1156I <sup>1</sup> | 1.2V    | -7    | Lead-Free fpBGA | 1156 | IND   | 92       |

| LFE3-95E-8FN1156I <sup>1</sup> | 1.2V    | -8    | Lead-Free fpBGA | 1156 | IND   | 92       |

<sup>1.</sup> This device has associated errata. View <a href="https://www.latticesemi.com/documents/ds1021.zip">www.latticesemi.com/documents/ds1021.zip</a> for a description of the errata.

# LatticeECP3 Family Data Sheet Supplemental Information

February 2009

**Preliminary Data Sheet DS1021**

#### For Further Information

A variety of technical notes for the LatticeECP3 family are available on the Lattice website at www.latticesemi.com.

- TN1169, LatticeECP3 sysCONFIG Usage Guide

- TN1176, LatticeECP3 SERDES/PCS Usage Guide

- TN1177, LatticeECP3 sysIO Usage Guide

- TN1178, LatticeECP3 sysCLOCK PLL/DLL Design and Usage Guide

- TN1179, LatticeECP3 Memory Usage Guide

- TN1180, LatticeECP3 High-Speed I/O Interface

- TN1181, Power Consumption and Management for LatticeECP3 Devices

- TN1182, LatticeECP3 sysDSP Usage Guide

- TN1184, LatticeECP3 Soft Error Detection (SED) Usage Guide

- TN1189, LatticeECP3 Hardware Checklist

For further information on interface standards refer to the following websites:

- JEDEC Standards (LVTTL, LVCMOS, SSTL, HSTL): www.jedec.org

- PCI: www.pcisig.com