Welcome to **E-XFL.COM**

# **Understanding Embedded - FPGAs (Field Programmable Gate Array)**

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                                             |

|--------------------------------|-----------------------------------------------------------------------------|

| Product Status                 | Obsolete                                                                    |

| Number of LABs/CLBs            | 8375                                                                        |

| Number of Logic Elements/Cells | 67000                                                                       |

| Total RAM Bits                 | 4526080                                                                     |

| Number of I/O                  | 380                                                                         |

| Number of Gates                | -                                                                           |

| Voltage - Supply               | 1.14V ~ 1.26V                                                               |

| Mounting Type                  | Surface Mount                                                               |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                                          |

| Package / Case                 | 672-BBGA                                                                    |

| Supplier Device Package        | 672-FPBGA (27x27)                                                           |

| Purchase URL                   | https://www.e-xfl.com/product-detail/lattice-semiconductor/lfe3-70e-8fn672i |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

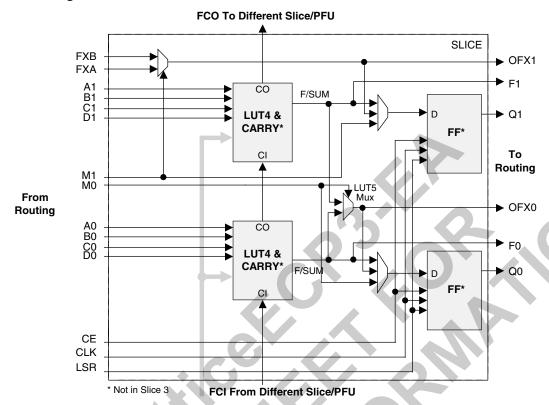

Figure 2-3. Slice Diagram

For Slices 0 and 1, memory control signals are generated from Slice 2 as follows:

WCK is CLK

WRE is from LSR

DI[3:2] for Slice 1 and DI[1:0] for Slice 0 data from Slice 2

WAD [A:D] is a 4-bit address from slice 2 LUT input

Table 2-2. Slice Signal Descriptions

| Function | Туре               | Signal Names   | Description                                                          |

|----------|--------------------|----------------|----------------------------------------------------------------------|

| Input    | Data signal        | A0, B0, C0, D0 | Inputs to LUT4                                                       |

| Input    | Data signal        | A1, B1, C1, D1 | Inputs to LUT4                                                       |

| Input    | Multi-purpose      | MO             | Multipurpose Input                                                   |

| Input    | Multi-purpose      | M1             | Multipurpose Input                                                   |

| Input    | Control signal     | CE             | Clock Enable                                                         |

| Input    | Control signal     | LSR            | Local Set/Reset                                                      |

| Input    | Control signal     | CLK            | System Clock                                                         |

| Input    | Inter-PFU signal   | FC             | Fast Carry-in <sup>1</sup>                                           |

| Input    | Inter-slice signal | FXA            | Intermediate signal to generate LUT6 and LUT7                        |

| Input    | Inter-slice signal | FXB            | Intermediate signal to generate LUT6 and LUT7                        |

| Output   | Data signals       | F0, F1         | LUT4 output register bypass signals                                  |

| Output   | Data signals       | Q0, Q1         | Register outputs                                                     |

| Output   | Data signals       | OFX0           | Output of a LUT5 MUX                                                 |

| Output   | Data signals       | OFX1           | Output of a LUT6, LUT7, LUT8 <sup>2</sup> MUX depending on the slice |

| Output   | Inter-PFU signal   | FCO            | Slice 2 of each PFU is the fast carry chain output <sup>1</sup>      |

<sup>1.</sup> See Figure 2-3 for connection details.

<sup>2.</sup> Requires two PFUs.

# **Modes of Operation**

Each slice has up to four potential modes of operation: Logic, Ripple, RAM and ROM.

#### **Logic Mode**

In this mode, the LUTs in each slice are configured as 4-input combinatorial lookup tables. A LUT4 can have 16 possible input combinations. Any four input logic functions can be generated by programming this lookup table. Since there are two LUT4s per slice, a LUT5 can be constructed within one slice. Larger look-up tables such as LUT6, LUT7 and LUT8 can be constructed by concatenating other slices. Note LUT8 requires more than four slices.

#### **Ripple Mode**

Ripple mode supports the efficient implementation of small arithmetic functions. In ripple mode, the following functions can be implemented by each slice:

- · Addition 2-bit

- Subtraction 2-bit

- Add/Subtract 2-bit using dynamic control

- · Up counter 2-bit

- · Down counter 2-bit

- · Up/Down counter with asynchronous clear

- Up/Down counter with preload (sync)

- · Ripple mode multiplier building block

- Multiplier support

- · Comparator functions of A and B inputs

- A greater-than-or-equal-to B

- A not-equal-to B

- A less-than-or-equal-to B

Ripple Mode includes an optional configuration that performs arithmetic using fast carry chain methods. In this configuration (also referred to as CCU2 mode) two additional signals, Carry Generate and Carry Propagate, are generated on a per slice basis to allow fast arithmetic functions to be constructed by concatenating Slices.

#### **RAM Mode**

In this mode, a 16x4-bit distributed single port RAM (SPR) can be constructed using each LUT block in Slice 0 and Slice 1 as a 16x1-bit memory. Slice 2 is used to provide memory address and control signals. A 16x2-bit pseudo dual port RAM (PDPR) memory is created by using one Slice as the read-write port and the other companion slice as the read-only port.

LatticeECP3 devices support distributed memory initialization.

The Lattice design tools support the creation of a variety of different size memories. Where appropriate, the software will construct these using distributed memory primitives that represent the capabilities of the PFU. Table 2-3 shows the number of slices required to implement different distributed RAM primitives. For more information about using RAM in LatticeECP3 devices, please see TN1179, <u>LatticeECP3 Memory Usage Guide</u>.

Table 2-3. Number of Slices Required to Implement Distributed RAM

|                  | SPR 16X4 | PDPR 16X4 |

|------------------|----------|-----------|

| Number of slices | 3        | 3         |

Note: SPR = Single Port RAM, PDPR = Pseudo Dual Port RAM

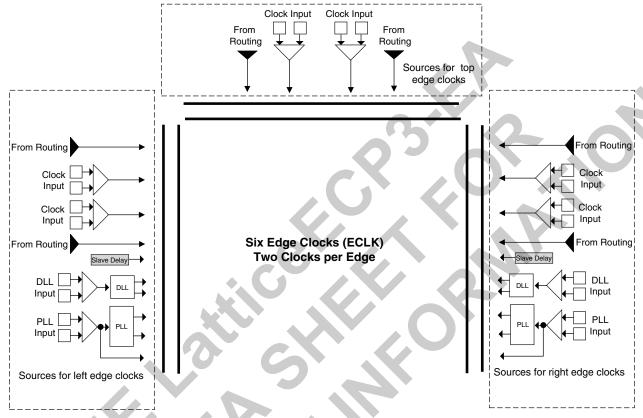

### **Edge Clock Sources**

Edge clock resources can be driven from a variety of sources at the same edge. Edge clock resources can be driven from adjacent edge clock PIOs, primary clock PIOs, PLLs, DLLs, Slave Delay and clock dividers as shown in Figure 2-19.

Figure 2-19. Edge Clock Sources

Notes:

- 1. Clock inputs can be configured in differential or single ended mode.

- 2. The two DLLs can also drive the two top edge clocks.

- 3. The top left and top right PLL can also drive the two top edge clocks.

# **Edge Clock Routing**

LatticeECP3 devices have a number of high-speed edge clocks that are intended for use with the PIOs in the implementation of high-speed interfaces. There are six edge clocks per device: two edge clocks on each of the top, left, and right edges. Different PLL and DLL outputs are routed to the two muxes on the left and right sides of the device. In addition, the CLKINDEL signal (generated from the DLL Slave Delay Line block) is routed to all the edge clock muxes on the left and right sides of the device. Figure 2-20 shows the selection muxes for these clocks.

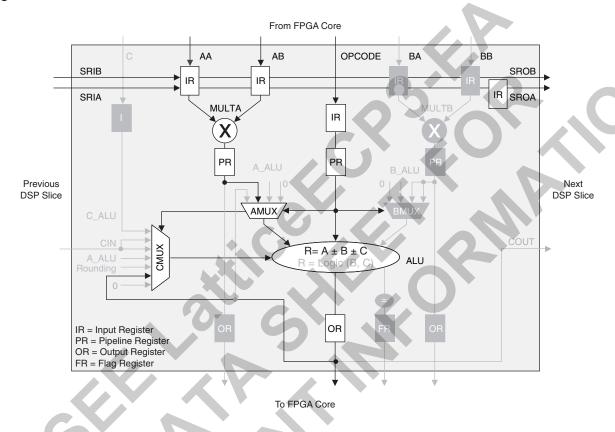

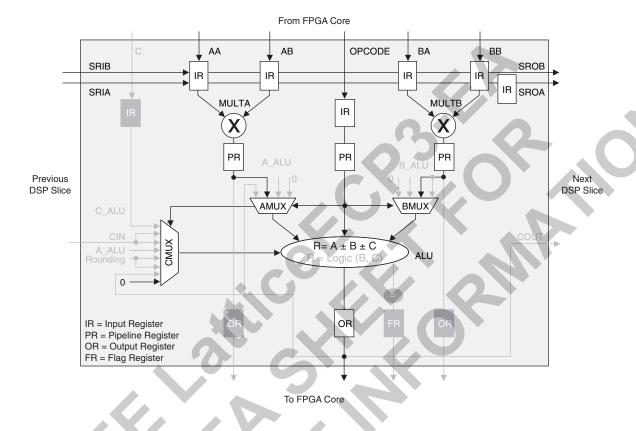

#### **MAC DSP Element**

In this case, the two operands, AA and AB, are multiplied and the result is added with the previous accumulated value. This accumulated value is available at the output. The user can enable the input and pipeline registers, but the output register is always enabled. The output register is used to store the accumulated value. The ALU is configured as the accumulator in the sysDSP slice in the LatticeECP3 family can be initialized dynamically. A registered overflow signal is also available. The overflow conditions are provided later in this document. Figure 2-27 shows the MAC sysDSP element.

Figure 2-27. MAC DSP Element

#### **MULTADDSUB DSP Element**

In this case, the operands AA and AB are multiplied and the result is added/subtracted with the result of the multiplier operation of operands BA and BB. The user can enable the input, output and pipeline registers. Figure 2-29 shows the MULTADDSUB sysDSP element.

Figure 2-29. MULTADDSUB

Two adjacent PIOs can be joined to provide a differential I/O pair (labeled as "T" and "C") as shown in Figure 2-32. The PAD Labels "T" and "C" distinguish the two PIOs. Approximately 50% of the PIO pairs on the left and right edges of the device can be configured as true LVDS outputs. All I/O pairs can operate as LVDS inputs.

Table 2-11. PIO Signal List

| Туре                          | Description                                                                                                                                                                                                                                                                         |

|-------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Input Data                    | Register bypassed input. This is not the same port as INCK.                                                                                                                                                                                                                         |

| Input Data                    | Ports to core for input data                                                                                                                                                                                                                                                        |

| Output Data                   | Output signals from core. An exception is the ONEGB port, used for tristate logic at the DQS pad.                                                                                                                                                                                   |

| PIO Control                   | Clock enables for input and output block flip-flops.                                                                                                                                                                                                                                |

| PIO Control                   | System Clock (PCLK) for input and output/TS blocks. Connected from clock ISB.                                                                                                                                                                                                       |

| PIO Control                   | Local Set/Reset                                                                                                                                                                                                                                                                     |

| PIO Control                   | Edge clock sources. Entire PIO selects one of two sources using mux.                                                                                                                                                                                                                |

| Read Control                  | From DQS_STROBE, shifted strobe for memory interfaces only.                                                                                                                                                                                                                         |

| Read Control                  | Ensures transfer from DQS domain to SCLK domain.                                                                                                                                                                                                                                    |

| Read Control                  | Used to guarantee INDDRX2 gearing by selectively enabling a D-Flip-Flop in datapath.                                                                                                                                                                                                |

| Read Control                  | Dynamic input delay control bits.                                                                                                                                                                                                                                                   |

| To Clock Distribution and PLL | PIO treated as clock PIO, path to distribute to primary clocks and PLL.                                                                                                                                                                                                             |

| Tristate Data                 | Tristate signal from core (SDR)                                                                                                                                                                                                                                                     |

| Write Control                 | Two clocks edges, 90 degrees out of phase, used in output gearing.                                                                                                                                                                                                                  |

| Write Control                 | Used for output and tristate logic at DQS only.                                                                                                                                                                                                                                     |

| Write Control                 | Shifting of write clocks for specific DQS group, using 6:0 each step is approximately 25ps, 128 steps. Bit 7 is an invert (timing depends on input frequency). There is also a static control for this 8-bit setting, enabled with a memory cell.                                   |

| PIO Control                   | Original delay code from DDR DLL                                                                                                                                                                                                                                                    |

| Output Data                   | Status flag from DATAVALID logic, used to indicate when input data is captured in IOLOGIC and valid to core.                                                                                                                                                                        |

| For DQS_Strobe                | Read signal for DDR memory interface                                                                                                                                                                                                                                                |

| For DQS_Strobe                | Unshifted DQS strobe from input pad                                                                                                                                                                                                                                                 |

| For DQS_Strobe                | DQSI biased to go high when DQSI is tristate, goes to input logic block as well as core logic.                                                                                                                                                                                      |

| Control from routing          | Global Set/Reset                                                                                                                                                                                                                                                                    |

|                               | Input Data Input Data Output Data Output Data PIO Control PIO Control PIO Control PIO Control Read Control Read Control Read Control To Clock Distribution and PLL Tristate Data Write Control Write Control Write Control Output Data For DQS_Strobe For DQS_Strobe For DQS_Strobe |

<sup>1.</sup> Signals available on left/right/top edges only.

#### PIO

The PIO contains four blocks: an input register block, output register block, tristate register block and a control logic block. These blocks contain registers for operating in a variety of modes along with the necessary clock and selection logic.

### Input Register Block

The input register blocks for the PIOs, in the left, right and top edges, contain delay elements and registers that can be used to condition high-speed interface signals, such as DDR memory interfaces and source synchronous interfaces, before they are passed to the device core. Figure 2-33 shows the input register block for the left, right and top edges. The input register block for the bottom edge contains one element to register the input signal and no DDR registers. The following description applies to the input register block for PIOs in the left, right and top edges only.

<sup>2.</sup> Selected PIO.

Table 2-14. Available SERDES Quads per LatticeECP3 Devices

| Package    | ECP3-17 | ECP3-35 | ECP3-70 | ECP3-95 | ECP3-150 |

|------------|---------|---------|---------|---------|----------|

| 256 ftBGA  | 1       | 1       | _       | _       | _        |

| 484 ftBGA  | 1       | 1       | 1       | 1       |          |

| 672 ftBGA  | _       | 1       | 2       | 2       | 2        |

| 1156 ftBGA | _       | _       | 3       | 3       | 4        |

#### **SERDES Block**

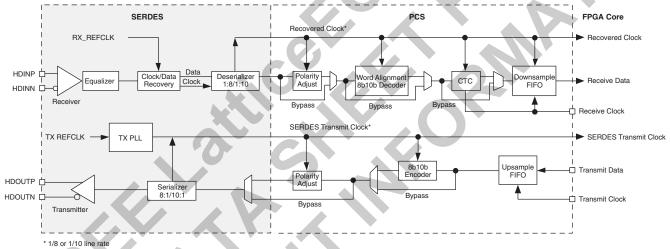

A SERDES receiver channel may receive the serial differential data stream, equalize the signal, perform Clock and Data Recovery (CDR) and de-serialize the data stream before passing the 8- or 10-bit data to the PCS logic. The SERDES transmitter channel may receive the parallel 8- or 10-bit data, serialize the data and transmit the serial bit stream through the differential drivers. Figure 2-41 shows a single-channel SERDES/PCS block. Each SERDES channel provides a recovered clock and a SERDES transmit clock to the PCS block and to the FPGA core logic.

Each transmit channel, receiver channel, and SERDES PLL shares the same power supply (VCCA). The output and input buffers of each channel have their own independent power supplies (VCCOB and VCCIB).

Figure 2-41. Simplified Channel Block Diagram for SERDES/PCS Block

#### **PCS**

As shown in Figure 2-41, the PCS receives the parallel digital data from the deserializer and selects the polarity, performs word alignment, decodes (8b/10b), provides Clock Tolerance Compensation and transfers the clock domain from the recovered clock to the FPGA clock via the Down Sample FIFO.

For the transmit channel, the PCS block receives the parallel data from the FPGA core, encodes it with 8b/10b, selects the polarity and passes the 8/10 bit data to the transmit SERDES channel.

The PCS also provides bypass modes that allow a direct 8-bit or 10-bit interface from the SERDES to the FPGA logic. The PCS interface to the FPGA can also be programmed to run at 1/2 speed for a 16-bit or 20-bit interface to the FPGA logic.

## SCI (SERDES Client Interface) Bus

The SERDES Client Interface (SCI) is an IP interface that allows the SERDES/PCS Quad block to be controlled by registers rather than the configuration memory cells. It is a simple register configuration interface that allows SERDES/PCS configuration without power cycling the device.

# sysl/O Single-Ended DC Electrical Characteristics

| Input/Output               | ,        | V <sub>IL</sub>          |                          | V <sub>IH</sub> |                             | V <sub>OH</sub>          |                        |                                   |

|----------------------------|----------|--------------------------|--------------------------|-----------------|-----------------------------|--------------------------|------------------------|-----------------------------------|

| Standard                   | Min. (V) | Max. (V)                 | Min. (V)                 | Max. (V)        | V <sub>OL</sub><br>Max. (V) | Min. (V)                 | I <sub>OL</sub> 1 (mA) | I <sub>OH</sub> <sup>1</sup> (mA) |

| LVCMOS33                   | -0.3     | 0.8                      | 2.0                      | 3.6             | 0.4                         | V <sub>CCIO</sub> - 0.4  | 20, 16,<br>12, 8, 4    | -20, -16,<br>-12, -8, -4          |

|                            |          |                          |                          |                 | 0.2                         | V <sub>CCIO</sub> - 0.2  | 0.1                    | -0.1                              |

| LVCMOS25                   | -0.3     | 0.7                      | 1.7                      | 3.6             | 0.4                         | V <sub>CCIO</sub> - 0.4  | 20, 16,<br>12, 8, 4    | -20, -16,<br>-12, -8, -4          |

|                            |          |                          |                          |                 | 0.2                         | V <sub>CCIO</sub> - 0.2  | 0.1                    | -0.1                              |

| LVCMOS18                   | -0.3     | 0.35 V <sub>CCIO</sub>   | 0.65 V <sub>CCIO</sub>   | 3.6             | 0.4                         | V <sub>CCIO</sub> - 0.4  | 16, 12,<br>8, 4        | -16, -12,<br>-8, -4               |

|                            |          |                          |                          |                 | 0.2                         | V <sub>CCIO</sub> - 0.2  | 0.1                    | -0.1                              |

| LVCMOS15                   | -0.3     | 0.35 V <sub>CCIO</sub>   | 0.65 V <sub>CCIO</sub>   | 3.6             | 0.4                         | V <sub>CCIO</sub> - 0.4  | 8, 4                   | -8, -4                            |

| 2701110010                 | 0.0      | 0.00 10010               | 0.00 10010               | 0.0             | 0.2                         | V <sub>CCIO</sub> - 0.2  | 0.1                    | -0.1                              |

| LVCMOS12                   | -0.3     | 0.35 V <sub>CC</sub>     | 0.65 V <sub>CC</sub>     | 3.6             | 0.4                         | V <sub>CCIO</sub> - 0.4  | 6, 2                   | -6, -2                            |

| 2701110012                 | 0.0      | 0.00 100                 | 0.00 100                 | 0.0             | 0.2                         | V <sub>CCIO</sub> - 0.2  | 0.1                    | -0.1                              |

| LVTTL33                    | -0.3     | 0.8                      | 2.0                      | 3.6             | 0.4                         | V <sub>CCIO</sub> - 0.4  | 20, 16,<br>12, 8, 4    | -20, -16,<br>-12, -8, -4          |

|                            |          |                          |                          |                 | 0.2                         | V <sub>CCIO</sub> - 0.2  | 0.1                    | -0.1                              |

| PCI33                      | -0.3     | 0.3 V <sub>CCIO</sub>    | 0.5 V <sub>CCIO</sub>    | 3.6             | 0.1 V <sub>CCIO</sub>       | 0.9 V <sub>CCIO</sub>    | 1.5                    | -0.5                              |

| SSTL18_I                   | -0.3     | V <sub>REF</sub> - 0.125 | V <sub>REF</sub> + 0.125 | 3.6             | 0.4                         | V <sub>CCIO</sub> - 0.4  | 6.7                    | -6.7                              |

| SSTL18_II<br>(DDR2 Memory) | -0.3     | V <sub>REF</sub> - 0.125 | V <sub>REF</sub> + 0.125 | 3.6             | 0.28                        | V <sub>CCIO</sub> - 0.28 | 8<br>11                | -8<br>-11                         |

|                            |          |                          |                          |                 |                             |                          | 7.6                    | -7.6                              |

| SSTL2_I                    | -0.3     | V <sub>REF</sub> - 0.18  | V <sub>REF</sub> + 0.18  | 3.6             | 0.54                        | V <sub>CCIO</sub> - 0.62 | 12                     | -12                               |

| SSTL2_II                   |          | '07                      |                          |                 |                             |                          | 15.2                   | -15.2                             |

| (DDR2 Memory)              | -0.3     | V <sub>REF</sub> - 0.18  | V <sub>REF</sub> + 0.18  | 3.6             | 0.35                        | V <sub>CCIO</sub> - 0.43 | 20                     | -20                               |

| SSTL3_I                    | -0.3     | V <sub>REF</sub> - 0.2   | V <sub>REF</sub> + 0.2   | 3.6             | 0.7                         | V <sub>CCIO</sub> - 1.1  | 8                      | -8                                |

| SSTL3_II                   | -0.3     | V <sub>REF</sub> - 0.2   | V <sub>REF</sub> + 0.2   | 3.6             | 0.5                         | V <sub>CCIO</sub> - 0.9  | 16                     | -16                               |

| SSTL15                     | -0.3     | V 0.1                    |                          | 3.6             | 0.3                         | V <sub>CCIO</sub> - 0.3  | 7.5                    | -7.5                              |

| (DDR3 Memory)              | -0.3     | V <sub>REF</sub> - 0.1   | V <sub>REF</sub> + 0.1   | 3.0             | 0.3                         | V <sub>CCIO</sub> * 0.8  | 9                      | -9                                |

| HSTL15_I                   | -0.3     | V <sub>REF</sub> - 0.1   | V <sub>REF</sub> + 0.1   | 3.6             | 0.4                         | V 0.4                    | 4                      | -4                                |

|                            | -0.3     | VREF - U. I              | VREF + 0.1               | 3.0             | 0.4                         | V <sub>CCIO</sub> - 0.4  | 8                      | -8                                |

| HSTL18_I                   | -0.3     | V <sub>REF</sub> - 0.1   | V <sub>REF</sub> + 0.1   | 3.6             | 0.4                         | V <sub>CCIO</sub> - 0.4  | 8                      | -8                                |

| 1101210_1                  | -0.0     | HEF - U.1                |                          | 0.0             | 0.4                         | CCIO - 0.4               | 12                     | -12                               |

| HSTL18_II                  | -0.3     | V <sub>REF</sub> - 0.1   | V <sub>REF</sub> + 0.1   | 3.6             | 0.4                         | V <sub>CCIO</sub> - 0.4  | 16                     | -16                               |

<sup>1.</sup> The average DC current drawn by I/Os between GND connections, or between the last GND in an I/O bank and the end of an I/O bank, as shown in the logic signal connections table shall not exceed n \* 8mA, where n is the number of I/Os between bank GND connections or between the last GND in a bank and the end of a bank.

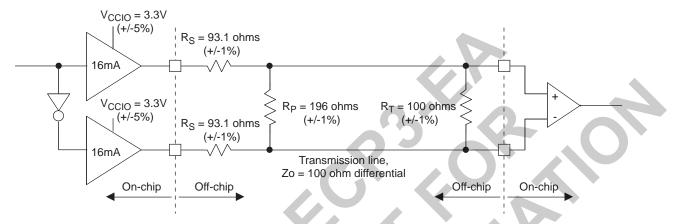

### LVPECL33

The LatticeECP3 devices support the differential LVPECL standard. This standard is emulated using complementary LVCMOS outputs in conjunction with a parallel resistor across the driver outputs. The LVPECL input standard is supported by the LVDS differential input buffer. The scheme shown in Figure 3-3 is one possible solution for point-to-point signals.

Figure 3-3. Differential LVPECL33

Table 3-3. LVPECL33 DC Conditions1

| Parameter         | Description                      | Typical | Units |

|-------------------|----------------------------------|---------|-------|

| V <sub>CCIO</sub> | Output Driver Supply (+/-5%)     | 3.30    | V     |

| Z <sub>OUT</sub>  | Driver Impedance                 | 10      | Ω     |

| R <sub>S</sub>    | Driver Series Resistor (+/-1%)   | 93      | Ω     |

| R <sub>P</sub>    | Driver Parallel Resistor (+/-1%) | 196     | Ω     |

| R <sub>T</sub>    | Receiver Termination (+/-1%)     | 100     | Ω     |

| V <sub>OH</sub>   | Output High Voltage              | 2.05    | V     |

| V <sub>OL</sub>   | Output Low Voltage               | 1.25    | V     |

| V <sub>OD</sub>   | Output Differential Voltage      | 0.80    | V     |

| $V_{CM}$          | Output Common Mode Voltage       | 1.65    | V     |

| Z <sub>BACK</sub> | Back Impedance                   | 100.5   | Ω     |

| I <sub>DC</sub>   | DC Output Current                | 12.11   | mA    |

<sup>1.</sup> For input buffer, see LVDS table.

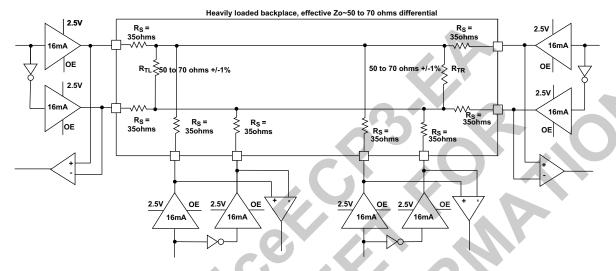

#### MLVDS25

The LatticeECP3 devices support the differential MLVDS standard. This standard is emulated using complementary LVCMOS outputs in conjunction with a parallel resistor across the driver outputs. The MLVDS input standard is supported by the LVDS differential input buffer. The scheme shown in Figure 3-5 is one possible solution for MLVDS standard implementation. Resistor values in Figure 3-5 are industry standard values for 1% resistors.

Figure 3-5. MLVDS25 (Multipoint Low Voltage Differential Signaling)

Table 3-5. MLVDS25 DC Conditions<sup>1</sup>

|                   | X V                              | Typical        |                |       |

|-------------------|----------------------------------|----------------|----------------|-------|

| Parameter         | Description                      | <b>Zo=50</b> Ω | <b>Z</b> o=70Ω | Units |

| V <sub>CCIO</sub> | Output Driver Supply (+/-5%)     | 2.50           | 2.50           | V     |

| Z <sub>OUT</sub>  | Driver Impedance                 | 10.00          | 10.00          | Ω     |

| R <sub>S</sub>    | Driver Series Resistor (+/-1%)   | 35.00          | 35.00          | Ω     |

| R <sub>TL</sub>   | Driver Parallel Resistor (+/-1%) | 50.00          | 70.00          | Ω     |

| R <sub>TR</sub>   | Receiver Termination (+/-1%)     | 50.00          | 70.00          | Ω     |

| V <sub>OH</sub>   | Output High Voltage              | 1.52           | 1.60           | V     |

| V <sub>OL</sub>   | Output Low Voltage               | 0.98           | 0.90           | V     |

| $V_{OD}$          | Output Differential Voltage      | 0.54           | 0.70           | V     |

| V <sub>CM</sub>   | Output Common Mode Voltage       | 1.25           | 1.25           | V     |

| I <sub>DC</sub>   | DC Output Current                | 21.74          | 20.00          | mA    |

<sup>1.</sup> For input buffer, see LVDS table.

# sysCLOCK PLL Timing

| Parameter                      | Descriptions                                        | Conditions                         | Clock         | Min.    | Тур. | Max.  | Units       |

|--------------------------------|-----------------------------------------------------|------------------------------------|---------------|---------|------|-------|-------------|

| 4                              | Input clock frequency (CLKI,                        |                                    | Edge clock    | 2       | _    | 500   | MHz         |

| f <sub>IN</sub>                | CLKFB)                                              |                                    | Primary clock | 2       | _    | 420   | MHz         |

| f.                             | Output clock frequency (CLKOP,                      |                                    | Edge clock    | 4       | _    | 500   | MHz         |

| TOUT                           | CLKOS)                                              |                                    | Primary clock | 4       | _    | 420   | MHz         |

| f <sub>OUT1</sub>              | K-Divider output frequency                          | CLKOK                              |               | 0.03125 | _    | 250   | MHz         |

| f <sub>OUT2</sub>              | K2-Divider output frequency                         | CLKOK2                             |               | 0.667   | _    | 166   | MHz         |

| $f_{VCO}$                      | PLL VCO frequency                                   |                                    |               | 500     | _    | 1000  | MHz         |

| f <sub>PFD</sub> <sup>3</sup>  | Phase detector input frequency                      |                                    | Edge clock    | 2       | _    | 500   | MHz         |

|                                |                                                     |                                    | Primary clock | 2       | _    | 420   | MHz         |

| AC Charac                      | teristics                                           |                                    |               | 1       |      |       |             |

| t <sub>PA</sub>                | Programmable delay unit                             |                                    |               | 65      | 130  | 260   | ps          |

|                                | 0                                                   |                                    | Edge clock    | 45      | 50   | 55    | %           |

| t <sub>DT</sub>                | Output clock duty cycle (CLKOS, at 50% setting)     | f <sub>OUT</sub> ≤ 250 MHz         | Primary clock | 45      | 50   | 55    | %           |

|                                | (02:100, at 00 /0 001g)                             | f <sub>OUT</sub> > 250MHz          | Primary clock | 30      | 50   | 70    | %           |

| t <sub>CPA</sub>               | Coarse phase shift error (CLKOS, at all settings)   |                                    |               | -5      | 0    | +5    | % of period |

| t <sub>OPW</sub>               | Output clock pulse width high or low (CLKOS)        | CON                                | 10            | 1.8     | _    | _     | ns          |

|                                |                                                     | f <sub>OUT</sub> ≥ 420MHz          |               | _       | _    | 200   | р-р         |

| t <sub>OPJIT</sub> 1           | Output clock period jitter                          | 420MHz > f <sub>OUT</sub> ≥ 100MHz |               | _       | _    | 250   | р-р         |

|                                |                                                     | f <sub>OUT</sub> < 100MHz          |               | _       | _    | 0.025 | UIPP        |

| t <sub>SK</sub>                | Input clock to output clock skew when N/M = integer | 2                                  |               | _       | _    | 500   | р-р         |

| <b>.</b> 2                     | Lock time                                           | 2 to 25 MHz                        |               | _       | _    | 200   | us          |

| t <sub>LOCK</sub> <sup>2</sup> | Lock time                                           | 25 to 500 MHz                      |               | _       | _    | 50    | us          |

| t <sub>UNLOCK</sub>            | Reset to PLL unlock time to ensure fast reset       |                                    |               | _       | _    | 50    | ns          |

| t <sub>HI</sub>                | Input clock high time                               | 90% to 90%                         |               | 0.5     | _    | _     | ns          |

| t <sub>LO</sub>                | Input clock low time                                | 10% to 10%                         |               | 0.5     | _    | _     | ns          |

| t <sub>IPJIT</sub>             | Input clock period jitter                           |                                    |               | _       | _    | 400   | р-р         |

| t <sub>RST</sub>               | Reset signal pulse width high,<br>RESETM,<br>RESETK |                                    |               | 10      | _    | _     | ns          |

|                                | Reset signal pulse width high, CNTRST               |                                    |               | 500     | _    | _     | ns          |

<sup>1.</sup> Jitter sample is taken over 10,000 samples of the primary PLL output with clean reference clock with no additional I/O toggling.

Output clock is valid after t<sub>LOCK</sub> for PLL reset and dynamic delay adjustment.

Period jitter and cycle-to-cycle jitter numbers are guaranteed for f<sub>PFD</sub> > 4MHz. For f<sub>PFD</sub> < 4MHz, the jitter numbers may not be met in certain conditions. Please contact the factory for f<sub>PFD</sub> < 4MHz.</li>

# **PCI Express Electrical and Timing Characteristics AC and DC Characteristics**

| Symbol                                   | Description                                                                           | <b>Test Conditions</b>                               | Min        | Тур      | Max                    | Units |

|------------------------------------------|---------------------------------------------------------------------------------------|------------------------------------------------------|------------|----------|------------------------|-------|

| Transmit <sup>1</sup>                    |                                                                                       | 1                                                    |            |          | l .                    |       |

| UI                                       | Unit interval                                                                         |                                                      | 399.88     | 400      | 400.12                 | ps    |

| V <sub>TX-DIFF_P-P</sub>                 | Differential peak-to-peak output voltage                                              |                                                      | 0.8        | 1.0      | 1.2                    | V     |

| V <sub>TX-DE-RATIO</sub>                 | De-emphasis differential output voltage ratio                                         |                                                      | -3         | -3.5     | -4                     | dB    |

| V <sub>TX-CM-AC_P</sub>                  | RMS AC peak common-mode output voltage                                                |                                                      |            | 1        | 20                     | mV    |

| V <sub>TX-RCV-DETECT</sub>               | Amount of voltage change allowed during receiver detection                            | 0                                                    |            |          | 600                    | mV    |

| $V_{TX-DC-CM}$                           | Tx DC common mode voltage                                                             |                                                      | 0          | 1        | V <sub>CCOB</sub> + 5% | V     |

| I <sub>TX-SHORT</sub>                    | Output short circuit current                                                          | V <sub>TX-D+</sub> =0.0V<br>V <sub>TX-D-</sub> =0.0V |            | _        | 90                     | mA    |

| Z <sub>TX-DIFF-DC</sub>                  | Differential output impedance                                                         |                                                      | 80         | 100      | 120                    | Ohms  |

| RL <sub>TX-DIFF</sub>                    | Differential return loss                                                              |                                                      | 10         |          | _                      | dB    |

| RL <sub>TX-CM</sub>                      | Common mode return loss                                                               |                                                      | 6.0        |          | _                      | dB    |

| T <sub>TX-RISE</sub>                     | Tx output rise time                                                                   | 20 to 80%                                            | 0.125      |          | _                      | UI    |

| T <sub>TX-FALL</sub>                     | Tx output fall time                                                                   | 20 to 80%                                            | 0.125      | <u> </u> | _                      | UI    |

| L <sub>TX-SKEW</sub>                     | Lane-to-lane static output skew for all lanes in port/link                            |                                                      | 1          | _        | 1.3                    | ns    |

| T <sub>TX-EYE</sub>                      | Transmitter eye width                                                                 |                                                      | 0.75       | _        | _                      | UI    |

| T <sub>TX-EYE-MEDIAN-TO-MAX-JITTER</sub> | Maximum time between jitter median and maximum deviation from median                  |                                                      | _          | _        | 0.125                  | UI    |

| Receive <sup>1, 2</sup>                  |                                                                                       |                                                      |            |          |                        |       |

| UI                                       | Unit Interval                                                                         |                                                      | 399.88     | 400      | 400.12                 | ps    |

| V <sub>RX-DIFF_P-P</sub>                 | Differential peak-to-peak input voltage                                               |                                                      | $0.34^{3}$ | _        | 1.2                    | V     |

| V <sub>RX-IDLE-DET-DIFF_P-P</sub>        | Idle detect threshold voltage                                                         |                                                      | 65         | 1        | 340 <sup>3</sup>       | mV    |

| V <sub>RX-CM-AC_P</sub>                  | Receiver common mode voltage for AC coupling                                          |                                                      |            | _        | 150                    | mV    |

| Z <sub>RX-DIFF-DC</sub>                  | DC differential input impedance                                                       |                                                      | 80         | 100      | 120                    | Ohms  |

| Z <sub>RX-DC</sub>                       | DC input impedance                                                                    |                                                      | 40         | 50       | 60                     | Ohms  |

| Z <sub>RX-HIGH-IMP-DC</sub>              | Power-down DC input impedance                                                         |                                                      | 200K       | _        | _                      | Ohms  |

| RL <sub>RX-DIFF</sub>                    | Differential return loss                                                              |                                                      | 10         |          | _                      | dB    |

| RL <sub>RX-CM</sub>                      | Common mode return loss                                                               |                                                      | 6.0        | _        | _                      | dB    |

| T <sub>RX-IDLE-DET-DIFF-ENTERTIME</sub>  | Maximum time required for receiver to recognize and signal an unexpected idle on link |                                                      |            |          | _                      | ms    |

<sup>1.</sup> Values are measured at 2.5 Gbps.

<sup>2.</sup> Measured with external AC-coupling on the receiver.

<sup>3.</sup>Not in compliance with PCI Express 1.1 standard.

# **XAUI/Serial Rapid I/O Type 3 Electrical and Timing Characteristics AC and DC Characteristics**

Table 3-13. Transmit

#### **Over Recommended Operating Conditions**

| Symbol                                   | Description                      | Test Conditions | Min.           | Тур. | Max. | Units |

|------------------------------------------|----------------------------------|-----------------|----------------|------|------|-------|

| T <sub>RF</sub>                          | Differential rise/fall time      | 20%-80%         | _              | 80   | _    | ps    |

| Z <sub>TX_DIFF_DC</sub>                  | Differential impedance           |                 | 80             | 100  | 120  | Ohms  |

| J <sub>TX_DDJ</sub> <sup>2, 3, 4</sup>   | Output data deterministic jitter |                 | <del>-</del> \ | 35   | 0.17 | UI    |

| J <sub>TX_TJ</sub> <sup>1, 2, 3, 4</sup> | Total output data jitter         |                 |                | _    | 0.35 | UI    |

- 1. Total jitter includes both deterministic jitter and random jitter.

- 2. Jitter values are measured with each CML output AC coupled into a 50-ohm impedance (100-ohm differential impedance).

- 3. Jitter and skew are specified between differential crossings of the 50% threshold of the reference signal.

- 4. Values are measured at 2.5 Gbps.

Table 3-14. Receive and Jitter Tolerance

| Symbol                                | Description                                   | Test Conditions              | Min. | Тур. | Max. | Units |

|---------------------------------------|-----------------------------------------------|------------------------------|------|------|------|-------|

| RL <sub>RX_DIFF</sub>                 | Differential return loss                      | From 100 MHz<br>to 3.125 GHz | 10   | V-L  | _    | dB    |

| RL <sub>RX_CM</sub>                   | Common mode return loss                       | From 100 MHz<br>to 3.125 GHz | 6    |      | _    | dB    |

| Z <sub>RX_DIFF</sub>                  | Differential termination resistance           |                              | 80   | 100  | 120  | Ohms  |

| J <sub>RX_DJ</sub> <sup>1, 2, 3</sup> | Deterministic jitter tolerance (peak-to-peak) |                              | 1    | _    | 0.37 | UI    |

| J <sub>RX_RJ</sub> <sup>1, 2, 3</sup> | Random jitter tolerance (peak-to-peak)        |                              | )-   | _    | 0.18 | UI    |

| J <sub>RX_SJ</sub> <sup>1, 2, 3</sup> | Sinusoidal jitter tolerance (peak-to-peak)    |                              |      | _    | 0.10 | UI    |

| J <sub>RX_TJ</sub> <sup>1, 2, 3</sup> | Total jitter tolerance (peak-to-peak)         |                              |      | _    | 0.65 | UI    |

| T <sub>RX_EYE</sub>                   | Receiver eye opening                          |                              | 0.35 | _    | _    | UI    |

- 1. Total jitter includes deterministic jitter, random jitter and sinusoidal jitter. The sinusoidal jitter tolerance mask is shown in Figure 3-14.

- 2. Jitter values are measured with each high-speed input AC coupled into a 50-ohm impedance.

- 3. Jitter and skew are specified between differential crossings of the 50% threshold of the reference signal.

- 4. Jitter tolerance parameters are characterized when Full Rx Equalization is enabled.

- 5. Values are measured at 2.5 Gbps.

# Gigabit Ethernet/Serial Rapid I/O Type 1/SGMII Electrical and Timing Characteristics

#### **AC and DC Characteristics**

## Table 3-17. Transmit

| Symbol                                   | Description                      | Test Conditions | Min. | Тур. | Max. | Units |

|------------------------------------------|----------------------------------|-----------------|------|------|------|-------|

| T <sub>RF</sub>                          | Differential rise/fall time      | 20%-80%         | _    | 80   | _    | ps    |

| Z <sub>TX_DIFF_DC</sub>                  | Differential impedance           |                 | 80   | 100  | 120  | Ohms  |

| J <sub>TX_DDJ</sub> <sup>3, 4, 5</sup>   | Output data deterministic jitter |                 |      | 1    | 0.10 | UI    |

| J <sub>TX_TJ</sub> <sup>2, 3, 4, 5</sup> | Total output data jitter         |                 | /- V | _    | 0.24 | UI    |

- 1. Rise and fall times measured with board trace, connector and approximately 2.5pf load.

- 2. Total jitter includes both deterministic jitter and random jitter. The random jitter is the total jitter minus the actual deterministic jitter.

- 3. Jitter values are measured with each CML output AC coupled into a 50-ohm impedance (100-ohm differential impedance).

- 4. Jitter and skew are specified between differential crossings of the 50% threshold of the reference signal.

- 5. Values are measured at 1.25 Gbps.

#### Table 3-18. Receive and Jitter Tolerance

| Symbol                                      | Description                                   | Test Conditions          | Min. | Тур.       | Max. | Units |

|---------------------------------------------|-----------------------------------------------|--------------------------|------|------------|------|-------|

| RL <sub>RX_DIFF</sub>                       | Differential return loss                      | From 100 MHz to 1.25 GHz | 10   |            | _    | dB    |

| RL <sub>RX_CM</sub>                         | Common mode return loss                       | From 100 MHz to 1.25 GHz | 6    | \ <u> </u> | _    | dB    |

| Z <sub>RX_DIFF</sub>                        | Differential termination resistance           |                          | 80   | 100        | 120  | Ohms  |

|                                             | Deterministic jitter tolerance (peak-to-peak) |                          | 7    | _          | 0.34 | UI    |

|                                             | Random jitter tolerance (peak-to-peak)        |                          |      | _          | 0.26 | UI    |

|                                             | Sinusoidal jitter tolerance (peak-to-peak)    |                          | _    | _          | 0.11 | UI    |

| J <sub>RX_TJ</sub> <sup>1, 2, 3, 4, 5</sup> | Total jitter tolerance (peak-to-peak)         |                          | _    | —          | 0.71 | UI    |

| T <sub>RX EYE</sub>                         | Receiver eye opening                          |                          | 0.29 | _          | _    | UI    |

- 1. Total jitter includes deterministic jitter, random jitter and sinusoidal jitter. The sinusoidal jitter tolerance mask is shown in Figure 3-14.

- 2. Jitter values are measured with each high-speed input AC coupled into a 50-ohm impedance.

- 3. Jitter and skew are specified between differential crossings of the 50% threshold of the reference signal.

- 4. Jitter tolerance, Differential Input Sensitivity and Receiver Eye Opening parameters are characterized when Full Rx Equalization is enabled.

- 5. Values are measured at 1.25 Gbps.

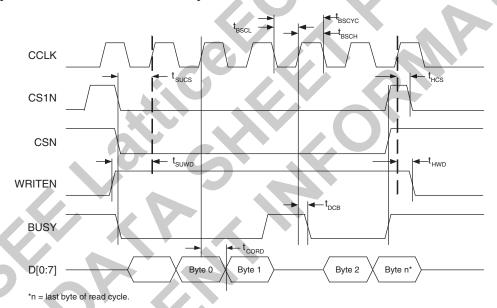

# **LatticeECP3 sysCONFIG Port Timing Specifications**

| Parameter            | Description                                                                                                                                    |                    | Min.     | Max.     | Units  |

|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|----------|----------|--------|

| POR, Confi           | guration Initialization, and Wakeup                                                                                                            |                    |          |          |        |

|                      | Time from the Application of $V_{CC}$ , $V_{CCAUX}$ or $V_{CCIO8}^*$ (Whichever is the Last to Cross the POR Trip Point) to the Rising Edge of | Master mode        | _        | 23       | ms     |

| t <sub>ICFG</sub>    | is the Last to Cross the POR Trip Point) to the Rising Edge of INITN                                                                           | Slave mode         |          | 6        | ms     |

| t <sub>VMC</sub>     | Time from t <sub>ICFG</sub> to the Valid Master MCLK                                                                                           |                    | _        | 5        | μs     |

| t <sub>PRGM</sub>    | PROGRAMN Low Time to Start Configuration                                                                                                       | 25                 | _        | ns       |        |

| t <sub>PRGMRJ</sub>  | PROGRAMN Pin Pulse Rejection                                                                                                                   |                    | _        | 10       | ns     |

| t <sub>DPPINIT</sub> | Delay Time from PROGRAMN Low to INITN Low                                                                                                      |                    | _        | 37       | ns     |

| t <sub>DPPDONE</sub> | Delay Time from PROGRAMN Low to DONE Low                                                                                                       | _                  | 37       | ns       |        |

| t <sub>DINIT</sub>   | PROGRAMN High to INITN High Delay                                                                                                              | 5                  |          | 1        | ms     |

| t <sub>MWC</sub>     | Additional Wake Master Clock Signals After DONE Pin is High                                                                                    |                    | 100      | 500      | cycles |

| t <sub>CZ</sub>      | MCLK From Active To Low To High-Z                                                                                                              |                    |          | 300      | ns     |

| All Configu          | ration Modes                                                                                                                                   |                    |          |          |        |

| t <sub>SUCDI</sub>   | Data Setup Time to CCLK/MCLK                                                                                                                   |                    | 5        | <u> </u> | ns     |

| t <sub>HCDI</sub>    | Data Hold Time to CCLK/MCLK                                                                                                                    |                    | 1        | -        | ns     |

| t <sub>CODO</sub>    | CCLK/MCLK to DOUT in Flowthrough Mode                                                                                                          |                    | -        | 12       | ns     |

| Slave Seria          |                                                                                                                                                |                    |          |          | ı      |

| t <sub>SSCH</sub>    | CCLK Minimum High Pulse                                                                                                                        |                    | 5        | _        | ns     |

| t <sub>SSCL</sub>    | CCLK Minimum Low Pulse                                                                                                                         |                    | 5        | _        | ns     |

| JOOL                 | Without encryption                                                                                                                             |                    |          | 33       | MHz    |

| f <sub>CCLK</sub>    | CCLK Frequency                                                                                                                                 | With encryption    | _        | 20       | MHz    |

| Master and           | Slave Parallel                                                                                                                                 | 71                 |          |          |        |

| t <sub>SUCS</sub>    | CSN[1:0] Setup Time to CCLK/MCLK                                                                                                               |                    | 7        | _        | ns     |

| t <sub>HCS</sub>     | CSN[1:0] Hold Time to CCLK/MCLK                                                                                                                |                    | 1        | _        | ns     |

| t <sub>SUWD</sub>    | WRITEN Setup Time to CCLK/MCLK                                                                                                                 |                    | 7        | _        | ns     |

| t <sub>HWD</sub>     | WRITEN Hold Time to CCLK/MCLK                                                                                                                  |                    | 1        | _        | ns     |

| t <sub>DCB</sub>     | CCLK/MCLK to BUSY Delay Time                                                                                                                   |                    | _        | 12       | ns     |

| t <sub>CORD</sub>    | CCLK to Out for Read Data                                                                                                                      |                    | _        | 12       | ns     |

| t <sub>BSCH</sub>    | CCLK Minimum High Pulse                                                                                                                        |                    | 6        | <u> </u> | ns     |

| t <sub>BSCL</sub>    | CCLK Minimum Low Pulse                                                                                                                         |                    | 6        | _        | ns     |

| t <sub>BSCYC</sub>   | Byte Slave Cycle Time                                                                                                                          |                    | 30       | <u> </u> | ns     |

|                      |                                                                                                                                                | Without encryption | _        | 33       | MHz    |

| f <sub>CCLK</sub>    | CCLK/MCLK Frequency                                                                                                                            | With encryption    | _        | 20       | MHz    |

| Master and           | Slave SPI                                                                                                                                      |                    |          | 1        | ı      |

| t <sub>CFGX</sub>    | INITN High to MCLK Low                                                                                                                         |                    | _        | 80       | ns     |

| t <sub>CSSPI</sub>   | INITN High to CSSPIN Low                                                                                                                       | 0.2                | 2        | μs       |        |

| t <sub>SOCDO</sub>   | MCLK Low to Output Valid                                                                                                                       | _                  | 15       | ns       |        |

| t <sub>CSPID</sub>   | CSSPIN[0:1] Low to First MCLK Edge Setup Time                                                                                                  | 0.3                |          | μs       |        |

|                      | Without encryption                                                                                                                             |                    |          | 33       | MHz    |

| f <sub>CCLK</sub>    | CCLK Frequency                                                                                                                                 | With encryption    | _        | 20       | MHz    |

| t <sub>SSCH</sub>    | CCLK Minimum High Pulse                                                                                                                        | 5                  | <u> </u> | ns       |        |

| t <sub>SSCL</sub>    | CCLK Minimum Low Pulse                                                                                                                         |                    | 5        | <u> </u> | ns     |

| t <sub>HLCH</sub>    | HOLDN Low Setup Time (Relative to CCLK)                                                                                                        |                    | 5        | _        | ns     |

# **LatticeECP3 sysCONFIG Port Timing Specifications (Continued)**

| Parameter         | Description                              | Min. | Max. | Units |

|-------------------|------------------------------------------|------|------|-------|

| t <sub>CHHH</sub> | HOLDN Low Hold Time (Relative to CCLK)   | 5    | _    | ns    |

| Master and        | Slave SPI (Continued)                    |      |      |       |

| t <sub>CHHL</sub> | HOLDN High Hold Time (Relative to CCLK)  | 5    |      | ns    |

| t <sub>HHCH</sub> | HOLDN High Setup Time (Relative to CCLK) | 5    | _    | ns    |

| t <sub>HLQZ</sub> | HOLDN to Output High-Z                   | _    | 9    | ns    |

| t <sub>HHQX</sub> | HOLDN to Output Low-Z                    | _    | 9    | ns    |

| Parameter              | Min.                 | Max.                 | Units |

|------------------------|----------------------|----------------------|-------|

| Master Clock Frequency | Selected value - 15% | Selected value + 15% | MHz   |

| Duty Cycle             | 40                   | 60                   | %     |

Figure 3-16. sysCONFIG Parallel Port Read Cycle

# **Pin Information Summary**

| Pin Information                            | Summary | ECP3         | -17EA        | E            | CP3-35E      | Α            | ECP3-70E/EA  |              |               |

|--------------------------------------------|---------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|---------------|

| Pin Typ                                    | e       | 256<br>ftBGA | 484<br>fpBGA | 256<br>ftBGA | 484<br>fpBGA | 672<br>fpBGA | 484<br>fpBGA | 672<br>fpBGA | 1156<br>fpBGA |

|                                            | Bank 0  | 26           | 36           | 26           | 42           | 48           | 42           | 60           | 86            |

|                                            | Bank 1  | 14           | 24           | 14           | 36           | 36           | 36           | 48           | 78            |

| 0 15                                       | Bank 2  | 6            | 12           | 6            | 24           | 24           | 24           | 34           | 36            |

| General Purpose<br>Inputs/Outputs per Bank | Bank 3  | 18           | 44           | 16           | 54           | 59           | 54           | 59           | 86            |

|                                            | Bank 6  | 20           | 44           | 18           | 63           | 61           | 63           | 67           | 86            |

|                                            | Bank 7  | 19           | 32           | 19           | 36           | 42           | 36           | 48           | 54            |

|                                            | Bank 8  | 24           | 24           | 24           | 24           | 24           | 24           | 24           | 24            |

|                                            | Bank 0  | 0            | 0            | 0            | 0            | 0            | 0            | 0            | 0             |

|                                            | Bank 1  | 0            | 0            | 0            | 0            | 0            | 0            | 0            | 0             |

|                                            | Bank 2  | 2            | 2            | 2            | 4            | 4            | 4            | 8            | 8             |

| General Purpose Inputs per Bank            | Bank 3  | 0            | 0            | 2            | 4            | 4            | 4            | 12           | 12            |

| Dank                                       | Bank 6  | 0            | 0            | 2            | 4            | 4            | 4            | 12           | 12            |

|                                            | Bank 7  | 4            | 4            | 4            | 4            | 4            | 4            | 8            | 8             |

|                                            | Bank 8  | 0            | 0            | 0            | 0            | 0            | 0            | 0            | 0             |

|                                            | Bank 0  | 0            | 0            | 0            | 0            | 0            | 0            | 0            | 0             |

|                                            | Bank 1  | 0            | 0            | 0            | 0            | 0            | 0            | 0            | 0             |

|                                            | Bank 2  | 0            | 0            | 0            | 0            | 0            | 0            | 0            | 0             |

| General Purpose Outputs per Bank           | Bank 3  | 0            | 0            | 0            | 0            | 0            | 0            | 0            | 0             |

| Dank                                       | Bank 6  | 0            | 0            | 0            | 0            | 0            | 0            | 0            | 0             |

|                                            | Bank 7  | 0            | 0            | 0            | 0            | 0            | 0            | 0            | 0             |

|                                            | Bank 8  | 0            | 0            | 0            | 0            | 0            | 0            | 0            | 0             |

| Total Single-Ended User I/O                |         | 133          | 222          | 133          | 295          | 310          | 295          | 380          | 490           |

| VCC                                        |         | 6            | 16           | 6            | 16           | 32           | 16           | 32           | 32            |

| VCCAUX                                     |         | 4            | 8            | 4            | 8            | 12           | 8            | 12           | 16            |

| VTT                                        |         | 4            | 4            | 4            | 4            | 4            | 4            | 4            | 8             |

| VCCA                                       |         | 4            | 4            | 4            | 4            | 8            | 4            | 8            | 16            |

| VCCPLL                                     |         | 2            | 4            | 2            | 4            | 4            | 4            | 4            | 4             |

|                                            | Bank 0  | 2            | 2            | 2            | 2            | 4            | 2            | 4            | 4             |

|                                            | Bank 1  | 2            | 2            | 2            | 2            | 4            | 2            | 4            | 4             |

|                                            | Bank 2  | 2            | 2            | 2            | 2            | 4            | 2            | 4            | 4             |

| VCCIO                                      | Bank 3  | 2            | 2            | 2            | 2            | 4            | 2            | 4            | 4             |

|                                            | Bank 6  | 2            | 2            | 2            | 2            | 4            | 2            | 4            | 4             |

|                                            | Bank 7  | 2            | 2            | 2            | 2            | 4            | 2            | 4            | 4             |

|                                            | Bank 8  | 2            | 2            | 2            | 2            | 2            | 2            | 2            | 2             |

| VCCJ                                       |         | 1            | 1            | 1            | 1            | 1            | 1            | 1            | 1             |

| TAP                                        |         | 4            | 4            | 4            | 4            | 4            | 4            | 4            | 4             |

| GND, GNDIO                                 |         | 50           | 98           | 50           | 98           | 139          | 98           | 139          | 233           |

| NC                                         |         | 0            | 73           | 0            | 0            | 96           | 0            | 0            | 238           |

| Reserved <sup>1</sup>                      |         | 0            | 2            | 0            | 2            | 2            | 2            | 2            | 2             |

| SERDES                                     |         | 26           | 26           | 26           | 26           | 26           | 26           | 52           | 78            |

| Miscellaneous Pins                         |         | 8            | 8            | 8            | 8            | 8            | 8            | 8            | 8             |

| Total Bonded Pins                          |         | 256          | 484          | 256          | 484          | 672          | 484          | 672          | 1156          |

# LatticeECP3 Devices, Lead-Free Packaging

The following devices may have associated errata. Specific devices with associated errata will be notated with a footnote.

#### Commercial

| Part Number        | Voltage | Grade | Package         | Pins | Temp. | LUTs (K) |

|--------------------|---------|-------|-----------------|------|-------|----------|

| LFE3-17EA-6FTN256C | 1.2V    | -6    | Lead-Free ftBGA | 256  | COM   | 17       |

| LFE3-17EA-7FTN256C | 1.2V    | -7    | Lead-Free ftBGA | 256  | COM   | 17       |

| LFE3-17EA-8FTN256C | 1.2V    | -8    | Lead-Free ftBGA | 256  | COM   | 17       |

| LFE3-17EA-6FN484C  | 1.2V    | -6    | Lead-Free fpBGA | 484  | COM   | 17       |

| LFE3-17EA-7FN484C  | 1.2V    | -7    | Lead-Free fpBGA | 484  | COM   | 17       |

| LFE3-17EA-8FN484C  | 1.2V    | -8    | Lead-Free fpBGA | 484  | COM   | 17       |

| Part Number        | Voltage | Grade | Package         | Pins | Temp. | LUTs (K) |

|--------------------|---------|-------|-----------------|------|-------|----------|

| LFE3-35EA-6FTN256C | 1.2V    | -6    | Lead-Free ftBGA | 256  | COM   | 33       |

| LFE3-35EA-7FTN256C | 1.2V    | -7    | Lead-Free ftBGA | 256  | СОМ   | 33       |

| LFE3-35EA-8FTN256C | 1.2V    | -8    | Lead-Free ftBGA | 256  | COM   | 33       |

| LFE3-35EA-6FN484C  | 1.2V    | -6    | Lead-Free fpBGA | 484  | СОМ   | 33       |

| LFE3-35EA-7FN484C  | 1.2V    | -7    | Lead-Free fpBGA | 484  | COM   | 33       |

| LFE3-35EA-8FN484C  | 1.2V    | -8    | Lead-Free fpBGA | 484  | СОМ   | 33       |

| LFE3-35EA-6FN672C  | 1.2V    | -6    | Lead-Free fpBGA | 672  | СОМ   | 33       |

| LFE3-35EA-7FN672C  | 1.2V    | -7    | Lead-Free fpBGA | 672  | COM   | 33       |

| LFE3-35EA-8FN672C  | 1.2V    | -8    | Lead-Free fpBGA | 672  | COM   | 33       |

| Part Number        | Voltage | Grade | Package         | Pins | Temp. | LUTs (K) |

|--------------------|---------|-------|-----------------|------|-------|----------|

| LFE3-70EA-6FN484C  | 1.2V    | -6    | Lead-Free fpBGA | 484  | COM   | 67       |

| LFE3-70EA-7FN484C  | 1.2V    | -7    | Lead-Free fpBGA | 484  | COM   | 67       |

| LFE3-70EA-8FN484C  | 1.2V    | -8    | Lead-Free fpBGA | 484  | COM   | 67       |

| LFE3-70EA-6FN672C  | 1.2V    | -6    | Lead-Free fpBGA | 672  | COM   | 67       |

| LFE3-70EA-7FN672C  | 1.2V    | -7    | Lead-Free fpBGA | 672  | COM   | 67       |

| LFE3-70EA-8FN672C  | 1.2V    | -8    | Lead-Free fpBGA | 672  | COM   | 67       |

| LFE3-70EA-6FN1156C | 1.2V    | -6    | Lead-Free fpBGA | 1156 | COM   | 67       |

| LFE3-70EA-7FN1156C | 1.2V    | -7    | Lead-Free fpBGA | 1156 | COM   | 67       |

| LFE3-70EA-8FN1156C | 1.2V    | -8    | Lead-Free fpBGA | 1156 | COM   | 67       |

### Industrial

The following devices may have associated errata. Specific devices with associated errata will be notated with a footnote.

| Part Number        | Voltage | Grade | Package         | Pins | Temp. | LUTs (K) |

|--------------------|---------|-------|-----------------|------|-------|----------|

| LFE3-17EA-6FTN256I | 1.2V    | -6    | Lead-Free ftBGA | 256  | IND   | 17       |

| LFE3-17EA-7FTN256I | 1.2V    | -7    | Lead-Free ftBGA | 256  | IND   | 17       |

| LFE3-17EA-8FTN256I | 1.2V    | -8    | Lead-Free ftBGA | 256  | IND   | 17       |

| LFE3-17EA-6FN484I  | 1.2V    | -6    | Lead-Free fpBGA | 484  | IND   | 17       |

| LFE3-17EA-7FN484I  | 1.2V    | -7    | Lead-Free fpBGA | 484  | IND   | 17       |

| LFE3-17EA-8FN484I  | 1.2V    | -8    | Lead-Free fpBGA | 484  | IND   | 17       |

| Part Number        | Voltage | Grade | Package         | Pins | Temp. | LUTs (K) |

|--------------------|---------|-------|-----------------|------|-------|----------|

| LFE3-35EA-6FTN256I | 1.2V    | -6    | Lead-Free ftBGA | 256  | IND   | 33       |

| LFE3-35EA-7FTN256I | 1.2V    | -7    | Lead-Free ftBGA | 256  | IND   | 33       |

| LFE3-35EA-8FTN256I | 1.2V    | -8    | Lead-Free ftBGA | 256  | IND   | 33       |

| LFE3-35EA-6FN484I  | 1.2V    | -6    | Lead-Free fpBGA | 484  | IND   | 33       |

| LFE3-35EA-7FN484I  | 1.2V    | -7    | Lead-Free fpBGA | 484  | IND   | 33       |

| LFE3-35EA-8FN484I  | 1.2V    | -8    | Lead-Free fpBGA | 484  | IND   | 33       |

| LFE3-35EA-6FN672I  | 1.2V    | -6    | Lead-Free fpBGA | 672  | IND   | 33       |

| LFE3-35EA-7FN672I  | 1.2V    | -7    | Lead-Free fpBGA | 672  | IND   | 33       |

| LFE3-35EA-8FN672I  | 1.2V    | -7    | Lead-Free fpBGA | 672  | IND   | 33       |

| Part Number        | Voltage | Grade | Package         | Pins | Temp. | LUTs (K) |

|--------------------|---------|-------|-----------------|------|-------|----------|

| LFE3-70EA-6FN484I  | 1.2V    | -6    | Lead-Free fpBGA | 484  | IND   | 67       |

| LFE3-70EA-7FN484I  | 1.2V    | -7    | Lead-Free fpBGA | 484  | IND   | 67       |

| LFE3-70EA-8FN484I  | 1.2V    | -8    | Lead-Free fpBGA | 484  | IND   | 67       |

| LFE3-70EA-6FN672I  | 1.2V    | -6    | Lead-Free fpBGA | 672  | IND   | 67       |

| LFE3-70EA-7FN672I  | 1.2V    | -7    | Lead-Free fpBGA | 672  | IND   | 67       |

| LFE3-70EA-8FN672I  | 1.2V    | -8    | Lead-Free fpBGA | 672  | IND   | 67       |

| LFE3-70EA-6FN1156I | 1.2V    | -6    | Lead-Free fpBGA | 1156 | IND   | 67       |

| LFE3-70EA-7FN1156I | 1.2V    | -7    | Lead-Free fpBGA | 1156 | IND   | 67       |

| LFE3-70EA-8FN1156I | 1.2V    | -8    | Lead-Free fpBGA | 1156 | IND   | 67       |

| Date                | Version         | Section                                        | Change Summary                                                                                                                                                                                                                                                                                                                            |