Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                                             |

|--------------------------------|-----------------------------------------------------------------------------|

| Product Status                 | Obsolete                                                                    |

| Number of LABs/CLBs            | 11500                                                                       |

| Number of Logic Elements/Cells | 92000                                                                       |

| Total RAM Bits                 | 4526080                                                                     |

| Number of I/O                  | 295                                                                         |

| Number of Gates                | -                                                                           |

| Voltage - Supply               | 1.14V ~ 1.26V                                                               |

| Mounting Type                  | Surface Mount                                                               |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                                             |

| Package / Case                 | 484-BBGA                                                                    |

| Supplier Device Package        | 484-FPBGA (23x23)                                                           |

| Purchase URL                   | https://www.e-xfl.com/product-detail/lattice-semiconductor/lfe3-95e-8fn484c |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

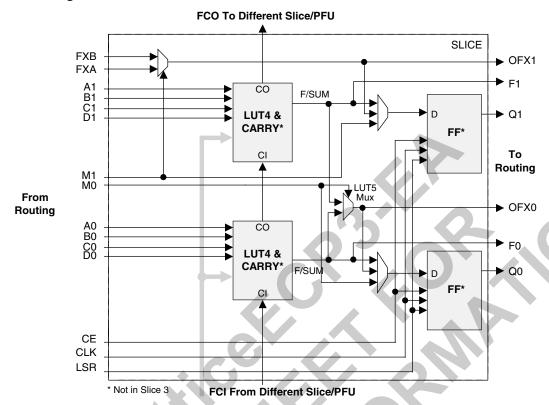

Figure 2-3. Slice Diagram

For Slices 0 and 1, memory control signals are generated from Slice 2 as follows:

WCK is CLK

WRE is from LSR

DI[3:2] for Slice 1 and DI[1:0] for Slice 0 data from Slice 2

WAD [A:D] is a 4-bit address from slice 2 LUT input

Table 2-2. Slice Signal Descriptions

| Function | Туре               | Signal Names   | Description                                                          |

|----------|--------------------|----------------|----------------------------------------------------------------------|

| Input    | Data signal        | A0, B0, C0, D0 | Inputs to LUT4                                                       |

| Input    | Data signal        | A1, B1, C1, D1 | Inputs to LUT4                                                       |

| Input    | Multi-purpose      | MO             | Multipurpose Input                                                   |

| Input    | Multi-purpose      | M1             | Multipurpose Input                                                   |

| Input    | Control signal     | CE             | Clock Enable                                                         |

| Input    | Control signal     | LSR            | Local Set/Reset                                                      |

| Input    | Control signal     | CLK            | System Clock                                                         |

| Input    | Inter-PFU signal   | FC             | Fast Carry-in <sup>1</sup>                                           |

| Input    | Inter-slice signal | FXA            | Intermediate signal to generate LUT6 and LUT7                        |

| Input    | Inter-slice signal | FXB            | Intermediate signal to generate LUT6 and LUT7                        |

| Output   | Data signals       | F0, F1         | LUT4 output register bypass signals                                  |

| Output   | Data signals       | Q0, Q1         | Register outputs                                                     |

| Output   | Data signals       | OFX0           | Output of a LUT5 MUX                                                 |

| Output   | Data signals       | OFX1           | Output of a LUT6, LUT7, LUT8 <sup>2</sup> MUX depending on the slice |

| Output   | Inter-PFU signal   | FCO            | Slice 2 of each PFU is the fast carry chain output <sup>1</sup>      |

<sup>1.</sup> See Figure 2-3 for connection details.

<sup>2.</sup> Requires two PFUs.

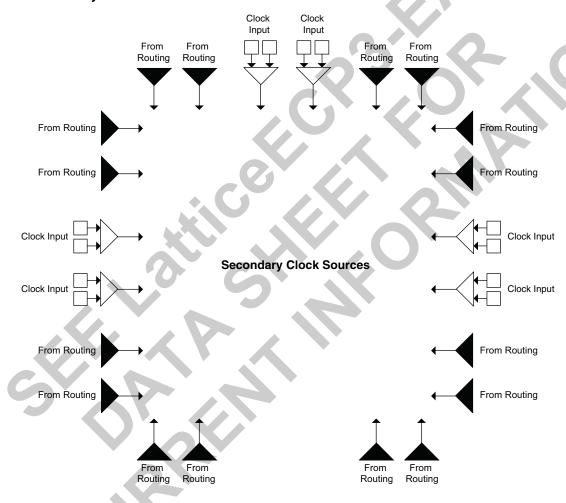

# **Secondary Clock/Control Sources**

LatticeECP3 devices derive eight secondary clock sources (SC0 through SC7) from six dedicated clock input pads and the rest from routing. Figure 2-14 shows the secondary clock sources. All eight secondary clock sources are defined as inputs to a per-region mux SC0-SC7. SC0-SC3 are primary for control signals (CE and/or LSR), and SC4-SC7 are for clock and high fanout data.

In an actual implementation, there is some overlap to maximize routability. In addition to SC0-SC3, SC7 is also an input to the control signals (LSR or CE). SC0-SC2 are also inputs to clocks along with SC4-SC7. High fanout logic signals (LUT inputs) will utilize the X2 and X0 switches where SC0-SC7 are inputs to X2 switches, and SC4-SC7 are inputs to X0 switches. Note that through X0 switches, SC4-SC7 can also access control signals CE/LSR.

Figure 2-14. Secondary Clock Sources

Note: Clock inputs can be configured in differential or single-ended mode.

# **Secondary Clock/Control Routing**

Global secondary clock is a secondary clock that is distributed to all regions. The purpose of the secondary clock routing is to distribute the secondary clock sources to the secondary clock regions. Secondary clocks in the LatticeECP3 devices are region-based resources. Certain EBR rows and special vertical routing channels bind the secondary clock regions. This special vertical routing channel aligns with either the left edge of the center DSP slice in the DSP row or the center of the DSP row. Figure 2-15 shows this special vertical routing channel and the 20 secondary clock regions for the LatticeECP3 family of devices. All devices in the LatticeECP3 family have eight

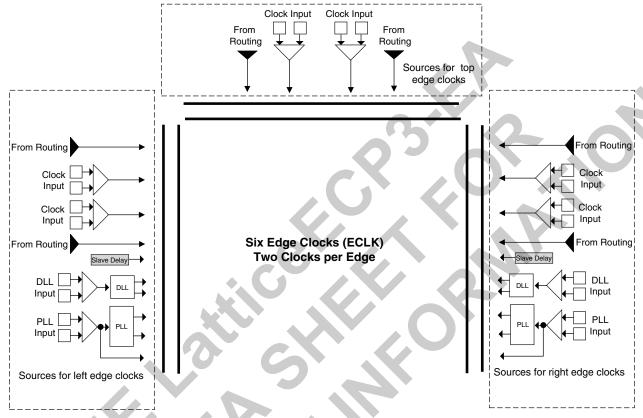

### **Edge Clock Sources**

Edge clock resources can be driven from a variety of sources at the same edge. Edge clock resources can be driven from adjacent edge clock PIOs, primary clock PIOs, PLLs, DLLs, Slave Delay and clock dividers as shown in Figure 2-19.

Figure 2-19. Edge Clock Sources

Notes:

- 1. Clock inputs can be configured in differential or single ended mode.

- 2. The two DLLs can also drive the two top edge clocks.

- 3. The top left and top right PLL can also drive the two top edge clocks.

# **Edge Clock Routing**

LatticeECP3 devices have a number of high-speed edge clocks that are intended for use with the PIOs in the implementation of high-speed interfaces. There are six edge clocks per device: two edge clocks on each of the top, left, and right edges. Different PLL and DLL outputs are routed to the two muxes on the left and right sides of the device. In addition, the CLKINDEL signal (generated from the DLL Slave Delay Line block) is routed to all the edge clock muxes on the left and right sides of the device. Figure 2-20 shows the selection muxes for these clocks.

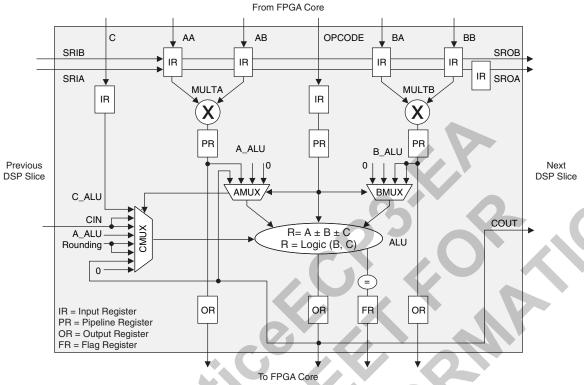

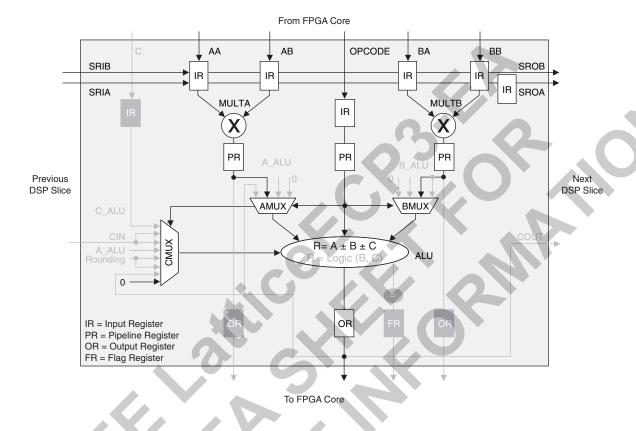

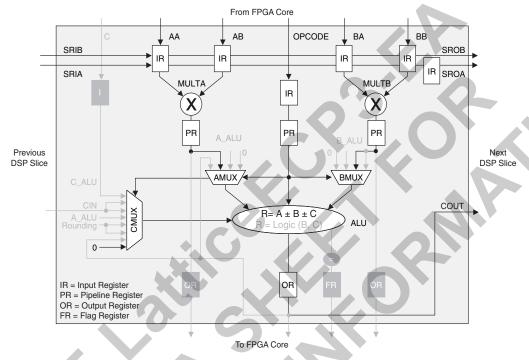

Figure 2-25. Detailed sysDSP Slice Diagram

Note: A\_ALU, B\_ALU and C\_ALU are internal signals generated by combining bits from AA, AB, BA BB and C inputs. See TN1182, LatticeECP3 sysDSP Usage Guide, for further information.

The LatticeECP2 sysDSP block supports the following basic elements.

- MULT (Multiply)

- MAC (Multiply, Accumulate)

- MULTADDSUB (Multiply, Addition/Subtraction)

- MULTADDSUBSUM (Multiply, Addition/Subtraction, Summation)

Table 2-8 shows the capabilities of each of the LatticeECP3 slices versus the above functions.

Table 2-8. Maximum Number of Elements in a Slice

| Width of Multiply | х9             | x18 | x36 |

|-------------------|----------------|-----|-----|

| MULT              | 4              | 2   | 1/2 |

| MAC               | 1              | 1   | _   |

| MULTADDSUB        | 2              | 1   | _   |

| MULTADDSUBSUM     | 1 <sup>1</sup> | 1/2 | _   |

<sup>1.</sup> One slice can implement 1/2 9x9 m9x9addsubsum and two m9x9addsubsum with two slices.

Some options are available in the four elements. The input register in all the elements can be directly loaded or can be loaded as a shift register from previous operand registers. By selecting "dynamic operation" the following operations are possible:

- In the Add/Sub option the Accumulator can be switched between addition and subtraction on every cycle.

- The loading of operands can switch between parallel and serial operations.

#### **MULTADDSUB DSP Element**

In this case, the operands AA and AB are multiplied and the result is added/subtracted with the result of the multiplier operation of operands BA and BB. The user can enable the input, output and pipeline registers. Figure 2-29 shows the MULTADDSUB sysDSP element.

Figure 2-29. MULTADDSUB

#### **MULTADDSUBSUM DSP Element**

In this case, the operands AA and AB are multiplied and the result is added/subtracted with the result of the multiplier operation of operands BA and BB of Slice 0. Additionally, the operands AA and AB are multiplied and the result is added/subtracted with the result of the multiplier operation of operands BA and BB of Slice 1. The results of both addition/subtractions are added by the second ALU following the slice cascade path. The user can enable the input, output and pipeline registers. Figure 2-30 and Figure 2-31 show the MULTADDSUBSUM sysDSP element

Figure 2-30. MULTADDSUBSUM Slice 0

#### **ALU Flags**

The sysDSP slice provides a number of flags from the ALU including:

- Equal to zero (EQZ)

- Equal to zero with mask (EQZM)

- · Equal to one with mask (EQOM)

- · Equal to pattern with mask (EQPAT)

- Equal to bit inverted pattern with mask (EQPATB)

- · Accumulator Overflow (OVER)

- Accumulator Underflow (UNDER)

- Either over or under flow supporting LatticeECP2 legacy designs (OVERUNDER)

### Clock, Clock Enable and Reset Resources

Global Clock, Clock Enable and Reset signals from routing are available to every sysDSP slice. From four clock sources (CLK0, CLK1, CLK2, and CLK3) one clock is selected for each input register, pipeline register and output register. Similarly Clock Enable (CE) and Reset (RST) are selected at each input register, pipeline register and output register.

# Resources Available in the LatticeECP3 Family

Table 2-9 shows the maximum number of multipliers for each member of the LatticeECP3 family. Table 2-10 shows the maximum available EBR RAM Blocks in each LatticeECP3 device. EBR blocks, together with Distributed RAM can be used to store variables locally for fast DSP operations.

Table 2-9. Maximum Number of DSP Slices in the LatticeECP3 Family

| Device   | DSP Slices | 9x9 Multiplier | 18x18 Multiplier | 36x36 Multiplier |

|----------|------------|----------------|------------------|------------------|

| ECP3-17  | 12         | 48             | 24               | 6                |

| ECP3-35  | 32         | 128            | 64               | 16               |

| ECP3-70  | 64         | 256            | 128              | 32               |

| ECP3-95  | 64         | 256            | 128              | 32               |

| ECP3-150 | 160        | 640            | 320              | 80               |

Table 2-10. Embedded SRAM in the LatticeECP3 Family

| Device   | EBR SRAM Block | Total EBR SRAM<br>(Kbits) |

|----------|----------------|---------------------------|

| ECP3-17  | 38             | 700                       |

| ECP3-35  | 72             | 1327                      |

| ECP3-70  | 240            | 4420                      |

| ECP3-95  | 240            | 4420                      |

| ECP3-150 | 372            | 6850                      |

#### **Lattice Semiconductor**

Input signals are fed from the sysl/O buffer to the input register block (as signal DI). If desired, the input signal can bypass the register and delay elements and be used directly as a combinatorial signal (INDD), a clock (INCK) and, in selected blocks, the input to the DQS delay block. If an input delay is desired, designers can select either a fixed delay or a dynamic delay DEL[3:0]. The delay, if selected, reduces input register hold time requirements when using a global clock.

The input block allows three modes of operation. In single data rate (SDR) the data is registered with the system clock by one of the registers in the single data rate sync register block.

In DDR mode, two registers are used to sample the data on the positive and negative edges of the modified DQS (ECLKDQSR) in the DDR Memory mode or ECLK signal when using DDR Generic mode, creating two data streams. Before entering the core, these two data streams are synchronized to the system clock to generate two data streams.

A gearbox function can be implemented in each of the input registers on the left and right sides. The gearbox function takes a double data rate signal applied to PIOA and converts it as four data streams, INA, IPA, INB and IPB. The two data streams from the first set of DDR registers are synchronized to the edge clock and then to the system clock before entering the core. Figure 2-30 provides further information on the use of the gearbox function.

The signal DDRCLKPOL controls the polarity of the clock used in the synchronization registers. It ensures adequate timing when data is transferred to the system clock domain from the ECLKDQSR (DDR Memory Interface mode) or ECLK (DDR Generic mode). The DDRLAT signal is used to ensure the data transfer from the synchronization registers to the clock transfer and gearbox registers.

The ECLKDQSR, DDRCLKPOL and DDRLAT signals are generated in the DQS Read Control Logic Block. See Figure 2-37 for an overview of the DQS read control logic.

Further discussion about using the DQS strobe in this module is discussed in the DDR Memory section of this data sheet.

Please see TN1180, LatticeECP3 High-Speed I/O Interface for more information on this topic.

# sysI/O Differential Electrical Characteristics LVDS25

### **Over Recommended Operating Conditions**

| Parameter                         | Description                                                | Test Conditions                                           | Min.   | Тур. | Max.  | Units |

|-----------------------------------|------------------------------------------------------------|-----------------------------------------------------------|--------|------|-------|-------|

| V <sub>INP</sub> V <sub>INM</sub> | Input Voltage                                              |                                                           | 0      | _    | 2.4   | V     |

| V <sub>CM</sub>                   | Input Common Mode Voltage                                  | Half the Sum of the Two Inputs                            | 0.05   |      | 2.35  | V     |

| $V_{THD}$                         | Differential Input Threshold                               | Difference Between the Two Inputs                         | +/-100 | _    | _     | mV    |

| I <sub>IN</sub>                   | Input Current                                              | Power On or Power Off                                     |        | _    | +/-10 | μΑ    |

| V <sub>OH</sub>                   | Output High Voltage for V <sub>OP</sub> or V <sub>OM</sub> | R <sub>T</sub> = 100 Ohm                                  | 1      | 1.38 | 1.60  | V     |

| $V_{OL}$                          | Output Low Voltage for $V_{OP}$ or $V_{OM}$                | R <sub>T</sub> = 100 Ohm                                  | 0.9V   | 1.03 |       | V     |

| $V_{OD}$                          | Output Voltage Differential                                | $(V_{OP} - V_{OM}), R_T = 100 \text{ Ohm}$                | 250    | 350  | 450   | mV    |

| ΔV <sub>OD</sub>                  | Change in V <sub>OD</sub> Between High and Low             | 0                                                         | -      | _    | 50    | mV    |

| V <sub>OS</sub>                   | Output Voltage Offset                                      | $(V_{OP} + V_{OM})/2$ , $R_T = 100 \text{ Ohm}$           | 1.125  | 1.20 | 1.375 | V     |

| ΔV <sub>OS</sub>                  | Change in V <sub>OS</sub> Between H and L                  |                                                           |        |      | 50    | mV    |

| I <sub>SAB</sub>                  | Output Short Circuit Current                               | V <sub>OD</sub> = 0V Driver Outputs Shorted to Each Other |        |      | 12    | mA    |

### **Differential HSTL and SSTL**

Differential HSTL and SSTL outputs are implemented as a pair of complementary single-ended outputs. All allowable single-ended output classes (class I and class II) are supported in this mode.

# LatticeECP3 Internal Switching Characteristics<sup>1, 2</sup> (Continued)

# **Over Recommended Commercial Operating Conditions**

|                         |                                                        | -        | -8   |        | -7 -6 |        | 6    |        |

|-------------------------|--------------------------------------------------------|----------|------|--------|-------|--------|------|--------|

| Parameter               | Description                                            | Min.     | Max. | Min.   | Max.  | Min.   | Max. | Units. |

| t <sub>HWREN_EBR</sub>  | Hold Write/Read Enable to PFU Memory                   | 0.141    | _    | 0.145  | _     | 0.149  | _    | ns     |

| t <sub>SUCE_EBR</sub>   | Clock Enable Setup Time to EBR Output<br>Register      | 0.087    |      | 0.096  |       | 0.104  |      | ns     |

| t <sub>HCE_EBR</sub>    | Clock Enable Hold Time to EBR Output<br>Register       | -0.066   |      | -0.080 |       | -0.094 |      | ns     |

| t <sub>SUBE_EBR</sub>   | Byte Enable Set-Up Time to EBR Output<br>Register      | -0.071   |      | -0.070 |       | -0.068 |      | ns     |

| t <sub>HBE_EBR</sub>    | Byte Enable Hold Time to EBR Output<br>Register        | 0.118    |      | 0.098  |       | 0.077  |      | ns     |

| DSP Block Tin           | ning <sup>3</sup>                                      |          |      |        |       |        |      |        |

| t <sub>SUI_DSP</sub>    | Input Register Setup Time                              | 0.32     |      | 0.36   | 7     | 0.39   |      | ns     |

| t <sub>HI_DSP</sub>     | Input Register Hold Time                               | -0.17    | K-   | -0.19  | 7     | -0.21  | 1    | ns     |

| t <sub>SUP_DSP</sub>    | Pipeline Register Setup Time                           | 2.23     | _    | 2.30   |       | 2.37   |      | ns     |

| t <sub>HP_DSP</sub>     | Pipeline Register Hold Time                            | -1.02    | _    | -1.09  | _     | -1.15  |      | ns     |

| t <sub>SUO_DSP</sub>    | Output Register Setup Time                             | 3.09     |      | 3.22   |       | 3.34   | _    | ns     |

| t <sub>HO_DSP</sub>     | Output Register Hold Time                              | -1.67    | V-   | -1.76  | -     | -1.84  | —    | ns     |

| t <sub>COI_DSP</sub>    | Input Register Clock to Output Time                    | -<       | 3.68 |        | 4.03  | _      | 4.38 | ns     |

| t <sub>COP_DSP</sub>    | Pipeline Register Clock to Output Time                 |          | 1.30 | -0     | 1.47  | _      | 1.64 | ns     |

| t <sub>COO_DSP</sub>    | Output Register Clock to Output Time                   | <b>(</b> | 0.58 | -7     | 0.60  | _      | 0.62 | ns     |

| t <sub>SUOPT_DSP</sub>  | Opcode Register Setup Time                             | 0.31     | - (  | 0.35   | _     | 0.39   | _    | ns     |

| t <sub>HOPT_DSP</sub>   | Opcode Register Hold Time                              | -0.20    |      | -0.24  | _     | -0.27  | _    | ns     |

| t <sub>SUDATA_DSP</sub> | Cascade_data through ALU to Output Register Setup Time | 1.55     | X    | 1.67   | _     | 1.78   | _    | ns     |

| t <sub>HPDATA_DSP</sub> | Cascade_data through ALU to Output Register Hold Time  | -0.44    |      | -0.53  | _     | -0.61  | _    | ns     |

<sup>1.</sup> Internal parameters are characterized but not tested on every device.

<sup>2.</sup> Commercial timing numbers are shown. Industrial timing numbers are typically slower and can be extracted from the ispLEVER software.

<sup>3.</sup> DSP slice is configured in Multiply Add/Sub 18x18 mode.

<sup>4.</sup> The output register is in Flip-flop mode.

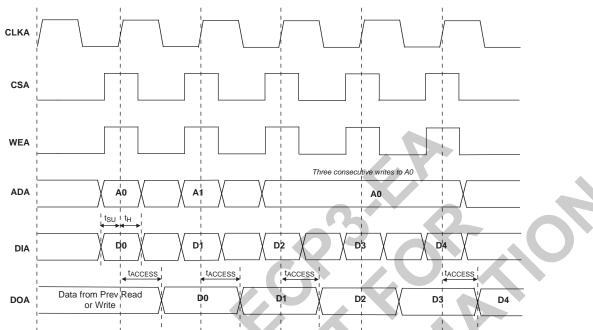

Figure 3-11. Write Through (SP Read/Write on Port A, Input Registers Only)

Note: Input data and address are registered at the positive edge of the clock and output data appears after the positive edge of the clock.

# LatticeECP3 Family Timing Adders<sup>1, 2, 3, 4, 5</sup> (Continued)

# **Over Recommended Commercial Operating Conditions**

| Buffer Type   | Description                                 | -8    | -7    | -6    | Units |

|---------------|---------------------------------------------|-------|-------|-------|-------|

| RSDS25        | RSDS, VCCIO = 2.5V                          | 0.05  | 0.10  | 0.16  | ns    |

| PPLVDS        | Point-to-Point LVDS, Emulated, VCCIO = 2.5V | -0.10 | -0.05 | 0.01  | ns    |

| LVPECL33      | LVPECL, Emulated, VCCIO = 3.0V              | -0.02 | -0.04 | -0.06 | ns    |

| HSTL18_I      | HSTL_18 class I 8mA drive, VCCIO = 1.8V     | -0.19 | -0.16 | -0.12 | ns    |

| HSTL18_II     | HSTL_18 class II, VCCIO = 1.8V              | -0.30 | -0.28 | -0.25 | ns    |

| HSTL18D_I     | Differential HSTL 18 class I 8mA drive      | -0.19 | -0.16 | -0.12 | ns    |

| HSTL18D_II    | Differential HSTL 18 class II               | -0.30 | -0.28 | -0.25 | ns    |

| HSTL15_I      | HSTL_15 class I 4mA drive, VCCIO = 1.5V     | -0.22 | -0.19 | -0.16 | ns    |

| HSTL15D_I     | Differential HSTL 15 class I 4mA drive      | -0.22 | -0.19 | -0.16 | ns    |

| SSTL33_I      | SSTL_3 class I, VCCIO = 3.0V                | 0.08  | 0.13  | 0.19  | ns    |

| SSTL33_II     | SSTL_3 class II, VCCIO = 3.0V               | -0.20 | -0.17 | -0.14 | ns    |

| SSTL33D_I     | Differential SSTL_3 class I                 | 0.08  | 0.13  | 0.18  | ns    |

| SSTL33D_II    | Differential SSTL_3 class II                | -0.20 | -0.17 | -0.14 | ns    |

| SSTL25_I      | SSTL_2 class I 8mA drive, VCCIO = 2.5V      | -0.06 | -0.02 | 0.02  | ns    |

| SSTL25_II     | SSTL_2 class II 16mA drive, VCCIO = 2.5V    | -0.19 | -0.15 | -0.12 | ns    |

| SSTL25D_I     | Differential SSTL_2 class I 8mA drive       | -0.06 | -0.02 | 0.02  | ns    |

| SSTL25D_II    | Differential SSTL_2 class II 16mA drive     | -0.19 | -0.15 | -0.12 | ns    |

| SSTL18_I      | SSTL_1.8 class I, VCCIO = 1.8V              | -0.14 | -0.10 | -0.07 | ns    |

| SSTL18_II     | SSTL_1.8 class II 8mA drive, VCCIO = 1.8V   | -0.20 | -0.17 | -0.14 | ns    |

| SSTL18D_I     | Differential SSTL_1.8 class I               | -0.14 | -0.10 | -0.07 | ns    |

| SSTL18D_II    | Differential SSTL_1.8 class II 8mA drive    | -0.20 | -0.17 | -0.14 | ns    |

| SSTL15        | SSTL_1.5, VCCIO = 1.5V                      | 0.07  | 0.08  | 0.08  | ns    |

| SSTL15D       | Differential SSTL_15                        | 0.07  | 0.08  | 0.08  | ns    |

| LVTTL33_4mA   | LVTTL 4mA drive, VCCIO = 3.0V               | 0.21  | 0.23  | 0.25  | ns    |

| LVTTL33_8mA   | LVTTL 8mA drive, VCCIO = 3.0V               | 0.09  | 0.09  | 0.10  | ns    |

| LVTTL33_12mA  | LVTTL 12mA drive, VCCIO = 3.0V              | 0.02  | 0.03  | 0.03  | ns    |

| LVTTL33_16mA  | LVTTL 16mA drive, VCCIO = 3.0V              | 0.12  | 0.13  | 0.13  | ns    |

| LVTTL33_20mA  | LVTTL 20mA drive, VCCIO = 3.0V              | 0.08  | 0.08  | 0.09  | ns    |

| LVCMOS33_4mA  | LVCMOS 3.3 4mA drive, fast slew rate        | 0.21  | 0.23  | 0.25  | ns    |

| LVCMOS33_8mA  | LVCMOS 3.3 8mA drive, fast slew rate        | 0.09  | 0.09  | 0.10  | ns    |

| LVCMOS33_12mA | LVCMOS 3.3 12mA drive, fast slew rate       | 0.02  | 0.03  | 0.03  | ns    |

| LVCMOS33_16mA | LVCMOS 3.3 16mA drive, fast slew rate       | 0.12  | 0.13  | 0.13  | ns    |

| LVCMOS33_20mA | LVCMOS 3.3 20mA drive, fast slew rate       | 0.08  | 0.08  | 0.09  | ns    |

| LVCMOS25_4mA  | LVCMOS 2.5 4mA drive, fast slew rate        | 0.12  | 0.12  | 0.12  | ns    |

| LVCMOS25_8mA  | LVCMOS 2.5 8mA drive, fast slew rate        | 0.05  | 0.05  | 0.05  | ns    |

| LVCMOS25_12mA | LVCMOS 2.5 12mA drive, fast slew rate       | 0.00  | 0.00  | 0.00  | ns    |

| LVCMOS25_16mA | LVCMOS 2.5 16mA drive, fast slew rate       | 0.08  | 0.08  | 0.08  | ns    |

| LVCMOS25_20mA | LVCMOS 2.5 20mA drive, fast slew rate       | 0.04  | 0.04  | 0.04  | ns    |

| LVCMOS18_4mA  | LVCMOS 1.8 4mA drive, fast slew rate        | 0.08  | 0.09  | 0.09  | ns    |

| LVCMOS18_8mA  | LVCMOS 1.8 8mA drive, fast slew rate        | 0.02  | 0.01  | 0.01  | ns    |

| LVCMOS18_12mA | LVCMOS 1.8 12mA drive, fast slew rate       | -0.03 | -0.03 | -0.03 | ns    |

| LVCMOS18_16mA | LVCMOS 1.8 16mA drive, fast slew rate       | 0.03  | 0.03  | 0.03  | ns    |

# LatticeECP3 Family Timing Adders<sup>1, 2, 3, 4, 5</sup> (Continued)

### **Over Recommended Commercial Operating Conditions**

| Buffer Type   | Description                           | -8    | -7    | -6    | Units |

|---------------|---------------------------------------|-------|-------|-------|-------|

| LVCMOS15_4mA  | LVCMOS 1.5 4mA drive, fast slew rate  | 0.09  | 0.10  | 0.10  | ns    |

| LVCMOS15_8mA  | LVCMOS 1.5 8mA drive, fast slew rate  | 0.01  | 0.01  | 0.00  | ns    |

| LVCMOS12_2mA  | LVCMOS 1.2 2mA drive, fast slew rate  | 0.08  | 0.08  | 0.08  | ns    |

| LVCMOS12_6mA  | LVCMOS 1.2 6mA drive, fast slew rate  | -0.02 | -0.02 | -0.02 | ns    |

| LVCMOS33_4mA  | LVCMOS 3.3 4mA drive, slow slew rate  | 1.64  | 1.71  | 1.77  | ns    |

| LVCMOS33_8mA  | LVCMOS 3.3 8mA drive, slow slew rate  | 1.39  | 1.45  | 1.51  | ns    |

| LVCMOS33_12mA | LVCMOS 3.3 12mA drive, slow slew rate | 1.21  | 1.27  | 1.33  | ns    |

| LVCMOS33_16mA | LVCMOS 3.3 16mA drive, slow slew rate | 1.43  | 1.49  | 1.55  | ns    |

| LVCMOS33_20mA | LVCMOS 3.3 20mA drive, slow slew rate | 1.23  | 1.28  | 1.34  | ns    |

| LVCMOS25_4mA  | LVCMOS 2.5 4mA drive, slow slew rate  | 1.66  | 1.70  | 1.74  | ns    |

| LVCMOS25_8mA  | LVCMOS 2.5 8mA drive, slow slew rate  | 1.39  | 1.43  | 1.46  | ns    |

| LVCMOS25_12mA | LVCMOS 2.5 12mA drive, slow slew rate | 1.20  | 1.24  | 1.28  | ns    |

| LVCMOS25_16mA | LVCMOS 2.5 16mA drive, slow slew rate | 1.42  | 1.45  | 1.49  | ns    |

| LVCMOS25_20mA | LVCMOS 2.5 20mA drive, slow slew rate | 1.22  | 1.26  | 1.29  | ns    |

| LVCMOS18_4mA  | LVCMOS 1.8 4mA drive, slow slew rate  | 1.61  | 1.65  | 1.68  | ns    |

| LVCMOS18_8mA  | LVCMOS 1.8 8mA drive, slow slew rate  | 1.32  | 1.36  | 1.39  | ns    |

| LVCMOS18_12mA | LVCMOS 1.8 12mA drive, slow slew rate | 1.14  | 1.17  | 1.21  | ns    |

| LVCMOS18_16mA | LVCMOS 1.8 16mA drive, slow slew rate | 1.35  | 1.38  | 1.42  | ns    |

| LVCMOS15_4mA  | LVCMOS 1.5 4mA drive, slow slew rate  | 1.57  | 1.60  | 1.64  | ns    |

| LVCMOS15_8mA  | LVCMOS 1.5 8mA drive, slow slew rate  | 0.01  | 0.01  | 0.00  | ns    |

| LVCMOS12_2mA  | LVCMOS 1.2 2mA drive, slow slew rate  | 1.51  | 1.54  | 1.58  | ns    |

| LVCMOS12_6mA  | LVCMOS 1.2 6mA drive, slow slew rate  | -0.02 | -0.02 | -0.02 | ns    |

| PCI33         | PCI, VCCIO = 3.0V                     | 0.19  | 0.21  | 0.24  | ns    |

<sup>1.</sup> Timing adders are characterized but not tested on every device.

<sup>2.</sup> LVCMOS timing measured with the load specified in Switching Test Condition table.

<sup>3.</sup> All other standards tested according to the appropriate specifications.

<sup>4.</sup> Not all I/O standards and drive strengths are supported for all banks. See the Architecture section of this data sheet for details.

<sup>5.</sup> Commercial timing numbers are shown. Industrial numbers are typically slower and can be extracted from the ispLEVER software.

# LatticeECP3 Maximum I/O Buffer Speed (Continued)<sup>1, 2, 3, 4, 5, 6</sup>

### **Over Recommended Operating Conditions**

| Buffer | Description                   | Max. | Units |  |

|--------|-------------------------------|------|-------|--|

| PCI33  | PCI, V <sub>CCIO</sub> = 3.3V | 66   | MHz   |  |

- 1. These maximum speeds are characterized but not tested on every device.

- 2. Maximum I/O speed for differential output standards emulated with resistors depends on the layout.

- 3. LVCMOS timing is measured with the load specified in the Switching Test Conditions table of this document.

- 4. All speeds are measured at fast slew.

- 5. Actual system operation may vary depending on user logic implementation.

- 6. Maximum data rate equals 2 times the clock rate when utilizing DDR.

# SERDES High-Speed Data Transmitter<sup>1</sup>

Table 3-6. Serial Output Timing and Levels

| Symbol                                 | Description                                                  | Frequency          | Min.                       | Тур.                       | Max.                       | Units   |

|----------------------------------------|--------------------------------------------------------------|--------------------|----------------------------|----------------------------|----------------------------|---------|

| V <sub>TX-DIFF-P-P-1.44</sub>          | Differential swing (1.44V setting) <sup>1,2</sup>            | 0.25 to 3.125 Gbps | 1150                       | 1440                       | 1730                       | mV, p-p |

| V <sub>TX-DIFF-P-P-1.35</sub>          | Differential swing (1.35V setting) <sup>1,2</sup>            | 0.25 to 3.125 Gbps | 1080                       | 1350                       | 1620                       | mV, p-p |

| V <sub>TX-DIFF-P-P-1.26</sub>          | Differential swing (1.26V setting) <sup>1,2</sup>            | 0.25 to 3.125 Gbps | 1000                       | 1260                       | 1510                       | mV, p-p |

| V <sub>TX-DIFF-P-P-1.13</sub>          | Differential swing (1.13V setting) <sup>1,2</sup>            | 0.25 to 3.125 Gbps | 840                        | 1130                       | 1420                       | mV, p-p |

| V <sub>TX-DIFF-P-P-1.04</sub>          | Differential swing (1.04V setting) <sup>1, 2</sup>           | 0.25 to 3.125 Gbps | 780                        | 1040                       | 1300                       | mV, p-p |

| V <sub>TX-DIFF-P-0.92</sub>            | Differential swing (0.92V setting) <sup>1, 2</sup>           | 0.25 to 3.125 Gbps | 690                        | 920                        | 1150                       | mV, p-p |

| V <sub>TX-DIFF-P-P-0.87</sub>          | Differential swing (0.87V setting) <sup>1, 2</sup>           | 0.25 to 3.125 Gbps | 650                        | 870                        | 1090                       | mV, p-p |

| V <sub>TX-DIFF-P-0.78</sub>            | Differential swing (0.78V setting) <sup>1,2</sup>            | 0.25 to 3.125 Gbps | 585                        | 780                        | 975                        | mV, p-p |

| V <sub>TX-DIFF-P-P-0.64</sub>          | Differential swing (0.64V setting) <sup>1, 2</sup>           | 0.25 to 3.125 Gbps | 480                        | 640                        | 800                        | mV, p-p |

| V <sub>OCM</sub>                       | Output common mode voltage                                   | <b>4</b>           | V <sub>CCOB</sub><br>-0.75 | V <sub>CCOB</sub><br>-0.60 | V <sub>CCOB</sub><br>-0.45 | V       |

| T <sub>TX-R</sub>                      | Rise time (20% to 80%)                                       |                    | 145                        | 185                        | 265                        | ps      |

| T <sub>TX-F</sub>                      | Fall time (80% to 20%)                                       | . ( 4 )            | 145                        | 185                        | 265                        | ps      |

| Z <sub>TX-OI-SE</sub>                  | Output Impedance 50/75/HiZ Ohms (single ended)               | // - /             | -20%                       | 50/75/<br>Hi Z             | +20%                       | Ohms    |

| R <sub>LTX-RL</sub>                    | Return loss (with package)                                   |                    | 10                         | 11/2                       |                            | dB      |

| T <sub>TX-INTRASKEW</sub>              | Lane-to-lane TX skew within a SERDES quad block (intra-quad) |                    |                            |                            | 200                        | ps      |

| T <sub>TX-INTERSKEW</sub> <sup>3</sup> | Lane-to-lane skew between SERDES quad blocks (inter-quad)    |                    | X                          | _                          | 1UI +200                   | ps      |

<sup>1.</sup> All measurements are with 50 ohm impedance.

Table 3-7. Channel Output Jitter

| Description   | Frequency  | Min.                | Тур. | Max. | Units   |

|---------------|------------|---------------------|------|------|---------|

| Deterministic | 3.125 Gbps | <b>V</b> - <b>A</b> | _    | 0.17 | UI, p-p |

| Random        | 3.125 Gbps | -                   | _    | 0.25 | UI, p-p |

| Total         | 3.125 Gbps |                     | _    | 0.35 | UI, p-p |

| Deterministic | 2.5Gbps    |                     | _    | 0.17 | UI, p-p |

| Random        | 2.5Gbps    | <b>V</b>            | _    | 0.20 | UI, p-p |

| Total         | 2.5Gbps    | _                   | _    | 0.35 | UI, p-p |

| Deterministic | 1.25 Gbps  |                     | _    | 0.10 | UI, p-p |

| Random        | 1.25 Gbps  | _                   | _    | 0.22 | UI, p-p |

| Total         | 1.25 Gbps  | _                   | _    | 0.24 | UI, p-p |

| Deterministic | 622 Mbps   | _                   | _    | 0.10 | UI, p-p |

| Random        | 622 Mbps   | _                   | _    | 0.20 | UI, p-p |

| Total         | 622 Mbps   | _                   | _    | 0.24 | UI, p-p |

| Deterministic | 250 Mbps   | _                   | _    | 0.10 | UI, p-p |

| Random        | 250 Mbps   | _                   | _    | 0.18 | UI, p-p |

| Total         | 250 Mbps   | _                   | _    | 0.24 | UI, p-p |

Note: Values are measured with PRBS 2<sup>7</sup>-1, all channels operating, FPGA logic active, I/Os around SERDES pins quiet, reference clock @ 10X mode.

<sup>2.</sup> See TN1176, LatticeECP3 SERDES/PCS Usage Guide for actual binary settings and the min-max range.

<sup>3.</sup> Inter-quad skew is between all SERDES channels on the device and requires the use of a low skew internal reference clock.

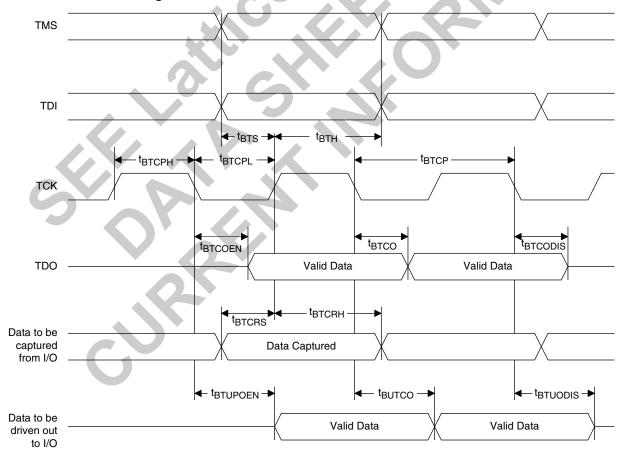

# **JTAG Port Timing Specifications**

# **Over Recommended Operating Conditions**

| Parameter                                                          | Min                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Max                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Units                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|--------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TCK clock frequency                                                | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | MHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| TCK [BSCAN] clock pulse width                                      | 40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| TCK [BSCAN] clock pulse width high                                 | 20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| TCK [BSCAN] clock pulse width low                                  | 20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| TCK [BSCAN] setup time                                             | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| TCK [BSCAN] hold time                                              | 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| TCK [BSCAN] rise/fall time                                         | 50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | mV/ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| TAP controller falling edge of clock to valid output               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| TAP controller falling edge of clock to valid disable              | <u></u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| TAP controller falling edge of clock to valid enable               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| BSCAN test capture register setup time                             | 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | $\overline{}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| BSCAN test capture register hold time                              | 25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| BSCAN test update register, falling edge of clock to valid output  | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| BSCAN test update register, falling edge of clock to valid disable | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| BSCAN test update register, falling edge of clock to valid enable  | $\Lambda$ -V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                                                    | TCK clock frequency  TCK [BSCAN] clock pulse width  TCK [BSCAN] clock pulse width high  TCK [BSCAN] clock pulse width low  TCK [BSCAN] setup time  TCK [BSCAN] hold time  TCK [BSCAN] rise/fall time  TAP controller falling edge of clock to valid output  TAP controller falling edge of clock to valid disable  TAP controller falling edge of clock to valid enable  BSCAN test capture register setup time  BSCAN test capture register hold time  BSCAN test update register, falling edge of clock to valid output  BSCAN test update register, falling edge of clock to valid output | TCK clock frequency  TCK [BSCAN] clock pulse width  40  TCK [BSCAN] clock pulse width high  20  TCK [BSCAN] clock pulse width low  20  TCK [BSCAN] setup time  10  TCK [BSCAN] hold time  8  TCK [BSCAN] rise/fall time  50  TAP controller falling edge of clock to valid output  TAP controller falling edge of clock to valid disable  TAP controller falling edge of clock to valid enable  BSCAN test capture register setup time  8  BSCAN test capture register hold time  25  BSCAN test update register, falling edge of clock to valid output  —  BSCAN test update register, falling edge of clock to valid output  —  BSCAN test update register, falling edge of clock to valid output  —  BSCAN test update register, falling edge of clock to valid disable  — | TCK clock frequency — 25  TCK [BSCAN] clock pulse width 40 —  TCK [BSCAN] clock pulse width high 20 —  TCK [BSCAN] clock pulse width low 20 —  TCK [BSCAN] setup time 10 —  TCK [BSCAN] hold time 8 —  TCK [BSCAN] rise/fall time 50 —  TAP controller falling edge of clock to valid output — 10  TAP controller falling edge of clock to valid disable — 10  TAP controller falling edge of clock to valid enable — 10  BSCAN test capture register setup time 8 —  BSCAN test capture register, falling edge of clock to valid output — 25  BSCAN test update register, falling edge of clock to valid disable — 25 |

Figure 3-25. JTAG Port Timing Waveforms

# Point-to-Point LVDS (PPLVDS)

### **Over Recommended Operating Conditions**

| Description                   | Min. | Тур. | Max. | Units |

|-------------------------------|------|------|------|-------|

| Output driver supply (+/- 5%) | 3.14 | 3.3  | 3.47 | V     |

| Output driver supply (+/- 5%) | 2.25 | 2.5  | 2.75 | V     |

| Input differential voltage    | 100  |      | 400  | mV    |

| Input common mode voltage     | 0.2  |      | 2.3  | V     |

| Output differential voltage   | 130  |      | 400  | mV    |

| Output common mode voltage    | 0.5  | 0.8  | 1.4  | V     |

# **RSDS**

# **Over Recommended Operating Conditions**

| Parameter Symbol                | Description                                             | Min. | Тур. | Max.          | Units |

|---------------------------------|---------------------------------------------------------|------|------|---------------|-------|

| V <sub>OD</sub>                 | Output voltage, differential, R <sub>T</sub> = 100 ohms | 100  | 200  | 600           | mV    |

| V <sub>OS</sub>                 | Output voltage, common mode                             | 0.5  | 1.2  | 1.5           | ٧     |

| I <sub>RSDS</sub>               | Differential driver output current                      | 1    | 2    | 6             | mA    |

| $V_{THD}$                       | Input voltage differential                              | 100  | _    | _ >           | mV    |

| V <sub>CM</sub>                 | Input common mode voltage                               | 0.3  |      | 1.5           | V     |

| T <sub>R</sub> , T <sub>F</sub> | Output rise and fall times, 20% to 80%                  |      | 500  | <b>&gt;</b> - | ps    |

| T <sub>ODUTY</sub>              | Output clock duty cycle                                 | 35   | 50   | 65            | %     |

Note: Data is for 2mA drive. Other differential driver current options are available.

# **Signal Descriptions (Cont.)**

| Signal Name                           | I/O | Description                                                                        |  |  |

|---------------------------------------|-----|------------------------------------------------------------------------------------|--|--|

| D7/SPID0                              | I/O | Parallel configuration I/O. SPI/SPIm data input. Open drain during configura tion. |  |  |

| DI/CSSPI0N/CEN                        | I/O | Serial data input for slave serial mode. SPI/SPIm mode chip select.                |  |  |

| Dedicated SERDES Signals <sup>2</sup> | •   |                                                                                    |  |  |

| PCS[Index]_HDINNm                     | I   | High-speed input, negative channel m                                               |  |  |

| PCS[Index]_HDOUTNm                    | 0   | High-speed output, negative channel m                                              |  |  |

| PCS[Index]_REFCLKN                    | I   | Negative Reference Clock Input                                                     |  |  |

| PCS[Index]_HDINPm                     | I   | High-speed input, positive channel m                                               |  |  |

| PCS[Index]_HDOUTPm                    | 0   | High-speed output, positive channel m                                              |  |  |

| PCS[Index]_REFCLKP                    | I   | Positive Reference Clock Input                                                     |  |  |

| PCS[Index]_VCCOBm                     | _   | Output buffer power supply, channel m (1.2V/1.5)                                   |  |  |

| PCS[Index]_VCCIBm                     | _   | Input buffer power supply, channel m (1.2V/1.5V)                                   |  |  |

<sup>1.</sup> When placing switching I/Os around these critical pins that are designed to supply the device with the proper reference or supply voltage, care must be given.

<sup>2.</sup> m defines the associated channel in the quad.

# **Pin Information Summary (Cont.)**

| Pin Information                                        | Summary              | ECP3      | -17 <b>EA</b> | ECP3-35EA |           |           |

|--------------------------------------------------------|----------------------|-----------|---------------|-----------|-----------|-----------|

| Pin Typ                                                | е                    | 256 ftBGA | 484 fpBGA     | 256 ftBGA | 484 fpBGA | 672 fpBGA |

|                                                        | Bank 0               | 13        | 18            | 13        | 21        | 24        |

|                                                        | Bank 1               | 7         | 12            | 7         | 18        | 18        |

| E 1 1 10''' 1: 11'O                                    | Bank 2               | 2         | 4             | 1         | 8         | 8         |

| Bank                                                   | Bank 3               | 4         | 13            | 5         | 20        | 19        |

|                                                        | Bank 6               | 5         | 13            | 6         | 22        | 20        |

|                                                        | Bank 7               | 6         | 10            | 6         | <b>11</b> | 13        |

|                                                        | Bank 8               | 12        | 12            | 12        | 12        | 12        |

|                                                        | Bank 0               | 0         | 0             | 0         | 0         | 0         |

|                                                        | Bank 1               | 0         | 0             | 0         | 0         | 0         |

| 15:4                                                   | Bank 2               | 2         | 3             | 3         | 6         | 6         |

| Highspeed Differential I/O per Bank                    | Bank 3               | 5         | 9             | 4         | 9         | 12        |

|                                                        | Bank 6               | 5         | 9             | 4         | 11        | 12        |

|                                                        | Bank 7               | 5         | 8             | 5         | 9         | 10        |