Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                                             |

|--------------------------------|-----------------------------------------------------------------------------|

| Product Status                 | Obsolete                                                                    |

| Number of LABs/CLBs            | 11500                                                                       |

| Number of Logic Elements/Cells | 92000                                                                       |

| Total RAM Bits                 | 4526080                                                                     |

| Number of I/O                  | 295                                                                         |

| Number of Gates                | -                                                                           |

| Voltage - Supply               | 1.14V ~ 1.26V                                                               |

| Mounting Type                  | Surface Mount                                                               |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                                          |

| Package / Case                 | 484-BBGA                                                                    |

| Supplier Device Package        | 484-FPBGA (23x23)                                                           |

| Purchase URL                   | https://www.e-xfl.com/product-detail/lattice-semiconductor/lfe3-95e-8fn484i |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

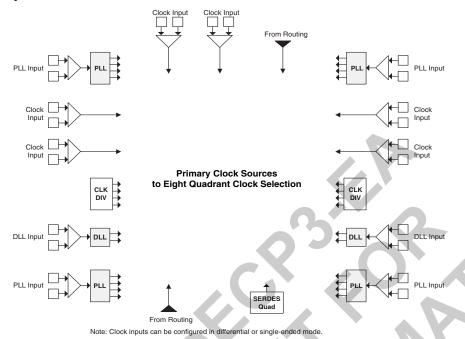

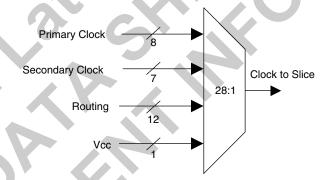

Figure 2-10. Primary Clock Sources for LatticeECP3-35

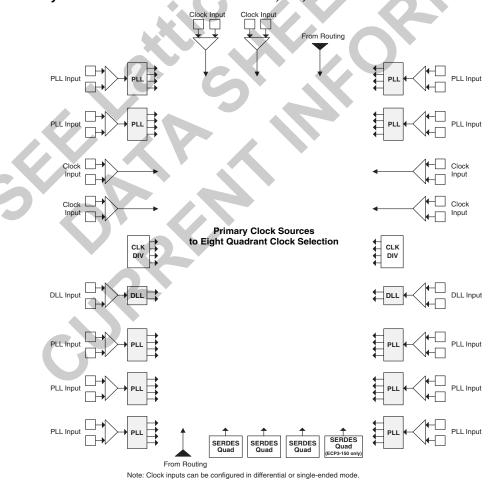

Figure 2-11. Primary Clock Sources for LatticeECP3-70, -95, -150

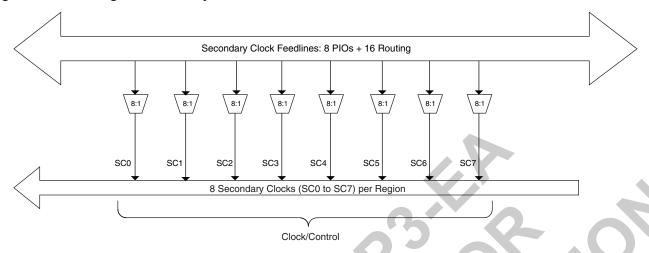

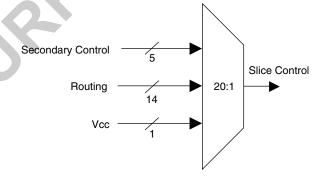

Figure 2-16. Per Region Secondary Clock Selection

#### Slice Clock Selection

Figure 2-17 shows the clock selections and Figure 2-18 shows the control selections for Slice0 through Slice2. All the primary clocks and seven secondary clocks are routed to this clock selection mux. Other signals can be used as a clock input to the slices via routing. Slice controls are generated from the secondary clocks/controls or other signals connected via routing.

If none of the signals are selected for both clock and control then the default value of the mux output is 1. Slice 3 does not have any registers; therefore it does not have the clock or control muxes.

Figure 2-17. Slice0 through Slice2 Clock Selection

Figure 2-18. Slice0 through Slice2 Control Selection

#### **ALU Flags**

The sysDSP slice provides a number of flags from the ALU including:

- Equal to zero (EQZ)

- Equal to zero with mask (EQZM)

- · Equal to one with mask (EQOM)

- · Equal to pattern with mask (EQPAT)

- Equal to bit inverted pattern with mask (EQPATB)

- · Accumulator Overflow (OVER)

- Accumulator Underflow (UNDER)

- Either over or under flow supporting LatticeECP2 legacy designs (OVERUNDER)

## Clock, Clock Enable and Reset Resources

Global Clock, Clock Enable and Reset signals from routing are available to every sysDSP slice. From four clock sources (CLK0, CLK1, CLK2, and CLK3) one clock is selected for each input register, pipeline register and output register. Similarly Clock Enable (CE) and Reset (RST) are selected at each input register, pipeline register and output register.

## Resources Available in the LatticeECP3 Family

Table 2-9 shows the maximum number of multipliers for each member of the LatticeECP3 family. Table 2-10 shows the maximum available EBR RAM Blocks in each LatticeECP3 device. EBR blocks, together with Distributed RAM can be used to store variables locally for fast DSP operations.

Table 2-9. Maximum Number of DSP Slices in the LatticeECP3 Family

| Device   | DSP Slices | 9x9 Multiplier | 18x18 Multiplier | 36x36 Multiplier |

|----------|------------|----------------|------------------|------------------|

| ECP3-17  | 12         | 48             | 24               | 6                |

| ECP3-35  | 32         | 128            | 64               | 16               |

| ECP3-70  | 64         | 256            | 128              | 32               |

| ECP3-95  | 64         | 256            | 128              | 32               |

| ECP3-150 | 160        | 640            | 320              | 80               |

Table 2-10. Embedded SRAM in the LatticeECP3 Family

| Device   | EBR SRAM Block | Total EBR SRAM<br>(Kbits) |

|----------|----------------|---------------------------|

| ECP3-17  | 38             | 700                       |

| ECP3-35  | 72             | 1327                      |

| ECP3-70  | 240            | 4420                      |

| ECP3-95  | 240            | 4420                      |

| ECP3-150 | 372            | 6850                      |

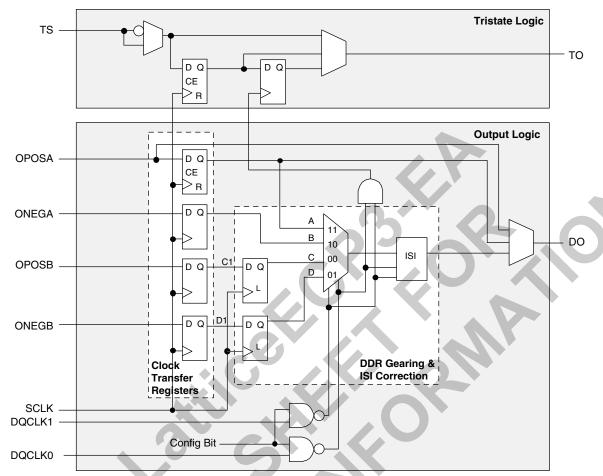

Figure 2-34. ECP3-70/95 (E or EA) Output and Tristate Block for Left and Right Edges

## **Tristate Register Block**

The tristate register block registers tri-state control signals from the core of the device before they are passed to the sysl/O buffers. The block contains a register for SDR operation and an additional register for DDR operation.

In SDR and non-gearing DDR modes, TS input feeds one of the flip-flops that then feeds the output. In DDRX2 mode, the register TS input is fed into another register that is clocked using the DQCLK0 and DQCLK1 signals. The output of this register is used as a tristate control.

#### ISI Calibration

The setting for Inter-Symbol Interference (ISI) cancellation occurs in the output register block. ISI correction is only available in the DDRX2 modes. ISI calibration settings exist once per output register block, so each I/O in a DQS-12 group may have a different ISI calibration setting.

The ISI block extends output signals at certain times, as a function of recent signal history. So, if the output pattern consists of a long strings of 0's to long strings of 1's, there are no delays on output signals. However, if there are quick, successive transitions from 010, the block will stretch out the binary 1. This is because the long trail of 0's will cause these symbols to interfere with the logic 1. Likewise, if there are quick, successive transitions from 101, the block will stretch out the binary 0. This block is controlled by a 3-bit delay control that can be set in the DQS control logic block.

For more information about this topic, please see the list of technical documentation at the end of this data sheet.

## **Control Logic Block**

The control logic block allows the selection and modification of control signals for use in the PIO block.

## **DDR Memory Support**

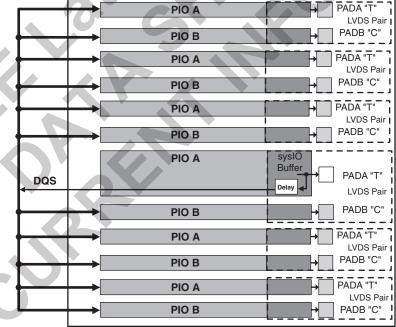

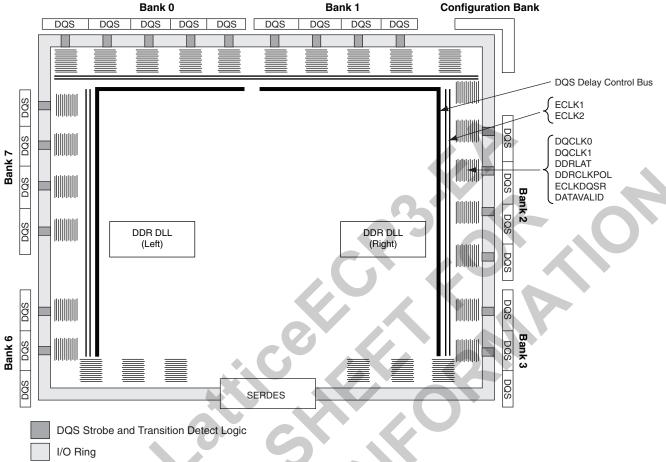

Certain PICs have additional circuitry to allow the implementation of high-speed source synchronous and DDR1, DDR2 and DDR3 memory interfaces. The support varies by the edge of the device as detailed below.

## Left and Right Edges

The left and right sides of the PIC have fully functional elements supporting DDR1, DDR2, and DDR3 memory interfaces. One of every 12 PIOs supports the dedicated DQS pins with the DQS control logic block. Figure 2-35 shows the DQS bus spanning 11 I/O pins. Two of every 12 PIOs support the dedicated DQS and DQS# pins with the DQS control logic block.

## **Bottom Edge**

PICs on the bottom edge of the device do not support DDR memory and Generic DDR interfaces.

## Top Edge

PICs on the top side are similar to the PIO elements on the left and right sides but do not support gearing on the output registers. Hence, the modes to support output/tristate DDR3 memory are removed on the top side.

The exact DQS pins are shown in a dual function in the Logic Signal Connections table in this data sheet. Additional detail is provided in the Signal Descriptions table. The DQS signal from the bus is used to strobe the DDR data from the memory into input register blocks. Interfaces on the left, right and top edges are designed for DDR memories that support 10 bits of data.

Figure 2-35. DQS Grouping on the Left, Right and Top Edges

#### **DLL Calibrated DQS Delay Block**

Source synchronous interfaces generally require the input clock to be adjusted in order to correctly capture data at the input register. For most interfaces, a PLL is used for this adjustment. However, in DDR memories the clock

Figure 2-36. Edge Clock, DLL Calibration and DQS Local Bus Distribution

<sup>\*</sup>Includes shared configuration I/Os and dedicated configuration I/Os.

## **DC Electrical Characteristics**

## **Over Recommended Operating Conditions**

| Symbol                                            | Parameter                                | Condition                                                                            | Min.                  | Тур. | Max.                  | Units |

|---------------------------------------------------|------------------------------------------|--------------------------------------------------------------------------------------|-----------------------|------|-----------------------|-------|

| I <sub>IL</sub> , I <sub>IH</sub> <sup>1, 4</sup> | Input or I/O Low Leakage                 | $0 \le V_{IN} \le (V_{CCIO} - 0.2V)$                                                 | _                     |      | 10                    | μΑ    |

| I <sub>IH</sub> <sup>1, 3</sup>                   | Input or I/O High Leakage                | $(V_{CCIO} - 0.2V) < V_{IN} \le 3.6V$                                                | _                     |      | 150                   | μΑ    |

| $I_{PU}$                                          | I/O Active Pull-up Current               | $0 \le V_{IN} \le 0.7 V_{CCIO}$                                                      | -30                   | 1    | -210                  | μΑ    |

| $I_{PD}$                                          | I/O Active Pull-down Current             | $V_{IL} (MAX) \le V_{IN} \le V_{CCIO}$                                               | 30                    | _    | 210                   | μΑ    |

| I <sub>BHLS</sub>                                 | Bus Hold Low Sustaining Current          | $V_{IN} = V_{IL} (MAX)$                                                              | 30                    | -    | _                     | μΑ    |

| I <sub>BHHS</sub>                                 | Bus Hold High Sustaining Current         | $V_{IN} = 0.7 V_{CCIO}$                                                              | -30                   |      |                       | μΑ    |

| I <sub>BHLO</sub>                                 | Bus Hold Low Overdrive Current           | $0 \le V_{IN} \le V_{CCIO}$                                                          | <b>—</b>              | -    | 210                   | μΑ    |

| I <sub>BHHO</sub>                                 | Bus Hold High Overdrive Current          | $0 \le V_{IN} \le V_{CCIO}$                                                          |                       | 1    | -210                  | μΑ    |

| $V_{BHT}$                                         | Bus Hold Trip Points                     | $0 \le V_{IN} \le V_{IH} (MAX)$                                                      | V <sub>IL</sub> (MAX) | b    | V <sub>IH</sub> (MIN) | V     |

| C1                                                | I/O Capacitance <sup>2</sup>             | $V_{CCIO} = 3.3V, 2.5V, 1.8V, 1.5V, 1.2V, V_{CC} = 1.2V, V_{IO} = 0 to V_{IH} (MAX)$ |                       | 8    |                       | pf    |

| C2                                                | Dedicated Input Capacitance <sup>2</sup> | $V_{CCIO} = 3.3V, 2.5V, 1.8V, 1.5V, 1.2V, V_{CC} = 1.2V, V_{IO} = 0 to V_{IH} (MAX)$ |                       | 6    |                       | pf    |

<sup>1.</sup> Input or I/O leakage current is measured with the pin configured as an input or as an I/O with the output driver tri-stated. It is not measured with the output driver active. Bus maintenance circuits are disabled.

<sup>2.</sup>  $T_A$  25°C, f = 1.0MHz.

Applicable to general purpose I/Os in top and bottom banks.

When used as V<sub>REF</sub> maximum leakage= 25μA.

## sysl/O Recommended Operating Conditions

|                                           |           | V <sub>CCIO</sub> |           |               | V <sub>REF</sub> (V) |       |

|-------------------------------------------|-----------|-------------------|-----------|---------------|----------------------|-------|

| Standard                                  | Min.      | Тур.              | Max.      | Min.          | Тур.                 | Max.  |

| LVCMOS33 <sup>2</sup>                     | 3.135     | 3.3               | 3.465     | _             | _                    | _     |

| LVCMOS25 <sup>2</sup>                     | 2.375     | 2.5               | 2.625     | _             | _                    | _     |

| LVCMOS18                                  | 1.71      | 1.8               | 1.89      | _             | _                    | _     |

| LVCMOS15                                  | 1.425     | 1.5               | 1.575     | _             | _                    | _     |

| LVCMOS12 <sup>2</sup>                     | 1.14      | 1.2               | 1.26      | - 4           |                      | _     |

| LVTTL33 <sup>2</sup>                      | 3.135     | 3.3               | 3.465     | 7             | <u> </u>             | _     |

| PCI33                                     | 3.135     | 3.3               | 3.465     | <i>1</i> -> \ | _                    | _     |

| SSTL15 <sup>3</sup>                       | 1.43      | 1.5               | 1.57      | 0.68          | 0.75                 | 0.9   |

| SSTL18_I, II <sup>2</sup>                 | 1.71      | 1.8               | 1.89      | 0.833         | 0.9                  | 0.969 |

| SSTL25_I, II <sup>2</sup>                 | 2.375     | 2.5               | 2.625     | 1.15          | 1.25                 | 1.35  |

| SSTL33_I, II <sup>2</sup>                 | 3.135     | 3.3               | 3.465     | 1.3           | 1.5                  | 1.7   |

| HSTL15_I <sup>2</sup>                     | 1.425     | 1.5               | 1.575     | 0.68          | 0.75                 | 0.9   |

| HSTL18_I, II <sup>2</sup>                 | 1.71      | 1.8               | 1.89      | 0.816         | 0.9                  | 1.08  |

| LVDS25 <sup>2</sup>                       | 2.375     | 2.5               | 2.625     |               | 1                    |       |

| MLVDS25 <sup>1</sup>                      | 2.375     | 2.5               | 2.625     |               |                      | _     |

| LVPECL33 <sup>1, 2</sup>                  | 3.135     | 3.3               | 3.465     | _             |                      | _     |

| Mini LVDS                                 | _         | -0                |           |               | _                    | _     |

| BLVDS25 <sup>1, 2</sup>                   | 2.375     | 2.5               | 2.625     | <b>40</b>     | _                    | _     |

| RSDS25 <sup>1, 2</sup>                    | 2.375     | 2.5               | 2.625     | -             | _                    | _     |

| RSDS25E <sup>1, 2</sup>                   | 2.375     | 2.5               | 2.625     |               | _                    | _     |

| TRLVDS                                    | 3.14      | 3.3               | 3.47      |               | _                    | _     |

| PPLVDS                                    | 3.14/2.25 | 3.3/2.5           | 3.47/2.75 | _             | _                    | _     |

| SSTL15D                                   | 1.43      | 1.5               | 1.57      | <u> </u>      | _                    | _     |

| SSTL18D_I <sup>2</sup> , II <sup>2</sup>  | 1.71      | 1.8               | 1.89      | _             | _                    | _     |

| SSTL25D_ I <sup>2</sup> , II <sup>2</sup> | 2.375     | 2.5               | 2.625     | _             | _                    | _     |

| SSTL33D_ I <sup>2</sup> , II <sup>2</sup> | 3.135     | 3.3               | 3.465     | _             | _                    | _     |

| HSTL15D_I <sup>2</sup>                    | 1.425     | 1.5               | 1.575     | _             | _                    | _     |

| HSTL18D_I <sup>2</sup> , II <sup>2</sup>  | 1.71      | 1.8               | 1.89      | _             | _                    | _     |

<sup>1.</sup> Inputs on chip. Outputs are implemented with the addition of external resistors.

<sup>2.</sup> For input voltage compatibility, refer to the "Mixed Voltage Support" section of TN1177, <u>LatticeECP3 sysIO Usage Guide</u>.

# LatticeECP3 External Switching Characteristics (Continued)<sup>1, 2</sup>

**Over Recommended Commercial Operating Conditions**

|                                   | -8                                           |                  | ·8                 | -     | -7       |          | -6      |         |        |

|-----------------------------------|----------------------------------------------|------------------|--------------------|-------|----------|----------|---------|---------|--------|

| Parameter                         | Description                                  | Device           | Min.               | Max.  | Min.     | Max.     | Min.    | Max.    | Units  |

| f <sub>MAX_GDDR</sub>             | DDRX1 Clock Frequency                        | ECP3-70E/95E     | _                  | 250   | _        | 250      | _       | 250     | MHz    |

| Generic DDRX1<br>Pin for Clock In | Inputs with Clock and Data (<10 Bits put     | Wide) Centered   | at Pin (           | GDDRX | (1_RX.I  | OQS.Ce   | entered | ) Using | DQS    |

| Left, Right and                   | Top for Data and Clock                       |                  |                    |       |          |          |         |         |        |

| t <sub>SUGDDR</sub>               | Data Valid After CLK                         | ECP3-150EA       |                    | _     |          | <b>—</b> |         | _       | ns     |

| t <sub>HGDDR</sub>                | Data Hold After CLK                          | ECP3-150EA       |                    | 17    |          | _        |         | _       | ns     |

| f <sub>MAX_GDDR</sub>             | DDRX1 Clock Frequency                        | ECP3-150EA       | _                  |       | <u> </u> |          | _       |         | ns     |

| Generic DDRX1 for Clock Input     | Inputs with Clock and Data (<10 Bits         | Wide) Aligned at | Pin (G             | DDRX1 | _RX.D    | QS.Alig  | ned) U  | sing DO | )S Pin |

| Left and Right S                  | Sides                                        |                  | 72                 |       |          |          | ,       |         |        |

| t <sub>DVACLKGDDR</sub>           | Data Setup Before CLK (Left and Right Sides) | ECP3-150EA       | _                  |       |          |          |         |         | UI     |

| t <sub>DVECLKGDDR</sub>           | Data Hold After CLK (Left and Right Sides)   | ECP3-150EA       | •                  |       |          | _        |         | _       | UI     |

| f <sub>MAX_GDDR</sub>             | DDRX1 Clock Frequency (Left and Right Sides) | ECP3-150EA       | 4                  |       |          |          | ~       |         | UI     |

| Top Side                          |                                              |                  |                    |       |          |          | •       | •       |        |

| t <sub>DVACLKGDDR</sub>           | Data Setup Before CLK (Top Side)             | ECP3-150EA       | <i>&gt;</i>        |       |          |          | _       |         | UI     |

| t <sub>DVECLKGDDR</sub>           | Data Hold After CLK (Top Side)               | ECP3-150EA       |                    | E.    |          | _        |         | _       | UI     |

| f <sub>MAX_GDDR</sub>             | DDRX1 Clock Frequency (Top Side)             | ECP3-150EA       | -/                 |       | <b>\</b> |          | _       |         | UI     |

| Pin for Clock In                  |                                              | vide) ocincied a |                    | JOHN  |          | <u> </u> |         |         | - OLK  |

| tsugddr                           | Data Setup Before CLK                        | ECP3-150EA       |                    | _     |          | _        |         | _       | ns     |

| t <sub>HGDDR</sub>                | Data Hold After CLK                          | ECP3-150EA       |                    | _     |          | _        |         | _       | ns     |

| f <sub>MAX_GDDR</sub>             | DDRX2 Clock Frequency                        | ECP3-150EA       | _                  |       | _        |          | _       |         | MHz    |

|                                   | Inputs with Clock in the Center of Da        |                  | out DLI            | ³(GDD | RX2 R    | X.FCL k  | Cente   | red)    |        |

| t <sub>SUGDDR</sub>               | Data Setup Before CLK                        | ECP3-70E/95E     | 260                |       | 312      |          | 352     |         | ps     |

| t <sub>HOGDDR</sub>               | Data Hold After CLK                          | ECP3-70E/95E     | 260                | _     | 312      | _        | 352     | _       | ps     |

| f <sub>MAX_GDDR</sub>             | DDR/DDRX2 Clock Frequency <sup>8</sup>       | ECP3-70E/95E     | _                  | 500   | _        | 420      | _       | 375     | MHz    |

|                                   | Inputs with Clock and Data (>10 Bits         |                  |                    |       | RX F     |          | aned)   | 0.0     |        |

|                                   | Side Using DLLCLKIN Pin for Clock In         | . •              |                    |       |          |          | 9       |         |        |

| † <sub>DVACLKGDDR</sub>           | Data Setup Before CLK (Left and Right Side)  | ECP3-150EA       | _                  |       | _        |          | _       |         | UI     |

| t <sub>DVECLKGDDR</sub>           | Data Hold After CLK (Left and Right Side)    | ECP3-150EA       |                    | -     |          | _        |         | _       | UI     |

| f <sub>MAX_GDDR</sub>             | DDRX1 Clock Frequency (Left and Right Side)  | ECP3-150EA       | _                  |       | _        |          | _       |         | MHz    |

| Top Side Using                    | PCLK Pin for Clock Input                     |                  |                    |       |          |          |         |         | 1      |

| t <sub>DVACLKGDDR</sub>           | Data Setup Before CLK (Top Side)             | ECP3-150EA       | _                  |       | _        |          | _       |         | UI     |

| †DVECLKGDDR                       | Data Hold After CLK (Top Side)               | ECP3-150EA       |                    | _     |          | _        |         | _       | UI     |

| f <sub>MAX_GDDR</sub>             | DDRX1 Clock Frequency (Top Side)             | ECP3-150EA       | _                  |       | _        |          | _       |         | MHz    |

|                                   | Inputs with Clock and Data Edges Al          |                  | EL <sup>3</sup> (G | DDRX2 | RX.EC    | LK.Ali   | gned)   |         | 1      |

| t <sub>DVACLKGDDR</sub>           | Data Valid After CLK                         | ECP3-70E/95E     | _                  | 0.235 | _        | 0.235    | _       | 0.235   | UI     |

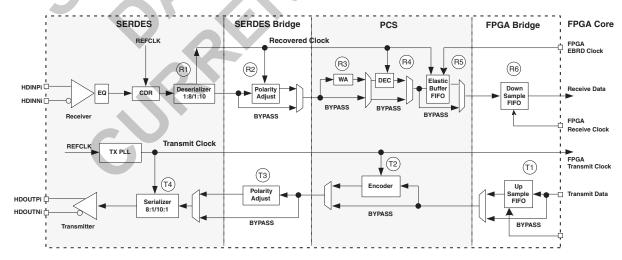

## **SERDES/PCS Block Latency**

Table 3-8 describes the latency of each functional block in the transmitter and receiver. Latency is given in parallel clock cycles. Figure 3-12 shows the location of each block.

Table 3-8. SERDES/PCS Latency Breakdown

| Item    | Description                                          | Min.     | Avg.          | Max.          | Fixed   | Bypass        | Units    |

|---------|------------------------------------------------------|----------|---------------|---------------|---------|---------------|----------|

| Transmi | t Data Latency¹                                      |          |               |               | •       | •             |          |

|         | FPGA Bridge - Gearing disabled with different clocks | 1        | 3             | 5             | _       | 1             | word clk |

| T1      | FPGA Bridge - Gearing disabled with same clocks      | _        | _             | -             | 3       | 1             | word clk |

|         | FPGA Bridge - Gearing enabled                        | 1        | 3             | 5             | _       | _             | word clk |

| T2      | 8b10b Encoder                                        | _        | -             |               | 2       | 1             | word clk |

| T3      | SERDES Bridge transmit                               | _        |               | 7             | 2       | 1             | word clk |

| T4      | Serializer: 8-bit mode                               | _        | 7-            |               | 15 + ∆1 | _             | UI + ps  |

| 14      | Serializer: 10-bit mode                              | 70       |               |               | 18 + ∆1 | - C           | UI + ps  |

| T5      | Pre-emphasis ON                                      |          | _             | -             | 1 + Δ2  | 7-            | UI + ps  |

| 15      | Pre-emphasis OFF                                     |          | - /           |               | 0 + Δ3  | 7-7           | UI + ps  |

| Receive | Data Latency <sup>2</sup>                            |          |               |               |         |               |          |

| R1      | Equalization ON                                      |          | _             | <b>&gt;</b> - | Δ1      | <b>&gt;</b> - | UI + ps  |

| n i     | Equalization OFF                                     |          | 1             |               | Δ2      | _             | UI + ps  |

| R2      | Deserializer: 8-bit mode                             |          |               | -             | 10 + ∆3 | _             | UI + ps  |

| ΠZ      | Deserializer: 10-bit mode                            | <b>/</b> |               |               | 12 + ∆3 | _             | UI + ps  |

| R3      | SERDES Bridge receive                                | <b>/</b> | _             | 1             | 2       | _             | word clk |

| R4      | Word alignment                                       | 3.1      | -             | 4             | —       | _             | word clk |

| R5      | 8b10b decoder                                        | \ -      | <i>&gt;</i> + | 7-            | 1       | _             | word clk |

| R6      | Clock Tolerance Compensation                         | 7        | 15            | 23            | 1       | 1             | word clk |

|         | FPGA Bridge - Gearing disabled with different clocks | 1        | 3             | 5             | _       | 1             | word clk |

| R7      | FPGA Bridge - Gearing disabled with same clocks      |          | <u> </u>      | _             | 3       | 1             | word clk |

|         | FPGA Bridge - Gearing enabled                        | 1        | 3             | 5             | _       | _             | word clk |

<sup>1.</sup>  $\Delta 1 = -245$ ps,  $\Delta 2 = +88$ ps,  $\Delta 3 = +112$ ps.

Figure 3-12. Transmitter and Receiver Latency Block Diagram

<sup>2.</sup>  $\Delta 1 = +118$ ps,  $\Delta 2 = +132$ ps,  $\Delta 3 = +700$ ps.

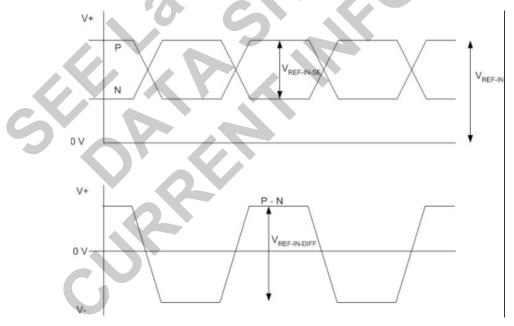

#### **SERDES External Reference Clock**

The external reference clock selection and its interface are a critical part of system applications for this product. Table 3-12 specifies reference clock requirements, over the full range of operating conditions.

Table 3-12. External Reference Clock Specification (refclkp/refclkn)

| Symbol                        | Description                                       | Min.  | Тур.     | Max.                   | Units                   |

|-------------------------------|---------------------------------------------------|-------|----------|------------------------|-------------------------|

| F <sub>REF</sub>              | Frequency range                                   | 15    | _        | 320                    | MHz                     |

| F <sub>REF-PPM</sub>          | Frequency tolerance <sup>4</sup>                  | -1000 | _        | 1000                   | ppm                     |

| V <sub>REF-IN-SE</sub>        | Input swing, single-ended clock <sup>1</sup>      | 200   | - 4      | V <sub>CCA</sub>       | mV, p-p                 |

| V <sub>REF-IN-DIFF</sub>      | Input swing, differential clock                   | 200   |          | 2*V <sub>CCA</sub>     | mV, p-p<br>differential |

| V <sub>REF-IN</sub>           | Input levels                                      | 0     |          | V <sub>CCA</sub> + 0.3 | V                       |

| V <sub>REF-CM-AC</sub>        | Input common mode range (AC coupled) <sup>2</sup> | 0.125 | <i>→</i> | V <sub>CCA</sub>       | V                       |

| D <sub>REF</sub>              | Duty cycle <sup>3</sup>                           | 40    | _        | 60                     | %                       |

| T <sub>REF-R</sub>            | Rise time (20% to 80%)                            | 200   | 500      | 1000                   | ps                      |

| T <sub>REF-F</sub>            | Fall time (80% to 20%)                            | 200   | 500      | 1000                   | ps                      |

| Z <sub>REF-IN-TERM-DIFF</sub> | Differential input termination                    | -20%  | 100/2K   | +20%                   | Ohms                    |

| C <sub>REF-IN-CAP</sub>       | Input capacitance                                 |       |          | 7                      | pF                      |

<sup>1.</sup> The signal swing for a single-ended input clock must be as large as the p-p differential swing of a differential input clock to get the same gain at the input receiver. Lower swings for the clock may be possible, but will tend to increase jitter.

Figure 3-13. SERDES External Reference Clock Waveforms

When AC coupled, the input common mode range is determined by: (Min input level) + (Peak-to-peak input swing)/2 ≤ (Input common mode voltage) ≤ (Max input level) - (Peak-to-peak input swing)/2

<sup>3.</sup> Measured at 50% amplitude.

<sup>4.</sup> Depending on the application, the PLL\_LOL\_SET and CDR\_LOL\_SET control registers may be adjusted for other tolerance values as described in TN1176, <u>LatticeECP3 SERDES/PCS Usage Guide</u>.

# **PCI Express Electrical and Timing Characteristics AC and DC Characteristics**

## **Over Recommended Operating Conditions**

| Symbol                                   | Description                                                                           | <b>Test Conditions</b>                               | Min        | Тур      | Max                    | Units |

|------------------------------------------|---------------------------------------------------------------------------------------|------------------------------------------------------|------------|----------|------------------------|-------|

| Transmit <sup>1</sup>                    |                                                                                       | 1                                                    |            |          | I.                     |       |

| UI                                       | Unit interval                                                                         |                                                      | 399.88     | 400      | 400.12                 | ps    |

| V <sub>TX-DIFF_P-P</sub>                 | Differential peak-to-peak output voltage                                              |                                                      | 0.8        | 1.0      | 1.2                    | V     |

| V <sub>TX-DE-RATIO</sub>                 | De-emphasis differential output voltage ratio                                         |                                                      | -3         | -3.5     | -4                     | dB    |

| V <sub>TX-CM-AC_P</sub>                  | RMS AC peak common-mode output voltage                                                |                                                      |            | 1        | 20                     | mV    |

| V <sub>TX-RCV-DETECT</sub>               | Amount of voltage change allowed during receiver detection                            | 0                                                    |            |          | 600                    | mV    |

| $V_{TX-DC-CM}$                           | Tx DC common mode voltage                                                             |                                                      | 0          | 1        | V <sub>CCOB</sub> + 5% | V     |

| I <sub>TX-SHORT</sub>                    | Output short circuit current                                                          | V <sub>TX-D+</sub> =0.0V<br>V <sub>TX-D-</sub> =0.0V |            | _        | 90                     | mA    |

| Z <sub>TX-DIFF-DC</sub>                  | Differential output impedance                                                         |                                                      | 80         | 100      | 120                    | Ohms  |

| RL <sub>TX-DIFF</sub>                    | Differential return loss                                                              |                                                      | 10         |          | _                      | dB    |

| RL <sub>TX-CM</sub>                      | Common mode return loss                                                               |                                                      | 6.0        |          | _                      | dB    |

| T <sub>TX-RISE</sub>                     | Tx output rise time                                                                   | 20 to 80%                                            | 0.125      |          | _                      | UI    |

| T <sub>TX-FALL</sub>                     | Tx output fall time                                                                   | 20 to 80%                                            | 0.125      | <u> </u> | _                      | UI    |

| L <sub>TX-SKEW</sub>                     | Lane-to-lane static output skew for all lanes in port/link                            |                                                      | 1          | _        | 1.3                    | ns    |

| T <sub>TX-EYE</sub>                      | Transmitter eye width                                                                 |                                                      | 0.75       | _        | _                      | UI    |

| T <sub>TX-EYE-MEDIAN-TO-MAX-JITTER</sub> | Maximum time between jitter median and maximum deviation from median                  |                                                      | _          | _        | 0.125                  | UI    |

| Receive <sup>1, 2</sup>                  |                                                                                       |                                                      |            |          |                        |       |

| UI                                       | Unit Interval                                                                         |                                                      | 399.88     | 400      | 400.12                 | ps    |

| V <sub>RX-DIFF_P-P</sub>                 | Differential peak-to-peak input voltage                                               |                                                      | $0.34^{3}$ | _        | 1.2                    | V     |

| V <sub>RX-IDLE-DET-DIFF_P-P</sub>        | Idle detect threshold voltage                                                         |                                                      | 65         | 1        | 340 <sup>3</sup>       | mV    |

| V <sub>RX-CM-AC_P</sub>                  | Receiver common mode voltage for AC coupling                                          |                                                      |            | _        | 150                    | mV    |

| Z <sub>RX-DIFF-DC</sub>                  | DC differential input impedance                                                       |                                                      | 80         | 100      | 120                    | Ohms  |

| Z <sub>RX-DC</sub>                       | DC input impedance                                                                    |                                                      | 40         | 50       | 60                     | Ohms  |

| Z <sub>RX-HIGH-IMP-DC</sub>              | Power-down DC input impedance                                                         |                                                      | 200K       | _        | _                      | Ohms  |

| RL <sub>RX-DIFF</sub>                    | Differential return loss                                                              |                                                      | 10         |          | _                      | dB    |

| RL <sub>RX-CM</sub>                      | Common mode return loss                                                               |                                                      | 6.0        | _        | _                      | dB    |

| T <sub>RX-IDLE-DET-DIFF-ENTERTIME</sub>  | Maximum time required for receiver to recognize and signal an unexpected idle on link |                                                      |            |          | _                      | ms    |

<sup>1.</sup> Values are measured at 2.5 Gbps.

<sup>2.</sup> Measured with external AC-coupling on the receiver.

<sup>3.</sup>Not in compliance with PCI Express 1.1 standard.

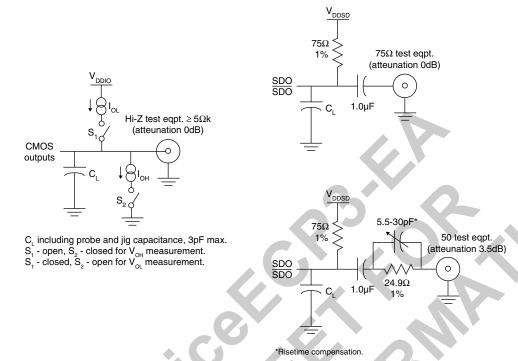

Figure 3-15. Test Loads

#### **Test Loads**

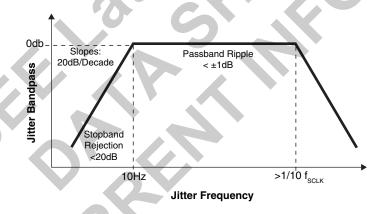

#### **Timing Jitter Bandpass**

## **LatticeECP3 sysCONFIG Port Timing Specifications (Continued)**

## **Over Recommended Operating Conditions**

| Parameter         | Description                              | Min. | Max. | Units |  |  |

|-------------------|------------------------------------------|------|------|-------|--|--|

| t <sub>CHHH</sub> | HOLDN Low Hold Time (Relative to CCLK)   | 5    | _    | ns    |  |  |

| Master and        | ster and Slave SPI (Continued)           |      |      |       |  |  |

| t <sub>CHHL</sub> | HOLDN High Hold Time (Relative to CCLK)  | 5    |      | ns    |  |  |

| t <sub>HHCH</sub> | HOLDN High Setup Time (Relative to CCLK) | 5    | _    | ns    |  |  |

| t <sub>HLQZ</sub> | HOLDN to Output High-Z                   | _    | 9    | ns    |  |  |

| t <sub>HHQX</sub> | HOLDN to Output Low-Z                    | _    | 9    | ns    |  |  |

| Parameter              | Min.                 | Max.                 | Units |

|------------------------|----------------------|----------------------|-------|

| Master Clock Frequency | Selected value - 15% | Selected value + 15% | MHz   |

| Duty Cycle             | 40                   | 60                   | %     |

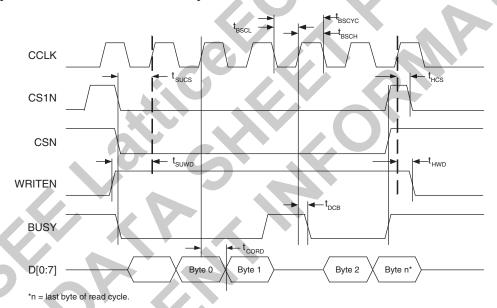

Figure 3-16. sysCONFIG Parallel Port Read Cycle

# LatticeECP3 Family Data Sheet Pinout Information

March 2010 Preliminary Data Sheet DS1021

## **Signal Descriptions**

| Signal Name                               | I/O | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-------------------------------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| General Purpose                           |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| P[Edga] [Paw/Calumn Number] [A/P]         | I/O | [Edge] indicates the edge of the device on which the pad is located. Valid edge designations are L (Left), B (Bottom), R (Right), T (Top).  [Row/Column Number] indicates the PFU row or the column of the device on which the PIC exists. When Edge is T (Top) or B (Bottom), only need to specify Column Number. When Edge is L (Left) or R (Right), only need to specify Row Number.                                                                                                                |

| P[Edge] [Row/Column Number]_[A/B]         |     | [A/B] indicates the PIO within the PIC to which the pad is connected. Some of these user-programmable pins are shared with special function pins. These pins, when not used as special purpose pins, can be programmed as I/Os for user logic. During configuration the user-programmable I/Os are tri-stated with an internal pull-up resistor enabled. If any pin is not used (or not bonded to a package pin), it is also tri-stated with an internal pull-up resistor enabled after configuration. |

| P[Edge][Row Number]E_[A/B/C/D]            | I   | These general purpose signals are input-only pins and are located near the PLLs.                                                                                                                                                                                                                                                                                                                                                                                                                       |

| GSRN                                      | I.  | Global RESET signal (active low). Any I/O pin can be GSRN.                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| NC                                        | -   | No connect.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| RESERVED                                  |     | This pin is reserved and should not be connected to anything on the board.                                                                                                                                                                                                                                                                                                                                                                                                                             |

| GND                                       |     | Ground. Dedicated pins.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| V <sub>CC</sub>                           | ) _ | Power supply pins for core logic. Dedicated pins.                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| V <sub>CCAUX</sub>                        |     | Auxiliary power supply pin. This dedicated pin powers all the differential and referenced input buffers.                                                                                                                                                                                                                                                                                                                                                                                               |

| V <sub>CCIOx</sub>                        | 4   | Dedicated power supply pins for I/O bank x.                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| V <sub>CCA</sub>                          |     | SERDES, transmit, receive, PLL and reference clock buffer power supply.                                                                                                                                                                                                                                                                                                                                                                                                                                |

| V <sub>CCPLL_[LOC]</sub>                  |     | General purpose PLL supply pins where LOC=L (left) or R (right).                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| V <sub>REF1_x</sub> , V <sub>REF2_x</sub> | _   | Reference supply pins for I/O bank x. Pre-determined pins in each bank are assigned as $V_{\text{REF}}$ inputs. When not used, they may be used as I/O pins.                                                                                                                                                                                                                                                                                                                                           |

| VTTx                                      | Y   | Power supply for on-chip termination of I/Os (Required for DDR3 and LVDS at 1.25Gbps).                                                                                                                                                                                                                                                                                                                                                                                                                 |

| XRES <sup>1</sup>                         |     | 10K ohm +/-1% resistor must be connected between this pad and ground.                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| PLL, DLL and Clock Functions              | V   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| [LOC][num]_GPLL[T, C]_IN_[index]          |     | General Purpose PLL (GPLL) input pads: LUM, LLM, RUM, RLM, num = row from center, T = true and C = complement, index A,B,Cat each side.                                                                                                                                                                                                                                                                                                                                                                |

| [LOC][num]_GPLL[T, C]_FB_[index]          | I   | Optional feedback GPLL input pads: LUM, LLM, RUM, RLM, num = row from center, T = true and C = complement, index A,B,Cat each side.                                                                                                                                                                                                                                                                                                                                                                    |

| [LOC]0_GDLLT_IN_[index]                   | I/O | General Purpose DLL (GDLL) input pads where LOC=RUM or LUM, T is True Complement, index is A or B.                                                                                                                                                                                                                                                                                                                                                                                                     |

| [LOC]0_GDLLT_FB_[index]                   | I/O | Optional feedback GDLL input pads where LOC=RUM or LUM, T is True Complement, index is A or B.                                                                                                                                                                                                                                                                                                                                                                                                         |

| PCLK[T, C][n:0]_[3:0]                     | -   | Primary Clock pads, T = true and C = complement, n per side, indexed by bank and 0, 1, 2, 3 within bank.                                                                                                                                                                                                                                                                                                                                                                                               |

# **Pin Information Summary (Cont.)**

| Pin Information Summary                                |                      | ECP3-17EA |           | ECP3-35EA |           |           |

|--------------------------------------------------------|----------------------|-----------|-----------|-----------|-----------|-----------|

| Pin Type                                               |                      | 256 ftBGA | 484 fpBGA | 256 ftBGA | 484 fpBGA | 672 fpBGA |

|                                                        | Bank 0               | 13        | 18        | 13        | 21        | 24        |

|                                                        | Bank 1               | 7         | 12        | 7         | 18        | 18        |

| E 1 1 10''' 1: 11'O                                    | Bank 2               | 2         | 4         | 1         | 8         | 8         |

| Emulated Differential I/O per Bank                     | Bank 3               | 4         | 13        | 5         | 20        | 19        |

| Barne                                                  | Bank 6               | 5         | 13        | 6         | 22        | 20        |

|                                                        | Bank 7               | 6         | 10        | 6         | <b>11</b> | 13        |

|                                                        | Bank 8               | 12        | 12        | 12        | 12        | 12        |

|                                                        | Bank 0               | 0         | 0         | 0         | 0         | 0         |

|                                                        | Bank 1               | 0         | 0         | 0         | 0         | 0         |

| 15:4                                                   | Bank 2               | 2         | 3         | 3         | 6         | 6         |

| Highspeed Differential I/O per Bank                    | Bank 3               | 5         | 9         | 4         | 9         | 12        |

|                                                        | Bank 6               | 5         | 9         | 4         | 11        | 12        |

|                                                        | Bank 7               | 5         | 8         | 5         | 9         | 10        |

|                                                        | Bank 8               | 0         | 0         | 0         | 0         | 0         |

|                                                        | Bank 0               | 26/13     | 36/18     | 26/13     | 42/21     | 48/24     |

|                                                        | Bank 1               | 14/7      | 24/12     | 14/7      | 36/18     | 36/18     |

| T. 10: 1 F 1 1/T. 1                                    | Bank 2               | 8/4       | 14/7      | 8/4       | 28/14     | 28/14     |

| Total Single Ended/ Total<br>Differential I/O per Bank | Bank 3               | 18/9      | 44/22     | 18/9      | 58/29     | 63/31     |

|                                                        | Bank 6               | 20/10     | 44/22     | 20/10     | 67/33     | 65/32     |

|                                                        | Bank 7               | 23/11     | 36/18     | 23/11     | 40/20     | 46/23     |

|                                                        | Bank 8               | 24/12     | 24/12     | 24/12     | 24/12     | 24/12     |

| DDR Groups Bonded per<br>Bank                          | Bank 0               | 2         | 3         | 2         | 3         | 4         |

|                                                        | Bank 1               | 1         | 2         | 1         | 3         | 3         |

|                                                        | Bank 2               | 0         | 1         | 0         | 2         | 2         |

|                                                        | Bank 3               | 1         | 3         | 1         | 3         | 4         |

|                                                        | Bank 6               | 1         | 3         | 1         | 4         | 4         |

|                                                        | Bank 7               | 1         | 2         | 1         | 3         | 3         |

|                                                        | Configuration Bank 8 | 0         | 0         | 0         | 0         | 0         |

| SERDES Quads                                           |                      | 1         | 1         | 1         | 1         | 1         |

<sup>1.</sup> These pins must remain floating on the board.

# **Pin Information Summary (Cont.)**

| Pin Information Summary Pin Type           |        |              | ECP3-95E/EA  |               | ECP3-        | 150EA         |

|--------------------------------------------|--------|--------------|--------------|---------------|--------------|---------------|

|                                            |        | 484<br>fpBGA | 672<br>fpBGA | 1156<br>fpBGA | 672<br>fpBGA | 1156<br>fpBGA |

|                                            | Bank 0 | 42           | 60           | 86            | 60           | 94            |

|                                            | Bank 1 | 36           | 48           | 78            | 48           | 86            |

|                                            | Bank 2 | 24           | 34           | 36            | 34           | 58            |

| General Purpose<br>Inputs/Outputs per bank | Bank 3 | 54           | 59           | 86            | 59           | 104           |

| mpato/Outputo per bank                     | Bank 6 | 63           | 67           | 86            | 67           | 104           |

|                                            | Bank 7 | 36           | 48           | 54            | 48           | 76            |

|                                            | Bank 8 | 24           | 24           | 24            | 24           | 24            |

|                                            | Bank 0 | 0            | 0            | 0             | 0            | 0             |

|                                            | Bank 1 | 0            | 0            | 0             | 0            | 0             |

|                                            | Bank 2 | 4            | 8            | 8             | 8            | 8             |

| General Purpose Inputs per<br>Bank         | Bank 3 | 4            | 12           | 12            | 12           | 12            |

| Dalik                                      | Bank 6 | 4            | 12           | 12            | 12           | 12            |

|                                            | Bank 7 | 4            | 8            | 8             | 8            | 8             |

|                                            | Bank 8 | 0            | 0            | 0             | 0            | 0             |

|                                            | Bank 0 | 0            | 0            | 0             | 0            | 0             |

|                                            | Bank 1 | 0            | 0            | 0             | 0            | 0             |

|                                            | Bank 2 | 0            | 0            | 0             | 0            | 0             |

| General Purpose Outputs per<br>Bank        | Bank 3 | 0            | 0            | 0             | 0            | 0             |

| Dalik                                      | Bank 6 | 0            | 0            | 0             | 0            | 0             |

|                                            | Bank 7 | 0            | 0            | 0             | 0            | 0             |

|                                            | Bank 8 | 0            | 0            | 0             | 0            | 0             |

| Total Single-Ended User I/O                |        | 295          | 380          | 490           | 380          | 586           |

| VCC                                        |        | 16           | 32           | 32            | 32           | 32            |

| VCCAUX                                     |        | 8            | 12           | 16            | 12           | 16            |

| VTT                                        |        | 4            | 4            | 8             | 4            | 8             |

| VCCA                                       |        | 4            | 8            | 16            | 8            | 16            |

| VCCPLL                                     |        | 4            | 4            | 4             | 4            | 4             |

|                                            | Bank 0 | 2            | 4            | 4             | 4            | 4             |

|                                            | Bank 1 | 2            | 4            | 4             | 4            | 4             |

| VCCIO                                      | Bank 2 | 2            | 4            | 4             | 4            | 4             |

|                                            | Bank 3 | 2            | 4            | 4             | 4            | 4             |

|                                            | Bank 6 | 2            | 4            | 4             | 4            | 4             |

|                                            | Bank 7 | 2            | 4            | 4             | 4            | 4             |

|                                            | Bank 8 | 2            | 2            | 2             | 2            | 2             |

| VCCJ                                       |        | 1            | 1            | 1             | 1            | 1             |

| TAP                                        |        | 4            | 4            | 4             | 4            | 4             |

| GND, GNDIO                                 |        | 98           | 139          | 233           | 139          | 233           |

| NC                                         |        | 0            | 0            | 238           | 0            | 116           |

| Reserved <sup>1</sup>                      |        | 2            | 2            | 2             | 2            | 2             |

| SERDES                                     |        | 26           | 52           | 78            | 52           | 104           |

| Miscellaneous Pins                         |        | 8            | 8            | 8             | 8            | 8             |

| Total Bonded Pins                          | 484    | 672          | 1156         | 672           | 1156         |               |

## **Logic Signal Connections**

Package pinout information can be found under "Data Sheets" on the LatticeECP3 product pages on the Lattice website at <a href="www.latticesemi.com/products/fpga/ecp3">www.latticesemi.com/products/fpga/ecp3</a> and in the Lattice ispLEVER Design Planner software. To create pinout information from within Design Planner, select View -> Package View. Then select Select File -> Export and choose a type of output file. See Design Planner help for more information.

## **Thermal Management**

Thermal management is recommended as part of any sound FPGA design methodology. To assess the thermal characteristics of a system, Lattice specifies a maximum allowable junction temperature in all device data sheets. Designers must complete a thermal analysis of their specific design to ensure that the device and package do not exceed the junction temperature limits. Refer to the Thermal Management document to find the device/package specific thermal values.

#### For Further Information

For further information regarding Thermal Management, refer to the following:

- Thermal Management document

- TN1181, Power Consumption and Management for LatticeECP3 Devices

- Power Calculator tool included with the Lattice ispLEVER design tool, or as a standalone download from www.latticesemi.com/software

| Part Number            | Voltage | Grade | Package         | Pins | Temp. | LUTs (K) |

|------------------------|---------|-------|-----------------|------|-------|----------|

| LFE3-150EA-6FN672CTW*  | 1.2V    | -6    | Lead-Free fpBGA | 672  | COM   | 149      |

| LFE3-150EA-7FN672CTW*  | 1.2V    | -7    | Lead-Free fpBGA | 672  | COM   | 149      |

| LFE3-150EA-8FN672CTW*  | 1.2V    | -8    | Lead-Free fpBGA | 672  | COM   | 149      |

| LFE3-150EA-6FN1156CTW* | 1.2V    | -6    | Lead-Free fpBGA | 1156 | COM   | 149      |

| LFE3-150EA-7FN1156CTW* | 1.2V    | -7    | Lead-Free fpBGA | 1156 | COM   | 149      |

| LFE3-150EA-8FN1156CTW* | 1.2V    | -8    | Lead-Free fpBGA | 1156 | COM   | 149      |

\*Note: Specifications for the LFE3-150EA-*sp*FN*pkg*CTW and LFE3-150EA-*sp*FN*pkg*ITW devices, (where *sp* is the speed and *pkg* is the package), are the same as the LFE3-150EA-*sp*FN*pkg*C and LFE3-150EA-*sp*FN*pkg*I devices respectively, except as specified below.

- The CTC (Clock Tolerance Circuit) inside the SERDES hard PCS in the TW device is not functional but it can be bypassed and implemented in soft IP.

- The SERDES XRES pin on the TW device passes CDM testing at 250V.

| Date                | Version         | Section                                        | Change Summary                                                                                                                                                                                                                                                                                                                            |

|---------------------|-----------------|------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| May 2009<br>(cont.) | 01.1<br>(cont.) | DC and Switching<br>Characteristics<br>(cont.) | Updated timing information                                                                                                                                                                                                                                                                                                                |

|                     |                 | , ,                                            | Updated SERDES minimum frequency.                                                                                                                                                                                                                                                                                                         |

|                     |                 |                                                | Added data to the following tables: External Switching Characteristics, Internal Switching Characteristics, Family Timing Adders, Maximum I/O Buffer Speed, DLL Timing, High Speed Data Transmitter, Channel Output Jitter, Typical Building Block Function Performance, Register-to-Register Performance, and Power Supply Requirements. |

|                     |                 |                                                | Updated Serial Input Data Specifications table.                                                                                                                                                                                                                                                                                           |

|                     |                 |                                                | Updated Transmit table, Serial Rapid I/O Type 2 Electrical and Timing Characteristics section.                                                                                                                                                                                                                                            |

|                     |                 | Pinout Information                             | Updated Signal Description tables.                                                                                                                                                                                                                                                                                                        |

|                     |                 |                                                | Updated Pin Information Summary tables and added footnote 1.                                                                                                                                                                                                                                                                              |

| July 2009           | 01.2            | Multiple                                       | Changed references of "multi-boot" to "dual-boot" throughout the data sheet.                                                                                                                                                                                                                                                              |

|                     |                 | Architecture                                   | Updated On-Chip Programmable Termination bullets.                                                                                                                                                                                                                                                                                         |

|                     |                 |                                                | Updated On-Chip Termination Options for Input Modes table.                                                                                                                                                                                                                                                                                |

|                     |                 |                                                | Updated On-Chip Termination figure.                                                                                                                                                                                                                                                                                                       |

|                     |                 | DC and Switching<br>Characterisitcs            | Changed min/max data for FREF_PPM and added footnote 4 in SERDES External Reference Clock Specification table.                                                                                                                                                                                                                            |

|                     |                 |                                                | Updated SERDES minimum frequency.                                                                                                                                                                                                                                                                                                         |

|                     |                 | Pinout Information                             | Corrected MCLK to be I/O and CCLK to be I in Signal Descriptions table                                                                                                                                                                                                                                                                    |

| August 2009         | 01.3            | DC and Switching<br>Characterisitcs            | Corrected truncated numbers for $V_{\text{CCIB}}$ and $V_{\text{CCOB}}$ in Recommended Operating Conditions table.                                                                                                                                                                                                                        |

| September 2009      | 01.4            | Architecture                                   | Corrected link in sysMEM Memory Block section.                                                                                                                                                                                                                                                                                            |

|                     |                 | .0.                                            | Updated information for On-Chip Programmable Termination and modified corresponding figure.                                                                                                                                                                                                                                               |

|                     |                 |                                                | Added footnote 2 to On-Chip Programmable Termination Options for Input Modes table.                                                                                                                                                                                                                                                       |

|                     |                 |                                                | Corrected Per Quadrant Primary Clock Selection figure.                                                                                                                                                                                                                                                                                    |

|                     |                 | DC and Switching<br>Characterisitcs            | Modified -8 Timing data for 1024x18 True-Dual Port RAM (Read-Before-Write, EBR Output Registers)                                                                                                                                                                                                                                          |

|                     |                 |                                                | Added ESD Performance table.                                                                                                                                                                                                                                                                                                              |

|                     |                 |                                                | LatticeECP3 External Switching Characteristics table - updated data for                                                                                                                                                                                                                                                                   |

|                     |                 |                                                | t <sub>DIBGDDR</sub> , t <sub>W_PRI</sub> , t <sub>W_EDGE</sub> and t <sub>SKEW_EDGE_DQS</sub> .  LatticeECP3 Internal Switching Characteristics table - updated data for                                                                                                                                                                 |

|                     |                 |                                                | t <sub>COO_PIO</sub> and added footnote #4.                                                                                                                                                                                                                                                                                               |