Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Item           | Description                                                                 |  |  |  |  |  |  |

|----------------|-----------------------------------------------------------------------------|--|--|--|--|--|--|

| Power-down     | Seven power-down modes                                                      |  |  |  |  |  |  |

| modes          | Sleep (high-speed) mode                                                     |  |  |  |  |  |  |

|                | Sleep (medium-speed) mode                                                   |  |  |  |  |  |  |

|                | Standby mode                                                                |  |  |  |  |  |  |

|                | Watch mode                                                                  |  |  |  |  |  |  |

|                | Subsleep mode                                                               |  |  |  |  |  |  |

| Subactive mode |                                                                             |  |  |  |  |  |  |

|                | Active (medium-speed) mode                                                  |  |  |  |  |  |  |

| Memory         | Large on-chip memory                                                        |  |  |  |  |  |  |

|                | <ul> <li>H8/3842R, H8/38342, H8/38442: 16-Kbyte ROM, 1-Kbyte RAM</li> </ul> |  |  |  |  |  |  |

|                | <ul> <li>H8/3843R, H8/38343, H8/38443: 24-Kbyte ROM, 1-Kbyte RAM</li> </ul> |  |  |  |  |  |  |

|                | • H8/3844R, H8/3844S, H8/38344, H8/38444: 32-Kbyte ROM, 2-Kbyte RAM         |  |  |  |  |  |  |

|                | • H8/3845R, H8/3845S, H8/38345, H8/38445: 40-Kbyte ROM, 2-Kbyte RAM         |  |  |  |  |  |  |

|                | • H8/3846R, H8/3846S, H8/38346, H8/38446: 48-Kbyte ROM, 2-Kbyte RAM         |  |  |  |  |  |  |

|                | • H8/3847R, H8/3847S, H8/38347, H8/38447: 60-Kbyte ROM, 2-Kbyte RAM         |  |  |  |  |  |  |

| I/O ports      | 84 pins                                                                     |  |  |  |  |  |  |

|                | • 71 I/O pins                                                               |  |  |  |  |  |  |

|                | 13 input pins                                                               |  |  |  |  |  |  |

### Section 1 Overview

| Item                    | Description                                                                                                                                                             |

|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Timers                  | Six on-chip timers                                                                                                                                                      |

|                         | Timer A: 8-bit timer                                                                                                                                                    |

|                         | Count-up timer with selection of eight internal clock signals divided from the system clock $(\phi)^*$ and four clock signals divided from the watch clock $(\phi w)^*$ |

|                         | Asynchronous event counter: 16-bit timer                                                                                                                                |

|                         | <ul> <li>Count-up timer able to count asynchronous external events<br/>independently of the MCU's internal clocks</li> </ul>                                            |

|                         | Timer C: 8-bit timer                                                                                                                                                    |

|                         | <ul> <li>Count-up/down timer with selection of seven internal clock signals or<br/>event input from external pin</li> </ul>                                             |

|                         | — Auto-reloading                                                                                                                                                        |

|                         | Timer F: 16-bit timer                                                                                                                                                   |

|                         | <ul> <li>Can be used as two independent 8-bit timers</li> </ul>                                                                                                         |

|                         | <ul> <li>Count-up timer with selection of four internal clock signals or event<br/>input from external pin</li> </ul>                                                   |

|                         | <ul> <li>Provision for toggle output by means of compare-match function</li> </ul>                                                                                      |

|                         | Timer G: 8-bit timer                                                                                                                                                    |

|                         | <ul> <li>Count-up timer with selection of four internal clock signals</li> </ul>                                                                                        |

|                         | <ul> <li>Incorporates input capture function (built-in noise canceler)</li> </ul>                                                                                       |

|                         | Watchdog timer                                                                                                                                                          |

|                         | <ul> <li>Reset signal generated by overflow of 8-bit counter</li> </ul>                                                                                                 |

| Serial                  | Three serial communication interface channels on chip                                                                                                                   |

| communication interface | <ul> <li>SCI1: Synchronous serial interface<br/>Choice of 8-bit or 16-bit transfer data</li> </ul>                                                                      |

|                         | <ul> <li>SCI3-1: 8-bit synchronous/asynchronous serial interface</li> </ul>                                                                                             |

|                         | Incorporates multiprocessor communication function                                                                                                                      |

|                         | <ul> <li>SCI3-2: 8-bit synchronous/asynchronous serial interface<br/>Incorporates multiprocessor communication function</li> </ul>                                      |

| 14-bit PWM              | Pulse-division PWM output for reduced ripple                                                                                                                            |

|                         | <ul> <li>Can be used as a 14-bit D/A converter by connecting to an external low-<br/>pass filter.</li> </ul>                                                            |

## 6. Wakeup Interrupt Request Register (IWPR)

| Bit           | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |

|---------------|--------|--------|--------|--------|--------|--------|--------|--------|

|               | IWPF7  | IWPF6  | IWPF5  | IWPF4  | IWPF3  | IWPF2  | IWPF1  | IWPF0  |

| Initial value | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      |

| Read/Write    | R/(W)* |

Note: \* All bits can only be written with 0, for flag clearing.

IWPR is an 8-bit read/write register containing wakeup interrupt request flags. When one of pins  $\overline{WKP}_7$  to  $\overline{WKP}_0$  is designated for wakeup input and a rising or falling edge is input at that pin, the corresponding flag in IWPR is set to 1. A flag is not cleared automatically when the corresponding interrupt is accepted. Flags must be cleared by writing 0.

Bits 7 to 0: Wakeup interrupt request flags (IWPF7 to IWPF0)

| Bit n<br>IWPFn | Description                                                                                                   |               |

|----------------|---------------------------------------------------------------------------------------------------------------|---------------|

| 0              | Clearing condition: (in<br>When IWPFn= 1, it is cleared by writing 0                                          | iitial value) |

| 1              | Setting condition:<br>When pin WKPn is designated for wakeup input and a rising or falling edg<br>at that pin | je is input   |

(n = 7 to 0)

### 7. Wakeup Edge Select Register (WEGR)

| Bit           | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |

|---------------|--------|--------|--------|--------|--------|--------|--------|--------|

|               | WKEGS7 | WKEGS6 | WKEGS5 | WKEGS4 | WKEGS3 | WKEGS2 | WKEGS1 | WKEGS0 |

| Initial value | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      |

| Read/Write    | R/W    |

WEGR is an 8-bit read/write register that specifies rising or falling edge sensing for pins  $\overline{WKPn}$ .

WEGR is initialized to H'00 by a reset.

| Interrupt Request |          |                                                                                                      |

|-------------------|----------|------------------------------------------------------------------------------------------------------|

| Flags S           | Set to 1 | Conditions                                                                                           |

| IRR1              | IRRI4    | When PMR1 bit IRQ4 is changed from 0 to 1 while pin $\overline{IRQ}_4$ is low and IEGR bit IEG4 = 0. |

|                   |          | When PMR1 bit IRQ4 is changed from 1 to 0 while pin $\overline{IRQ}_4$ is low and IEGR bit IEG4 = 1. |

|                   | IRRI3    | When PMR1 bit IRQ3 is changed from 0 to 1 while pin $\overline{IRQ}_3$ is low and IEGR bit IEG3 = 0. |

|                   |          | When PMR1 bit IRQ3 is changed from 1 to 0 while pin $\overline{IRQ}_3$ is low and IEGR bit IEG3 = 1. |

|                   | IRRI2    | When PMR1 bit IRQ2 is changed from 0 to 1 while pin $\overline{IRQ}_2$ is low and IEGR bit IEG2 = 0. |

|                   |          | When PMR1 bit IRQ2 is changed from 1 to 0 while pin $\overline{IRQ}_2$ is low and IEGR bit IEG2 = 1. |

|                   | IRRI1    | When PMR1 bit IRQ1 is changed from 0 to 1 while pin $\overline{IRQ}_1$ is low and IEGR bit IEG1 = 0. |

|                   |          | When PMR1 bit IRQ1 is changed from 1 to 0 while pin $\overline{IRQ}_1$ is low and IEGR bit IEG1 = 1. |

|                   | IRRI0    | When PMR3 bit IRQ0 is changed from 0 to 1 while pin $\overline{IRQ}_0$ is low and IEGR bit IEG0 = 0. |

|                   |          | When PMR3 bit IRQ0 is changed from 1 to 0 while pin $\overline{IRQ}_0$ is low and IEGR bit IEG0 = 1. |

| IWPR              | IWPF7    | When PMR5 bit WKP7 is changed from 0 to 1 while pin $\overline{WKP}_7$ is low.                       |

|                   | IWPF6    | When PMR5 bit WKP6 is changed from 0 to 1 while pin $\overline{\text{WKP}}_6$ is low.                |

|                   | IWPF5    | When PMR5 bit WKP5 is changed from 0 to 1 while pin $\overline{WKP}_5$ is low.                       |

|                   | IWPF4    | When PMR5 bit WKP4 is changed from 0 to 1 while pin $\overline{WKP}_4$ is low.                       |

|                   | IWPF3    | When PMR5 bit WKP3 is changed from 0 to 1 while pin $\overline{WKP}_3$ is low.                       |

|                   | IWPF2    | When PMR5 bit WKP2 is changed from 0 to 1 while pin $\overline{WKP}_2$ is low.                       |

|                   | IWPF1    | When PMR5 bit WKP1 is changed from 0 to 1 while pin $\overline{WKP}_1$ is low.                       |

|                   | IWPF0    | When PMR5 bit WKP0 is changed from 0 to 1 while pin $\overline{\text{WKP}}_0$ is low.                |

#### Table 3.5 Conditions Under which Interrupt Request Flag is Set to 1

Figure 3.7 shows the procedure for setting a bit in a port mode register and clearing the interrupt request flag.

When switching a pin function, mask the interrupt before setting the bit in the port mode register. After accessing the port mode register, execute at least one instruction (e.g., NOP), then clear the interrupt request flag from 1 to 0. If the instruction to clear the flag is executed immediately after the port mode register access without executing an intervening instruction, the flag will not be cleared.

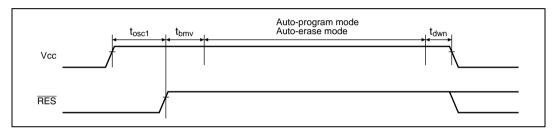

### 6.10.8 Programmer Mode Transition Time

Commands cannot be accepted during the oscillation stabilization period or the programmer mode setup period. After the programmer mode setup time, a transition is made to memory read mode.

| <b>Table 6.23</b> | Stipulated Transition Times to Command Wait State |

|-------------------|---------------------------------------------------|

|-------------------|---------------------------------------------------|

| Item                                               | Symbol            | Min | Мах | Unit | Notes       |

|----------------------------------------------------|-------------------|-----|-----|------|-------------|

| Oscillation stabilization time(crystal oscillator) | T <sub>osc1</sub> | 10  | _   | ms   | Figure 6.20 |

| Oscillation stabilization time(ceramic oscillator) | T <sub>osc1</sub> | 5   |     | ms   |             |

| Programmer mode setup time                         | T <sub>bmv</sub>  | 10  |     | ms   |             |

| Vcc hold time                                      | $T_{dwn}$         | 0   |     | ms   |             |

Figure 6.20 Oscillation Stabilization Time, Boot Program Transfer Time, and Power-Down Sequence

#### 6.10.9 Notes on Memory Programming

- 1. When performing programming using programmer mode on a chip that has been programmed/erased in an on-board programming mode, auto-erasing is recommended before carrying out auto-programming.

- 2. The flash memory is initially in the erased state when the device is shipped by Renesas Technology. For other chips for which the erasure history is unknown, it is recommended that auto-erasing be executed to check and supplement the initialization (erase) level.

#### 8.9.3 **Pin Functions**

Table 8.24 shows the port 8 pin functions.

#### Table 8.24 Port 8 Pin Functions

#### Pin Pin Functions and Selection Method

$\begin{array}{ll} P8_7/SEG_{32} & \mbox{The pin function depends on bit PCR8}_n \mbox{ in PCR8 and bits SGS3 to SGS0 in} \\ to P8_0/SEG_{25} & \mbox{LPCR}. \end{array}$

(n = 7 to 0)

| SGS3 to SGS0 | (                         | 001*, 01**,1***            |                                |

|--------------|---------------------------|----------------------------|--------------------------------|

| PCR8n        | 0                         | *                          |                                |

| Pin function | P8 <sub>n</sub> input pin | P8 <sub>n</sub> output pin | SEG <sub>n+25</sub> output pin |

\*: Don't care

#### 8.9.4 Pin States

Table 8.25 shows the port 8 pin states in each operating mode.

#### Table 8.25 Port 8 Pin States

| Pins                   | Reset              | Sleep                        | Subsleep                     | Standby            | Watch                        | Subactive  | Active     |

|------------------------|--------------------|------------------------------|------------------------------|--------------------|------------------------------|------------|------------|

| P87/SEG32 to P80/SEG25 | High-<br>impedance | Retains<br>previous<br>state | Retains<br>previous<br>state | High-<br>impedance | Retains<br>previous<br>state | Functional | Functional |

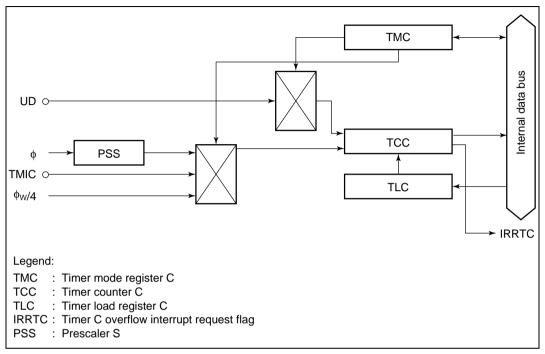

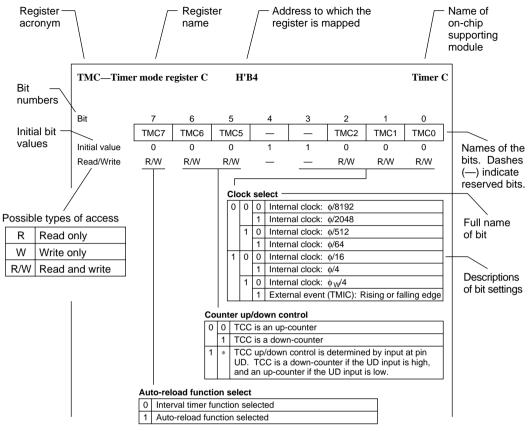

#### 2. Block Diagram

Figure 9.2 shows a block diagram of timer C.

### 3. Pin Configuration

Table 9.5 shows the timer C pin configuration.

### Table 9.5Pin Configuration

| Name                            | Abbr. | I/O   | Function                         |

|---------------------------------|-------|-------|----------------------------------|

| Timer C event input             | TMIC  | Input | Input pin for event input to TCC |

| Timer C up/down-count selection | UD    | Input | Timer C up/down select           |

### 4. Register Configuration

Table 9.6 shows the register configuration of timer C.

#### Table 9.6Timer C Registers

| Name                  | Abbr.   | R/W | Initial Value | Address |

|-----------------------|---------|-----|---------------|---------|

| Timer mode register C | TMC     | R/W | H'18          | H'FFB4  |

| Timer counter C       | TCC     | R   | H'00          | H'FFB5  |

| Timer load register C | TLC     | W   | H'00          | H'FFB5  |

| Clock stop register 1 | CKSTPR1 | R/W | H'FF          | H'FFFA  |

### 9.3.2 Register Descriptions

### 1. Timer Mode Register C (TMC)

| Bit           | 7    | 6    | 5    | 4 | 3 | 2    | 1    | 0    |

|---------------|------|------|------|---|---|------|------|------|

|               | TMC7 | TMC6 | TMC5 | — | — | TMC2 | TMC1 | TMC0 |

| Initial value | 0    | 0    | 0    | 1 | 1 | 0    | 0    | 0    |

| Read/Write    | R/W  | R/W  | R/W  | _ | _ | R/W  | R/W  | R/W  |

TMC is an 8-bit read/write register for selecting the auto-reload function and input clock, and performing up/down-counter control.

Upon reset, TMC is initialized to H'18.

Bit 7: Auto-reload function select (TMC7)

Bit 7 selects whether timer C is used as an interval timer or auto-reload timer.

| Bit 7<br>TMC7 | Description                      |                 |

|---------------|----------------------------------|-----------------|

| 0             | Interval timer function selected | (initial value) |

| 1             | Auto-reload function selected    |                 |

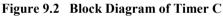

#### 2. Read Access

In access to TCF, when the upper byte is read the upper-byte data is transferred directly to the CPU and the lower-byte data is transferred to TEMP. Next, when the lower byte is read, the lower-byte data in TEMP is transferred to the CPU.

In access to OCRF, when the upper byte is read the upper-byte data is transferred directly to the CPU. When the lower byte is read, the lower-byte data is transferred directly to the CPU.

Figure 9.5 shows an example in which TCF is read when it contains H'AAFF.

Figure 9.5 Read Access to TCF (TCF  $\rightarrow$  CPU)

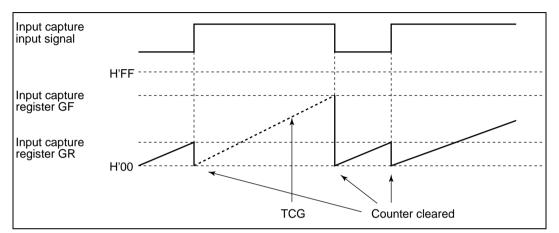

## 9.5.6 Timer G Application Example

Using timer G, it is possible to measure the high and low widths of the input capture input signal as absolute values. For this purpose, CCLR1 and CCLR0 should both be set to 1 in TMG.

Figure 9.16 shows an example of the operation in this case.

Figure 9.16 Timer G Application Example

#### 9.7.4 Asynchronous Event Counter Operation Modes

Asynchronous event counter operation modes are shown in table 9.21.

#### Table 9.21 Asynchronous Event Counter Operation Modes

| Reset | Active         | Sleep                        | Watch                                          | Subactive                                                     | Subsleep                                                                        | Standby                                                                                           | Module<br>Standby                                                                                                 |

|-------|----------------|------------------------------|------------------------------------------------|---------------------------------------------------------------|---------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|

| Reset | Functions      | Functions                    | Held*                                          | Functions                                                     | Functions                                                                       | Held*                                                                                             | Held                                                                                                              |

| Reset | Functions      | Functions                    | Functions*                                     | Functions                                                     | Functions                                                                       | Functions*                                                                                        | Halted                                                                                                            |

| Reset | Functions      | Functions                    | Functions*                                     | Functions                                                     | Functions                                                                       | Functions*                                                                                        | Halted                                                                                                            |

|       | Reset<br>Reset | ResetFunctionsResetFunctions | ResetFunctionsFunctionsResetFunctionsFunctions | ResetFunctionsFunctionsHeld*ResetFunctionsFunctionsFunctions* | ResetFunctionsFunctionsHeld*FunctionsResetFunctionsFunctionsFunctions*Functions | ResetFunctionsFunctionsHeld*FunctionsFunctionsResetFunctionsFunctionsFunctions*FunctionsFunctions | ResetFunctionsFunctionsHeld*FunctionsFunctionsHeld*ResetFunctionsFunctionsFunctions*FunctionsFunctions*Functions* |

Note: \* When an asynchronous external event is input, the counter increments but the counter overflow H/L flags are not affected.

#### 9.7.5 Application Notes

- 1. When reading the values in ECH and ECL, the correct value will not be returned if the event counter increments during the read operation. Therefore, if the counter is being used in the 8-bit mode, clear bits CUEH and CUEL in ECCSR to 0 before reading ECH or ECL. If the counter is being used in the 16-bit mode, clear CUEL only to 0 before reading ECH or ECL.

- 2. In the H8/3847R Group, if the internal power supply step-down circuit is not used, the maximum clock frequency to be input to the AEVH and AEVL pins is 16 MHz when Vcc = 4.5 to 5.5 V, 10 MHz when Vcc = 2.7 to 5.5 V, and 4 MHz when Vcc = 1.8 to 5.5 V. If the internal power step-down circuit is used, the maximum clock frequency to be input is 10 MHz when Vcc = 2.7 to 5.5 V, and 4 MHz when Vcc = 1.8 to 5.5 V. In the H8/3847S Group, the maximum clock frequency to be input is 10 MHz when Vcc = 1.8 to 3.6 V. In the H8/38347 Group and H8/38447 Group, the maximum clock frequency to be input is 16 MHz when Vcc = 2.7 to 5.5 V. In addition, ensure that the high and low widths of the clock are at least 32 ns. The duty cycle is immaterial.

**Bit 3:** Parity error (PER)

Bit 3 indicates that a parity error has occurred during reception with parity added in asynchronous mode.

| Bit 3<br>PER |    | Description                                                                                                                                                                                                                              |                 |

|--------------|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

| 0            |    | Reception in progress or completed <sup>*1</sup><br>Clearing condition:<br>After reading PER = 1, cleared by writing 0 to PER                                                                                                            | (initial value) |

| 1            |    | A parity error has occurred during reception <sup>*2</sup><br>Setting condition:<br>When the number of 1 bits in the receive data plus parity bit does not<br>match the parity designated by bit PM in the serial mode register<br>(SMR) |                 |

| Notes:       | 1. | When bit RE in SCR3 is cleared to 0, bit PER is not affected and retains i state.                                                                                                                                                        | ts previous     |

|              | 2. | Receive data in which it a parity error has occurred is still transferred to R                                                                                                                                                           | RDR. but bit    |

Receive data in which it a parity error has occurred is still transferred to RDR, but bit RDRF is not set. Reception cannot be continued with bit PER set to 1. In synchronous mode, neither transmission nor reception is possible when bit FER is set to 1.

Bit 2: Transmit end (TEND)

Bit 2 indicates that bit TDRE is set to 1 when the last bit of a transmit character is sent.

Bit 2 is a read-only bit and cannot be modified.

| Bit 2<br>TEND | Description                                                                                                                                                        |                 |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

| 0             | Transmission in progress<br>Clearing conditions:<br>After reading TDRE = 1, cleared by writing 0 to TDRE<br>When data is written to TDR by an instruction          |                 |

| 1             | Transmission ended<br>Setting conditions:<br>When bit TE in SCR3 is cleared to 0<br>When bit TDRE is set to 1 when the last bit of a transmit character is<br>sent | (initial value) |

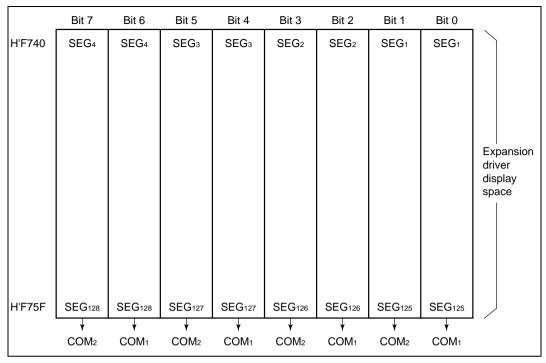

Figure 13.11 LCD RAM Map with Segment Externally Expanded (SGX = "1", SGS3 to SGS0 = "0000" 1/2 duty)

| Instruc-<br>tion | Mnemonic         | Instruction<br>Fetch<br>I | Branch<br>Addr. Read<br>J | Stack<br>Operation<br>K | Word Data<br>Access<br>M | Internal<br>Operation<br>N |

|------------------|------------------|---------------------------|---------------------------|-------------------------|--------------------------|----------------------------|

| SUB              | SUB.B Rs, Rd     | 1                         |                           |                         |                          |                            |

|                  | SUB.W Rs, Rd     | 1                         |                           |                         |                          |                            |

| SUBS             | SUBS.W #1, Rd    | 1                         |                           |                         |                          |                            |

|                  | SUBS.W #2, Rd    | 1                         |                           |                         |                          |                            |

| POP              | POP Rd           | 1                         |                           | 1                       |                          | 2                          |

| PUSH             | PUSH Rs          | 1                         |                           | 1                       |                          | 2                          |

| SUBX             | SUBX.B #xx:8, Rd | 1                         |                           |                         |                          |                            |

|                  | SUBX.B Rs, Rd    | 1                         |                           |                         |                          |                            |

| XOR              | XOR.B #xx:8, Rd  | 1                         |                           |                         |                          |                            |

|                  | XOR.B Rs, Rd     | 1                         |                           |                         |                          |                            |

| XORC             | XORC #xx:8, CCR  | 1                         |                           |                         |                          |                            |

Notes: 1. n: Initial value in R4L. The source and destination operands are accessed n + 1 times each.

2. 1 in the H8/3847R Group and 0 in the H8/3847S Group, H8/38347 Group, and H8/38447 Group.

## **B.2** Functions

\*: Don't care

#### EBR-Erase Block Register

#### H'F023 Flash Memory

| Bit           | 7                                                            | 6                                        | 5         | 4    | 3   | 2   | 1   | 0   |  |

|---------------|--------------------------------------------------------------|------------------------------------------|-----------|------|-----|-----|-----|-----|--|

|               | EB7                                                          | EB6                                      | EB5       | EB4  | EB3 | EB2 | EB1 | EB0 |  |

| Initial value | 0                                                            | 0                                        | 0         | 0    | 0   | 0   | 0   | 0   |  |

| Read/Write    | R/W                                                          | R/W                                      | R/W       | R/W  | R/W | R/W | R/W | R/W |  |

|               |                                                              |                                          |           |      |     |     |     |     |  |

|               |                                                              |                                          | Blocks 71 | to 0 |     |     |     |     |  |

|               | 0 When a block of EB7 to EB0 is not selected (initial value) |                                          |           |      |     |     |     |     |  |

|               |                                                              | 1 When a block of EB7 to EB0 is selected |           |      |     |     |     |     |  |

Note: Set the bit of EBR to H'00 when erasing.

| FENR—Flash N  | FENR—Flash Memory Enable Register H'F02B |            |            |              |           |            |   |   |  |  |

|---------------|------------------------------------------|------------|------------|--------------|-----------|------------|---|---|--|--|

| Bit           | 7                                        | 6          | 5          | 4            | 3         | 2          | 1 | 0 |  |  |

|               | FLSHE                                    |            |            |              |           | _          |   | _ |  |  |

| Initial value | 0                                        | 0          | 0          | 0            | 0         | 0          | 0 | 0 |  |  |

| Read/Write    | R/W                                      | _          | _          | _            | _         |            |   | _ |  |  |

|               | Flash I                                  | Memory C   | Control Re | egister En   | able      |            |   |   |  |  |

|               | 0 Th                                     | e flash me | emory con  | trol registe | er cannot | be accesse | d |   |  |  |

|               | 1 Th                                     | e flash me | emory con  | trol registe | er can be | accessed   |   |   |  |  |

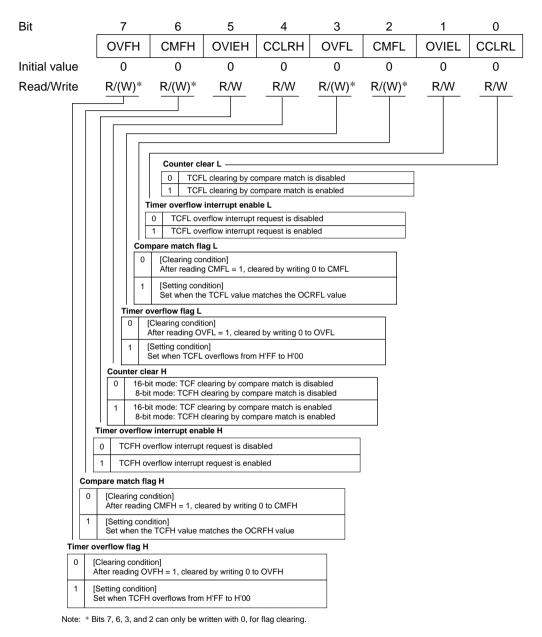

#### TCSRF—Timer Control/Status Register F

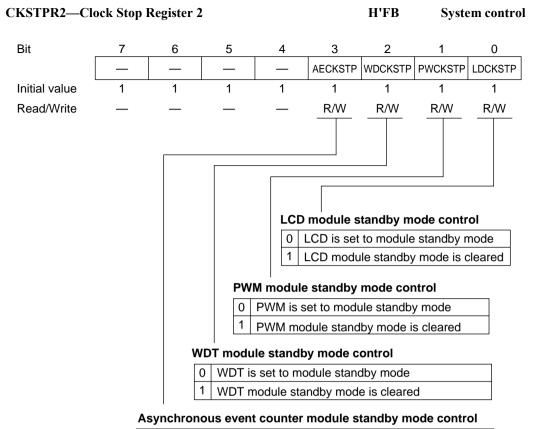

| 0 | Asynchronous event counter is set to module standby mode |

|---|----------------------------------------------------------|

|---|----------------------------------------------------------|

1 Asynchronous event counter module standby mode is cleared

| Product T | уре      |                 |                             | Product Code     | Mark Code | Package (Package Code)      |  |  |

|-----------|----------|-----------------|-----------------------------|------------------|-----------|-----------------------------|--|--|

| H8/38447  | H8/38442 | Mask            | Regular                     | HD64338442H      | 38442H    | 100-pin QFP (FP-100B)       |  |  |

| Group     |          | ROM<br>versions | products                    | HD64338442W      | 38442W    | 100-pin TQFP (TFP-<br>100G) |  |  |

|           |          |                 |                             | HD64338442X      | 38442X    | 100-pin TQFP (TFP-100B)     |  |  |

|           |          |                 |                             | HCD64338442      | —         | Die                         |  |  |

|           |          |                 | Wide-                       | HD64338442HW     | 38442H    | 100-pin QFP (FP-100B)       |  |  |

|           |          |                 | range<br>specifi-<br>cation | HD64338442WW     | 38442W    | 100-pin TQFP (TFP-<br>100G) |  |  |

|           |          |                 | products                    | HD64338442XW     | 38442X    | 100-pin TQFP (TFP-100B)     |  |  |

|           | H8/38443 | Mask            | Regular                     | HD64338443H      | 38443H    | 100-pin QFP (FP-100B)       |  |  |

|           |          | ROM<br>versions | products                    | HD64338443W      | 38443W    | 100-pin TQFP (TFP-<br>100G) |  |  |

|           |          |                 |                             | HD64338443X      | 38443X    | 100-pin TQFP (TFP-100B)     |  |  |

|           |          |                 |                             | HCD64338443      | _         | Die                         |  |  |

|           |          |                 | Wide-                       | HD64338443HW     | 38443H    | 100-pin QFP (FP-100B)       |  |  |

|           |          |                 | range<br>specifi-<br>cation | HD64338443WW     | 38443W    | 100-pin TQFP (TFP-<br>100G) |  |  |

|           |          |                 | products                    | HD64338443XW     | 38443X    | 100-pin TQFP (TFP-100B)     |  |  |

|           | H8/38444 |                 | Regular                     | HD64338444H      | 38444H    | 100-pin QFP (FP-100B)       |  |  |

|           |          | ROM<br>versions | products                    | HD64338444W      | 38444W    | 100-pin TQFP (TFP-<br>100G) |  |  |

|           |          |                 |                             | HD64338444X      | 38444X    | 100-pin TQFP (TFP-100B      |  |  |

|           |          |                 |                             | HCD64338444      |           | Die                         |  |  |

|           |          |                 | Wide-                       | HD64338444HW     | 38444H    | 100-pin QFP (FP-100B)       |  |  |

|           |          |                 | range<br>specifi-<br>cation | HD64338444WW     | 38444W    | 100-pin TQFP (TFP-<br>100G) |  |  |

|           |          |                 | products                    | HD64338444XW     | 38444X    | 100-pin TQFP (TFP-100B)     |  |  |

|           |          | F-ZTAT          | Regular                     | HD64F38444H      | F38444H   | 100-pin QFP (FP-100B)       |  |  |

|           |          | versions        | products                    | HD64F38444W      | F38444W   | 100-pin TQFP (TFP-<br>100G) |  |  |

|           |          |                 |                             | HD64F38444X      | F38444X   | 100-pin TQFP (TFP-100B)     |  |  |

|           |          |                 | Wide-                       | HD64F38444HW     | F38444H   | 100-pin QFP (FP-100B)       |  |  |

|           |          |                 | range<br>specifi-<br>cation | HD64F38444W<br>W | F38444W   | 100-pin TQFP (TFP-<br>100G) |  |  |

|           |          |                 | products                    | HD64F38444XW     | F38444X   | 100-pin TQFP (TFP-100B)     |  |  |

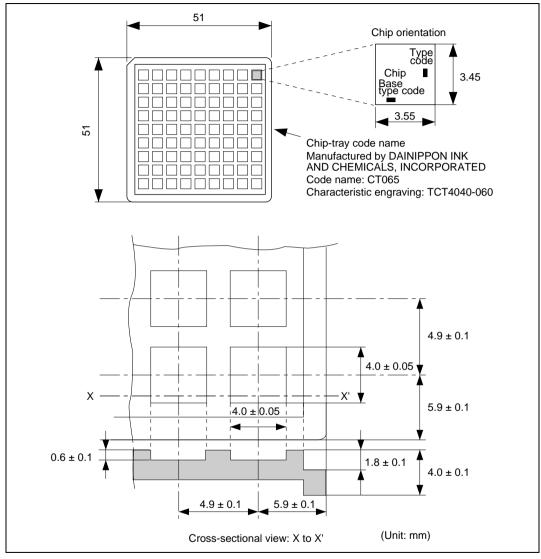

The specifications of the chip tray for the HCD6433847S, HCD6433846S, HCD6433845S, and HCD6433844S are shown in figure I.2.

Figure I.2 Specifications of Chip Tray