Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                    |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | H8/300L                                                                     |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 8MHz                                                                        |

| Connectivity               | SCI                                                                         |

| Peripherals                | LCD, PWM, WDT                                                               |

| Number of I/O              | 71                                                                          |

| Program Memory Size        | 32KB (32K x 8)                                                              |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 2K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                                 |

| Data Converters            | A/D 12x10b                                                                  |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 100-TQFP                                                                    |

| Supplier Device Package    | 100-TQFP (14x14)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/df38344xwv |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 2.5.7 System Control Instructions

Table 2.10 describes the system control instructions. Figure 2.9 shows their object code formats.

| Instruction | n Size <sup>*</sup>          | Function                                                                                                 |

|-------------|------------------------------|----------------------------------------------------------------------------------------------------------|

| RTE         | _                            | Returns from an exception-handling routine                                                               |

| SLEEP       | _                            | Causes a transition from active mode to a power-down mode. See section 5, Power-Down Modes, for details. |

| LDC         | В                            | $Rs \to CCR, \ \ \text{\#IMM} \to CCR$                                                                   |

|             |                              | Moves immediate data or general register contents to the condition code register                         |

| STC         | В                            | $CCR \rightarrow Rd$                                                                                     |

|             |                              | Copies the condition code register to a specified general register                                       |

| ANDC        | В                            | $CCR \land \#IMM \rightarrow CCR$                                                                        |

|             |                              | Logically ANDs the condition code register with immediate data                                           |

| ORC         | В                            | $CCR \lor \#IMM \rightarrow CCR$                                                                         |

|             |                              | Logically ORs the condition code register with immediate data                                            |

| XORC        | В                            | $CCR \oplus \#IMM \to CCR$                                                                               |

|             |                              | Logically exclusive-ORs the condition code register with immediate data                                  |

| NOP         |                              | $PC + 2 \rightarrow PC$                                                                                  |

|             |                              | Only increments the program counter                                                                      |

| Note: *     | Size: Operand siz<br>B: Byte | ze                                                                                                       |

## Table 2.10 System Control Instructions

Rev. 6.00 Aug 04, 2006 page 67 of 680 REJ09B0145-0600

# Section 3 Exception Handling

## 3.1 Overview

Exception handling is performed in the H8/3847R Group when a reset or interrupt occurs. Table 3.1 shows the priorities of these two types of exception handling.

#### Table 3.1 Exception Handling Types and Priorities

| Priority | Exception Source | Time of Start of Exception Handling                                                                                                                     |

|----------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| High     | Reset            | Exception handling starts as soon as the reset state is cleared                                                                                         |

| Low      | Interrupt        | When an interrupt is requested, exception handling starts after execution of the present instruction or the exception handling in progress is completed |

| LOW      |                  | progress is completed                                                                                                                                   |

## 3.2 Reset

#### 3.2.1 Overview

A reset is the highest-priority exception. The internal state of the CPU and the registers of the onchip peripheral modules are initialized.

### 3.2.2 Reset Sequence

As soon as the  $\overline{\text{RES}}$  pin goes low, all processing is stopped and the chip enters the reset state.

To make sure the chip is reset properly, observe the following precautions.

- At power on: Hold the RES pin low until the clock pulse generator output stabilizes.

- Resetting during operation: Hold the  $\overline{\text{RES}}$  pin low for at least 10 system clock cycles.

Reset exception handling takes place as follows.

- The CPU internal state and the registers of on-chip peripheral modules are initialized, with the I bit of the condition code register (CCR) set to 1.

- The PC is loaded from the reset exception handling vector address (H'0000 to H'0001), after which the program starts executing from the address indicated in PC.

## Renesas

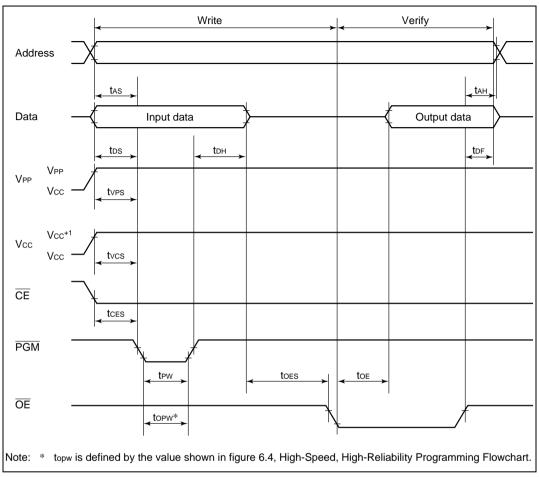

Figure 6.5 shows a PROM write/verify timing diagram.

Figure 6.5 PROM Write/Verify Timing

8. Do not change the TEST pin and P24 pin input levels in boot mode.

|                                                                         | Host Operation                                                                                                | LSI Operation                                                                                                                                                                                                        |  |  |  |

|-------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Item                                                                    | Processing Contents                                                                                           | Processing Contents                                                                                                                                                                                                  |  |  |  |

|                                                                         |                                                                                                               | Branches to boot program at reset-start.                                                                                                                                                                             |  |  |  |

| Bit rate<br>adjustment                                                  | Continuously transmits data H'00 at specified bit rate.                                                       | <ul> <li>Measures low-level period of receive data H'00.</li> <li>Calculates bit rate and sets it in BRR of SCI3.</li> <li>Transmits data H'00 to the host to indicate that the adjustment has ended.</li> </ul>     |  |  |  |

| Flash memory erase                                                      | Transmits data H'55 when data H'00 is received and no error occurs.                                           | ,                                                                                                                                                                                                                    |  |  |  |

|                                                                         |                                                                                                               | Checks flash memory data, erases all flash memory<br>blocks in case of written data existing, and transmits<br>data H'AA to host. (If erase could not be done,<br>transmits data H'FF to host and aborts operation.) |  |  |  |

| ▼<br>Transfer of                                                        | Transmits number of bytes (N) of                                                                              |                                                                                                                                                                                                                      |  |  |  |

| programming control<br>program                                          | programming control program to be<br>transferred as 2-byte data (low-order<br>byte following high-order byte) | Echobacks the 2-byte received data to host.                                                                                                                                                                          |  |  |  |

| +                                                                       | <b>↓</b>                                                                                                      |                                                                                                                                                                                                                      |  |  |  |

| Transfer of<br>programming control<br>program (repeated for<br>N times) | Transmits 1-byte of programming<br>control program                                                            | Echobacks received data to host and also transfers it to RAM.                                                                                                                                                        |  |  |  |

| ▼<br>Execution of                                                       |                                                                                                               | Transmits 1-byte data H'AA to host.                                                                                                                                                                                  |  |  |  |

| Programming<br>control program                                          |                                                                                                               | Branches to programming control program<br>transferred to on-chip RAM and starts execution.                                                                                                                          |  |  |  |

## Table 6.9Boot Mode Operation

#### Table 6.10 Oscillating Frequencies (f<sub>OSC</sub>) for which Automatic Adjustment of LSI Bit Rate Is Possible

| Product Group  | Host Bit Rate | Oscillating Frequencies (f <sub>osc</sub> ) Range of LSI |

|----------------|---------------|----------------------------------------------------------|

| H8/38347F-ZTAT | 19,200 bps    | 16 MHz                                                   |

| H8/38344F-ZTAT | 9,600 bps     | 8 to 16 MHz                                              |

| H8/38447F-ZTAT | 4,800 bps     | 6 to 16 MHz                                              |

| H8/38444F-ZTAT | 2,400 bps     | 2 to 16 MHz                                              |

|                | 1,200 bps     | 2 to 16 MHz                                              |

| Port   | Description                                                                                                       | Pins                                                                                                                                                             | Other Functions                                                                                                                                                                                                                                                                                                                                  | Function<br>Switching<br>Registers |

|--------|-------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|

| Port 3 | <ul> <li>8-bit I/O port</li> <li>MOS input pull-up option</li> <li>Large-current port (H8/3847R Group,</li> </ul> | P3 <sub>7</sub> /AEVL<br>P3 <sub>6</sub> /AEVH<br>P3 <sub>5</sub> /TXD <sub>31</sub><br>P3 <sub>4</sub> /RXD <sub>31</sub><br>P3 <sub>3</sub> /SCK <sub>31</sub> | SCI3-1 data output (TXD <sub>31</sub> ), data<br>input (RXD <sub>31</sub> ), clock input/output<br>(SCK <sub>31</sub> ), and asynchronous counter<br>event inputs AEVL, AEVH                                                                                                                                                                     | PMR3<br>SCR31<br>SMR31             |

|        | (18/38347 Group<br>and H8/38447<br>Group)                                                                         | P3 <sub>2</sub> /RESO <sup>*1</sup><br>P3 <sub>1</sub> /UD/EXCL <sup>*2</sup><br>P3 <sub>0</sub> /PWM                                                            | Reset output <sup>*1</sup> , timer C count-up/<br>down select input, and 14-bit PWM<br>output, external subclock input <sup>*2</sup>                                                                                                                                                                                                             | PMR2<br>PMR3                       |

| Port 4 | 1-bit input port                                                                                                  | P4 <sub>3</sub> /IRQ <sub>0</sub>                                                                                                                                | External interrupt 0                                                                                                                                                                                                                                                                                                                             | PMR3                               |

|        | • 3-bit I/O port                                                                                                  | P4 <sub>2</sub> /TXD <sub>32</sub><br>P4 <sub>1</sub> /RXD <sub>32</sub><br>P4 <sub>0</sub> /SCK <sub>32</sub>                                                   | SCI3-2 data output (TXD <sub>32</sub> ), data<br>input (RXD <sub>32</sub> ), clock input/output<br>(SCK <sub>32</sub> )                                                                                                                                                                                                                          | SCR32<br>SMR32                     |

| Port 5 | <ul><li> 8-bit I/O port</li><li> MOS input pull-up option</li></ul>                                               | $\frac{P5_7 \text{ to } P5_0}{WKP_7 \text{ to } WKP_0}$<br>SEG <sub>8</sub> to SEG <sub>1</sub>                                                                  | Wakeup input ( $\overline{WKP}_7$ to $\overline{WKP}_0$ ),<br>segment output (SEG <sub>8</sub> to SEG <sub>1</sub> )                                                                                                                                                                                                                             | PMR5<br>LPCR                       |

| Port 6 | <ul><li> 8-bit I/O port</li><li> MOS input pull-up option</li></ul>                                               | $P6_7$ to $P6_0/$<br>SEG <sub>16</sub> to SEG <sub>9</sub>                                                                                                       | Segment output (SEG <sub>16</sub> to SEG <sub>9</sub> )                                                                                                                                                                                                                                                                                          | LPCR                               |

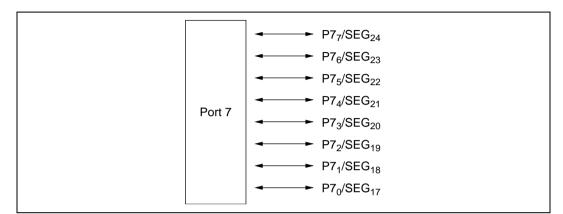

| Port 7 | • 8-bit I/O port                                                                                                  | P7 <sub>7</sub> to P7 <sub>0</sub> /<br>SEG <sub>24</sub> to SEG <sub>17</sub>                                                                                   | Segment output (SEG <sub>24</sub> to SEG <sub>17</sub> )                                                                                                                                                                                                                                                                                         | LPCR                               |

| Port 8 | • 8-bit I/O port                                                                                                  | P87 to P80/<br>SEG32 to SEG25                                                                                                                                    | Segment output (SEG <sub>32</sub> to SEG <sub>25</sub> )                                                                                                                                                                                                                                                                                         | LPCR                               |

| Port 9 | • 8-bit I/O port                                                                                                  | P97/SEG40/CL1 <sup>*3</sup><br>P96/SEG39/CL2 <sup>*3</sup><br>P95/SEG38/DO <sup>*3</sup><br>P94/SEG37/M <sup>*3</sup><br>P93 to P90/<br>SEG36 to SEG33           | <ul> <li>Segment output (SEG<sub>40</sub> to SEG<sub>37</sub>)</li> <li>Latch clock (CL<sub>1</sub>)<sup>*3</sup>, shift clock (CL<sub>2</sub>)<sup>*3</sup>, display data (DO)<sup>*3</sup> and alternating signal (M)<sup>*3</sup> for external expansion of segment</li> <li>Segment output (SEG<sub>36</sub> to SEG<sub>33</sub>)</li> </ul> | LPCR                               |

| Port A | • 4-bit I/O port                                                                                                  | PA <sub>3</sub> to PA <sub>0</sub> /<br>COM <sub>4</sub> to COM <sub>1</sub>                                                                                     | Common output (COM <sub>4</sub> to COM <sub>1</sub> )                                                                                                                                                                                                                                                                                            | LPCR                               |

| Port B | 8-bit input port                                                                                                  | PB <sub>7</sub> to PB <sub>0</sub> /<br>AN <sub>7</sub> to AN <sub>0</sub>                                                                                       | A/D converter analog input                                                                                                                                                                                                                                                                                                                       | AMR                                |

| Port C | • 4-bit input port                                                                                                | PC <sub>3</sub> to PC <sub>0</sub> /<br>AN <sub>11</sub> to AN <sub>8</sub>                                                                                      | A/D converter analog input                                                                                                                                                                                                                                                                                                                       | AMR                                |

Notes: 1. The RESO function is not implemented in the H8/38347 Group and H8/38447 Group.

2. The EXCL function is only implemented in the H8/38347 Group and H8/38447 Group.

3. The external expansion function for LCD segments is not implemented in the H8/38347 Group and H8/38447 Group.

Rev. 6.00 Aug 04, 2006 page 204 of 680 REJ09B0145-0600

## 8.8 Port 7

#### 8.8.1 Overview

Port 7 is an 8-bit I/O port, configured as shown in figure 8.7.

## 8.8.2 Register Configuration and Description

Table 8.20 shows the port 7 register configuration.

## Table 8.20Port 7 Registers

| Name                    | Abbr. | R/W | Initial Value | Address |

|-------------------------|-------|-----|---------------|---------|

| Port data register 7    | PDR7  | R/W | H'00          | H'FFDA  |

| Port control register 7 | PCR7  | W   | H'00          | H'FFEA  |

#### 4. Register Configuration

Table 9.6 shows the register configuration of timer C.

#### Table 9.6Timer C Registers

| Name                  | Abbr.   | R/W | Initial Value | Address |

|-----------------------|---------|-----|---------------|---------|

| Timer mode register C | TMC     | R/W | H'18          | H'FFB4  |

| Timer counter C       | TCC     | R   | H'00          | H'FFB5  |

| Timer load register C | TLC     | W   | H'00          | H'FFB5  |

| Clock stop register 1 | CKSTPR1 | R/W | H'FF          | H'FFFA  |

#### 9.3.2 Register Descriptions

#### 1. Timer Mode Register C (TMC)

| Bit           | 7    | 6    | 5    | 4 | 3 | 2    | 1    | 0    |

|---------------|------|------|------|---|---|------|------|------|

|               | TMC7 | TMC6 | TMC5 | — | — | TMC2 | TMC1 | TMC0 |

| Initial value | 0    | 0    | 0    | 1 | 1 | 0    | 0    | 0    |

| Read/Write    | R/W  | R/W  | R/W  | _ | _ | R/W  | R/W  | R/W  |

TMC is an 8-bit read/write register for selecting the auto-reload function and input clock, and performing up/down-counter control.

Upon reset, TMC is initialized to H'18.

Bit 7: Auto-reload function select (TMC7)

Bit 7 selects whether timer C is used as an interval timer or auto-reload timer.

| Bit 7<br>TMC7 | Description                      |                 |

|---------------|----------------------------------|-----------------|

| 0             | Interval timer function selected | (initial value) |

| 1             | Auto-reload function selected    |                 |

### 2. Timer Counter C (TCC)

| Bit           | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|---------------|------|------|------|------|------|------|------|------|

|               | TCC7 | TCC6 | TCC5 | TCC4 | тсс3 | TCC2 | TCC1 | тссо |

| Initial value | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |

| Read/Write    | R    | R    | R    | R    | R    | R    | R    | R    |

TCC is an 8-bit read-only up-counter, which is incremented by internal clock or external event input. The clock source for input to this counter is selected by bits TMC2 to TMC0 in timer mode register C (TMC). TCC values can be read by the CPU at any time.

When TCC overflows from H'FF to H'00 or to the value set in TLC, or underflows from H'00 to H'FF or to the value set in TLC, the IRRTC bit in IRR2 is set to 1.

TCC is allocated to the same address as TLC.

Upon reset, TCC is initialized to H'00.

### 3. Timer Load Register C (TLC)

| Bit           | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|---------------|------|------|------|------|------|------|------|------|

|               | TLC7 | TLC6 | TLC5 | TLC4 | TLC3 | TLC2 | TLC1 | TLC0 |

| Initial value | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |

| Read/Write    | W    | W    | W    | W    | W    | W    | W    | W    |

TLC is an 8-bit write-only register for setting the reload value of timer counter C (TCC).

When a reload value is set in TLC, the same value is loaded into timer counter C as well, and TCC starts counting up from that value. When TCC overflows or underflows during operation in auto-reload mode, the TLC value is loaded into TCC. Accordingly, overflow/underflow periods can be set within the range of 1 to 256 input clocks.

The same address is allocated to TLC as to TCC.

Upon reset, TLC is initialized to H'00.

Bit 2: Watchdog timer on (WDON)

Bit 2 enables watchdog timer operation.

| Bit 2<br>WDON | Description                                                                                                                        |                 |

|---------------|------------------------------------------------------------------------------------------------------------------------------------|-----------------|

| 0             | Watchdog timer operation is disabled<br>Clearing condition:<br>Reset, or when TCSRWE = 1 and 0 is written in both B2WI and<br>WDON | (initial value) |

| 1             | Watchdog timer operation is enabled<br>Setting condition:<br>When TCSRWE = 1 and 0 is written in B2WI and 1 is written in<br>WDON  |                 |

Counting starts when this bit is set to 1, and stops when this bit is cleared to 0.

Bit 1: Bit 0 write inhibit (B0WI)

Bit 1 controls the writing of data to bit 0 in TCSRW.

| Bit 1 |                          |                 |

|-------|--------------------------|-----------------|

| B0WI  | Description              |                 |

| 0     | Bit 0 is write-enabled   |                 |

| 1     | Bit 0 is write-protected | (initial value) |

This bit is always read as 1. Data written to this bit is not stored.

Bit 0: Watchdog timer reset (WRST)

Bit 0 indicates that TCW has overflowed, generating an internal reset signal. The internal reset signal generated by the overflow resets the entire chip. WRST is cleared to 0 by a reset from the  $\overline{\text{RES}}$  pin, or when software writes 0.

| Bit 0<br>WRST | Description                                                                                        |

|---------------|----------------------------------------------------------------------------------------------------|

| 0             | Clearing condition:<br>Reset by RES pin<br>When TCSRWE = 1, and 0 is written in both B0WI and WRST |

| 1             | Setting condition:<br>When TCW overflows and an internal reset signal is generated                 |

### 10.2.5 Interrupt Source

SCI1 has one interrupt source: transfer completion.

When SCI1 completes transfer, IRRS1 is set to 1 in IRR1. The SCI1 interrupt source can be enabled or disabled by the IENS1 bit in IENR1.

For details, see section 3.3, Interrupts.

## 10.2.6 Application Notes

- (1) When SCK<sub>1</sub> is designated as an input pin and an external clock is selected as the clock source, the external clock must not be input before transfer operation is started by setting STF to 1 in SCSR1.

- (2) In subactive or subsleep mode, SCI1 can be used only when the CPU operation clock is  $\varphi_W/2.$

- (3) Do not read or write to SCSRI during serial transfer. Use one of the following methods to confirm that serial transfer has ended.

- (a) Use SCI1 interrupt exception handling.Set IENSI to 1 in IENR1, and execute interrupt exception handling.

- (b) Perform IRR1 polling.

Confirm that IRRS1 has been set to 1 in IRRI while SCI interrupts are disabled (IENS1 = 0 in IEHR1).

Bit 1: Multiprocessor bit receive (MPBR)

Bit 1 stores the multiprocessor bit in a receive character during multiprocessor format reception in asynchronous mode.

Bit 1 is a read-only bit and cannot be modified.

| Bit 1<br>MPBR | Description                                                                                                                  |

|---------------|------------------------------------------------------------------------------------------------------------------------------|

| 0             | Data in which the multiprocessor bit is 0 has been received* (initial value)                                                 |

| 1             | Data in which the multiprocessor bit is 1 has been received                                                                  |

| Note: *       | When bit RE is cleared to 0 in SCR3 with the multiprocessor format, bit MPBR is not affected and retains its previous state. |

Bit 0: Multiprocessor bit transfer (MPBT)

Bit 0 stores the multiprocessor bit added to transmit data when transmitting in asynchronous mode. The bit MPBT setting is invalid when synchronous mode is selected, when the multiprocessor communication function is disabled, and when not transmitting.

| Bit 0<br>MPBT | Description                           |                 |

|---------------|---------------------------------------|-----------------|

| 0             | A 0 multiprocessor bit is transmitted | (initial value) |

| 1             | A 1 multiprocessor bit is transmitted |                 |

#### 8. Bit Rate Register (BRR)

| Bit           | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|---------------|------|------|------|------|------|------|------|------|

|               | BRR7 | BRR6 | BRR5 | BRR4 | BRR3 | BRR2 | BRR1 | BRR0 |

| Initial value | 1    | 1    | 1    | 1    | 1    | 1    | 1    | 1    |

| Read/Write    | R/W  |

BRR is an 8-bit register that designates the transmit/receive bit rate in accordance with the baud rate generator operating clock selected by bits CKS1 and CKS0 of the serial mode register (SMR).

BRR can be read or written by the CPU at any time.

BRR is initialized to H'FF upon reset, and in standby, module standby, or watch mode.

#### 10.3.3 Operation

### 1. Overview

SCI3 can perform serial communication in two modes: asynchronous mode in which synchronization is provided character by character, and synchronous mode in which synchronization is provided by clock pulses. The serial mode register (SMR) is used to select asynchronous or synchronous mode and the data transfer format, as shown in table 10.11.

The clock source for SCI3 is determined by bit COM in SMR and bits CKE1 and CKE0 in SCR3, as shown in table 10.12.

- a. Asynchronous mode

- Choice of 5-, 7-, or 8-bit data length

- Choice of parity addition, multiprocessor bit addition, and addition of 1 or 2 stop bits. (The combination of these parameters determines the data transfer format and the character length.)

- Framing error (FER), parity error (PER), overrun error (OER), and break detection during reception

- Choice of internal or external clock as the clock source

When internal clock is selected: SCI3 operates on the baud rate generator clock, and a clock with the same frequency as the bit rate can be output.

When external clock is selected: A clock with a frequency 16 times the bit rate must be input. (The on-chip baud rate generator is not used.)

b. Synchronous mode

•

- Data transfer format: Fixed 8-bit data length

- Overrun error (OER) detection during reception

- Choice of internal or external clock as the clock source When internal clock is selected: SCI3 operates on the baud rate generator clock, and a serial clock is output.

When external clock is selected: The on-chip baud rate generator is not used, and SCI3 operates on the input serial clock.

• Transmitting

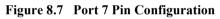

Figure 10.11 shows an example of a flowchart for data transmission. This procedure should be followed for data transmission after initializing SCI3.

#### Figure 10.11 Example of Data Transmission Flowchart (Asynchronous Mode)

SCI3 operates as follows when transmitting data.

SCI3 monitors bit TDRE in SSR, and when it is cleared to 0, recognizes that data has been written to TDR and transfers data from TDR to TSR. It then sets bit TDRE to 1 and starts transmitting. If bit TIE in SCR3 is set to 1 at this time, a TXI request is made.

Serial data is transmitted from the TXD pin using the relevant data transfer format in table 10.14. When the stop bit is sent, SCI3 checks bit TDRE. If bit TDRE is cleared to 0, SCI3 transfers data from TDR to TSR, and when the stop bit has been sent, starts transmission of the next frame. If bit TDRE is set to 1 bit TEND in SSR bit is set to 1, the mark state, in which 1s are transmitted, is established after the stop bit has been sent. If bit TEIE in SCR3 is set to 1 at this time, a TEI request is made.

Start Transmit Stop Start Transmit Stop Mark bit data bit data MPB bit MPB bit state Serial 0 D0 D1 0/1 0 D0 D7 0/1 1 1 D7 1 D1 1 data 1 frame 1 frame TDRE TEND TXI request TDRE **TXI** request LSI TEI request cleared to 0 operation User Data written processing to TDR

Figure 10.23 shows an example of the operation when transmitting using the multiprocessor format.

### Figure 10.23 Example of Operation when Transmitting Using Multiprocessor Format (8-bit data, multiprocessor bit, 1 stop bit)

• Multiprocessor receiving

Figure 10.24 shows an example of a flowchart for multiprocessor data reception. This procedure should be followed for multiprocessor data reception after initializing SCI3.

## Renesas

| PWDRU         |        |        |        |        |        |        |        |        |

|---------------|--------|--------|--------|--------|--------|--------|--------|--------|

| Bit           | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |

|               | —      | —      | PWDRU5 | PWDRU4 | PWDRU3 | PWDRU2 | PWDRU1 | PWDRU0 |

| Initial value | 1      | 1      | 0      | 0      | 0      | 0      | 0      | 0      |

| Read/Write    |        |        | W      | W      | W      | W      | W      | W      |

|               |        |        |        |        |        |        |        |        |

| PWDRL         |        |        |        |        |        |        |        |        |

| Bit           | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |

|               | PWDRL7 | PWDRL6 | PWDRL5 | PWDRL4 | PWDRL3 | PWDRL2 | PWDRL1 | PWDRL0 |

| Initial value | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      |

| Read/Write    | W      | W      | W      | W      | W      | W      | W      | W      |

#### 11.2.2 PWM Data Registers U and L (PWDRU, PWDRL)

PWDRU and PWDRL form a 14-bit write-only register, with the upper 6 bits assigned to PWDRU and the lower 8 bits to PWDRL. The value written to PWDRU and PWDRL gives the total high-level width of one PWM waveform cycle.

When 14-bit data is written to PWDRU and PWDRL, the register contents are latched in the PWM waveform generator, updating the PWM waveform generation data. The 14-bit data should always be written in the following sequence:

- 1. Write the lower 8 bits to PWDRL.

- 2. Write the upper 6 bits to PWDRU.

PWDRU and PWDRL are write-only registers. If they are read, all bits are read as 1.

Upon reset, PWDRU and PWDRL are initialized to H'C000.

#### 15.2.3 AC Characteristics

Table 15.3 lists the control signal timing, and tables 15.4 and 15.5 list the serial interface timing.

#### Table 15.3 Control Signal Timing

$V_{CC} = 1.8$  V to 5.5 V,  $AV_{CC} = 1.8$  V to 5.5 V,  $V_{SS} = AV_{SS} = 0.0$  V,  $Ta = -20^{\circ}C$  to  $+75^{\circ}C^{*4}$  (including subactive mode) unless otherwise indicated.

|                                       |                     | Applicable                          | Values | 6                    |               |                                         |                                                  | Reference                                        |              |

|---------------------------------------|---------------------|-------------------------------------|--------|----------------------|---------------|-----------------------------------------|--------------------------------------------------|--------------------------------------------------|--------------|

| Item                                  | Symbol              | Pins                                | Min    | Тур                  | Max           | Unit                                    | Test Condition                                   | Figure                                           |              |

| System clock                          | f <sub>osc</sub>    | OSC <sub>1</sub> , OSC <sub>2</sub> | 2      | _                    | 16            | MHz                                     | $V_{\rm CC}$ = 4.5 V to 5.5 V                    | *2                                               |              |

| oscillation<br>frequency              |                     |                                     | 2      | _                    | 10            | -                                       | $V_{\rm CC}$ = 2.7 V to 5.5 V                    |                                                  |              |

| nequency                              |                     |                                     | 2      | _                    | 4             | -                                       | $V_{CC}$ = 1.8 V to 5.5 V                        | _                                                |              |

| OSC clock ( $\phi_{OSC}$ ) cycle time | t <sub>osc</sub>    | OSC <sub>1</sub> , OSC <sub>2</sub> | 62.5   | _                    | 500<br>(1000) | ns                                      | $V_{\rm CC}$ = 4.5 V to 5.5 V                    | Figure 15.1                                      |              |

|                                       |                     |                                     | 100    | _                    | 500<br>(1000) | -                                       | $V_{CC}$ = 2.7 V to 5.5 V                        | Figure 15.1                                      |              |

|                                       |                     |                                     | 250    | _                    | 500<br>(1000) | -                                       | $V_{\rm CC}$ = 1.8 V to 5.5 V                    | _                                                |              |

| System clock (                        | t <sub>cyc</sub>    |                                     | 2      | _                    | 128           | tosc                                    |                                                  |                                                  |              |

| cycle time                            |                     |                                     | —      | —                    | 244.1         | μs                                      | _                                                |                                                  |              |

| Subclock oscilla-<br>tion frequency   | f <sub>w</sub>      | X <sub>1</sub> , X <sub>2</sub>     | —      | 32.768<br>or<br>38.4 | _             | kHz                                     |                                                  |                                                  |              |

| Watch clock ( $\phi_W$ ) cycle time   | tw                  | X <sub>1</sub> , X <sub>2</sub>     | _      | 30.5<br>or<br>26.0   | _             | μs                                      |                                                  | Figure 15.1                                      |              |

| Subclock ( $\phi_{SUB}$ ) cycle time  | t <sub>subcyc</sub> |                                     | 2      | _                    | 8             | t <sub>w</sub>                          |                                                  | *1                                               |              |

| Instruction cycle time                |                     |                                     | 2      |                      | _             | t <sub>cyc</sub><br>t <sub>subcyc</sub> |                                                  |                                                  |              |

| Oscillation stabilization time        | t <sub>rc</sub>     | OSC <sub>1</sub> , OSC <sub>2</sub> | —      | 20                   | 45            | μs                                      | Figure 15.10<br>V <sub>CC</sub> = 2.2 V to 5.5 V | Figure 15.10                                     |              |

|                                       |                     |                                     |        | _                    | 0.1           | 8                                       | ms                                               | Figure 15.10<br>V <sub>CC</sub> = 2.2 V to 5.5 V | Figure 15.10 |

|                                       |                     |                                     | _      | _                    | 50            | ms                                      | Except the above                                 |                                                  |              |

|                                       |                     | X <sub>1</sub> , X <sub>2</sub>     | _      | _                    | 2.0           | S                                       |                                                  |                                                  |              |

|                                        |              |                   | Values | 6   |     |                                                |                        | Reference   |

|----------------------------------------|--------------|-------------------|--------|-----|-----|------------------------------------------------|------------------------|-------------|

| ltem                                   |              | Symbol            | Min    | Тур | Мах | Unit                                           | <b>Test Conditions</b> | Figure      |

| Input clock                            | Asynchronous | t <sub>Scyc</sub> | 4      |     |     | $t_{\text{cyc}}$ or                            |                        | Figure 15.6 |

| cycle                                  | Synchronous  | _                 | 6      |     | _   | t <sub>subcyc</sub>                            |                        |             |

| Input clock put                        | se width     | t <sub>scкw</sub> | 0.4    |     | 0.6 | t <sub>Scyc</sub>                              |                        | Figure 15.6 |

| Transmit data delay time (synchronous) |              | $t_{TXD}$         | _      | _   | 1   | $t_{\text{cyc}} \text{ or } t_{\text{subcyc}}$ |                        | Figure 15.7 |

| Receive data setup time (synchronous)  |              | t <sub>RXS</sub>  | 400.0  | —   | -   | ns                                             |                        | Figure 15.7 |

| Receive data hold time (synchronous)   |              | t <sub>RXH</sub>  | 400.0  | —   | _   | ns                                             |                        | Figure 15.7 |

#### Table 15.21 Serial Interface (SCI3-1, SCI3-2) Timing

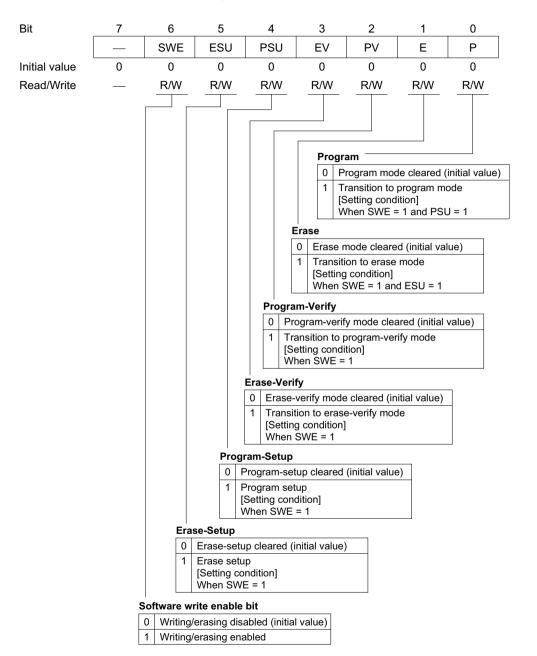

#### FLMCR1—Flash Memory Control Register 1

#### H'F020 Flash Memory

| Product T         | уре      |                         |                                      | Product Code | Mark Code        | Package (Package Code       |

|-------------------|----------|-------------------------|--------------------------------------|--------------|------------------|-----------------------------|

| H8/3847R<br>Group | H8/3845R |                         | Regular<br>products                  | HD6433845RH  | HD6433845R(***)H | 100-pin QFP (FP-100B)       |

|                   |          | ROM versions            |                                      | HD6433845RF  | HD6433845R(***)F | 100-pin QFP (FP-100A)       |

|                   |          | VEISIONS                |                                      | HD6433845RX  | HD6433845R(***)X | 100-pin TQFP (TFP-100B      |

|                   |          |                         |                                      | HD6433845RW  | HD6433845R(***)W | 100-pin TQFP (TFP-<br>100G) |

|                   |          |                         |                                      | HCD6433845R  | —                | Die                         |

|                   |          | Mask                    | Wide-                                | HD6433845RD  | HD6433845R(***)H | 100-pin QFP (FP-100B)       |

|                   |          | ROM versions            | range                                | HD6433845RE  | HD6433845R(***)F | 100-pin QFP (FP-100A)       |

|                   |          | Voroiono                | specifi-<br>cation                   | HD6433845RL  | HD6433845R(***)X | 100-pin TQFP (TFP-100B      |

|                   |          |                         | products                             | HD6433845RWI | HD6433845R(***)W | 100-pin TQFP (TFP-<br>100G) |

|                   | H8/3846R |                         | Regular                              | HD6433846RH  | HD6433846R(***)H | 100-pin QFP (FP-100B)       |

|                   |          | ROM versions            | products                             | HD6433846RF  | HD6433846R(***)F | 100-pin QFP (FP-100A)       |

|                   |          |                         |                                      | HD6433846RX  | HD6433846R(***)X | 100-pin TQFP (TFP-100B      |

|                   |          |                         |                                      | HD6433846RW  | HD6433846R(***)W | 100-pin TQFP (TFP-<br>100G) |

|                   |          |                         |                                      | HCD6433846R  | _                | Die                         |

|                   |          |                         | Wide-<br>range<br>specifi-<br>cation | HD6433846RD  | HD6433846R(***)H | 100-pin QFP (FP-100B)       |

|                   |          |                         |                                      | HD6433846RE  | HD6433846R(***)F | 100-pin QFP (FP-100A)       |

|                   |          |                         |                                      | HD6433846RL  | HD6433846R(***)X | 100-pin TQFP (TFP-100E      |

|                   | _        |                         | products                             | HD6433846RWI | HD6433846R(***)W | 100-pin TQFP (TFP-<br>100G) |

|                   | H8/3847R | Mask<br>ROM<br>versions | Regular<br>products                  | HD6433847RH  | HD6433847R(***)H | 100-pin QFP (FP-100B)       |

|                   |          |                         |                                      | HD6433847RF  | HD6433847R(***)F | 100-pin QFP (FP-100A)       |

|                   |          |                         |                                      | HD6433847RX  | HD6433847R(***)X | 100-pin TQFP (TFP-100E      |

|                   |          |                         |                                      | HD6433847RW  | HD6433847R(***)W | 100-pin TQFP (TFP-<br>100G) |

|                   |          |                         |                                      | HCD6433847R  | _                | Die                         |

|                   |          |                         | Wide-                                | HD6433847RD  | HD6433847R(***)H | 100-pin QFP (FP-100B)       |

|                   |          |                         | range<br>specifi-                    | HD6433847RE  | HD6433847R(***)F | 100-pin QFP (FP-100A)       |

|                   |          |                         | cation                               | HD6433847RL  | HD6433847R(***)X | 100-pin TQFP (TFP-100E      |

|                   |          |                         | products                             | HD6433847RWI | HD6433847R(***)W | 100-pin TQFP(TFP-100G       |

|                   |          | ZTAT                    | Regular                              | HD6473847RH  | HD6473847RH      | 100-pin QFP (FP-100B)       |

|                   |          | versions                | products                             | HD6473847RF  | HD6473847RF      | 100-pin QFP (FP-100A)       |

|                   |          |                         |                                      | HD6473847RX  | HD6473847RX      | 100-pin TQFP (TFP-100E      |

|                   |          |                         |                                      | HD6473847RW  | HD6473847RW      | 100-pin TQFP(TFP-100G       |

|                   |          |                         | Wide-                                | HD6473847RD  | HD6473847RH      | 100-pin QFP (FP-100B)       |

|                   |          |                         | range                                | HD6473847RE  | HD6473847RF      | 100-pin QFP (FP-100A)       |

|                   |          |                         | specifi-<br>cation                   | HD6473847RL  | HD6473847RX      | 100-pin TQFP (TFP-100E      |

|                   |          |                         | products                             | HD6473847RWI | HD6473847RW      | 100-pin TQFP (TFP-<br>100G) |