Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

|                            |                                                                            |

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 18                                                                         |

| Program Memory Size        | 28KB (16K x 14)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 2K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                |

| Data Converters            | A/D 17x12b; D/A 1x5b                                                       |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 20-UFQFN Exposed Pad                                                       |

| Supplier Device Package    | 20-UQFN (4x4)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f18446-e-gz |

### 7.8.12 STKPTR

Name: STKPTR Address: 0xFED

Stack Pointer Register

| Bit    | 7 | 6 | 5 | 4   | 3   | 2           | 1   | 0   |

|--------|---|---|---|-----|-----|-------------|-----|-----|

|        |   |   |   |     |     | STKPTR[4:0] |     |     |

| Access |   |   |   | R/W | R/W | R/W         | R/W | R/W |

| Reset  |   |   |   | 0   | 0   | 0           | 0   | 0   |

Bits 4:0 - STKPTR[4:0] Stack Pointer Location bits

**Important:** An internal Reset event (RESET instruction, BOR, WWDT, POR, STKOVF, STKUNF) does not drive the  $\overline{MCLR}$  pin low.

#### **Related Links**

Master Clear (MCLR) Pin

#### 8.4.2 MCLR Disabled

When MCLR is disabled, the MCLR becomes input-only and pin functions such as internal weak pull-ups are under software control.

#### **Related Links**

I/O Priorities

## 8.5 Windowed Watchdog Timer (WWDT) Reset

The Windowed Watchdog Timer generates a Reset if the firmware does not issue a CLRWDT instruction within the time-out period or window set. The TO and PD bits in the STATUS register and the RWDT bit are changed to indicate a WDT Reset. The WDTWV bit indicates if the WDT Reset has occurred due to a timeout or a window violation.

#### **Related Links**

**STATUS**

(WWDT) Windowed Watchdog Timer

#### 8.6 RESET Instruction

A RESET instruction will cause a device Reset. The RI bit will be set to '0'. See "Reset Condition for Special Registers" table for default conditions after a RESET instruction has occurred.

#### 8.7 Stack Overflow/Underflow Reset

The device can reset when the Stack Overflows or Underflows. The STKOVF or STKUNF bits register indicate the Reset condition. These Resets are enabled by setting the STVREN bit in Configuration Words.

#### **Related Links**

**CONFIG2**

Overflow/Underflow Reset

#### 8.8 Programming Mode Exit

Upon exit of Programming mode, the device will behave as if a POR had just occurred.

#### 8.9 Power-up Timer (PWRT)

The Power-up Timer optionally delays device execution after a BOR or POR event. This timer is typically used to allow  $V_{DD}$  to stabilize before allowing the device to start running.

### 9.6.6 OSCTUNE

Name: OSCTUNE Address: 0x892

### **HFINTOSC Tuning Register**

| Bit    | 7 | 6 | 5   | 4   | 3    | 2      | 1   | 0   |

|--------|---|---|-----|-----|------|--------|-----|-----|

|        |   |   |     |     | HFTU | N[5:0] |     |     |

| Access |   |   | R/W | R/W | R/W  | R/W    | R/W | R/W |

| Reset  |   |   | 0   | 0   | 0    | 0      | 0   | 0   |

Bits 5:0 - HFTUN[5:0] HFINTOSC Frequency Tuning bits

| Value   | Description                                                                                 |

|---------|---------------------------------------------------------------------------------------------|

| 01 1111 | Maximum frequency                                                                           |

| 00 0000 | Center frequency. Oscillator module is running at the calibrated frequency (default value). |

| 10 0000 | Minimum frequency                                                                           |

#### 10.7.1 INTCON

Name: INTCON Address: 0x00B

### Interrupt Control Register

| Bit    | 7   | 6    | 5 | 4 | 3 | 2 | 1 | 0      |

|--------|-----|------|---|---|---|---|---|--------|

|        | GIE | PEIE |   |   |   |   |   | INTEDG |

| Access | R/W | R/W  |   |   |   |   |   | R/W    |

| Reset  | 0   | 0    |   |   |   |   |   | 1      |

#### Bit 7 – GIE Global Interrupt Enable bit

|   | Value | Description                   |

|---|-------|-------------------------------|

|   | 1     | Enables all active interrupts |

| ( | )     | Disables all interrupts       |

#### Bit 6 - PEIE Peripheral Interrupt Enable bit

|   | Value | Description                              |

|---|-------|------------------------------------------|

| ĺ | 1     | Enables all active peripheral interrupts |

|   | 0     | Disables all peripheral interrupts       |

#### Bit 0 - INTEDG External Interrupt Edge Select bit

| Value | Description                          |

|-------|--------------------------------------|

| 1     | Interrupt on rising edge of INT pin  |

| 0     | Interrupt on falling edge of INT pin |

**Important:** Interrupt flag bits are set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the global enable bit. User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt. This feature allows for software polling.

#### 10.7.2 PIE0

Name: PIE0 Address: 0x716

Peripheral Interrupt Enable Register 0

| Bit    | 7 | 6 | 5      | 4     | 3 | 2 | 1 | 0    |

|--------|---|---|--------|-------|---|---|---|------|

|        |   |   | TMR0IE | IOCIE |   |   |   | INTE |

| Access |   |   | R/W    | R/W   |   |   |   | R/W  |

| Reset  |   |   | 0      | 0     |   |   |   | 0    |

#### Bit 5 - TMR0IE Timer0 Interrupt Enable bit

| Value | Description |

|-------|-------------|

| 1     | Enabled     |

| 0     | Disabled    |

#### Bit 4 - IOCIE Interrupt-on-Change Enable bit

| Value | Description |

|-------|-------------|

| 1     | Enabled     |

| 0     | Disabled    |

#### Bit 0 - INTE External Interrupt Enable bit(1)

| Value | Description |

|-------|-------------|

| 1     | Enabled     |

| 0     | Disabled    |

#### Note:

1. The External Interrupt INT pin is selected by INTPPS.

**Note:** Bit PEIE of the INTCON register must be set to enable any peripheral interrupt controlled by PIE1-PIE8. Interrupt sources controlled by the PIE0 register do not require PEIE to be set in order to allow interrupt vectoring (when GIE is set).

#### **Related Links**

**xxxPPS**

# 11.4 Register Summary - Power Savings Control

| Offset | Name     | Bit Pos. |       |       |     |     |  |           |  |

|--------|----------|----------|-------|-------|-----|-----|--|-----------|--|

| 0x0812 | VREGCON  | 7:0      |       |       |     |     |  | VREGPM    |  |

| 0x0813 | Reserved |          |       |       |     |     |  |           |  |

| 0x088B |          |          |       |       |     |     |  |           |  |

| 0x088C | CPUDOZE  | 7:0      | IDLEN | DOZEN | ROI | DOE |  | DOZE[2:0] |  |

## 11.5 Register Definitions: Power Savings Control

### 14. I/O Ports

#### 14.1 PORT Availability

Table 14-1. PORT Availability Per Device

| PORTs | PORT Description                  | PIC16(L)F18426 | PIC16(L)F18446 |

|-------|-----------------------------------|----------------|----------------|

| PORTA | 6-bit wide, bidirectional port.   | •              | •              |

| PORTB | 4-bit wide, bidirectional port.   |                | •              |

| PORTC | 6/8-bit wide, bidirectional port. | •              | •              |

### 14.2 I/O Ports Description

Each port has standard registers for its operation. These registers are:

- PORTx registers (reads the levels on the pins of the device)

- LATx registers (output latch)

- TRISx registers (data direction)

- ANSELx registers (analog select)

- WPUx registers (weak pull-up)

- INLVLx (input level control)

- SLRCONx registers (slew rate control)

- ODCONx registers (open-drain control)

Most port pins share functions with device peripherals, both analog and digital. In general, when a peripheral is enabled on a port pin, that pin cannot be used as a general purpose output; however, the pin can still be read.

The Data Latch (LATx registers) is useful for read-modify-write operations on the value that the I/O pins are driving.

A write operation to the LATx register has the same effect as a write to the corresponding PORTx register. A read of the LATx register reads of the values held in the I/O PORT latches, while a read of the PORTx register reads the actual I/O pin value.

Ports that support analog inputs have an associated ANSELx register. When an ANSELx bit is set, the digital input buffer associated with that bit is disabled.

Disabling the input buffer prevents analog signal levels on the pin between a logic high and low from causing excessive current in the logic input circuitry. A simplified model of a generic I/O port, without the interfaces to other peripherals, is shown in the following figure:

#### 20.8.14 ADFLTR

Name: ADFLTR Address: 0x094

### ADC Filter Register

| Bit    | 15         | 14 | 13 | 12 | 11 | 10 | 9  | 8  |

|--------|------------|----|----|----|----|----|----|----|

|        | FLTRH[7:0] |    |    |    |    |    |    |    |

| Access | RO         | RO | RO | RO | RO | RO | RO | RO |

| Reset  | x          | x  | x  | x  | x  | x  | x  | x  |

|        |            |    |    |    |    |    |    |    |

| Bit    | 7          | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

|        | FLTRL[7:0] |    |    |    |    |    |    |    |

| Access | RO         | RO | RO | RO | RO | RO | RO | RO |

| Reset  | x          | x  | x  | x  | x  | x  | x  | x  |

#### Bits 15:8 - FLTRH[7:0] ADC Filter Output Most Significant bits

In Accumulate, Average, and Burst Average mode, this is equal to ADACC right shifted by the CRS bits. In LPF mode, this is the output of the low-pass filter.

#### Bits 7:0 - FLTRL[7:0] ADC Filter Output Least Significant bits

In Accumulate, Average, and Burst Average mode, this is equal to ADACC right shifted by the CRS bits. In LPF mode, this is the output of the low-pass filter.

## 22.8 Register Summary - NCO

| Offset | Name                | Bit Pos. |               |           |     |     |          |     |        |     |

|--------|---------------------|----------|---------------|-----------|-----|-----|----------|-----|--------|-----|

|        |                     | 7:0      |               | ,         |     | ACC | L[7:0]   |     | ~      |     |

| 0x058C | 0x058C NCO1ACC 15:8 |          |               | ACCH[7:0] |     |     |          |     |        |     |

|        |                     | 23:16    |               |           |     |     |          | ACC | U[3:0] |     |

|        |                     | 7:0      | INCL[7:0]     |           |     |     |          |     |        |     |

| 0x058F | NCO1INC             | 15:8     | 5:8 INCH[7:0] |           |     |     |          |     |        |     |

|        |                     | 23:16    | INCU[3:0]     |           |     |     |          |     |        |     |

| 0x0592 | NCO1CON             | 7:0      | EN            |           | OUT | POL |          |     |        | PFM |

| 0x0593 | NCO1CLK             | 7:0      | PWS[2:0]      |           |     |     | CKS[3:0] |     |        |     |

## 22.9 Register Definitions: NCO

Long bit name prefixes for the NCO peripherals are shown in the table below. Refer to the "Long Bit Names Section" for more information.

Table 22-2. NCO Long Bit Name Prefixes

| Peripheral | Bit Name Prefix |  |

|------------|-----------------|--|

| NCO        | NCO             |  |

#### **Related Links**

Long Bit Names

#### 31.15.1 CWGxCON0

Name: CWGxCON0 Address: 0x610,0x61A

### CWG Control Register 0

| Bit    | 7   | 6      | 5 | 4 | 3 | 2   | 1         | 0   |

|--------|-----|--------|---|---|---|-----|-----------|-----|

|        | EN  | LD     |   |   |   |     | MODE[2:0] |     |

| Access | R/W | R/W/HC |   |   |   | R/W | R/W       | R/W |

| Reset  | 0   | 0      |   |   |   | 0   | 0         | 0   |

#### Bit 7 - EN CWG1 Enable bit

| Value | Description        |

|-------|--------------------|

| 1     | Module is enabled  |

| 0     | Module is disabled |

#### Bit 6 - LD CWG1 Load Buffers bit(1)

| Value | Description                                                                                |

|-------|--------------------------------------------------------------------------------------------|

| 1     | Dead-band count buffers to be loaded on CWG data rising edge, following first falling edge |

|       | after this bit is set                                                                      |

| 0     | Buffers remain unchanged                                                                   |

#### Bits 2:0 - MODE[2:0] CWG1 Mode bits

| Value | Description                                       |

|-------|---------------------------------------------------|

| 111   | Reserved                                          |

| 110   | Reserved                                          |

| 101   | CWG outputs operate in Push-Pull mode             |

| 100   | CWG outputs operate in Half-Bridge mode           |

| 011   | CWG outputs operate in Reverse Full-Bridge mode   |

| 010   | CWG outputs operate in Forward Full-Bridge mode   |

| 001   | CWG outputs operate in Synchronous Steering mode  |

| 000   | CWG outputs operate in Asynchronous Steering mode |

#### Note:

1. This bit can only be set after EN = 1; it cannot be set in the same cycle when EN is set.

**Table 32-1. MDSRC Selection MUX Connections**

| SRCS<4:0>   | Connection                |  |  |

|-------------|---------------------------|--|--|

| 11111-10010 | Reserved                  |  |  |

| 10001       | MSSP2 - SDO               |  |  |

| 10000       | MSSP1 - SDO               |  |  |

| 01111       | EUSART1 TX (TX/CK output) |  |  |

| 01110       | CLC4 OUT                  |  |  |

| 01101       | CLC3 OUT                  |  |  |

| 01100       | CLC2 OUT                  |  |  |

| 01011       | CLC1 OUT                  |  |  |

| 01010       | C2 OUT                    |  |  |

| 01001       | C1 OUT                    |  |  |

| 01000       | NCO1 OUT                  |  |  |

| 00111       | PWM7 OUT                  |  |  |

| 00110       | PWM6 OUT                  |  |  |

| 00101       | CCP4 OUT                  |  |  |

| 00100       | CCP3 OUT                  |  |  |

| 00011       | CCP2 OUT                  |  |  |

| 00010       | CCP1 OUT                  |  |  |

| 00001       | MDBIT                     |  |  |

| 00000       | Pin selected by MDSRCPPS  |  |  |

## 32.3 Carrier Signal Sources

The carrier high signal and carrier low signal can be supplied from the following sources.

The carrier high signal is selected by configuring the CHS bits.

**Table 32-2. MDCARH Source Selections**

| MDCARH   |            |  |  |  |  |

|----------|------------|--|--|--|--|

| CHS<3:0> | Connection |  |  |  |  |

| 1111     | Reserved   |  |  |  |  |

| 1110     | CLC4 OUT   |  |  |  |  |

| 1101     | CLC3 OUT   |  |  |  |  |

| 1100     | CLC2 OUT   |  |  |  |  |

| 1011     | CLC1 OUT   |  |  |  |  |

# PIC16(L)F18426/46

(CLC) Configurable Logic Cell

#### Gate 4: CLCxSEL3

Register number suffixes are different than the gate numbers because other variations of this module have multiple gate selections in the same register.

Data gating is indicated in the right side of Figure 33-2. Only one gate is shown in detail. The remaining three gates are configured identically with the exception that the data enables correspond to the enables for that gate.

#### 33.1.3 Logic Function

There are eight available logic functions including:

- AND-OR

- OR-XOR

- AND

- S-R Latch

- D Flip-Flop with Set and Reset

- D Flip-Flop with Reset

- J-K Flip-Flop with Reset

- Transparent Latch with Set and Reset

Logic functions are shown in the following diagram. Each logic function has four inputs and one output. The four inputs are the four data gate outputs of the previous stage. The output is fed to the inversion stage and from there to other peripherals, an output pin, and back to the CLC itself.

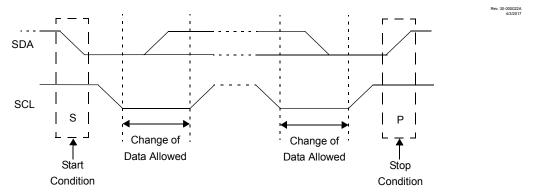

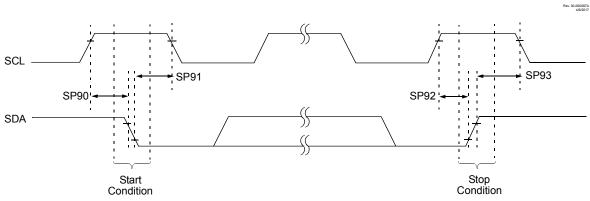

#### 35.4.8 Stop Condition

A Stop condition is a transition of the SDA line from low-to-high state while the SCL line is high.

**Important:** At least one SCL low time must appear before a Stop is valid, therefore, if the SDA line goes low then high again while the SCL line stays high, only the Start condition is detected.

Figure 35-12. I<sup>2</sup>C Start and Stop Conditions

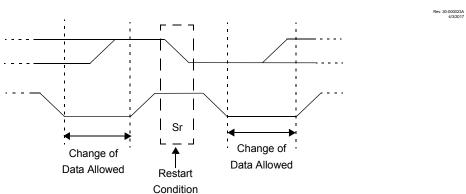

#### 35.4.9 Restart Condition

A Restart is valid any time that a Stop would be valid. A master can issue a Restart if it wishes to hold the bus after terminating the current transfer. A Restart has the same effect on the slave that a Start would, resetting all slave logic and preparing it to clock in an address. The master may want to address the same or another slave. Figure 35-13 shows the wave form for a Restart condition.

In 10-bit Addressing Slave mode a Restart is required for the master to clock data out of the addressed slave. Once a slave has been fully addressed, matching both high and low address bytes, the master can issue a Restart and the high address byte with the R/W bit set. The slave logic will then hold the clock and prepare to clock out data.

After a full match with  $R/\overline{W}$  clear in 10-bit mode, a prior match flag is set and maintained until a Stop condition, a high address with  $R/\overline{W}$  clear, or high address match fails.

Figure 35-13. I<sup>2</sup>C Restart Condition

Table 36-1. Baud Rate Formulas

| Configuration Bits                                                       |       |      | BRG/EUSART Mode     | Baud Rate Formula            |  |  |  |

|--------------------------------------------------------------------------|-------|------|---------------------|------------------------------|--|--|--|

| SYNC                                                                     | BRG16 | BRGH | BRG/EUSART Moue     | Dauu Kale Foiliula           |  |  |  |

| 0                                                                        | 0     | 0    | 8-bit/Asynchronous  | F <sub>OSC</sub> /[64 (n+1)] |  |  |  |

| 0                                                                        | 0     | 1    | 8-bit/Asynchronous  | E /[16 (n+1)]                |  |  |  |

| 0                                                                        | 1     | 0    | 16-bit/Asynchronous | F <sub>OSC</sub> /[16 (n+1)] |  |  |  |

| 0                                                                        | 1     | 1    | 16-bit/Asynchronous |                              |  |  |  |

| 1                                                                        | 0     | х    | 8-bit/Synchronous   | F <sub>OSC</sub> /[4 (n+1)]  |  |  |  |

| 1                                                                        | 1     | х    | 16-bit/Synchronous  |                              |  |  |  |

| <b>Note:</b> x = Don't care, n = value of SPxBRGH:SPxBRGL register pair. |       |      |                     |                              |  |  |  |

Table 36-2. Sample Baud Rates for Asynchronous Modes

|        | SYNC = 0, BRGH = 0, BRG16 = 0 |            |                             |                               |            |                             |                               |            |                             |                                |            |                             |

|--------|-------------------------------|------------|-----------------------------|-------------------------------|------------|-----------------------------|-------------------------------|------------|-----------------------------|--------------------------------|------------|-----------------------------|

| BAUD   | Fosc                          | = 32.0     | 00 MHz                      | F <sub>OSC</sub> = 20.000 MHz |            |                             | F <sub>OSC</sub> = 18.432 MHz |            |                             | F <sub>OSC</sub> = 11.0592 MHz |            |                             |

| RATE   | Actual<br>Rate                | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate                | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate                | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate                 | %<br>Error | SPBRG<br>value<br>(decimal) |

| 300    | _                             | _          | _                           | _                             | _          | _                           | _                             | _          | _                           | _                              | _          |                             |

| 1200   |                               |            |                             | 1221                          | 1.73       | 255                         | 1200                          | 0.00       | 239                         | 1200                           | 0.00       | 143                         |

| 2400   | 2404                          | 0.16       | 207                         | 2404                          | 0.16       | 129                         | 2400                          | 0.00       | 119                         | 2400                           | 0.00       | 71                          |

| 9600   | 9615                          | 0.16       | 51                          | 9470                          | -1.36      | 32                          | 9600                          | 0.00       | 29                          | 9600                           | 0.00       | 17                          |

| 10417  | 10417                         | 0.00       | 47                          | 10417                         | 0.00       | 29                          | 10286                         | -1.26      | 27                          | 10165                          | -2.42      | 16                          |

| 19.2k  | 19.23k                        | 0.16       | 25                          | 19.53k                        | 1.73       | 15                          | 19.20k                        | 0.00       | 14                          | 19.20k                         | 0.00       | 8                           |

| 57.6k  | 55.55k                        | -3.55      | 3                           | _                             |            | _                           | 57.60k                        | 0.00       | 7                           | 57.60k                         | 0.00       | 2                           |

| 115.2k | _                             | _          | _                           | _                             | _          | _                           | _                             | _          | _                           | _                              | _          | _                           |

|      | SYNC = 0, BRGH = 0, BRG16 = 0 |            |                             |                  |            |                             |                   |            |                             |                  |            |                             |  |  |  |

|------|-------------------------------|------------|-----------------------------|------------------|------------|-----------------------------|-------------------|------------|-----------------------------|------------------|------------|-----------------------------|--|--|--|

| BAUD | Fosc = 8.000 MHz              |            |                             | Fosc = 4.000 MHz |            |                             | Fosc = 3.6864 MHz |            |                             | Fosc = 1.000 MHz |            |                             |  |  |  |

| RATE | Actual<br>Rate                | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate   | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate    | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate   | %<br>Error | SPBRG<br>value<br>(decimal) |  |  |  |

| 300  | _                             |            |                             | 300              | 0.16       | 207                         | 300               | 0.00       | 191                         | 300              | 0.16       | 51                          |  |  |  |

| 1200 | 1202                          | 0.16       | 103                         | 1202             | 0.16       | 51                          | 1200              | 0.00       | 47                          | 1202             | 0.16       | 12                          |  |  |  |

| 2400 | 2404                          | 0.16       | 51                          | 2404             | 0.16       | 25                          | 2400              | 0.00       | 23                          | _                | _          | _                           |  |  |  |

| 9600 | 9615                          | 0.16       | 12                          | _                | _          | _                           | 9600              | 0.00       | 5                           | _                | _          | _                           |  |  |  |

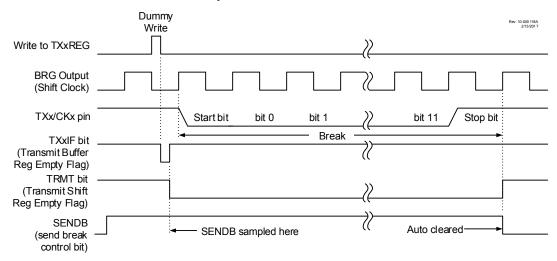

- Write '55h' to TXxREG to load the Sync character into the transmit FIFO buffer.

- After the Break has been sent, the SENDB bit is reset by hardware and the Sync character is then transmitted.

When the TXxREG becomes empty, as indicated by the TXxIF, the next data byte can be written to TXxREG.

#### 36.2.5 Receiving a Break Character

The EUSART module can receive a Break character in two ways.

The first method to detect a Break character uses the FERR bit of the RCxSTA register and the received data as indicated by RCxREG. The Baud Rate Generator is assumed to have been initialized to the expected baud rate.

A Break character has been received when all three of the following conditions are true:

- RCxIF bit is set

- FERR bit is set

- RCxREG = 00h

The second method uses the Auto-Wake-up feature described in Auto-Wake-up on Break. By enabling this feature, the EUSART will sample the next two transitions on RX/DT, cause an RCxIF interrupt, and receive the next data byte followed by another interrupt.

Note that following a Break character, the user will typically want to enable the Auto-Baud Detect feature. For both methods, the user can set the ABDEN bit of the BAUDxCON register before placing the EUSART in Sleep mode.

Figure 36-10. Send Break Character Sequence

#### 36.3 **EUSART Synchronous Mode**

Synchronous serial communications are typically used in systems with a single master and one or more slaves. The master device contains the necessary circuitry for baud rate generation and supplies the clock for all devices in the system. Slave devices can take advantage of the master clock by eliminating the internal clock generation circuitry.

#### 36.6.1 RCxSTA

Name: RCxSTA Address: 0x011D

#### Receive Status and Control Register

| Bit    | 7    | 6   | 5    | 4    | 3     | 2    | 1    | 0    |

|--------|------|-----|------|------|-------|------|------|------|

|        | SPEN | RX9 | SREN | CREN | ADDEN | FERR | OERR | RX9D |

| Access | R/W  | R/W | R/W  | R/W  | R/W   | RO   | R/HC | R/HC |

| Reset  | 0    | 0   | 0    | 0    | 0     | 0    | 0    | 0    |

#### Bit 7 - SPEN Serial Port Enable bit

| Va | alue | Description                          |

|----|------|--------------------------------------|

| 1  |      | Serial port enabled                  |

| 0  |      | Serial port disabled (held in Reset) |

#### Bit 6 - RX9 9-Bit Receive Enable bit

| Value | Description             |

|-------|-------------------------|

| 1     | Selects 9-bit reception |

| 0     | Selects 8-bit reception |

#### Bit 5 – SREN Single Receive Enable bit

Controls reception. This bit is cleared by hardware when reception is complete

| Value | Condition             | Description                |

|-------|-----------------------|----------------------------|

| 1     | SYNC = 1 AND CSRC = 1 | Start single receive       |

| 0     | SYNC = 1 AND CSRC = 1 | Single receive is complete |

| X     | SYNC = 0 OR CSRC = 0  | Don't care                 |

#### Bit 4 - CREN Continuous Receive Enable bit

| Value | Condition | Description                                                                 |

|-------|-----------|-----------------------------------------------------------------------------|

| 1     | SYNC = 1  | Enables continuous receive until enable bit CREN is cleared (CREN overrides |

|       |           | SREN)                                                                       |

| 0     | SYNC = 1  | Disables continuous receive                                                 |

| 1     | SYNC = 0  | Enables receiver                                                            |

| 0     | SYNC = 0  | Disables receiver                                                           |

#### Bit 3 - ADDEN Address Detect Enable bit

| Value | Condition            | Description                                                                                   |

|-------|----------------------|-----------------------------------------------------------------------------------------------|

| 1     | SYNC = 0 AND RX9 = 1 | The receive buffer is loaded and the interrupt occurs only when the ninth received bit is set |

| 0     | SYNC = 0 AND RX9 = 1 | All bytes are received and interrupt always occurs. Ninth bit can be used as parity bit       |

| Χ     | RX9 = 0 OR SYNC = 1  | Don't care                                                                                    |

### Bit 2 - FERR Framing Error bit

# PIC16(L)F18426/46

# (EUSART) Enhanced Universal Synchronous Asyn...

| Value | Condition | Description                                                          |

|-------|-----------|----------------------------------------------------------------------|

| 1     | SYNC=0    | Auto-Baud Detect mode is enabled (clears when auto-baud is complete) |

| 0     | SYNC=0    | Auto-Baud Detect is complete or mode is disabled                     |

| X     | SYNC=1    | Don't care                                                           |

|                          | Standard Operating Conditions (unless otherwise stated) $V_{DD} = 3.0V, T_A = 25^{\circ}C$ |                              |   |      |    |    |  |  |  |

|--------------------------|--------------------------------------------------------------------------------------------|------------------------------|---|------|----|----|--|--|--|

| v <sub>DD</sub> – 3.0 v, | 1A - 25 C                                                                                  |                              |   |      |    |    |  |  |  |

| Param No.                | Param No. Sym. Characteristic Min. Typ. † Max. Units Conditions                            |                              |   |      |    |    |  |  |  |

| DSB03*                   | R <sub>UNIT</sub>                                                                          | Unit Resistor<br>Value       | _ | 5000 | _  | Ω  |  |  |  |

| DSB04*                   | T <sub>ST</sub>                                                                            | Settling Time <sup>(1)</sup> | _ | _    | 10 | μs |  |  |  |

<sup>\* -</sup> These parameters are characterized but not tested.

#### Note:

1. Settling time measured while DACR<4:0> transitions from '00000' to '01111'.

# 42.4.11 Fixed Voltage Reference (FVR) Specifications Table 42-17.

| Standard O | Standard Operating Conditions (unless otherwise stated) |                   |      |        |      |       |                          |  |  |  |

|------------|---------------------------------------------------------|-------------------|------|--------|------|-------|--------------------------|--|--|--|

| Param No.  | Sym.                                                    | Characteristic    | Min. | Typ. † | Max. | Units | Conditions               |  |  |  |

| FVR01      | V <sub>FVR</sub> 1                                      | 1x Gain (1.024V)  | -4   | _      | +4   | %     | VDD≥2.5V, -40°C to 85°C  |  |  |  |

| FVR02      | V <sub>FVR</sub> 2                                      | 2x Gain (2.048V)  | -4   | _      | +4   | %     | VDD≥2.5V, -40°C to 85°C  |  |  |  |

| FVR03      | V <sub>FVR</sub> 4                                      | 4x Gain (4.096V)  | -5   | _      | +5   | %     | VDD≥4.75V, -40°C to 85°C |  |  |  |

| FVR04      | T <sub>FVRST</sub>                                      | FVR Start-up Time |      | 60     | _    | μs    |                          |  |  |  |

# 42.4.12 Zero Cross Detect (ZCD) Specifications Table 42-18.

#### **Standard Operating Conditions (unless otherwise stated)** $V_{DD} = 3.0V, T_A = 25^{\circ}C$ Characteristic Conditions Param Sym. Min. Typ. † Max. Units No. ZC01 Voltage on Zero V 0.75 $V_{PINZC}$ Cross Pin ZC02 Maximum source or 600 μΑ I<sub>ZCD\_MAX</sub> sink current ZC03 T<sub>RESPH</sub> Response Time, 1 μs Rising Edge T<sub>RESPI</sub> Response Time, 1 μs Falling Edge † Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design

guidance only and are not tested.

<sup>†</sup> Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

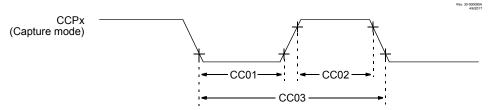

Figure 42-13. Capture/Compare/PWM Timings (CCP)

Note: Refer to Figure 42-4 for load conditions.

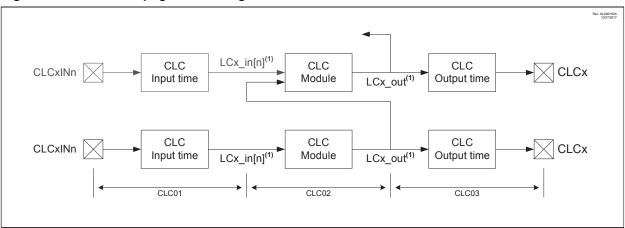

# 42.4.15 Configurable Logic Cell (CLC) Characteristics Table 42-21.

#### **Standard Operating Conditions (unless otherwise stated)** Operating Temperature: -40°C≤T<sub>A</sub>≤+125°C Param No. Sym. Characteristic Min. Max. Units **Conditions** Typ. † CLC01\* 7 CLC input time OS5 (Note1) T<sub>CI CIN</sub> ns CLC02\* CLC module input to $V_{DD} = 1.8V$ $T_{CLC}$ 24 ns output propagation time 12 $V_{DD} > 3.6V$ ns CLC03\* T<sub>CLCOUT</sub> CLC output Rise Time OS7 (Note1) time Fall Time OS8 (Note1) CLC04\* CLC maximum 32 MHz $F_{CLCMAX}$ Fosc switching frequency

#### Note:

1. See "I/O and CLKOUT Timing Specifications" for OS5, OS7 and OS8 rise and fall times.

Figure 42-14. CLC Propagation Timing

**Related Links**

<sup>\* -</sup> These parameters are characterized but not tested.

<sup>† -</sup> Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

| Standard Operating Conditions (unless otherwise stated) |          |                  |                  |      |        |      |       |            |

|---------------------------------------------------------|----------|------------------|------------------|------|--------|------|-------|------------|

| Param. No.                                              | Sym.     | Characteristic   |                  | Min. | Тур. † | Max. | Units | Conditions |

|                                                         |          |                  | 400 kHz<br>mode  | 600  | _      | _    |       |            |

| * - These pa                                            | rameters | are characterize | ed but not teste | ed.  |        |      |       |            |

Figure 42-21. I<sup>2</sup>C Bus Start/Stop Bits Timing

Note: Refer to Figure 42-4 for load conditions.

# 42.4.20 I<sup>2</sup>C Bus Data Requirements Table 42-26.

| Standard Operating Conditions (unless otherwise stated) |                   |                 |                 |                    |          |       |                                                      |

|---------------------------------------------------------|-------------------|-----------------|-----------------|--------------------|----------|-------|------------------------------------------------------|

| Param.<br>No.                                           | Sym.              | Characteristic  |                 | Min.               | Max.     | Units | Conditions                                           |

| SP100*                                                  | T <sub>HIGH</sub> | Clock high time | 100 kHz<br>mode | 4.0                | _        | μs    | Device must<br>operate at a<br>minimum of 1.5<br>MHz |

|                                                         |                   |                 | 400 kHz<br>mode | 0.6                | <u>—</u> | μs    | Device must<br>operate at a<br>minimum of 10<br>MHz  |

|                                                         |                   |                 | SSP<br>module   | 1.5T <sub>CY</sub> | _        |       |                                                      |

| SP101*                                                  | T <sub>LOW</sub>  | Clock low time  | 100 kHz<br>mode | 4.7                | <u> </u> | μs    | Device must<br>operate at a<br>minimum of 1.5<br>MHz |

|                                                         |                   |                 | 400 kHz<br>mode | 1.3                | <u> </u> | μs    | Device must<br>operate at a<br>minimum of 10<br>MHz  |