#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 32MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 18                                                                          |

| Program Memory Size        | 28KB (16K x 14)                                                             |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 256 x 8                                                                     |

| RAM Size                   | 2K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                 |

| Data Converters            | A/D 17x12b; D/A 1x5b                                                        |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                                              |

| Supplier Device Package    | 20-SSOP                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f18446t-i-ss |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

*Device ID, EEPROM, and Configuration Words*" section for more information on accessing these memory locations. For more information on checksum calculation, see the *"PIC16(L)F184XX Memory Programming Specification"*, (DS40001970).

#### **Related Links**

NVMREG Access to Device Information Area, Device Configuration Area, User ID, Device ID, EEPROM, and Configuration Words

### 4.5 Device ID and Revision ID

The 14-bit device ID word is located at 0x8006 and the 14-bit revision ID is located at 0x8005. These locations are read-only and cannot be erased or modified.

Development tools, such as device programmers and debuggers, may be used to read the Device ID, Revision ID and Configuration Words. Refer to the *"Nonvolatile Memory (NVM) Control"* section for more information on accessing these locations.

#### **Related Links**

(NVM) Nonvolatile Memory Control

### 4.6 Register Summary - Configuration Words

| Offset  | Name           | Bit Pos. |        |     |             |             |             |             |              |          |

|---------|----------------|----------|--------|-----|-------------|-------------|-------------|-------------|--------------|----------|

| 0x8007  | CONFIG1        | 7:0      |        |     | RSTOSC[2:0] |             |             |             | FEXTOSC[2:0] | J        |

| 0x8007  | CONFIGI        | 13:8     |        |     | FCMEN       |             | CSWEN       |             |              | CLKOUTEN |

| 0x8008  | CONFIG2        | 7:0      | BOF    | REN | LPBOREN     |             |             | PWR         | FS[1:0]      | MCLRE    |

| 0x0000  | CONFIG2        | 13:8     |        |     | DEBUG       | STVREN      | PPS1WAY     | ZCDDIS      | BORV         |          |

| 0x8009  | CONFIG3        | 7:0      |        | WDT | E[1:0]      |             | WDTCPS[4:0] |             |              |          |

| 0x8009  | CONFIGS        | 13:8     |        |     |             | WDTCCS[2:0] | WDTCWS[2:0] |             |              | I        |

| 0x800A  | CONFIG4        | 7:0      | WRTAPP |     | SAFEN       |             | BBEN        | BBSIZE[2:0] |              |          |

| UXOUUA  | CONFIG4        | 13:8     |        |     | LVP         |             | WRTSAF      | WRTD        | WRTC         | WRTB     |

| 0x800B  | 0x800B CONFIG5 | 7:0      |        |     |             |             |             |             |              | CP       |

| UNCOULD | CONFIGS        | 13:8     |        |     |             |             |             |             |              |          |

## 4.7 Register Definitions: Configuration Words

#### 9.2.1.4 4x PLL

The oscillator module contains a 4x PLL that can be used with the external clock sources to provide a system clock source. The input frequency for the PLL must fall within specifications.

The PLL can be enabled for use by one of two methods:

- 1. Program the RSTOSC bits in the Configuration Word 1 to '010' (enable EXTOSC with 4x PLL).

- 2. Write the NOSC bits to '010' (enable EXTOSC with 4x PLL).

#### **Related Links**

OSCCON1

**PLL Specifications**

#### 9.2.1.5 Secondary Oscillator

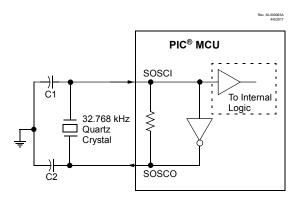

The secondary oscillator is a separate oscillator block that can be used as an alternate system clock source. The secondary oscillator is optimized for 32.768 kHz, and can be used with an external crystal oscillator connected to the SOSCI and SOSCO device pins, or an external clock source connected to the SOSCIN pin. The secondary oscillator can be selected during run-time using clock switching.

#### Figure 9-5. Quartz Crystal Operation (Secondary Oscillator)

#### Note:

- 1. Quartz crystal characteristics vary according to type, package and manufacturer. The user should consult the manufacturer data sheets for specifications and recommended application.

- 2. Always verify oscillator performance over the V<sub>DD</sub> and temperature range that is expected for the application.

- 3. For oscillator design assistance, reference the following Microchip Application Notes:

- AN826, "Crystal Oscillator Basics and Crystal Selection for PIC<sup>®</sup> and PIC<sup>®</sup> Devices" (DS00826)

- AN849, *"Basic PIC<sup>®</sup> Oscillator Design"* (DS00849)

- AN943, "Practical PIC<sup>®</sup> Oscillator Analysis and Design" (DS00943)

- AN949, "Making Your Oscillator Work" (DS00949)

- TB097, "Interfacing a Micro Crystal MS1V-T1K 32.768 kHz Tuning Fork Crystal to a PIC16F690/SS" (DS91097)

- AN1288, "Design Practices for Low-Power External Oscillators" (DS01288)

#### **Related Links**

Clock Switching

# PIC16(L)F18426/46

Interrupts

**Note:** Interrupt flag bits are set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the Global Enable bit, GIE, of the INTCON appropriate interrupt flag bits are clear prior to enabling an interrupt.

## 11.4 Register Summary - Power Savings Control

| Offset | Name     | Bit Pos. |       |       |     |     |  |           |  |

|--------|----------|----------|-------|-------|-----|-----|--|-----------|--|

| 0x0812 | VREGCON  | 7:0      |       |       |     |     |  | VREGPM    |  |

| 0x0813 |          |          |       |       |     |     |  |           |  |

|        | Reserved |          |       |       |     |     |  |           |  |

| 0x088B |          |          |       |       |     |     |  |           |  |

| 0x088C | CPUDOZE  | 7:0      | IDLEN | DOZEN | ROI | DOE |  | DOZE[2:0] |  |

## 11.5 Register Definitions: Power Savings Control

#### 13.6.4 NVMCON2

| Name:    | NVMCON2 |

|----------|---------|

| Address: | 0x81F   |

Nonvolatile Memory Control 2 Register

| Bit    | 7  | 6  | 5  | 4     | 3        | 2  | 1  | 0  |

|--------|----|----|----|-------|----------|----|----|----|

|        |    |    |    | NVMCC | DN2[7:0] |    |    |    |

| Access | WO | WO | WO | WO    | WO       | WO | WO | WO |

| Reset  | 0  | 0  | 0  | 0     | 0        | 0  | 0  | 0  |

Bits 7:0 - NVMCON2[7:0] Flash Memory Unlock Pattern bits

**Note:** To unlock writes, a 55h must be written first followed by an AAh before setting the WR bit of the NVMCON1 register. The value written to this register is used to unlock the writes.

# PIC16(L)F18426/46

## (PPS) Peripheral Pin Select Module

| Input Signal         | Input Pagiator         | Default loca         | tion at POR       | Reset Value (xxxPPS<4:0>) |                   |  |

|----------------------|------------------------|----------------------|-------------------|---------------------------|-------------------|--|

| Input Signal<br>Name | Input Register<br>Name | 14/16-pin<br>devices | 20-pin<br>devices | 14/16-pin<br>devices      | 20-pin<br>devices |  |

| SS1                  | SS1PPS                 | RC3                  | RC6               | 10011                     | 10110             |  |

| SCK2                 | SCL2PPS                | RC4                  | RB7               | 10100                     | 01111             |  |

| SCL2                 | SCL2PPS                | RC4                  | RB7               | 10100                     | 01111             |  |

| SDI2                 | SDA2PPS                | RC5                  | RB5               | 10101                     | 01101             |  |

| SDA2                 | SDA2PPS                | RC5                  | RB5               | 10101                     | 01101             |  |

| SS2                  | SS2PPS                 | RA0                  | RA1               | 00000                     | 00001             |  |

| RX1                  | RX1PPS                 | RC5                  | RB5               | 10101                     | 01101             |  |

| DT1 <sup>(1)</sup>   | RX1PPS                 | RC5                  | RB5               | 10101                     | 01101             |  |

| CK1 <sup>(1)</sup>   | CK1PPS                 | RC4                  | RB7               | 10100                     | 01111             |  |

| SMT1SIG              | SMT1SIGPPS             | RC0                  | RC0               | 10000                     | 10000             |  |

| SMT1WIN              | SMT1WINPPS             | RA5                  | RA5               | 00100                     | 00100             |  |

| Noto:                |                        |                      |                   |                           |                   |  |

#### Note:

1. DT1 and CK1 are bidirectional signals used in EUSART synchronous mode.

## 15.2 PPS Outputs

Each I/O pin has an RxyPPS register with which the pin output source is selected. With few exceptions, the port TRIS control associated with that pin retains control over the pin output driver. Peripherals that control the pin output driver as part of the peripheral operation will override the TRIS control as needed. These peripherals include:

- EUSART (synchronous operation)

- MSSP (I<sup>2</sup>C)

Although every pin has its own RxyPPS peripheral selection register, the selections are identical for every pin as shown in the following table.

**Important:** The notation "Rxy" is a place holder for the pin identifier. The 'x' holds the place of the PORT letter and the 'y' holds the place of the bit number. For example, Rxy = RA0 for the RA0PPS register.

#### Table 15-2. PPS Output Signal Routing Options

| Output Signal Name | RxyPPS Register Value |

|--------------------|-----------------------|

| ADCGRDA            | 0x1F                  |

| ADCGRDB            | 0x20                  |

| C10UT              | 0x11                  |

#### 17.6.8 IOCCN

Name:IOCCNAddress:0x1F54

Interrupt-on-Change Negative Edge Register

| Bit    | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |

|--------|--------|--------|--------|--------|--------|--------|--------|--------|

|        | IOCCN7 | IOCCN6 | IOCCN5 | IOCCN4 | IOCCN3 | IOCCN2 | IOCCN1 | IOCCN0 |

| Access | R/W    |

| Reset  | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      |

Bits 0, 1, 2, 3, 4, 5, 6, 7 – IOCCNn Interrupt-on-Change Negative Edge Enable bits

| Value | Description                                                                              |

|-------|------------------------------------------------------------------------------------------|

| 1     | Interrupt-on-Change enabled on the IOCC pin for a negative-going edge. Associated Status |

|       | bit and interrupt flag will be set upon detecting an edge.                               |

| 0     | Interrupt-on-Change disabled for the associated pin                                      |

Note: IOCCN6 and IOCCN7 are available on 20-pin or higher pin-count devices only.

- ADC Precharge Time

- Additional Sample and Hold Capacitor

- Single/Double Sample Conversion

- Guard Ring Outputs

#### 20.1.1 Port Configuration

The ADC can be used to convert both analog and digital signals. When converting analog signals, the I/O pin should be configured for analog by setting the associated TRIS and ANSEL bits. Refer to the "I/O Ports" section for more information.

**Important:** Analog voltages on any pin that is defined as a digital input may cause the input buffer to conduct excess current.

#### **Related Links**

I/O Ports

#### 20.1.2 Channel Selection

The ADPCH register determines which channel is connected to the sample and hold circuit.

When changing channels, a delay is required before starting the next conversion.

There are several channel selections available, as shown in the following table:

| РСН           | ADC Positive Channel Input       |

|---------------|----------------------------------|

| 111111        | Fixed Voltage Reference (FVR) 2  |

| 111110        | Fixed Voltage Reference (FVR) 1  |

| 111101        | DAC1 output                      |

| 111100        | Temperature Indicator            |

| 111011        | AV <sub>SS</sub> (Analog Ground) |

| 111010-011000 | Reserved. No channel connected.  |

| 010111        | RC7/ANC7                         |

| 010110        | RC6/ANC6                         |

| 010101        | RC5/ ANC5                        |

| 010100        | RC4/ ANC4                        |

| 010011        | RC3/ANC3                         |

| 010010        | RC2/ANC2                         |

| 010001        | RC1/ ANC1                        |

| 010000        | RC0/ANC0                         |

| 001111        | RB7/ANB7                         |

#### Table 20-1. ADC Positive Input Channel Selections

#### 20.8.16 ADPREV

Name:ADPREVAddress:0x09B

#### ADC Previous Result Register

| Bit    | 15 | 14 | 13 | 12   | 11      | 10 | 9  | 8  |

|--------|----|----|----|------|---------|----|----|----|

|        |    |    |    | PREV | 'H[7:0] |    |    |    |

| Access | RO | RO | RO | RO   | RO      | RO | RO | RO |

| Reset  | x  | х  | x  | x    | x       | x  | x  | х  |

|        |    |    |    |      |         |    |    |    |

| Bit    | 7  | 6  | 5  | 4    | 3       | 2  | 1  | 0  |

|        |    |    |    | PREV | ′L[7:0] |    |    |    |

| Access | RO | RO | RO | RO   | RO      | RO | RO | RO |

| Reset  | х  | x  | х  | х    | х       | х  | х  | x  |

Bits 15:8 – PREVH[7:0] Previous ADC Result Most Significant bits

| Value     | Condition | Description                                                               |

|-----------|-----------|---------------------------------------------------------------------------|

| 0 to 0xFF | PSIS = 1  | Upper byte of ADFLTR at the start of current ADC conversion               |

| varies    | PSIS = 0  | Upper bits of ADRES at the start of current ADC conversion <sup>(1)</sup> |

Bits 7:0 - PREVL[7:0] Previous ADC Result Least Significant bits

| Value     | Condition | Description                                                               |

|-----------|-----------|---------------------------------------------------------------------------|

| 0 to 0xFF | PSIS = 1  | Lower byte of ADFLTR at the start of current ADC conversion               |

| varies    | PSIS = 0  | Lower bits of ADRES at the start of current ADC conversion <sup>(1)</sup> |

**Note:** If PSIS = 0, PREVH and PREVL are formatted the same way as ADRES is, depending on the FRM bit.

#### 20.8.21 ADUTH

Name:ADUTHAddress:0x08E

ADC Upper Threshold Register

ADLTH and ADUTH are compared with ADERR to set the UTHR and LTHR bits. Depending on the setting of MD, an interrupt may be triggered by the results of this comparison.

| Bit    | 15        | 14        | 13  | 12  | 11  | 10  | 9   | 8   |  |  |

|--------|-----------|-----------|-----|-----|-----|-----|-----|-----|--|--|

|        |           | UTHH[7:0] |     |     |     |     |     |     |  |  |

| Access | R/W       | R/W       | R/W | R/W | R/W | R/W | R/W | R/W |  |  |

| Reset  | 0         | 0         | 0   | 0   | 0   | 0   | 0   | 0   |  |  |

|        |           |           |     |     |     |     |     |     |  |  |

| Bit    | 7         | 6         | 5   | 4   | 3   | 2   | 1   | 0   |  |  |

|        | UTHL[7:0] |           |     |     |     |     |     |     |  |  |

| Access | R/W       | R/W       | R/W | R/W | R/W | R/W | R/W | R/W |  |  |

| Reset  | 0         | 0         | 0   | 0   | 0   | 0   | 0   | 0   |  |  |

Bits 15:8 – UTHH[7:0] ADC Upper Threshold MSB.

Bits 7:0 – UTHL[7:0] ADC Upper Threshold LSB.

## 24.4 ZCD Interrupts

An interrupt will be generated upon a change in the ZCD logic output when the appropriate interrupt enables are set. A rising edge detector and a falling edge detector are present in the ZCD for this purpose.

The ZCDIF bit of the PIRx register will be set when either edge detector is triggered and its associated enable bit is set. The INTP enables rising edge interrupts and the INTN bit enables falling edge interrupts. Priority of the interrupt can be changed if the IPEN bit of the INTCON register is set. The ZCD interrupt can be made high or low priority by setting or clearing the ZCDIP bit of the IPRx register.

To fully enable the interrupt, the following bits must be set:

- ZCDIE bit of the PIEx register

- INTP bit for rising edge detection

- INTN bit for falling edge detection

- PEIE and GIE bits of the INTCON register

Changing the POL bit will cause an interrupt, regardless of the level of the SEN bit.

The ZCDIF bit of the PIRx register must be cleared in software as part of the interrupt service. If another edge is detected while this flag is being cleared, the flag will still be set at the end of the sequence.

Related Links INTCON PIR2

## 24.5 Correction for Z<sub>CPINV</sub> Offset

The actual voltage at which the ZCD switches is the reference voltage at the non-inverting input of the ZCD op amp. For external voltage source waveforms other than square waves, this voltage offset from zero causes the zero-cross event to occur either too early or too late.

#### 24.5.1 Correction by AC Coupling

When the external voltage source is sinusoidal, the effects of the  $Z_{CPINV}$  offset can be eliminated by isolating the external voltage source from the ZCD pin with a capacitor, in addition to the voltage reducing resistor. The capacitor will cause a phase shift resulting in the ZCD output switch in advance of the actual zero crossing event. The phase shift will be the same for both rising and falling zero crossings, which can be compensated for by either delaying the CPU response to the ZCD switch by a timer or other means, or selecting a capacitor value large enough that the phase shift is negligible.

To determine the series resistor and capacitor values for this configuration, start by computing the impedance, Z, to obtain a peak current of 300  $\mu$ A. Next, arbitrarily select a suitably large non-polar capacitor and compute its reactance, Xc, at the external voltage source frequency. Finally, compute the series resistor, capacitor peak voltage, and phase shift by the formulas shown below.

When this technique is used and the input signal is not present, the ZCD will tend to oscillate. To avoid this oscillation, connect the ZCD pin to  $V_{DD}$  or GND with a high-impedance resistor such as 200K.

#### Equation 24-2. R-C Equations

$V_{PEAK}$  = external voltage source peak voltage

f = external voltage source frequency

#### 27.9.5 TxCLKCON

| Name:    | TxCLKCON          |

|----------|-------------------|

| Address: | 0x290,0x296,0x29C |

Timer Clock Source Selection Register

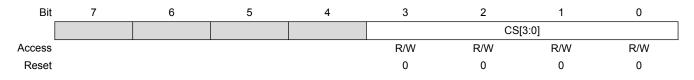

### Bits 3:0 - CS[3:0] Timer Clock Source Selection bits

| Value | Description                      |

|-------|----------------------------------|

| n     | See Clock Source Selection table |

- T2TMR is cleared

- The PWM output is active. (Exception: When the PWM duty cycle = 0%, the PWM output will remain inactive.)

- The PWMxDCH and PWMxDCL register values are latched into the buffers.

**Important:** The Timer2 postscaler has no effect on the PWM operation.

### 30.4 PWM Duty Cycle

The PWM duty cycle is specified by writing a 10-bit value to the PWMxDCH and PWMxDCL register pair. The PWMxDCH register contains the eight MSbs and the PWMxDCL<7:6>, the two LSbs. The PWMxDCH and PWMxDCL registers can be written to at any time.

The formulas below are used to calculate the PWM pulse width and the PWM duty cycle ratio.

#### Equation 30-2. Pulse Width

$PulseWidth = (PWMxDCH: PWMxDCL < 7:6 >) \bullet Tosc \bullet (TMR2PrescaleValue)$

Note:  $T_{OSC} = 1/F_{OSC}$

#### Equation 30-3. Duty Cycle Ratio

$DutyCycleRatio = \frac{(PWMxDCH:PWMxDCL < 7:6 > )}{4(T2PR + 1)}$

The 8-bit timer T2TMR register is concatenated with the two Least Significant bits of  $1/F_{OSC}$ , adjusted by the Timer2 prescaler to create the 10-bit time base. The system clock is used if the Timer2 prescaler is set to 1:1.

### 30.5 **PWM Resolution**

The resolution determines the number of available duty cycles for a given period. For example, a 10-bit resolution will result in 1024 discrete duty cycles, whereas an 8-bit resolution will result in 256 discrete duty cycles.

The maximum PWM resolution is ten bits when T2PR is 255. The resolution is a function of the T2PR register value as shown below.

#### Equation 30-4. PWM Resolution

$Resolution = \frac{\log[4(T2PR + 1)]}{\log(2)}bits$

**Important:** If the pulse-width value is greater than the period, the assigned PWM pin(s) will remain unchanged.

# 33. (CLC) Configurable Logic Cell

The Configurable Logic Cell (CLCx) module provides programmable logic that operates outside the speed limitations of software execution. The logic cell takes up to 64 input signals and, through the use of configurable gates, reduces the 64 inputs to four logic lines that drive one of eight selectable single-output logic functions.

Input sources are a combination of the following:

- I/O pins

- Internal clocks

- Peripherals

- Register bits

The output can be directed internally to peripherals and to an output pin.

**Important:** There are several CLC instances on this device. Throughout this section, the lower case 'x' in register names is a generic reference to the CLC instance number. For example, the first instance of the control register is CLC1CON and is generically described in this chapter as CLCxCON.

The following figure is a simplified diagram showing signal flow through the CLC. Possible configurations include:

- Combinatorial Logic

- AND

- NAND

- AND-OR

- AND-OR-INVERT

- OR-XOR

- OR-XNOR

- Latches

- S-R

- Clocked D with Set and Reset

- Transparent D with Set and Reset

#### 33.8.9 CLCxGLS2

| Name:    | CLCxGLS2                    |

|----------|-----------------------------|

| Address: | 0x1E18,0x1E22,0x1E2C,0x1E36 |

CLCx Gate3 Logic Select Register

| Bit    | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

|--------|-------|-------|-------|-------|-------|-------|-------|-------|

|        | G3D4T | G3D4N | G3D3T | G3D3N | G3D2T | G3D2N | G3D1T | G3D1N |

| Access | R/W   |

| Reset  | x     | x     | x     | x     | x     | x     | x     | x     |

#### Bits 1, 3, 5, 7 – G3DyT

dyT: Gate3 Data 'y' True (non-inverted) bit Reset States: Default = xxxx POR/BOR = x All Other Resets = u

| Value | Description              |

|-------|--------------------------|

| 1     | dyT is gated into g3     |

| 0     | dyT is not gated into g3 |

#### Bits 0, 2, 4, 6 – G3DyN

dyN: Gate3 Data 'y' Negated (inverted) bit Reset States: Default = xxxx POR/BOR = x All Other Resets = u

| Value | Description              |

|-------|--------------------------|

| 1     | dyN is gated into g3     |

| 0     | dyN is not gated into g3 |

If the AHEN bit is set, just as with any other address reception, the slave hardware will stretch the clock after the eighth falling edge of SCL. The slave must then set its ACKEN value and release the clock with communication progressing as it would normally.

#### 35.5.9 SSP Mask Register

An SSP Mask register (SSPxMSK) is available in I<sup>2</sup>C Slave mode as a mask for the value held in the SSPSR register during an address comparison operation. A zero ('0') bit in the SSPxMSK register has the effect of making the corresponding bit of the received address a "don't care".

This register is reset to all '1's upon any Reset condition and, therefore, has no effect on standard SSP operation until written with a mask value.

The SSP Mask register is active during:

- 7-bit Address mode: address compare of A<7:1>.

- 10-bit Address mode: address compare of A<7:0> only. The SSP mask has no effect during the reception of the first (high) byte of the address.

### 35.6 I<sup>2</sup>C Master Mode

Master mode is enabled by setting and clearing the appropriate SSPM bits and setting the SSPEN bit. In Master mode, the SDA and SCK pins must be configured as inputs. The MSSP peripheral hardware will override the output driver TRIS controls when necessary to drive the pins low.

Master mode of operation is supported by interrupt generation on the detection of the Start and Stop conditions. The Stop (P) and Start (S) bits are cleared from a Reset or when the MSSP module is disabled. Control of the I<sup>2</sup>C bus may be taken when the P bit is set, or the bus is Idle.

In Firmware Controlled Master mode, user code conducts all I<sup>2</sup>C bus operations based on Start and Stop bit condition detection. Start and Stop condition detection is the only active circuitry in this mode. All other communication is done by the user software directly manipulating the SDA and SCL lines.

The following events will cause the SSP Interrupt Flag bit, SSPxIF, to be set (SSP interrupt, if enabled):

- Start condition detected

- Stop condition detected

- Data transfer byte transmitted/received

- Acknowledge transmitted/received

- Repeated Start generated

#### Important:

- The MSSP module, when configured in I<sup>2</sup>C Master mode, does not allow queuing of events. For instance, the user is not allowed to initiate a Start condition and immediately write the SSPxBUF register to initiate transmission before the Start condition is complete. In this case, the SSPxBUF will not be written to and the WCOL bit will be set, indicating that a write to the SSPxBUF did not occur.

- 2. Master mode suspends Start/Stop detection when sending the Start/Stop condition by means of the SEN/PEN control bits. The SSPxIF bit is set at the end of the Start/Stop generation when hardware clears the control bit.

# 36.5 Register Summary - EUSART

| Offset | Name     | Bit Pos. |        |             |      |      |       |      |      |       |

|--------|----------|----------|--------|-------------|------|------|-------|------|------|-------|

| 0x0119 | RC1REG   | 7:0      |        | RCREG[7:0]  |      |      |       |      |      |       |

| 0x011A | TX1REG   | 7:0      |        | TXREG[7:0]  |      |      |       |      |      |       |

| 0x011B | SP1BRG   | 7:0      |        | SPBRGL[7:0] |      |      |       |      |      |       |

| UXUTIB | SPIBRG   | 15:8     |        | SPBRGH[7:0] |      |      |       |      |      |       |

| 0x011D | RC1STA   | 7:0      | SPEN   | RX9         | SREN | CREN | ADDEN | FERR | OERR | RX9D  |

| 0x011E | TX1STA   | 7:0      | CSRC   | TX9         | TXEN | SYNC | SENDB | BRGH | TRMT | TX9D  |

| 0x011F | BAUD1CON | 7:0      | ABDOVF | RCIDL       |      | SCKP | BRG16 |      | WUE  | ABDEN |

## 36.6 Register Definitions: EUSART Control

# PIC16(L)F18426/46

# **Register Summary**

| Offset | Name        | Bit Pos. |     |             |  |      |             |   |    |        |

|--------|-------------|----------|-----|-------------|--|------|-------------|---|----|--------|

| 0x1F56 |             |          |     |             |  |      |             |   |    |        |

|        | Reserved    |          |     |             |  |      |             |   |    |        |

| 0x1F7F |             |          |     |             |  |      |             |   |    |        |

| 0x1F80 | INDF0       | 7:0      |     |             |  | INDF | 0[7:0]      | 1 | 1  |        |

| 0x1F81 | INDF1       | 7:0      |     |             |  | INDF | 1[7:0]      |   |    |        |

| 0x1F82 | PCL         | 7:0      |     |             |  | PCL  | [7:0]       |   |    |        |

| 0x1F83 | STATUS      | 7:0      |     |             |  | TO   | PD          | Z | DC | С      |

| 0.4504 | 50.00       | 7:0      |     |             |  | FSR  | L[7:0]      |   |    |        |

| 0x1F84 | FSR0        | 15:8     |     |             |  | FSR  | H[7:0]      |   |    |        |

| 0.4500 | 50.54       | 7:0      |     |             |  | FSR  | L[7:0]      |   |    |        |

| 0x1F86 | FSR1        | 15:8     |     | FSRH[7:0]   |  |      |             |   |    |        |

| 0x1F88 | BSR         | 7:0      |     | BSR[5:0]    |  |      |             |   |    |        |

| 0x1F89 | WREG        | 7:0      |     |             |  | WRE  | G[7:0]      |   |    |        |

| 0x1F8A | PCLATH      | 7:0      |     |             |  |      | PCLATH[6:0] |   |    |        |

| 0x1F8B | INTCON      | 7:0      | GIE | PEIE        |  |      |             |   |    | INTEDG |

| 0x1F8C |             |          |     |             |  |      |             |   |    |        |

|        | Reserved    |          |     |             |  |      |             |   |    |        |

| 0x1FE3 |             |          |     |             |  |      |             |   |    |        |

| 0x1FE4 | STATUS_SHAD | 7:0      |     |             |  | TO   | PD          | Z | DC | С      |

| 0x1FE5 | WREG_SHAD   | 7:0      |     | WREG[7:0]   |  |      |             |   |    |        |

| 0x1FE6 | BSR_SHAD    | 7:0      |     | BSR[5:0]    |  |      |             |   |    |        |

| 0x1FE7 | PCLATH_SHAD | 7:0      |     | PCLATH[6:0] |  |      |             |   |    |        |

| 0x1FE8 |             | 7:0      |     |             |  | FSR  | L[7:0]      |   |    |        |

| UXIFE  | FSR0_SHAD   | 15:8     |     |             |  | FSR  | H[7:0]      |   |    |        |

| 0x1FEA |             | 7:0      |     |             |  | FSR  | L[7:0]      |   |    |        |

| UXIFEA | FSR1_SHAD   | 15:8     |     |             |  | FSR  | H[7:0]      |   |    |        |

# PIC16(L)F18426/46

# Instruction Set Summary

| MOVLW        | Move literal | Move literal to W                                                                            |  |  |  |  |

|--------------|--------------|----------------------------------------------------------------------------------------------|--|--|--|--|

| Description: |              | The 8-bit literal 'k' is loaded into W register.<br>The "don't cares" will assemble as '0's. |  |  |  |  |

| Words:       | 1            |                                                                                              |  |  |  |  |

| Cycles:      | 1            |                                                                                              |  |  |  |  |

|              |              |                                                                                              |  |  |  |  |

| Example:          | MOVIW | 5Ah |

|-------------------|-------|-----|

| After Instruction |       |     |

| 14/ - 41          |       |     |

W = 5Ah

| MOVWF            | Move W to f                       |  |  |  |

|------------------|-----------------------------------|--|--|--|

| Syntax:          | [ <i>label</i> ] MOVWF f          |  |  |  |

| Operands:        | 0 ≤ f ≤ 127                       |  |  |  |

| Operation:       | $(W) \to f$                       |  |  |  |

| Status Affected: | None                              |  |  |  |

| Description:     | Move data from W to register 'f'. |  |  |  |

| Words:           | 1                                 |  |  |  |

| Cycles:          | 1                                 |  |  |  |

| Example:                         | MOVWF | LATA                                  |

|----------------------------------|-------|---------------------------------------|

| Before Instruction<br>LATA = FFh |       | , , , , , , , , , , , , , , , , , , , |

| W = 4Fh                          |       |                                       |

| After Instruction                |       |                                       |

| LATA = 4Fh                       |       |                                       |

| W = 4Fh                          |       |                                       |

| MOVWI     | Move W to INDFn                                             |

|-----------|-------------------------------------------------------------|

| Syntax:   | [ <i>label</i> ] MOVWI ++FSRn<br>[ <i>label</i> ] MOVWIFSRn |

|           | [ <i>label</i> ] MOVWI FSRn++                               |

|           | [ label ] MOVWI FSRn                                        |

|           | [ <i>label</i> ] MOVWI k[FSRn]                              |

| Operands: |                                                             |

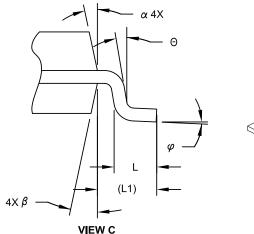

#### 14-Lead Plastic Small Outline (SL) - Narrow, 3.90 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units | MILLIMETERS |     |      |

|--------------------------|-------|-------------|-----|------|

| Dimension Limits         |       | MIN         | NOM | MAX  |

| Number of Pins           | N     | 14          |     |      |

| Pitch                    | е     | 1.27 BSC    |     |      |

| Overall Height           | A     | -           | -   | 1.75 |

| Molded Package Thickness | A2    | 1.25        | -   | -    |

| Standoff §               | A1    | 0.10        | -   | 0.25 |

| Overall Width            | E     | 6.00 BSC    |     |      |

| Molded Package Width     | E1    | 3.90 BSC    |     |      |

| Overall Length           | D     | 8.65 BSC    |     |      |

| Chamfer (Optional)       | h     | 0.25        | -   | 0.50 |

| Foot Length              | L     | 0.40        | -   | 1.27 |

| Footprint                | L1    | 1.04 REF    |     |      |

| Lead Angle               | Θ     | 0°          | -   | -    |

| Foot Angle               | φ     | 0°          | -   | 8°   |

| Lead Thickness           | С     | 0.10        | -   | 0.25 |

| Lead Width               | b     | 0.31        | -   | 0.51 |

| Mold Draft Angle Top     | α     | 5°          | -   | 15°  |

| Mold Draft Angle Bottom  | β     | 5°          | -   | 15°  |

Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. § Significant Characteristic

- Dimension D does not include mold flash, protrusions or gate burrs, which shall not exceed 0.15 mm per end. Dimension E1 does not include interlead flash or protrusion, which shall not exceed 0.25 mm per side.

- Dimensioning and tolerancing per ASME Y14.5M BSC: Basic Dimension. Theoretically exact value shown without tolerances. REF: Reference Dimension, usually without tolerance, for information purposes only.

- 5. Datums A & B to be determined at Datum H.

Microchip Technology Drawing No. C04-065C Sheet 2 of 2