Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                              |

|----------------------------|------------------------------------------------------------------------------|

| Product Status             | Active                                                                       |

| Core Processor             | PIC                                                                          |

| Core Size                  | 8-Bit                                                                        |

| Speed                      | 32MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                    |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                        |

| Number of I/O              | 12                                                                           |

| Program Memory Size        | 28KB (16K x 14)                                                              |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | 256 x 8                                                                      |

| RAM Size                   | 2K x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                  |

| Data Converters            | A/D 11x12b; D/A 1x5b                                                         |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

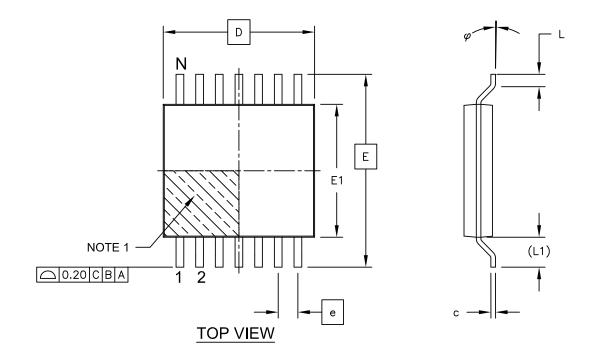

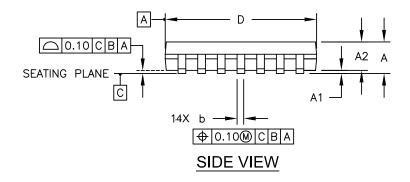

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 14-SOIC (0.154", 3.90mm Width)                                               |

| Supplier Device Package    | 14-SOIC                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf18426t-i-sl |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Device Information Area**

| Address Range           | Name of Region        | Standard Device Information                           |

|-------------------------|-----------------------|-------------------------------------------------------|

| 8118h                   | FVRA1X                | ADC FVR1 Output voltage for 1x setting (in mV)        |

| 8119h                   | FVRA2X                | ADC FVR1 Output Voltage for 2x setting (in mV)        |

| 811Ah                   | FVRA4X <sup>(1)</sup> | ADC FVR1 Output Voltage for 4x setting (in mV)        |

| 811Bh                   | FVRC1X                | Comparator FVR2 output voltage for 1x setting (in mV) |

| 811Ch                   | FVRC2X                | Comparator FVR2 output voltage for 2x setting (in mV) |

| 811Dh                   | FVRC4X <sup>(1)</sup> | Comparator FVR2 output voltage for 4x setting (in mV) |

| 811Eh-811Fh             |                       | Unassigned (2 Words)                                  |

| Note:<br>1. Value not p | resent on LF device   | S.                                                    |

# 5.1 Microchip Unique identifier (MUI)

The PIC16(L)F184XX devices are individually encoded during final manufacturing with a Microchip Unique Identifier, or MUI. The MUI cannot be erased by a Bulk Erase command or any other useraccessible means. This feature allows for manufacturing traceability of Microchip Technology devices in applications where this is required. It may also be used by the application manufacturer for a number of functions that require unverified unique identification, such as:

- Tracking the device

- Unique serial number

The MUI consists of nine program words and one reserved program word. When taken together, these fields form a unique identifier. The MUI is stored in read-only locations, located between 8100h to 8109h in the DIA space. The above table lists the addresses of the identifier words.

**Important:** For applications that require verified unique identification, contact your Microchip Technology sales office to create a Serialized Quick Turn Programming option.

# 5.2 External Unique Identifier (EUI)

The EUI data is stored at locations 810Ah to 8111h in the program memory region. This region is an optional space for placing application specific information. The data is coded per customer requirements during manufacturing. The EUI cannot be erased by a Bulk Erase command.

**Important:** Data is stored in this address range on receiving a request from the customer. The customer may contact the local sales representative or Field Applications Engineer, and provide them the unique identifier information that is required to be stored in this region.

# 7.8.12 STKPTR

Name:STKPTRAddress:0xFED

Stack Pointer Register

| Bit    | 7 | 6 | 5 | 4   | 3   | 2           | 1   | 0   |

|--------|---|---|---|-----|-----|-------------|-----|-----|

|        |   |   |   |     |     | STKPTR[4:0] |     |     |

| Access |   |   |   | R/W | R/W | R/W         | R/W | R/W |

| Reset  |   |   |   | 0   | 0   | 0           | 0   | 0   |

Bits 4:0 - STKPTR[4:0] Stack Pointer Location bits

### 9.2.2 Internal Clock Sources

The device may be configured to use the internal oscillator block as the system clock by performing one of the following actions:

- Program the RSTOSC bits in Configuration Words to select the INTOSC clock source, which will be used as the default system clock upon a device Reset.

- Write the NOSC bits to switch the system clock source to the internal oscillator during run-time.

In INTOSC mode, OSC1/CLKIN is available for general purpose I/O. OSC2/CLKOUT is available for general purpose I/O or CLKOUT.

The function of the OSC2/CLKOUT pin is determined by the CLKOUTEN bit in Configuration Words.

The internal oscillator block has two independent oscillators that can produce two internal system clock sources.

- 1. The **HFINTOSC** (High-Frequency Internal Oscillator) is factory-calibrated and operates up to 32 MHz. The frequency of HFINTOSC can be selected through the OSCFRQ Frequency Selection register, and fine-tuning can be done via the OSCTUNE register.

- 2. The LFINTOSC (Low-Frequency Internal Oscillator) is factory-calibrated and operates at 31 kHz.

#### **Related Links**

#### **Clock Switching**

## 9.2.2.1 HFINTOSC

The High-Frequency Internal Oscillator (HFINTOSC) is a precision digitally-controlled internal clock source that produces a stable clock up to 32 MHz. The HFINTOSC can be enabled through one of the following methods:

- Programming the RSTOSC bits in Configuration Word 1 to '110' (F<sub>OSC</sub> = 1 MHz) or '000' (F<sub>OSC</sub> = 32 MHz) to set the oscillator upon device Power-up or Reset.

- Write to the NOSC bits during run-time.

The HFINTOSC frequency can be selected by setting the HFFRQ bits.

The NDIV bits allow for division of the HFINTOSC output from a range between 1:1 and 1:512.

Related Links Clock Switching OSCCON1 OSCFRO

#### 9.2.2.2 MFINTOSC

The module provides two (500 kHz and 31.25 kHz) constant clock outputs. These clocks are digital divisors of the HFINTOSC clock. Dynamic divider logic is used to provide constant MFINTOSC clock rates for all settings of HFINTOSC.

The MFINTOSC cannot be used to drive the system but it is used to clock certain modules such as the Timers and WWDT.

#### 9.2.2.3 2x PLL

The oscillator module contains a PLL that can be used with the HFINTOSC clock source to provide a system clock source. The input frequency to the PLL is limited to 8, 12, or 16 MHz, which will yield a system clock source of 16, 24, or 32 MHz, respectively.

# (WWDT) Windowed Watchdog Timer

| Conditions                                              | WWDT                         |

|---------------------------------------------------------|------------------------------|

| WDTE = 10 and enter Sleep                               |                              |

| CLRWDT Command                                          |                              |

| Oscillator Fail Detected                                |                              |

| Exit Sleep + System Clock = SOSC, EXTRC, INTOSC, EXTCLK |                              |

| Exit Sleep + System Clock = XT, HS, LP                  | Cleared until the end of OST |

| Change INTOSC divider (IRCF bits)                       | Unaffected                   |

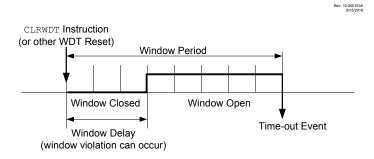

# Figure 12-2. Window Period and Delay

#### **Related Links**

Oscillator Start-up Timer (OST) STATUS PCON0 Memory Organization

# (PPS) Peripheral Pin Select Module

| Input Signal         | Input Pagiator         | Default loca         | tion at POR       | Reset Value (xxxPPS<4:0>) |                   |  |

|----------------------|------------------------|----------------------|-------------------|---------------------------|-------------------|--|

| Input Signal<br>Name | Input Register<br>Name | 14/16-pin<br>devices | 20-pin<br>devices | 14/16-pin<br>devices      | 20-pin<br>devices |  |

| SS1                  | SS1PPS                 | RC3                  | RC6               | 10011                     | 10110             |  |

| SCK2                 | SCL2PPS                | RC4                  | RB7               | 10100                     | 01111             |  |

| SCL2                 | SCL2PPS                | RC4                  | RB7               | 10100                     | 01111             |  |

| SDI2                 | SDA2PPS                | RC5                  | RB5               | 10101                     | 01101             |  |

| SDA2                 | SDA2PPS                | RC5                  | RB5               | 10101                     | 01101             |  |

| SS2                  | SS2PPS                 | RA0                  | RA1               | 00000                     | 00001             |  |

| RX1                  | RX1PPS                 | RC5                  | RB5               | 10101                     | 01101             |  |

| DT1 <sup>(1)</sup>   | RX1PPS                 | RC5                  | RB5               | 10101                     | 01101             |  |

| CK1 <sup>(1)</sup>   | CK1PPS                 | RC4                  | RB7               | 10100                     | 01111             |  |

| SMT1SIG              | SMT1SIGPPS             | RC0                  | RC0               | 10000                     | 10000             |  |

| SMT1WIN              | SMT1WINPPS             | RA5                  | RA5               | 00100                     | 00100             |  |

| Noto:                |                        |                      |                   |                           |                   |  |

#### Note:

1. DT1 and CK1 are bidirectional signals used in EUSART synchronous mode.

# 15.2 PPS Outputs

Each I/O pin has an RxyPPS register with which the pin output source is selected. With few exceptions, the port TRIS control associated with that pin retains control over the pin output driver. Peripherals that control the pin output driver as part of the peripheral operation will override the TRIS control as needed. These peripherals include:

- EUSART (synchronous operation)

- MSSP (I<sup>2</sup>C)

Although every pin has its own RxyPPS peripheral selection register, the selections are identical for every pin as shown in the following table.

**Important:** The notation "Rxy" is a place holder for the pin identifier. The 'x' holds the place of the PORT letter and the 'y' holds the place of the bit number. For example, Rxy = RA0 for the RA0PPS register.

## Table 15-2. PPS Output Signal Routing Options

| Output Signal Name | RxyPPS Register Value |

|--------------------|-----------------------|

| ADCGRDA            | 0x1F                  |

| ADCGRDB            | 0x20                  |

| C10UT              | 0x11                  |

# 16. (PMD) Peripheral Module Disable

This module provides the ability to selectively enable or disable a peripheral. Disabling a peripheral places it in its lowest possible power state. The user can disable unused modules to reduce the overall power consumption.

The PIC16(L)F18426/46 devices address this requirement by allowing peripheral modules to be selectively enabled or disabled. Disabling a peripheral places it in the lowest possible power mode.

Important: All modules are ON by default following any system Reset.

# 16.1 Disabling a Module

A peripheral can be disabled by setting the corresponding peripheral disable bit in the PMDx register. Disabling a module has the following effects:

- The module is held in Reset and does not function.

- All the SFRs pertaining to that peripheral become "unimplemented"

- Writing is disabled

- Reading returns 0x00

- Module outputs are disabled

## **Related Links**

PPSLOCK

# 16.2 Enabling a Module

Clearing the corresponding module disable bit in the PMDx register, re-enables the module and the SFRs will reflect the Power-on Reset values.

**Important:** There should be no reads/writes to the module SFRs for at least two instruction cycles after it has been re-enabled.

# 16.3 System Clock Disable

Setting SYSCMD disables the system clock (F<sub>OSC</sub>) distribution network to the peripherals. Not all peripherals make use of SYSCLK, so not all peripherals are affected. Refer to the specific peripheral description to see if it will be affected by this bit.

## **Related Links**

PMD0

#### 16.5.1 PMD0

Name:PMD0Address:0x796

PMD Control Register 0

| Bit    | 7      | 6     | 5 | 4 | 3 | 2     | 1      | 0     |

|--------|--------|-------|---|---|---|-------|--------|-------|

|        | SYSCMD | FVRMD |   |   |   | NVMMD | CLKRMD | IOCMD |

| Access | R/W    | R/W   |   |   |   | R/W   | R/W    | R/W   |

| Reset  | 0      | 0     |   |   |   | 0     | 0      | 0     |

**Bit 7 – SYSCMD** Disable Peripheral System Clock Network bit Disables the System clock network

| Va | alue | Description                                       |

|----|------|---------------------------------------------------|

| 1  |      | System clock network disabled (F <sub>OSC</sub> ) |

| 0  |      | System clock network enabled                      |

# Bit 6 – FVRMD Disable Fixed Voltage Reference bit

| Value | Description         |

|-------|---------------------|

| 1     | FVR module disabled |

| 0     | FVR module enabled  |

**Bit 2 – NVMMD** NVM Module Disable bit<sup>(1)</sup> Disables the NVM module

| Value | Description                                                                         |

|-------|-------------------------------------------------------------------------------------|

| 1     | All Memory reading and writing is disabled; NVMCON registers cannot be written; FSR |

|       | access to these locations returns zero.                                             |

| 0     | NVM module enabled                                                                  |

#### Bit 1 – CLKRMD Disable Clock Reference bit

| Value | Description          |

|-------|----------------------|

| 1     | CLKR module disabled |

| 0     | CLKR module enabled  |

### Bit 0 – IOCMD Disable Interrupt-on-Change bit, All Ports

| Value | Description            |

|-------|------------------------|

| 1     | IOC module(s) disabled |

| 0     | IOC module(s) enabled  |

#### Note:

1. When enabling NVM, a delay of up to 1 µs may be required before accessing data.

# **Related Links**

System Clock Disable

- ADC Precharge Time

- Additional Sample and Hold Capacitor

- Single/Double Sample Conversion

- Guard Ring Outputs

## 20.1.1 Port Configuration

The ADC can be used to convert both analog and digital signals. When converting analog signals, the I/O pin should be configured for analog by setting the associated TRIS and ANSEL bits. Refer to the "I/O Ports" section for more information.

**Important:** Analog voltages on any pin that is defined as a digital input may cause the input buffer to conduct excess current.

#### **Related Links**

I/O Ports

### 20.1.2 Channel Selection

The ADPCH register determines which channel is connected to the sample and hold circuit.

When changing channels, a delay is required before starting the next conversion.

There are several channel selections available, as shown in the following table:

| РСН           | ADC Positive Channel Input       |

|---------------|----------------------------------|

| 111111        | Fixed Voltage Reference (FVR) 2  |

| 111110        | Fixed Voltage Reference (FVR) 1  |

| 111101        | DAC1 output                      |

| 111100        | Temperature Indicator            |

| 111011        | AV <sub>SS</sub> (Analog Ground) |

| 111010-011000 | Reserved. No channel connected.  |

| 010111        | RC7/ANC7                         |

| 010110        | RC6/ANC6                         |

| 010101        | RC5/ ANC5                        |

| 010100        | RC4/ ANC4                        |

| 010011        | RC3/ANC3                         |

| 010010        | RC2/ANC2                         |

| 010001        | RC1/ ANC1                        |

| 010000        | RC0/ANC0                         |

| 001111        | RB7/ANB7                         |

#### Table 20-1. ADC Positive Input Channel Selections

# 20.8.11 ADCAP

Name:ADCAPAddress:0x10E

ADC Additional Sample Capacitor Selection Register

| Bit    | 7 | 6 | 5 | 4   | 3   | 2        | 1   | 0   |

|--------|---|---|---|-----|-----|----------|-----|-----|

|        |   |   |   |     |     | CAP[4:0] |     |     |

| Access |   |   |   | R/W | R/W | R/W      | R/W | R/W |

| Reset  |   |   |   | 0   | 0   | 0        | 0   | 0   |

Bits 4:0 - CAP[4:0] ADC Additional Sample Capacitor Selection bits

| Value   | Description                                |

|---------|--------------------------------------------|

| 1 to 31 | Number of pF in the additional capacitance |

| 0       | No additional capacitance                  |

# 20.8.20 ADLTH

Name:ADLTHAddress:0x08C

ADC Lower Threshold Register

ADLTH and ADUTH are compared with ADERR to set the UTHR and LTHR bits. Depending on the setting of MD, an interrupt may be triggered by the results of this comparison.

| Bit    | 15  | 14  | 13  | 12   | 11     | 10  | 9   | 8   |

|--------|-----|-----|-----|------|--------|-----|-----|-----|

|        |     |     |     | LTHF | H[7:0] |     |     |     |

| Access | R/W | R/W | R/W | R/W  | R/W    | R/W | R/W | R/W |

| Reset  | 0   | 0   | 0   | 0    | 0      | 0   | 0   | 0   |

|        |     |     |     |      |        |     |     |     |

| Bit    | 7   | 6   | 5   | 4    | 3      | 2   | 1   | 0   |

|        |     |     |     | LTHI | _[7:0] |     |     |     |

| Access | R/W | R/W | R/W | R/W  | R/W    | R/W | R/W | R/W |

| Reset  | 0   | 0   | 0   | 0    | 0      | 0   | 0   | 0   |

Bits 15:8 – LTHH[7:0] ADC Lower Threshold MSB.

Bits 7:0 – LTHL[7:0] ADC Lower Threshold LSB.

# PIC16(L)F18426/46 (CWG) Complementary Waveform Generator Modul...

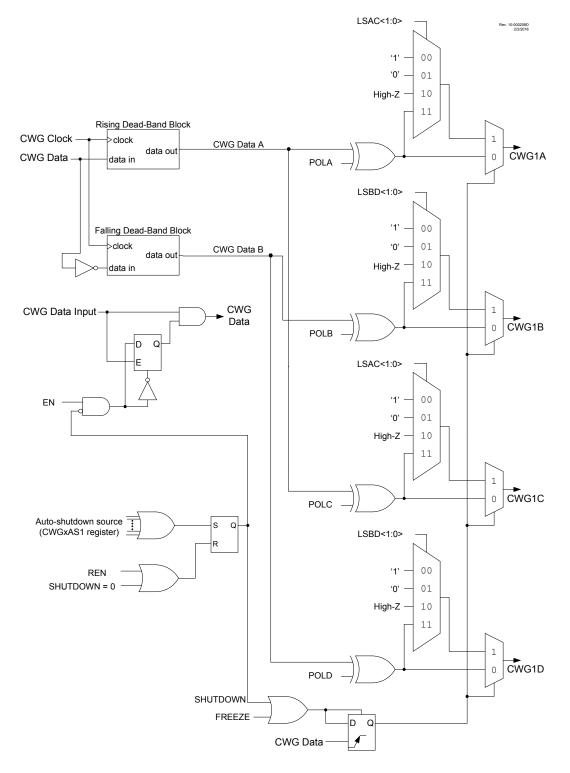

### Figure 31-2. Simplified CWG Block Diagram (Half-Bridge Mode, MODE<2:0> = 100)

# 31.2.2 Push-Pull Mode

In Push-Pull mode, two output signals are generated, alternating copies of the input as illustrated in Figure 31-3. This alternation creates the push-pull effect required for driving some transformer-based

# (DSM) Data Signal Modulator Module

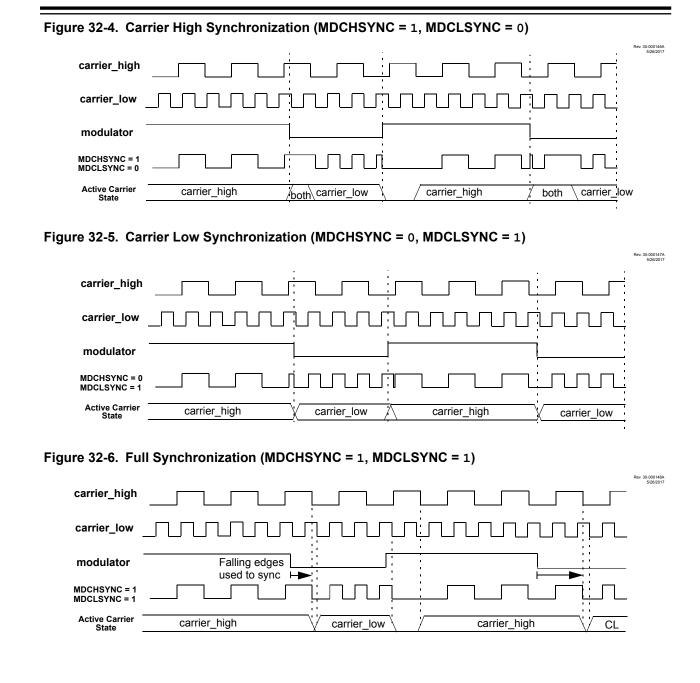

# 32.5 Carrier Source Polarity Select

The signal provided from any selected input source for the carrier high and carrier low signals can be inverted. Inverting the signal for the carrier high and low source is enabled by setting the CHPOL bit and the CLPOL bit, respectively.

# 32.6 Programmable Modulator Data

The BIT bit can be selected as the modulation source. This gives the user the ability to provide software driven modulation.

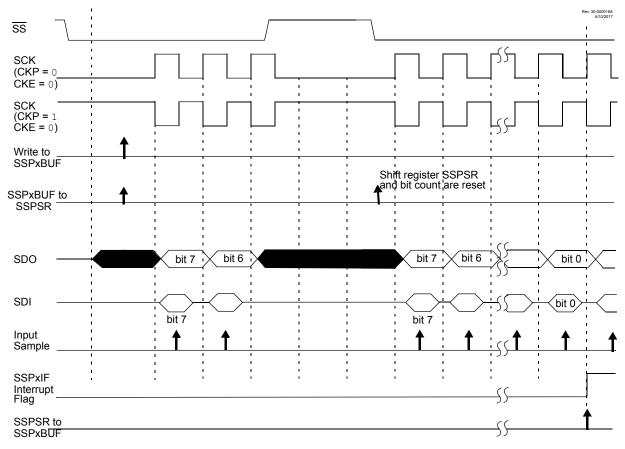

- 2. When the SPI is used in Slave mode with CKE set; the user must enable  $\overline{SS}$  pin control.

- 3. While operated in SPI Slave mode the SMP bit must remain clear.

When the SPI module resets, the bit counter is forced to '0'. This can be done by either forcing the  $\overline{SS}$  pin to a high level or clearing the SSPEN bit.

the Baud Rate Generator is turned off until another write to the SSPxBUF takes place, holding SCL low and allowing SDA to float.

#### 35.6.6.1 BF Status Flag

In Transmit mode, the BF bit is set when the CPU writes to SSPxBUF and is cleared when all eight bits are shifted out.

#### 35.6.6.2 WCOL Status Flag

If the user writes the SSPxBUF when a transmit is already in progress (i.e., SSPSR is still shifting out a data byte), the WCOL bit is set and the contents of the buffer are unchanged (the write does not occur).

The WCOL bit must be cleared by software before the next transmission.

#### 35.6.6.3 ACKSTAT Status Flag

In Transmit mode, the ACKSTAT bit is cleared when the slave has sent an Acknowledge ( $\overline{ACK} = 0$ ) and is set when the slave does not Acknowledge ( $\overline{ACK} = 1$ ). A slave sends an Acknowledge when it has recognized its address (including a general call), or when the slave has properly received its data.

#### 35.6.6.4 Typical transmit sequence:

- 1. The user generates a Start condition by setting the SEN bit.

- 2. SSPxIF is set by hardware on completion of the Start.

- 3. SSPxIF is cleared by software.

- 4. The MSSP module will wait the required start time before any other operation takes place.

- 5. The user loads the SSPxBUF with the slave address to transmit.

- 6. Address is shifted out the SDA pin until all eight bits are transmitted. Transmission begins as soon as SSPxBUF is written to.

- 7. The MSSP module shifts in the ACK bit from the slave device and writes its value into the ACKSTAT bit.

- 8. The MSSP module generates an interrupt at the end of the ninth clock cycle by setting the SSPxIF bit.

- 9. The user loads the SSPxBUF with eight bits of data.

- 10. Data is shifted out the SDA pin until all eight bits are transmitted.

- 11. The MSSP module shifts in the ACK bit from the slave device and writes its value into the ACKSTAT bit.

- 12. Steps 8-11 are repeated for all transmitted data bytes.

- 13. The user generates a Stop or Restart condition by setting the PEN or RSEN bits. Interrupt is generated once the Stop/Restart condition is complete.

# 35.9.1 SSPxSTAT

| Name:    | SSPxSTAT    |

|----------|-------------|

| Address: | 0x18F,0x199 |

**MSSP Status Register**

| Bit    | 7   | 6   | 5   | 4  | 3  | 2   | 1  | 0  |

|--------|-----|-----|-----|----|----|-----|----|----|

|        | SMP | CKE | D/A | Р  | S  | R/W | UA | BF |

| Access | R/W | R/W | RO  | RO | RO | RO  | RO | RO |

| Reset  | 0   | 0   | 0   | 0  | 0  | 0   | 0  | 0  |

Bit 7 – SMP Slew Rate Control bit

| Value | Mode             | Description                                                               |

|-------|------------------|---------------------------------------------------------------------------|

| 1     | SPI Master       | Input data is sampled at the end of data output time                      |

| 0     | SPI Master       | Input data is sampled at the middle of data output time                   |

| 0     | SPI Slave        | Keep this bit cleared in SPI Slave mode                                   |

| 1     | l <sup>2</sup> C | Slew rate control is disabled for Standard Speed mode (100 kHz and 1 MHz) |

| 0     | l <sup>2</sup> C | Slew rate control is enabled for High-Speed mode (400 kHz)                |

# Bit 6 – CKE

SPI: Clock select bit<sup>(4)</sup> I<sup>2</sup>C: SMBus Select bit

| Value | Mode             | Description                                                       |

|-------|------------------|-------------------------------------------------------------------|

| 1     | SPI              | Transmit occurs on the transition from active to Idle clock state |

| 0     | SPI              | Transmit occurs on the transition from Idle to active clock state |

| 1     | I <sup>2</sup> C | Enables SMBus-specific inputs                                     |

| 0     | I <sup>2</sup> C | Disables SMBus-specific inputs                                    |

# Bit 5 – D/Ā

Data/Address bit

| Value | Mode                           | Description                                                      |

|-------|--------------------------------|------------------------------------------------------------------|

| Х     | SPI or I <sup>2</sup> C Master | Reserved                                                         |

| 1     | I <sup>2</sup> C Slave         | Indicates that the last byte received or transmitted was data    |

| 0     | I <sup>2</sup> C Slave         | Indicates that the last byte received or transmitted was address |

# Bit 4 – P

Stop bit<sup>(1)</sup>

| Value | Mode             | Description                    |

|-------|------------------|--------------------------------|

| Х     | SPI              | Reserved                       |

| 1     | I <sup>2</sup> C | Stop bit was detected last     |

| 0     | l <sup>2</sup> C | Stop bit was not detected last |

## Bit 3 – S

Start bit(1)

# (MSSP) Master Synchronous Serial Port Module

| Value | Description                                                                       |

|-------|-----------------------------------------------------------------------------------|

| 1     | Initiates Stop condition on SDAx and SCLx pins; automatically cleared by hardware |

| 0     | Stop condition is Idle                                                            |

#### Bit 1 – RSEN

Repeated Start Condition Enable bit (Master mode only)<sup>(2)</sup>

| Value | Description                                                                        |

|-------|------------------------------------------------------------------------------------|

| 1     | Initiates Repeated Start condition on SDAx and SCLx pins; automatically cleared by |

|       | hardware                                                                           |

| 0     | Repeated Start condition is Idle                                                   |

# Bit 0 – SEN

Start Condition Enable bit (Master mode only)<sup>(2)</sup>

| Value | Description                                                                        |

|-------|------------------------------------------------------------------------------------|

| 1     | Initiates Start condition on SDAx and SCLx pins; automatically cleared by hardware |

| 0     | Start condition is Idle                                                            |

## Note:

- 1. The value that will be transmitted when the user initiates an Acknowledge sequence at the end of a receive.

- 2. If the I<sup>2</sup>C module is active, these bits may not be set (no spooling) and the SSPxBUF may not be written (or writes to the SSPxBUF are disabled).

# PIC16(L)F18426/46 (EUSART) Enhanced Universal Synchronous Asyn...

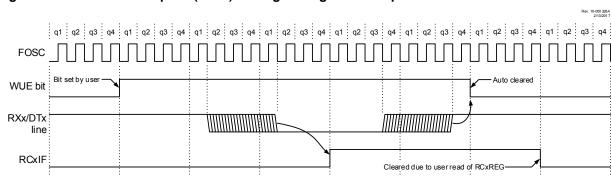

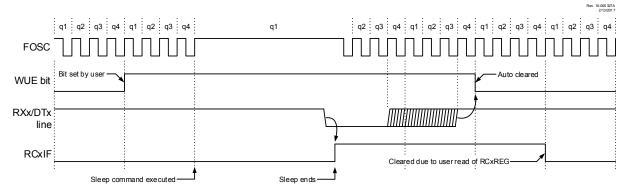

Note 1: The EUSART remains in idle while the WUE bit is set.

# Figure 36-9. Auto-Wake-up Bit (WUE) Timings During Sleep

Note 1: The EUSART remains in idle while the WUE bit is set.

# 36.2.4 Break Character Sequence

The EUSART module has the capability of sending the special Break character sequences that are required by the LIN bus standard. A Break character consists of a Start bit, followed by 12 '0' bits and a Stop bit.

To send a Break character, set the SENDB and TXEN bits of the TXxSTA register. The Break character transmission is then initiated by a write to the TXxREG. The value of data written to TXxREG will be ignored and all '0's will be transmitted.

The SENDB bit is automatically reset by hardware after the corresponding Stop bit is sent. This allows the user to preload the transmit FIFO with the next transmit byte following the Break character (typically, the Sync character in the LIN specification).

The TRMT bit of the TXxSTA register indicates when the transmit operation is active or idle, just as it does during normal transmission. See Figure 36-10 for more detail.

# 36.2.4.1 Break and Sync Transmit Sequence

The following sequence will start a message frame header made up of a Break, followed by an auto-baud Sync byte. This sequence is typical of a LIN bus master.

- 1. Configure the EUSART for the desired mode.

- 2. Set the TXEN and SENDB bits to enable the Break sequence.

- 3. Load the TXxREG with a dummy character to initiate transmission (the value is ignored).

# **Electrical Specifications**

| Param    | Sym.                | Characteristic            | Min. |                     | Max.   | Units | Conditions          |

|----------|---------------------|---------------------------|------|---------------------|--------|-------|---------------------|

| No.      | Sym.                |                           |      | Тур. †              | IVIAX. | Units | Conditions          |

| ECL Osc  | illator             |                           |      |                     |        |       |                     |

| OS1      | F <sub>ECL</sub>    | Clock Frequency           |      | —                   | 500    | kHz   |                     |

| OS2      | T <sub>ECL_DC</sub> | Clock Duty Cycle          | 40   | —                   | 60     | %     |                     |

| ECM Osc  | illator             |                           | 1    | 1                   | 1      |       |                     |

| OS3      | F <sub>ECM</sub>    | Clock Frequency           |      | _                   | 4      | MHz   |                     |

| OS4      | T <sub>ECM_DC</sub> | Clock Duty Cycle          | 40   | _                   | 60     | %     |                     |

| ECH Osc  | illator             |                           |      |                     |        |       |                     |

| OS5      | F <sub>ECH</sub>    | Clock Frequency           |      | _                   | 32     | MHz   |                     |

| OS6      | T <sub>ECH_DC</sub> | Clock Duty Cycle          | 40   | _                   | 60     | %     |                     |

| LP Oscil | ator                |                           | 1    | 1                   | 1      |       |                     |

| OS7      | F <sub>LP</sub>     | Clock Frequency           |      | _                   | 100    | kHz   | Note 4              |

| XT Oscil | ator                |                           | 1    |                     | 1      |       |                     |

| OS8      | F <sub>XT</sub>     | Clock Frequency           |      | _                   | 4      | MHz   | Note 4              |

| HS Oscil | lator               |                           | 1    |                     | 1      |       |                     |

| OS9      | F <sub>HS</sub>     | Clock Frequency           |      | _                   | 20     | MHz   | Note 4              |

| Seconda  | ry Oscillator       | •                         | 1    |                     | 1      |       |                     |

| OS10     | F <sub>SEC</sub>    | Clock Frequency           | 32.4 | 32.768              | 33.1   | kHz   | Note 4              |

| System ( | Dscillator          |                           |      |                     |        |       |                     |

| OS20     | F <sub>OSC</sub>    | System Clock<br>Frequency |      |                     | 32     | MHz   | (Note 2, Note<br>3) |

| OS21     | F <sub>CY</sub>     | Instruction<br>Frequency  | —    | F <sub>OSC</sub> /4 | _      | MHz   |                     |

| OS22     | T <sub>CY</sub>     | Instruction Period        | 125  | 1/F <sub>CY</sub>   | _      | ns    |                     |

Table 42-7.

\* These parameters are characterized but not tested.

† - Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note:

Instruction cycle period (T<sub>CY</sub>) equals four times the input oscillator time base period. All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices

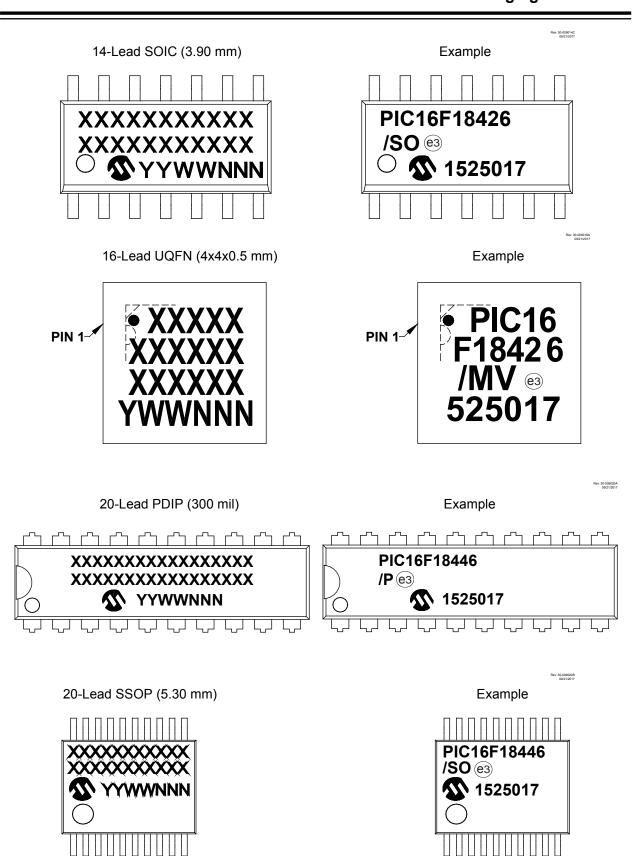

# PIC16(L)F18426/46 Packaging Information

# **Packaging Information**

# 14-Lead Plastic Thin Shrink Small Outline (ST) - 4.4 mm Body [TSSOP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-087C Sheet 1 of 2