Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 32MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 18                                                                          |

| Program Memory Size        | 28KB (16K x 14)                                                             |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 256 x 8                                                                     |

| RAM Size                   | 2K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 17x12b; D/A 1x5b                                                        |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 20-UFQFN Exposed Pad                                                        |

| Supplier Device Package    | 20-UQFN (4x4)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf18446-i-gz |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 3.2 16-Level Stack with Overflow and Underflow

These devices have a hardware stack memory 15 bits wide and 16 words deep. A Stack Overflow or Underflow will set the appropriate bit (STKOVF or STKUNF) in the PCON0 register, and if enabled, will cause a software Reset.

Related Links Stack PCON0

# 3.3 File Select Registers

There are two 16-bit File Select Registers (FSR). FSRs can access all file registers and program memory, which allows one Data Pointer for all memory. When an FSR points to program memory, there is one additional instruction cycle in instructions using INDF to allow the data to be fetched. General purpose memory can also be addressed linearly, providing the ability to access contiguous data larger than 80 bytes.

#### **Related Links**

Indirect Addressing

# 3.4 Instruction Set

There are 50 instructions for the enhanced mid-range CPU to support the features of the CPU.

#### Related Links

Instruction Set Summary

*Device ID, EEPROM, and Configuration Words*" section for more information on accessing these memory locations. For more information on checksum calculation, see the *"PIC16(L)F184XX Memory Programming Specification"*, (DS40001970).

#### **Related Links**

NVMREG Access to Device Information Area, Device Configuration Area, User ID, Device ID, EEPROM, and Configuration Words

### 4.5 Device ID and Revision ID

The 14-bit device ID word is located at 0x8006 and the 14-bit revision ID is located at 0x8005. These locations are read-only and cannot be erased or modified.

Development tools, such as device programmers and debuggers, may be used to read the Device ID, Revision ID and Configuration Words. Refer to the *"Nonvolatile Memory (NVM) Control"* section for more information on accessing these locations.

#### **Related Links**

(NVM) Nonvolatile Memory Control

# 4.6 Register Summary - Configuration Words

| Offset  | Name    | Bit Pos. |        |     |             |             |         |             |              |          |

|---------|---------|----------|--------|-----|-------------|-------------|---------|-------------|--------------|----------|

| 0x8007  | CONFIG1 | 7:0      |        |     | RSTOSC[2:0] |             |         |             | FEXTOSC[2:0] | J        |

| 0x8007  | CONFIGI | 13:8     |        |     | FCMEN       |             | CSWEN   |             |              | CLKOUTEN |

| 0x8008  | CONFIG2 | 7:0      | BOF    | REN | LPBOREN     |             |         | PWR         | FS[1:0]      | MCLRE    |

| 0x0000  | CONFIG2 | 13:8     |        |     | DEBUG       | STVREN      | PPS1WAY | ZCDDIS      | BORV         |          |

| 0x8009  | CONFIG3 | 7:0      |        | WDT | E[1:0]      |             |         | WDTCPS[4:0] |              |          |

| 0x8009  | CONFIGS | 13:8     |        |     |             | WDTCCS[2:0] |         |             | WDTCWS[2:0]  | I        |

| 0x800A  | CONFIG4 | 7:0      | WRTAPP |     |             | SAFEN       | BBEN    |             | BBSIZE[2:0]  |          |

| UXOUUA  | CONFIG4 | 13:8     |        |     | LVP         |             | WRTSAF  | WRTD        | WRTC         | WRTB     |

| 0x800B  | CONFIG5 | 7:0      |        |     |             |             |         |             |              | CP       |

| UNCOULD | CONFIGS | 13:8     |        |     |             |             |         |             |              |          |

# 4.7 Register Definitions: Configuration Words

#### 7.8.1 INDF0

Name: INDF0 Address: 0x00 + n\*0x80 [n=0..63]

Indirect Data Register. This is a virtual register. The GPR/SFR register addressed by the FSR0 register is the target for all operations involving the INDF0 register.

| Bit    | 7   | 6   | 5   | 4    | 3      | 2   | 1   | 0   |

|--------|-----|-----|-----|------|--------|-----|-----|-----|

|        |     |     |     | INDF | 0[7:0] |     |     |     |

| Access | R/W | R/W | R/W | R/W  | R/W    | R/W | R/W | R/W |

| Reset  | 0   | 0   | 0   | 0    | 0      | 0   | 0   | 0   |

Bits 7:0 – INDF0[7:0] Indirect data pointed to by the FSR0 register Related Links Core Registers

**Important:** An internal Reset event (RESET instruction, BOR, WWDT, POR, STKOVF, STKUNF) does not drive the MCLR pin low.

#### **Related Links**

Master Clear (MCLR) Pin

#### 8.4.2 MCLR Disabled

When MCLR is disabled, the MCLR becomes input-only and pin functions such as internal weak pull-ups are under software control.

#### **Related Links**

I/O Priorities

# 8.5 Windowed Watchdog Timer (WWDT) Reset

The Windowed Watchdog Timer generates a Reset if the firmware does not issue a CLRWDT instruction within the time-out period or window set. The  $\overline{TO}$  and  $\overline{PD}$  bits in the STATUS register and the  $\overline{RWDT}$  bit are changed to indicate a WDT Reset. The  $\overline{WDTWV}$  bit indicates if the WDT Reset has occurred due to a timeout or a window violation.

#### **Related Links**

STATUS (WWDT) Windowed Watchdog Timer

#### 8.6 RESET Instruction

A RESET instruction will cause a device Reset. The RI bit will be set to '0'. See *"Reset Condition for Special Registers"* table for default conditions after a RESET instruction has occurred.

#### 8.7 Stack Overflow/Underflow Reset

The device can reset when the Stack Overflows or Underflows. The STKOVF or STKUNF bits register indicate the Reset condition. These Resets are enabled by setting the STVREN bit in Configuration Words.

#### **Related Links**

CONFIG2 Overflow/Underflow Reset

# 8.8 Programming Mode Exit

Upon exit of Programming mode, the device will behave as if a POR had just occurred.

# 8.9 Power-up Timer (PWRT)

The Power-up Timer optionally delays device execution after a BOR or POR event. This timer is typically used to allow  $V_{DD}$  to stabilize before allowing the device to start running.

# 13.5 Register Summary: NVM Control

| Offset | Name     | Bit Pos. |                                    |  |      |          |          |  |  |

|--------|----------|----------|------------------------------------|--|------|----------|----------|--|--|

| 0x081A | NVMADR   | 7:0      | NVMADRL[7:0]                       |  |      |          |          |  |  |

| 02001A | INVINADR | 15:8     | NVMADRH[6:0]                       |  |      |          |          |  |  |

| 0x081C | NVMDAT   | 7:0      |                                    |  | NVMD | ATL[7:0] |          |  |  |

| 000010 | NVINDAT  | 15:8     |                                    |  |      | NVMDA    | ATH[5:0] |  |  |

| 0x081E | NVMCON1  | 7:0      | NVMREGS LWLO FREE WRERR WREN WR RD |  |      |          |          |  |  |

| 0x081F | NVMCON2  | 7:0      | NVMCON2[7:0]                       |  |      |          |          |  |  |

# 13.6 Register Definitions: Nonvolatile Memory

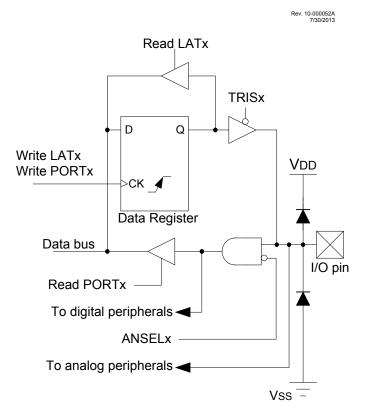

#### Figure 14-1. Generic I/O Port Operation

#### 14.3 I/O Priorities

Each pin defaults to the PORT data latch after Reset. Other functions are selected with the peripheral pin select logic. See *"Peripheral Pin Select (PPS) Module"* for more information.

Analog input functions, such as ADC and comparator inputs, are not shown in the peripheral pin select lists. These inputs are active when the I/O pin is set for Analog mode using the ANSELx register. Digital output functions may continue to control the pin when it is in Analog mode.

Analog outputs, when enabled, take priority over digital outputs and force the digital output driver into a high-impedance state.

The pin function priorities are as follows:

- 1. Configuration bits

- 2. Analog outputs (disable the input buffers)

- 3. Analog inputs

- 4. Port inputs and outputs from PPS

#### **Related Links**

(PPS) Peripheral Pin Select Module

# 14.4 PORTx Registers

In this section the generic names such as PORTx, LATx, TRISx, etc. can be associated with PORTA, PORTB, PORTC, etc, depending on availability per device (see related link below).

#### 14.6.2 PORTB

Name: PORTB Address: 0x00D

PORTB Register

| Bit    | 7   | 6   | 5   | 4   | 3 | 2 | 1 | 0 |

|--------|-----|-----|-----|-----|---|---|---|---|

|        | RB7 | RB6 | RB5 | RB4 |   |   |   |   |

| Access | R/W | R/W | R/W | R/W |   |   |   |   |

| Reset  | х   | х   | х   | х   |   |   |   |   |

Bits 4, 5, 6, 7 - RBn Port I/O Value bits Reset States: POR/BOR = xxxx All Other Resets = uuuu

| Value | Description                   |

|-------|-------------------------------|

| 1     | Port pin is ≥ V <sub>IH</sub> |

| 0     | Port pin is ≤ V <sub>IL</sub> |

Note: Writes to PORTB are actually written to the corresponding LATB register.

Reads from PORTB register return actual I/O pin values.

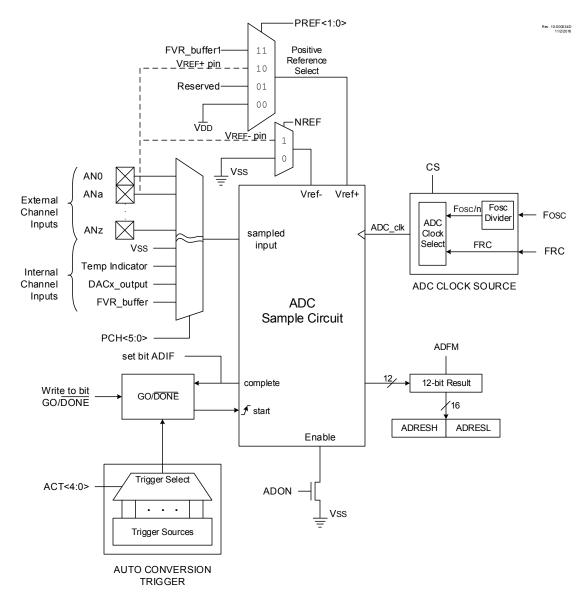

#### Figure 20-1. ADC<sup>2</sup> Block Diagram

# 20.1 ADC Configuration

When configuring and using the ADC the following functions must be considered:

- Port Configuration

- Channel Selection

- ADC Voltage Reference Selection

- ADC Conversion Clock Source

- Interrupt Control

- Result Formatting

- Conversion Trigger Selection

- ADC Acquisition Time

#### 20.8.17 ADACC

Name:ADACCAddress:0x096

#### ADC Accumulator Register

See Computation Modes for more details.

| Bit    | 23  | 22  | 21  | 20   | 19     | 18  | 17   | 16     |

|--------|-----|-----|-----|------|--------|-----|------|--------|

|        |     |     |     |      |        |     | ACCU | J[1:0] |

| Access |     |     |     |      |        |     | R/W  | R/W    |

| Reset  |     |     |     |      |        |     | x    | x      |

|        |     |     |     |      |        |     |      |        |

| Bit    | 15  | 14  | 13  | 12   | 11     | 10  | 9    | 8      |

|        |     |     |     | ACCH | H[7:0] |     |      |        |

| Access | R/W | R/W | R/W | R/W  | R/W    | R/W | R/W  | R/W    |

| Reset  | x   | x   | x   | х    | x      | x   | x    | x      |

|        |     |     |     |      |        |     |      |        |

| Bit    | 7   | 6   | 5   | 4    | 3      | 2   | 1    | 0      |

|        |     |     |     | ACCL | _[7:0] |     |      |        |

| Access | R/W | R/W | R/W | R/W  | R/W    | R/W | R/W  | R/W    |

| Reset  | х   | x   | x   | x    | x      | x   | х    | x      |

#### Bits 17:16 - ACCU[1:0]

ADC Accumulator MSB. Upper two bits of accumulator value.

#### Bits 15:8 – ACCH[7:0]

ADC Accumulator middle bits. Higher eight bits of accumulator value.

#### Bits 7:0 - ACCL[7:0]

ADC Accumulator LSB. Lower eight bits of accumulator value.

#### 20.8.22 ADACT

Name:ADACTAddress:0x117

ADC AUTO Conversion Trigger Source Selection Register

| Bit    | 7 | 6 | 5 | 4   | 3   | 2        | 1   | 0   |

|--------|---|---|---|-----|-----|----------|-----|-----|

|        |   |   |   |     |     | ACT[4:0] |     |     |

| Access |   |   |   | R/W | R/W | R/W      | R/W | R/W |

| Reset  |   |   |   | 0   | 0   | 0        | 0   | 0   |

Bits 4:0 - ACT[4:0] Auto-Conversion Trigger Select Bits

| Value    | Description                                    |

|----------|------------------------------------------------|

| 00000 to | See ADC Auto-Conversion Trigger Sources table. |

| 11111    |                                                |

#### 29.1.2 Open-Drain Output Option

When operating in Output mode (the Compare or PWM modes), the drivers for the CCPx pins can be optionally configured as open-drain outputs. This feature allows the voltage level on the pin to be pulled to a higher level through an external pull-up resistor and allows the output to communicate with external circuits without the need for additional level shifters.

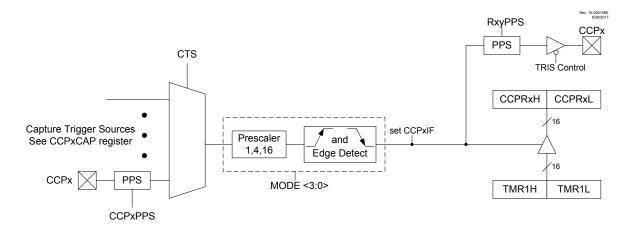

#### 29.2 Capture Mode

Capture mode makes use of the 16-bit odd numbered timer resources (Timer1, Timer3, etc.). When an event occurs on the capture source, the 16-bit CCPRx register captures and stores the 16-bit value of the TMRx register. An event is defined as one of the following and is configured by the MODE bits:

- Every falling edge of CCPx input

- Every rising edge of CCPx input

- Every 4<sup>th</sup> rising edge of CCPx input

- Every 16<sup>th</sup> rising edge of CCPx input

- Every edge of CCPx input (rising or falling)

When a capture is made, the Interrupt Request Flag bit CCPxIF of the PIRx register is set. The interrupt flag must be cleared in software. If another capture occurs before the value in the CCPRx register is read, the old captured value is overwritten by the new captured value.

**Important:** If an event occurs during a 2-byte read, the high and low-byte data will be from different events. It is recommended while reading the CCPRxH:CCPRxL register pair to either disable the module or read the register pair twice for data integrity.

The following figure shows a simplified diagram of the capture operation.

#### Figure 29-1. Capture Mode Operation Block Diagram

#### 29.2.1 Capture Sources

In Capture mode, the CCPx pin should be configured as an input by setting the associated TRIS control bit.

# 32. (DSM) Data Signal Modulator Module

The Data Signal Modulator (DSM) is a peripheral which allows the user to mix a data stream, also known as a modulator signal, with a carrier signal to produce a modulated output.

Both the carrier and the modulator signals are supplied to the DSM module either internally, from the output of a peripheral, or externally through an input pin.

The modulated output signal is generated by performing a logical "AND" operation of both the carrier and modulator signals and then provided to the MDOUT pin.

The carrier signal is comprised of two distinct and separate signals. A carrier high (CARH) signal and a carrier low (CARL) signal. During the time in which the modulator (MOD) signal is in a logic high state, the DSM mixes the carrier high signal with the modulator signal. When the modulator signal is in a logic low state, the DSM mixes the carrier low signal with the modulator signal.

Using this method, the DSM can generate the following types of Key Modulation schemes:

- Frequency-Shift Keying (FSK)

- Phase-Shift Keying (PSK)

- On-Off Keying (OOK)

Additionally, the following features are provided within the DSM module:

- Carrier Synchronization

- Carrier Source Polarity Select

- Programmable Modulator Data

- Modulated Output Polarity Select

- Peripheral Module Disable, which provides the ability to place the DSM module in the lowest power consumption mode

The figure below shows a Simplified Block Diagram of the Data Signal Modulator peripheral.

#### 33.8.2 CLCxPOL

| Name:    | CLCxPOL                     |

|----------|-----------------------------|

| Address: | 0x1E11,0x1E1B,0x1E25,0x1E2F |

Signal Polarity Control Register

| Bit    | 7   | 6 | 5 | 4 | 3     | 2     | 1     | 0     |

|--------|-----|---|---|---|-------|-------|-------|-------|

|        | POL |   |   |   | G4POL | G3POL | G2POL | G1POL |

| Access | R/W | • |   |   | R/W   | R/W   | R/W   | R/W   |

| Reset  | 0   |   |   |   | x     | х     | x     | x     |

#### Bit 7 – POL

CLCxOUT Output Polarity Control bit

| Value | Description                                  |

|-------|----------------------------------------------|

| 1     | The output of the logic cell is inverted     |

| 0     | The output of the logic cell is not inverted |

Bits 0, 1, 2, 3 – GyPOL

Gate Output Polarity Control bit Reset States: Default = xxxx POR/BOR = x All Other Resets = u

| Value | Description                                                |  |  |

|-------|------------------------------------------------------------|--|--|

| 1     | The gate output is inverted when applied to the logic cell |  |  |

| 0     | he output of the gate is not inverted                      |  |  |

# 35. (MSSP) Master Synchronous Serial Port Module

The Master Synchronous Serial Port (MSSP) module is a serial interface useful for communicating with other peripheral or microcontroller devices. These peripheral devices may be serial EEPROMs, shift registers, display drivers, A/D converters, etc. The MSSP module can operate in one of two modes:

- Serial Peripheral Interface (SPI)

- Inter-Integrated Circuit (I<sup>2</sup>C)

The SPI interface supports the following modes and features:

- Master mode

- Slave mode

- Clock Parity

- Slave Select Synchronization (Slave mode only)

- Daisy-chain connection of slave devices

The I<sup>2</sup>C interface supports the following modes and features:

- Master mode

- Slave mode

- Byte NACKing (Slave mode)

- Limited multi-master support

- 7-bit and 10-bit addressing

- Start and Stop interrupts

- Interrupt masking

- Clock stretching

- Bus collision detection

- General call address matching

- Address masking

- Address Hold and Data Hold modes

- Selectable SDA hold times

# 35.1 SPI Mode Overview

The Serial Peripheral Interface (SPI) bus is a synchronous serial data communication bus that operates in Full-Duplex mode. Devices communicate in a master/slave environment where the master device initiates the communication. A slave device is controlled through a Chip Select known as Slave Select.

The SPI bus specifies four signal connections:

- Serial Clock (SCK)

- Serial Data Out (SDO)

- Serial Data In (SDI)

- Slave Select (SS)

The following figure shows the block diagram of the MSSP module when operating in SPI mode.

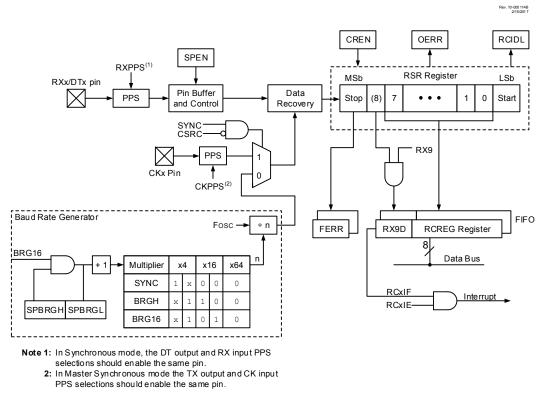

# 36.1 EUSART Asynchronous Mode

The EUSART transmits and receives data using the standard non-return-to-zero (NRZ) format. NRZ is implemented with two levels: a Voh Mark state which represents a '1' data bit, and a Vol Space state which represents a '0' data bit. NRZ refers to the fact that consecutively transmitted data bits of the same value stay at the output level of that bit without returning to a neutral level between each bit transmission. An NRZ transmission port idles in the Mark state. Each character transmission consists of one Start bit followed by eight or nine data bits and is always terminated by one or more Stop bits. The Start bit is always a space and the Stop bits are always marks. The most common data format is eight bits. Each transmitted bit persists for a period of 1/(Baud Rate). An on-chip dedicated 8-bit/16-bit Baud Rate Generator is used to derive standard baud rate frequencies from the system oscillator. See Table 36-2 for examples of baud rate configurations.

The EUSART transmits and receives the LSb first. The EUSART's transmitter and receiver are functionally independent, but share the same data format and baud rate. Parity is not supported by the hardware, but can be implemented in software and stored as the ninth data bit.

#### 36.1.1 EUSART Asynchronous Transmitter

The Figure 36-1 is a simplified representation of the transmitter. The heart of the transmitter is the serial Transmit Shift Register (TSR), which is not directly accessible by software. The TSR obtains its data from the transmit buffer, which is the TXxREG register.

#### 36.1.1.1 Enabling the Transmitter

The EUSART transmitter is enabled for asynchronous operations by configuring the following three control bits:

#### 36.1.2.6 Receiving 9-Bit Characters

The EUSART supports 9-bit character reception. When the RX9 bit of the RCxSTA register is set the EUSART will shift nine bits into the RSR for each character received. The RX9D bit of the RCxSTA register is the ninth and Most Significant data bit of the top unread character in the receive FIFO. When reading 9-bit data from the receive FIFO buffer, the RX9D data bit must be read before reading the eight Least Significant bits from the RCxREG.

#### 36.1.2.7 Address Detection

A special Address Detection mode is available for use when multiple receivers share the same transmission line, such as in RS-485 systems. Address detection is enabled by setting the ADDEN bit of the RCxSTA register.

Address detection requires 9-bit character reception. When address detection is enabled, only characters with the ninth data bit set will be transferred to the receive FIFO buffer, thereby setting the RCxIF interrupt bit. All other characters will be ignored.

Upon receiving an address character, user software determines if the address matches its own. Upon address match, user software must disable address detection by clearing the ADDEN bit before the next Stop bit occurs. When user software detects the end of the message, determined by the message protocol used, software places the receiver back into the Address Detection mode by setting the ADDEN bit.

#### 36.1.2.8 Asynchronous Reception Setup

- 1. Initialize the SPxBRGH:SPxBRGL register pair and the BRGH and BRG16 bits to achieve the desired baud rate (see the EUSART Baud Rate Generator (BRG) section).

- 2. Set the RXxPPS register to select the RXx/DTx input pin.

- 3. Clear the ANSEL bit for the RXx pin (if applicable).

- 4. Enable the serial port by setting the SPEN bit. The SYNC bit must be clear for asynchronous operation.

- 5. If interrupts are desired, set the RCxIE bit of the PIEx register and the GIE and PEIE bits of the INTCON register.

- 6. If 9-bit reception is desired, set the RX9 bit.

- 7. Enable reception by setting the CREN bit.

- 8. The RCxIF interrupt flag bit will be set when a character is transferred from the RSR to the receive buffer. An interrupt will be generated if the RCxIE interrupt enable bit was also set.

- 9. Read the RCxSTA register to get the error flags and, if 9-bit data reception is enabled, the ninth data bit.

- 10. Get the received eight Least Significant data bits from the receive buffer by reading the RCxREG register.

- 11. If an overrun occurred, clear the OERR flag by clearing the CREN receiver enable bit.

#### 36.1.2.9 9-Bit Address Detection Mode Setup

This mode would typically be used in RS-485 systems. To set up an Asynchronous Reception with Address Detect Enable follow these steps:

- 1. Initialize the SPxBRGH:SPxBRGL register pair and the BRGH and BRG16 bits to achieve the desired baud rate (see the EUSART Baud Rate Generator (BRG) section).

- 2. Set the RXxPPS register to select the RXx input pin.

- 3. Clear the ANSEL bit for the RXx pin (if applicable).

- 4. Enable the serial port by setting the SPEN bit. The SYNC bit must be clear for asynchronous operation.

#### 36.6.6 TXxREG

Name:TXxREGAddress:0x011A

Transmit Data Register

| Bit    | 7   | 6   | 5   | 4    | 3      | 2   | 1   | 0   |

|--------|-----|-----|-----|------|--------|-----|-----|-----|

|        |     |     |     | TXRE | G[7:0] |     |     |     |

| Access | R/W | R/W | R/W | R/W  | R/W    | R/W | R/W | R/W |

| Reset  | 0   | 0   | 0   | 0    | 0      | 0   | 0   | 0   |

Bits 7:0 - TXREG[7:0] Transmit Data

# PIC16(L)F18426/46

# Instruction Set Summary

| ΜΟνωι                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Move W to INDFn    |             |    |  |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-------------|----|--|--|--|--|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | $-32 \le k \le 31$ |             |    |  |  |  |  |

| Operation:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                    |             |    |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | None               |             |    |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | MODE               | SYNTAX      | mm |  |  |  |  |

| Status                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Preincrement       | ++FSRn      | 00 |  |  |  |  |

| Affected:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Predecrement       | FSRn        | 01 |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Postincrement      | FSRn++      | 10 |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Postdecrement      | FSRn        | 11 |  |  |  |  |

| Description:This instruction is used to move data between W and one of the indirect registers<br>(INDFn).<br>Before/after this move, the pointer (FSRn) is updated by pre/post incrementing/<br>decrementing it.<br>The INDFn registers are not physical registers.<br>Any instruction that accesses an INDFn register actually accesses the register at the<br>address specified by the FSRn.<br>FSRn is limited to the range 0000h-FFFFh.<br>Incrementing/decrementing it beyond these bounds will cause it to wrap-around.<br>The increment/decrement operation on FSRn WILL NOT affect any Status bits. |                    |             |    |  |  |  |  |

| NOP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | No (               | Operation   |    |  |  |  |  |

| Syntax:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                    | label 1 NOP |    |  |  |  |  |

| Syntax:          | [ label ] NOP |  |  |  |  |  |

|------------------|---------------|--|--|--|--|--|

| Operands:        | None          |  |  |  |  |  |

| Operation:       | No operation  |  |  |  |  |  |

| Status Affected: | None          |  |  |  |  |  |

| Description:     | No operation. |  |  |  |  |  |

| Words:           | 1             |  |  |  |  |  |

| Cycles:          | 1             |  |  |  |  |  |

# PIC16(L)F18426/46

# **Electrical Specifications**

| Param Sym. Characteristic Min. Typ. † Max. Units Cond |                     |                           |      |                     |        |       |                     |  |

|-------------------------------------------------------|---------------------|---------------------------|------|---------------------|--------|-------|---------------------|--|

| No.                                                   | Sym.                |                           |      | тур. Г              | IVIAX. | Units | Conditions          |  |

| ECL Osc                                               | illator             |                           |      |                     |        |       |                     |  |

| OS1                                                   | F <sub>ECL</sub>    | Clock Frequency           |      | —                   | 500    | kHz   |                     |  |

| OS2                                                   | T <sub>ECL_DC</sub> | Clock Duty Cycle          | 40   | —                   | 60     | %     |                     |  |

| ECM Osc                                               | illator             |                           | 1    | 1                   | 1      |       |                     |  |

| OS3                                                   | F <sub>ECM</sub>    | Clock Frequency           |      | _                   | 4      | MHz   |                     |  |

| OS4                                                   | T <sub>ECM_DC</sub> | Clock Duty Cycle          | 40   | _                   | 60     | %     |                     |  |

| ECH Osc                                               | illator             |                           |      |                     |        |       |                     |  |

| OS5                                                   | F <sub>ECH</sub>    | Clock Frequency           |      | _                   | 32     | MHz   |                     |  |

| OS6                                                   | T <sub>ECH_DC</sub> | Clock Duty Cycle          | 40   | _                   | 60     | %     |                     |  |

| LP Oscil                                              | ator                |                           | 1    | 1                   | 1      |       |                     |  |

| OS7                                                   | F <sub>LP</sub>     | Clock Frequency           |      | _                   | 100    | kHz   | Note 4              |  |

| XT Oscil                                              | ator                |                           | 1    | 1                   | 1      |       |                     |  |

| OS8                                                   | F <sub>XT</sub>     | Clock Frequency           |      | _                   | 4      | MHz   | Note 4              |  |

| HS Oscil                                              | lator               |                           | 1    | 1                   | 1      |       |                     |  |

| OS9                                                   | F <sub>HS</sub>     | Clock Frequency           |      | _                   | 20     | MHz   | Note 4              |  |

| Seconda                                               | ry Oscillator       | •                         | 1    | 1                   | 1      |       |                     |  |

| OS10                                                  | F <sub>SEC</sub>    | Clock Frequency           | 32.4 | 32.768              | 33.1   | kHz   | Note 4              |  |

| System Oscillator                                     |                     |                           |      |                     |        |       |                     |  |

| OS20                                                  | F <sub>OSC</sub>    | System Clock<br>Frequency |      |                     | 32     | MHz   | (Note 2, Note<br>3) |  |

| OS21                                                  | F <sub>CY</sub>     | Instruction<br>Frequency  | —    | F <sub>OSC</sub> /4 | _      | MHz   |                     |  |

| OS22                                                  | T <sub>CY</sub>     | Instruction Period        | 125  | 1/F <sub>CY</sub>   | _      | ns    |                     |  |

Table 42-7.

\* These parameters are characterized but not tested.

† - Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note:

Instruction cycle period (T<sub>CY</sub>) equals four times the input oscillator time base period. All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices

| Standard Operating Conditions (unless otherwise stated) |                     |                                                       |                      |                     |                                     |                  |                                                                   |

|---------------------------------------------------------|---------------------|-------------------------------------------------------|----------------------|---------------------|-------------------------------------|------------------|-------------------------------------------------------------------|

| Param No.                                               | Sym.                | Characteristic                                        | Min.                 | Тур. †              | Max.                                | Units            | Conditions                                                        |

| RST01*                                                  | T <sub>MCLR</sub>   | MCLR Pulse Width<br>Low to ensure Reset               | 2                    | —                   | —                                   | μs               |                                                                   |

| RST02*                                                  | T <sub>IOZ</sub>    | I/O high-impedance<br>from Reset<br>detection         | _                    |                     | 2                                   | μs               |                                                                   |

| RST03                                                   | T <sub>WDT</sub>    | Watchdog Timer<br>Time-out Period                     | _                    | 16                  | —                                   | ms               | 1:512 Prescaler                                                   |

| RST04*                                                  | T <sub>PWRT</sub>   | Power-up Timer<br>Period                              |                      | 65                  |                                     | ms               |                                                                   |

| RST05                                                   | T <sub>OST</sub>    | Oscillator Start-up<br>Timer Period <sup>(1, 2)</sup> |                      | 1024                | _                                   | T <sub>OSC</sub> |                                                                   |

| RST06                                                   | V <sub>BOR</sub>    | Brown-out Reset<br>Voltage                            | 2.55<br>2.30<br>1.80 | 2.7<br>2.45<br>1.90 | 2.85<br>2.60 <sup>(3)</sup><br>2.05 | V<br>V<br>V      | BORV=0<br>BORV=1(F<br>devices only)<br>BORV=1(LF<br>Devices only) |

| RST07                                                   | V <sub>BORHYS</sub> | Brown-out Reset<br>Hysteresis                         |                      | 40                  | —                                   | mV               |                                                                   |

| RST08                                                   | T <sub>BORDC</sub>  | Brown-out Reset<br>Response Time                      | —                    | 3                   | —                                   | μs               |                                                                   |

| RST09                                                   | V <sub>LPBOR</sub>  | Low-Power Brown-<br>out Reset Voltage                 | 1.8                  | 1.9                 | 2.2                                 | V                |                                                                   |

#### Table 42-11.

\* - These parameters are characterized but not tested.

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

#### Note:

- 1. By design, the Oscillator Start-up Timer (OST) counts the first 1024 cycles, independent of frequency.

- 2. To ensure these voltage tolerances,  $V_{DD}$  and  $V_{SS}$  must be capacitively decoupled as close to the device as possible. 0.1  $\mu$ F and 0.01  $\mu$ F values in parallel are recommended.

- 3. This value corresponds to V<sub>BORMAX</sub>