#### Microchip Technology - PIC16LF18446-I/P Datasheet

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 18                                                                         |

| Program Memory Size        | 28KB (16K x 14)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 2K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                |

| Data Converters            | A/D 17x12b; D/A 1x5b                                                       |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Through Hole                                                               |

| Package / Case             | 14-DIP (0.300", 7.62mm)                                                    |

| Supplier Device Package    | 14-PDIP                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf18446-i-p |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Device Configuration

| Value | Description                                                               |

|-------|---------------------------------------------------------------------------|

| 11    | WDT enabled regardless of Sleep; SEN is ignored                           |

| 10    | WDT enabled while Sleep = 0, suspended when Sleep = 1; SEN bit is ignored |

| 01    | WDT enabled/disabled by SEN bit                                           |

| 00    | WDT disabled, SEN bit is ignored                                          |

### Bits 4:0 - WDTCPS[4:0] WDT Period Select bits

|                    |                            | WDTCON0   | [WDTI                                                |        |                            |

|--------------------|----------------------------|-----------|------------------------------------------------------|--------|----------------------------|

| WDTCPS             | VDTCPS<br>Value Divider Ra |           | Ratio Typical Time Out<br>(F <sub>IN</sub> = 31 kHz) |        | Software Control of WDTPS? |

| 11111              | 01011                      | 1:65536   | 2 <sup>16</sup>                                      | 2s     | Yes                        |

| 11110<br><br>10011 | 11110<br><br>10011         | 1:32      | 2 <sup>5</sup>                                       | 1 ms   | No                         |

| 10010              | 10010                      | 1:8388608 | 2 <sup>23</sup>                                      | 256s   |                            |

| 10001              | 10001                      | 1:4194304 | 2 <sup>22</sup>                                      | 128s   |                            |

| 10000              | 10000                      | 1:2097152 | 2 <sup>21</sup>                                      | 64s    |                            |

| 01111              | 01111                      | 1:1048576 | 2 <sup>20</sup>                                      | 32s    |                            |

| 01110              | 01110                      | 1:524288  | 2 <sup>19</sup>                                      | 16s    |                            |

| 01101              | 01101                      | 1:262144  | 2 <sup>18</sup>                                      | 8s     |                            |

| 01100              | 01100                      | 1:131072  | 2 <sup>17</sup>                                      | 4s     |                            |

| 01011              | 01011                      | 1:65536   | 2 <sup>16</sup>                                      | 2s     |                            |

| 01010              | 01010                      | 1:32768   | 2 <sup>15</sup>                                      | 1s     |                            |

| 01001              | 01001                      | 1:16384   | 2 <sup>14</sup>                                      | 512 ms | No                         |

| 01000              | 01000                      | 1:8192    | 2 <sup>13</sup>                                      | 256 ms |                            |

| 00111              | 00111                      | 1:4096    | 2 <sup>12</sup>                                      | 128 ms |                            |

| 00110              | 00110                      | 1:2048    | 2 <sup>11</sup>                                      | 64 ms  |                            |

| 00101              | 00101                      | 1:1024    | 2 <sup>10</sup>                                      | 32 ms  |                            |

| 00100              | 00100                      | 1:512     | 2 <sup>9</sup>                                       | 16 ms  |                            |

| 00011              | 00011                      | 1:256     | 2 <sup>8</sup>                                       | 8 ms   |                            |

| 00010              | 00010                      | 1:128     | 2 <sup>7</sup>                                       | 4 ms   |                            |

| 00001              | 00001                      | 1:64      | 2 <sup>6</sup>                                       | 2 ms   |                            |

| 00000              | 00000                      | 1:32      | 2 <sup>5</sup>                                       | 1 ms   |                            |

## 6. Device Configuration Information

The Device Configuration Information (DCI) is a dedicated region in the Program Flash Memory mapped from 8200h to 821Fh. The data stored in the DCI memory is hard-coded into the device during manufacturing. Refer to the table below for the complete DCI table address and description. The DCI holds information about the device which is useful for programming and bootloader applications. These locations are read-only and cannot be erased or modified.

| ADDRESS | Name  | DESCRIPTION             | PIC16(L)F18426/46 | UNITS   |

|---------|-------|-------------------------|-------------------|---------|

| 8200h   | ERSIZ | Erase Row Size          | 32                | Words   |

| 8201h   | WLSIZ | Number of write latches | 32                | Latches |

| 8202h   | URSIZ | Number of User Rows     | 512               | Rows    |

| 8203h   | EESIZ | EE Data memory size     | 256               | Bytes   |

| 8204h   | PCNT  | Pin Count               | 14, 16, 20        | Pins    |

Table 6-1. Device Configuration Information for Devices

## 6.1 DIA and DCI Access

The DIA and DCI data are read-only and cannot be erased or modified. See section *"NVMREG Access to Device Information Area, Device Configuration Area, User ID, Device ID, EEPROM, and Configuration Words"* for more information on accessing these memory locations.

Development tools, such as device programmers and debuggers, may be used to read the DIA and DCI regions, similar to the Device ID and Revision ID.

#### **Related Links**

NVMREG Access to Device Information Area, Device Configuration Area, User ID, Device ID, EEPROM, and Configuration Words

# PIC16(L)F18426/46 Memory Organization

Rev. 10-000043A

memory left at any given time. The STKPTR always points at the currently used place on the stack. Therefore, a CALL or CALLW will increment the STKPTR and then write the PC, and a return will unload the PC value from the stack and then decrement the STKPTR.

Reference the following figures for examples of accessing the stack.

### Figure 7-4. Accessing the Stack Example 1

|           |        |        | 7/30/2013                                                                              |

|-----------|--------|--------|----------------------------------------------------------------------------------------|

|           | 1      |        |                                                                                        |

| TOSH:TOSL | 0x0F   |        | STKPTR = 0x1F (STVREN = 0)                                                             |

|           | 0x0E   |        |                                                                                        |

|           | 0x0D   |        |                                                                                        |

|           | 0x0C   |        |                                                                                        |

|           | 0x0B   |        | <ul> <li>Initial Stack Configuration:</li> </ul>                                       |

|           | 0x0A   |        |                                                                                        |

|           | 0x09   |        | After Reset, the stack is empty. The empty stack is initialized so the Stack           |

|           | 0x08   |        | Pointer is pointing at 0x1F. If the Stack                                              |

|           | 0x07   |        | Overflow/Underflow Reset is enabled, the<br>TOSH/TOSL register will return '0'. If the |

|           | 0x06   |        | Stack Overflow/Underflow Reset is                                                      |

|           | 0x05   |        | disabled, the TOSH/TOSL register will<br>return the contents of stack address          |

|           | 0x04   |        | 0x0F.                                                                                  |

|           | 0x03   |        |                                                                                        |

|           | 0x02   |        |                                                                                        |

|           | 0x01   |        |                                                                                        |

|           | 0x00   |        |                                                                                        |

| TOSH:TOSL | 0x1F   | 0x0000 | STKPTR = 0x1F (STVREN = 1)                                                             |

|           | $\lor$ | L      | $\square (31 \text{ VREN} - 1)$                                                        |

### 7.8.9 PCLATH

Name:

PCLATH

Address:

0x0A + n\*0x80 [n=0..63]

Program Counter Latches.

Write Buffer for the upper 7 bits of the Program Counter

| Bit    | 7 | 6           | 5   | 4   | 3   | 2   | 1   | 0   |  |

|--------|---|-------------|-----|-----|-----|-----|-----|-----|--|

| ĺ      |   | PCLATH[6:0] |     |     |     |     |     |     |  |

| Access |   | R/W         | R/W | R/W | R/W | R/W | R/W | R/W |  |

| Reset  |   | 0           | 0   | 0   | 0   | 0   | 0   | 0   |  |

Bits 6:0 – PCLATH[6:0] High PC Latch register Holding register for Program Counter bits <6:0> Related Links

**Core Registers**

#### 9.2.2 Internal Clock Sources

The device may be configured to use the internal oscillator block as the system clock by performing one of the following actions:

- Program the RSTOSC bits in Configuration Words to select the INTOSC clock source, which will be used as the default system clock upon a device Reset.

- Write the NOSC bits to switch the system clock source to the internal oscillator during run-time.

In INTOSC mode, OSC1/CLKIN is available for general purpose I/O. OSC2/CLKOUT is available for general purpose I/O or CLKOUT.

The function of the OSC2/CLKOUT pin is determined by the CLKOUTEN bit in Configuration Words.

The internal oscillator block has two independent oscillators that can produce two internal system clock sources.

- 1. The **HFINTOSC** (High-Frequency Internal Oscillator) is factory-calibrated and operates up to 32 MHz. The frequency of HFINTOSC can be selected through the OSCFRQ Frequency Selection register, and fine-tuning can be done via the OSCTUNE register.

- 2. The LFINTOSC (Low-Frequency Internal Oscillator) is factory-calibrated and operates at 31 kHz.

#### **Related Links**

#### **Clock Switching**

#### 9.2.2.1 HFINTOSC

The High-Frequency Internal Oscillator (HFINTOSC) is a precision digitally-controlled internal clock source that produces a stable clock up to 32 MHz. The HFINTOSC can be enabled through one of the following methods:

- Programming the RSTOSC bits in Configuration Word 1 to '110' (F<sub>OSC</sub> = 1 MHz) or '000' (F<sub>OSC</sub> = 32 MHz) to set the oscillator upon device Power-up or Reset.

- Write to the NOSC bits during run-time.

The HFINTOSC frequency can be selected by setting the HFFRQ bits.

The NDIV bits allow for division of the HFINTOSC output from a range between 1:1 and 1:512.

Related Links Clock Switching OSCCON1 OSCFRO

#### 9.2.2.2 MFINTOSC

The module provides two (500 kHz and 31.25 kHz) constant clock outputs. These clocks are digital divisors of the HFINTOSC clock. Dynamic divider logic is used to provide constant MFINTOSC clock rates for all settings of HFINTOSC.

The MFINTOSC cannot be used to drive the system but it is used to clock certain modules such as the Timers and WWDT.

#### 9.2.2.3 2x PLL

The oscillator module contains a PLL that can be used with the HFINTOSC clock source to provide a system clock source. The input frequency to the PLL is limited to 8, 12, or 16 MHz, which will yield a system clock source of 16, 24, or 32 MHz, respectively.

### 24.10 Register Summary: ZCD Control

| Offset | Name   | Bit Pos. |     |     |     |  |      |      |

|--------|--------|----------|-----|-----|-----|--|------|------|

| 0x091F | ZCDCON | 7:0      | SEN | OUT | POL |  | INTP | INTN |

### 24.11 Register Definitions: ZCD Control

Long bit name prefixes for the ZCD peripherals are shown in the table below. Refer to the "Long Bit Names Section" for more information.

#### Table 24-1. ZCD Long Bit Name Prefixes

| Peripheral | Bit Name Prefix |  |  |  |

|------------|-----------------|--|--|--|

| ZCD        | ZCD             |  |  |  |

#### **Related Links**

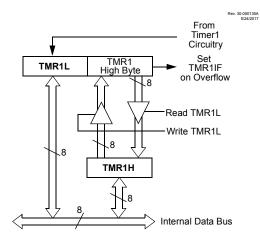

Long Bit Names Long Bit Names When a write request of the TMRxL register is requested, the TMRxH buffer register is simultaneously updated with the contents of the TMRxH register. The value of TMRxH must be preloaded into the TMRxH buffer register prior to the write request for the TMRxL register. This provides the user with the ability to write all 16 bits to the TMRxL:TMRxH register pair at the same time.

Any requests to write to the TMRxH directly does not clear the Timer1 prescaler value. The prescaler value is only cleared through write requests to the TMRxL register.

#### Figure 26-3. Timer1 16-Bit Read/Write Mode Block Diagram

### 26.7 Timer1 Gate

Timer1 can be configured to count freely or the count can be enabled and disabled using Timer1 gate circuitry. This is also referred to as Timer1 gate enable.

Timer1 gate can also be driven by multiple selectable sources.

#### 26.7.1 Timer1 Gate Enable

The Timer1 Gate Enable mode is enabled by setting the GE bit. The polarity of the Timer1 Gate Enable mode is configured using the GPOL bit.

When Timer1 Gate Enable mode is enabled, Timer1 will increment on the rising edge of the Timer1 clock source. When Timer1 Gate signal is inactive, the timer will not increment and hold the current count. Enable mode is disabled, no incrementing will occur and Timer1 will hold the current count. See figure below for timing details.

| TMRxCLK | GPOL | TxG | Timer1 Operation |

|---------|------|-----|------------------|

| 1       | 1    | 1   | Counts           |

| 1       | 1    | 0   | Holds Count      |

| 1       | 0    | 1   | Holds Count      |

| ↑       | 0    | 0   | Counts           |

#### Table 26-3. Timer1 Gate Enable Selections

Timer2 Module

|          | MODE  | E<4:0>                          | Output                            |                                                                   |                               | Timer Contro    | ol                             |  |  |

|----------|-------|---------------------------------|-----------------------------------|-------------------------------------------------------------------|-------------------------------|-----------------|--------------------------------|--|--|

| Mode     | <4:3> | <2:0>                           | Operation                         | Operation                                                         | Start                         | Reset           | Stop                           |  |  |

|          |       | 100                             |                                   | Rising edge<br>start and<br>Rising edge<br>Reset (Figure<br>27-9) | ON = 1 and<br>TMRx_ers ↑      | TMRx_ers<br>↑   |                                |  |  |

|          |       | 101                             | Edge<br>Triggered<br>Start<br>and | Falling edge<br>start and<br>Falling edge<br>Reset                | ON = 1 and<br>TMRx_ers ↓      | TMRx_ers<br>↓   |                                |  |  |

|          |       | 110                             | Hardware<br>Reset<br>(Note 1)     | Rising edge<br>start and<br>Low level<br>Reset (Figure<br>27-10)  | ON = 1 and<br>TMRx_ers ↑      | TMRx_ers<br>= 0 |                                |  |  |

|          |       | 111                             |                                   | Falling edge<br>start and<br>High level<br>Reset                  | ON = 1 and<br>TMRx_ers ↓      | TMRx_ers<br>= 1 |                                |  |  |

|          |       | 000                             |                                   |                                                                   | Reserved                      |                 |                                |  |  |

| Mono-    |       | 001                             | Edge<br>Triggered<br>) Start      | Rising edge<br>start<br>(Figure 27-11)                            | ON = 1 and<br>TMRx_ers ↑      |                 | ON = 0<br>or                   |  |  |

| stable   |       | 010                             |                                   | Falling edge<br>start                                             | ON = 1 and<br>TMRx_ers ↓      |                 | Next clock after<br>TMRx = PRx |  |  |

|          |       | 011                             | (Note 1)                          | Any edge<br>start                                                 | ON = 1 and<br>TMRx_ers        |                 | (Note 3)                       |  |  |

| Reserved | 10    | 100                             |                                   |                                                                   | Reserved                      | ·               |                                |  |  |

| Reserved |       | 101                             |                                   |                                                                   | Reserved                      |                 |                                |  |  |

| One-shot |       | Level<br>110 Triggered<br>Start | Triggered<br>Start                | High level<br>start and<br>Low level<br>Reset (Figure<br>27-12)   | ON = 1 and<br>TMRx_ers =<br>1 | TMRx_ers<br>= 0 | ON = 0 or<br>Held in Reset     |  |  |

|          |       | 111                             | and<br>Hardware<br>Reset          | Low level<br>start &<br>High level<br>Reset                       | ON = 1 and<br>TMRx_ers =<br>0 | TMRx_ers<br>= 1 | (Note 2)                       |  |  |

#### 33.8.5 CLCxSEL2

| Name:    | CLCxSEL2                    |

|----------|-----------------------------|

| Address: | 0x1E14,0x1E1E,0x1E28,0x1E32 |

Generic CLCx Data 1 Select Register

| Bit    | 7 | 6 | 5        | 4   | 3   | 2   | 1   | 0   |  |  |

|--------|---|---|----------|-----|-----|-----|-----|-----|--|--|

|        |   |   | D3S[5:0] |     |     |     |     |     |  |  |

| Access |   |   | R/W      | R/W | R/W | R/W | R/W | R/W |  |  |

| Reset  |   |   | x        | x   | x   | х   | х   | x   |  |  |

|        |   |   |          |     |     |     |     |     |  |  |

#### Bits 5:0 - D3S[5:0]

CLCx Data3 Input Selection bits Reset States: POR/BOR = xxxxx All Other Resets = uuuuuu

| Value | Description                                     |

|-------|-------------------------------------------------|

| n     | Refer to CLC Input Sources for input selections |

tev. 30-000012A 3/31/2017

### (MSSP) Master Synchronous Serial Port Module

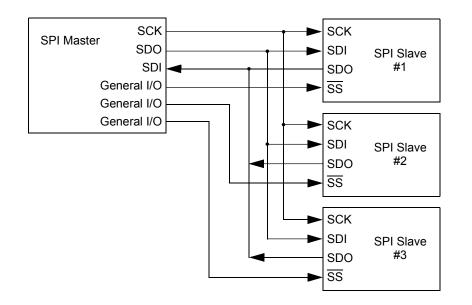

#### Figure 35-2. SPI Master and Multiple Slave Connection

#### 35.1.1 SPI Mode Registers

The MSSP module has five registers for SPI mode operation. These are:

- MSSP STATUS register (SSPxSTAT)

- MSSP Control register 1 (SSPxCON1)

- MSSP Control register 3 (SSPxCON3)

- MSSP Data Buffer register (SSPxBUF)

- MSSP Address register (SSPxADD)

- MSSP Shift register (SSPSR)

(Not directly accessible)

SSPxCON1 and SSPxSTAT are the control and STATUS registers for SPI mode operation. The SSPxCON1 register is readable and writable. The lower six bits of the SSPxSTAT are read-only. The upper two bits of the SSPxSTAT are read/write.

One of the five SPI master modes uses the SSPxADD value to determine the Baud Rate Generator clock frequency. More information on the Baud Rate Generator is available in Baud Rate Generator.

SSPSR is the shift register used for shifting data in and out. SSPxBUF provides indirect access to the SSPSR register. SSPxBUF is the buffer register to which data bytes are written, and from which data bytes are read.

In receive operations, SSPSR and SSPxBUF together create a buffered receiver. When SSPSR receives a complete byte, it is transferred to SSPxBUF and the SSPxIF interrupt is set.

During transmission, the SSPxBUF is not buffered. A write to SSPxBUF will write to both SSPxBUF and SSPSR.

#### 35.2 SPI Mode Operation

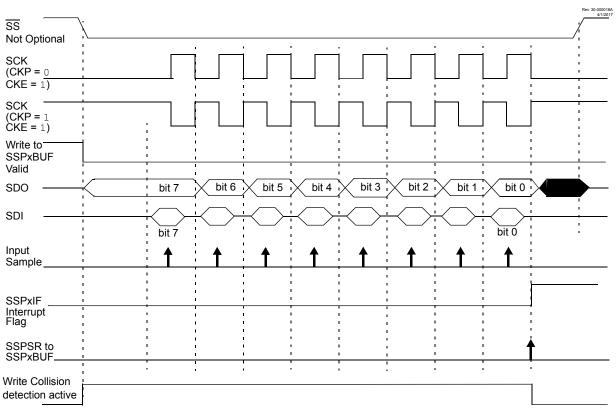

Transmissions involve two shift registers, eight bits in size, one in the master and one in the slave. With either the master or the slave device, data is always shifted out one bit at a time, with the Most Significant

(MSSP) Master Synchronous Serial Port Module

Figure 35-8. SPI Mode Waveform (Slave Mode with CKE = 1)

#### 35.2.5 SPI Operation in Sleep Mode

In SPI Master mode, module clocks may be operating at a different speed than when in Full-Power mode; in the case of the Sleep mode, all clocks are halted.

Special care must be taken by the user when the MSSP clock is much faster than the system clock.

In Slave mode, when MSSP interrupts are enabled, after the master completes sending data, an MSSP interrupt will wake the controller from Sleep.

If an exit from Sleep mode is not desired, MSSP interrupts should be disabled.

In SPI Master mode, when the Sleep mode is selected, all module clocks are halted and the transmission/reception will remain in that state until the device wakes. After the device returns to Run mode, the module will resume transmitting and receiving data.

In SPI Slave mode, the SPI Transmit/Receive Shift register operates asynchronously to the device. This allows the device to be placed in Sleep mode and data to be shifted into the SPI Transmit/Receive Shift register. When all eight bits have been received, the MSSP interrupt flag bit will be set and if enabled, will wake the device.

### 35.3 I<sup>2</sup>C Mode Overview

The Inter-Integrated Circuit (I<sup>2</sup>C) bus is a multi-master serial data communication bus. Devices communicate in a master/slave environment where the master devices initiate the communication. A

#### 35.4.2 Arbitration

Each master device must monitor the bus for Start and Stop bits. If the device detects that the bus is busy, it cannot begin a new message until the bus returns to an Idle state.

However, two master devices may try to initiate a transmission on or about the same time. When this occurs, the process of arbitration begins. Each transmitter checks the level of the SDA data line and compares it to the level that it expects to find. The first transmitter to observe that the two levels do not match, loses arbitration, and must stop transmitting on the SDA line.

For example, if one transmitter holds the SDA line to a logical one (lets it float) and a second transmitter holds it to a logical zero (pulls it low), the result is that the SDA line will be low. The first transmitter then observes that the level of the line is different than expected and concludes that another transmitter is communicating.

The first transmitter to notice this difference is the one that loses arbitration and must stop driving the SDA line. If this transmitter is also a master device, it also must stop driving the SCL line. It then can monitor the lines for a Stop condition before trying to reissue its transmission. In the meantime, the other device that has not noticed any difference between the expected and actual levels on the SDA line continues with its original transmission. It can do so without any complications, because so far, the transmission appears exactly as expected with no other transmitter disturbing the message.

Slave Transmit mode can also be arbitrated, when a master addresses multiple slaves, but this is less common.

If two master devices are sending a message to two different slave devices at the address stage, the master sending the lower slave address always wins arbitration. When two master devices send messages to the same slave address, and addresses can sometimes refer to multiple slaves, the arbitration process must continue into the data stage.

Arbitration usually occurs very rarely, but it is a necessary process for proper multi-master support.

#### 35.4.3 Byte Format

All communication in I<sup>2</sup>C is done in 9-bit segments. A byte is sent from a master to a slave or vice-versa, followed by an Acknowledge bit sent back. After the eighth falling edge of the SCL line, the device outputting data on the SDA changes that pin to an input and reads in an acknowledge value on the next clock pulse.

The clock signal, SCL, is provided by the master. Data is valid to change while the SCL signal is low, and sampled on the rising edge of the clock. Changes on the SDA line while the SCL line is high define special conditions on the bus, explained below.

#### 35.4.4 Definition of I<sup>2</sup>C Terminology

There is language and terminology in the description of  $I^2C$  communication that have definitions specific to  $I^2C$ . That word usage is defined below and may be used in the rest of this document without explanation. This table was adapted from the Philips  $I^2C$  specification.

| TERM        | Description                                                                              |

|-------------|------------------------------------------------------------------------------------------|

| Transmitter | The device which shifts data out onto the bus.                                           |

| Receiver    | The device which shifts data in from the bus.                                            |

| Master      | The device that initiates a transfer, generates clock signals and terminates a transfer. |

## (EUSART) Enhanced Universal Synchronous Asyn...

|        | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) |

|--------|----------------|------------|-----------------------------|----------------|------------|-----------------------------|----------------|------------|-----------------------------|----------------|------------|-----------------------------|

| 300    | 300.0          | 0.00       | 6666                        | 300.0          | -0.01      | 4166                        | 300.0          | 0.00       | 3839                        | 300.0          | 0.00       | 2303                        |

| 1200   | 1200           | -0.02      | 3332                        | 1200           | -0.03      | 1041                        | 1200           | 0.00       | 959                         | 1200           | 0.00       | 575                         |

| 2400   | 2401           | -0.04      | 832                         | 2399           | -0.03      | 520                         | 2400           | 0.00       | 479                         | 2400           | 0.00       | 287                         |

| 9600   | 9615           | 0.16       | 207                         | 9615           | 0.16       | 129                         | 9600           | 0.00       | 119                         | 9600           | 0.00       | 71                          |

| 10417  | 10417          | 0.00       | 191                         | 10417          | 0.00       | 119                         | 10378          | -0.37      | 110                         | 10473          | 0.53       | 65                          |

| 19.2k  | 19.23k         | 0.16       | 103                         | 19.23k         | 0.16       | 64                          | 19.20k         | 0.00       | 59                          | 19.20k         | 0.00       | 35                          |

| 57.6k  | 57.14k         | -0.79      | 34                          | 56.818         | -1.36      | 21                          | 57.60k         | 0.00       | 19                          | 57.60k         | 0.00       | 11                          |

| 115.2k | 117.6k         | 2.12       | 16                          | 113.636        | -1.36      | 10                          | 115.2k         | 0.00       | 9                           | 115.2k         | 0.00       | 5                           |

|        |                  | SYNC = 0, BRGH = 0, BRG16 = 1 |                             |                  |            |                             |                   |            |                             |                  |            |                             |  |

|--------|------------------|-------------------------------|-----------------------------|------------------|------------|-----------------------------|-------------------|------------|-----------------------------|------------------|------------|-----------------------------|--|

| BAUD   | Fosc = 8.000 MHz |                               |                             | Fosc = 4.000 MHz |            |                             | Fosc = 3.6864 MHz |            |                             | Fosc = 1.000 MHz |            |                             |  |

| RATE   | Actual<br>Rate   | %<br>Error                    | SPBRG<br>value<br>(decimal) | Actual<br>Rate   | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate    | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate   | %<br>Error | SPBRG<br>value<br>(decimal) |  |

| 300    | 299.9            | -0.02                         | 1666                        | 300.1            | 0.04       | 832                         | 300.0             | 0.00       | 767                         | 300.5            | 0.16       | 207                         |  |

| 1200   | 1199             | -0.08                         | 416                         | 1202             | 0.16       | 207                         | 1200              | 0.00       | 191                         | 1202             | 0.16       | 51                          |  |

| 2400   | 2404             | 0.16                          | 207                         | 2404             | 0.16       | 103                         | 2400              | 0.00       | 95                          | 2404             | 0.16       | 25                          |  |

| 9600   | 9615             | 0.16                          | 51                          | 9615             | 0.16       | 25                          | 9600              | 0.00       | 23                          |                  | —          |                             |  |

| 10417  | 10417            | 0.00                          | 47                          | 10417            | 0.00       | 23                          | 10473             | 0.53       | 21                          | 10417            | 0.00       | 5                           |  |

| 19.2k  | 19.23k           | 0.16                          | 25                          | 19.23k           | 0.16       | 12                          | 19.20k            | 0.00       | 11                          |                  | —          | —                           |  |

| 57.6k  | 55556            | -3.55                         | 8                           |                  |            |                             | 57.60k            | 0.00       | 3                           |                  |            |                             |  |

| 115.2k |                  |                               |                             |                  |            | —                           | 115.2k            | 0.00       | 1                           |                  |            |                             |  |

SYNC = 0, BRGH = 1, BRG16 = 1 or SYNC = 1, BRG16 = 1

| BAUD | Fosc = 32.000 MHz |            |                             | Fosc = 20.000 MHz |            |                             | Fosc = 18.432 MHz |            |                             | Fosc = 11.0592 MHz |            |                             |

|------|-------------------|------------|-----------------------------|-------------------|------------|-----------------------------|-------------------|------------|-----------------------------|--------------------|------------|-----------------------------|

| RATE | Actual<br>Rate    | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate    | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate    | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate     | %<br>Error | SPBRG<br>value<br>(decimal) |

| 300  | 300.0             | 0.00       | 26666                       | 300.0             | 0.00       | 16665                       | 300.0             | 0.00       | 15359                       | 300.0              | 0.00       | 9215                        |

| 1200 | 1200              | 0.00       | 6666                        | 1200              | -0.01      | 4166                        | 1200              | 0.00       | 3839                        | 1200               | 0.00       | 2303                        |

| 2400 | 2400              | 0.01       | 3332                        | 2400              | 0.02       | 2082                        | 2400              | 0.00       | 1919                        | 2400               | 0.00       | 1151                        |

| 9600 | 9604              | 0.04       | 832                         | 9597              | -0.03      | 520                         | 9600              | 0.00       | 479                         | 9600               | 0.00       | 287                         |

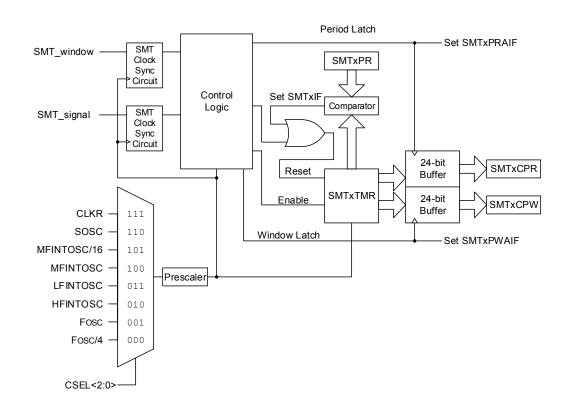

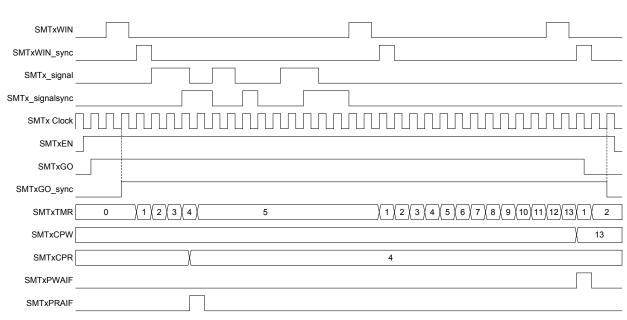

## 37. (SMT) Signal Measurement Timer

The SMT is a 24-bit counter with advanced clock and gating logic, which can be configured for measuring a variety of digital signal parameters such as pulse width, frequency and duty cycle, and the time difference between edges on two signals.

Features of the SMT include:

- 24-bit timer/counter

- Two 24-bit measurement capture registers

- One 24-bit period match register

- Multi-mode operation, including relative timing measurement

- Interrupt on period match and acquisition complete

- Multiple clock, signal and window sources

Below is the block diagram for the SMT module.

#### Figure 37-1. Signal Measurement Timer Block Diagram

Rev. 10-000161E 10/12/2016

### 37.1 SMT Operation

#### 37.1.1 Clock Source Selection

The SMT clock source is selected by configuring the CSEL bits in the SMTxCLK register. The clock source can be prescaled using the PS bits of the SMTxCON0 register. The prescaled clock source is

Rev. 10-000186A 4/22/2016

Rev. 10-000185A 4/26/2016

### (SMT) Signal Measurement Timer

| SMTxWIN         |   |         |   |    |

|-----------------|---|---------|---|----|

| SMTxWIN_sync    |   |         |   | ΙΓ |

| SMTx_signal     |   |         |   |    |

| SMTx_signalsync |   |         |   |    |

| SMTx Clock      |   |         |   |    |

| SMTxEN          |   |         |   |    |

| SMTxGO          |   |         |   |    |

| SMTxGO_sync     |   |         |   |    |

| SMTxTMR         | 0 | 1 2 3 4 | 5 |    |

| SMTxCPW         |   |         |   |    |

| SMTxCPR         |   | X       |   | 4  |

| SMTxPWAIF       |   |         |   |    |

| SMTxPRAIF       |   |         |   |    |

#### 37.1.6.8 Capture Mode

This mode captures the Timer value based on a rising or falling edge on the window input and triggers an interrupt. This mimics the capture feature of a CCP module. The timer begins incrementing upon the SMTxGO bit being set, and updates the value of the SMTxCPR register on each rising edge of window signal, and updates the value of the SMTxCPW register on each falling edge of the window signal. The timer is not reset by any hardware conditions in this mode and must be reset by software, if desired. See figures below.

# Instruction Set Summary

| BRW                 | Relative Branch with W                                                                                                                                                                                  |

|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Status<br>Affected: | None                                                                                                                                                                                                    |

| Description:        | Add the contents of W (unsigned) to the PC.<br>Since the PC will have incremented to fetch the next instruction, the new address will<br>be PC + 1 + (W).<br>This instruction is a 2-cycle instruction. |

| BSF              | Bit Set f                         |

|------------------|-----------------------------------|

| Syntax:          | [ <i>label</i> ]BSF f, b          |

| Operands:        | $0 \le f \le 127$ $0 \le b \le 7$ |

| Operation:       | $1 \rightarrow (f < b >)$         |

| Status Affected: | None                              |

| Description:     | Bit 'b' in register 'f' is set.   |

| BTFSC            | Bit Test File, Skip if Clear                                                                                                                                                                                         |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] BTFSC f, b                                                                                                                                                                                          |

| Operands:        | $0 \le f \le 127$<br>$0 \le b \le 7$                                                                                                                                                                                 |

| Operation:       | skip if (f <b>) = 0</b>                                                                                                                                                                                              |

| Status Affected: | None                                                                                                                                                                                                                 |

| Description:     | If bit 'b' in register 'f' is '1', the next instruction is executed.<br>If bit 'b', in register 'f', is '0', the next instruction is discarded,<br>and a NOP is executed instead, making this a 2-cycle instruction. |

| BTFSS            | Bit Test File, Skip if Set                                                                                                                                                                              |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] BTFSS f, b                                                                                                                                                                             |

| Operands:        | $0 \le f \le 127$<br>$0 \le b < 7$                                                                                                                                                                      |

| Operation:       | skip if (f <b>) = 1</b>                                                                                                                                                                                 |

| Status Affected: | None                                                                                                                                                                                                    |

| Description:     | If bit 'b' in register 'f' is '0', the next instruction is executed.<br>If bit 'b' is '1', then the next instruction is discarded,<br>and a NOP is executed instead, making this a 2-cycle instruction. |

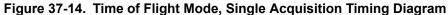

**Electrical Specifications**

#### Note:

- 1. The shaded region indicates the permissible combinations of voltage and frequency.

- 2. Refer to External Clock/Oscillator Timing Requirements for each Oscillator mode's supported frequencies.

#### **Related Links**

Supply Voltage

## 42.3 DC Characteristics

#### 42.3.1 Supply Voltage

#### Table 42-1.

| PIC16LF1                                                           | PIC16LF18426/46 only              |  |     |  |     |   |                           |  |  |  |  |  |  |

|--------------------------------------------------------------------|-----------------------------------|--|-----|--|-----|---|---------------------------|--|--|--|--|--|--|

| Standard Operating Conditions (unless otherwise stated)            |                                   |  |     |  |     |   |                           |  |  |  |  |  |  |

| Param.<br>No. Sym. Characteristic Min. Typ.† Max. Units Conditions |                                   |  |     |  |     |   |                           |  |  |  |  |  |  |

| Supply Vo                                                          | oltage                            |  |     |  |     |   |                           |  |  |  |  |  |  |

| 002                                                                | V                                 |  | 1.8 |  | 3.6 | V | F <sub>OSC</sub> ≤ 16 MHz |  |  |  |  |  |  |

| D002                                                               | V <sub>DD</sub>                   |  | 2.5 |  | 3.6 | V | F <sub>OSC</sub> > 16 MHz |  |  |  |  |  |  |

| RAM Data                                                           | RAM Data Retention <sup>(1)</sup> |  |     |  |     |   |                           |  |  |  |  |  |  |

## **Electrical Specifications**

| PIC16F18                                                | PIC16F18426/46 only                          |                                                        |        |       |        |       |                 |         |  |  |  |  |  |

|---------------------------------------------------------|----------------------------------------------|--------------------------------------------------------|--------|-------|--------|-------|-----------------|---------|--|--|--|--|--|

| Standard Operating Conditions (unless otherwise stated) |                                              |                                                        |        |       |        |       |                 |         |  |  |  |  |  |

| Param.                                                  | Sum                                          | Device                                                 | Min.   | Тур.† | Max.   | Units | Conc            | litions |  |  |  |  |  |

| No.                                                     | Sym.                                         | Characteristics                                        | IVIII. |       | IVIAA. | Units | V <sub>DD</sub> | Note    |  |  |  |  |  |

| D102                                                    | I <sub>DDHFOPLL</sub>                        | HFINTOSC = 32<br>MHz                                   |        | 3.7   | 5.6    | mA    | 3.0V            |         |  |  |  |  |  |

| D103                                                    | I <sub>DD<sub>HSPLL32</sub></sub>            | HS+PLL = 32 MHz                                        | _      | 3.7   | 5.7    | mA    | 3.0V            |         |  |  |  |  |  |

| D104                                                    | I <sub>DD<sub>IDLE</sub></sub>               | IDLE mode,<br>HFINTOSC = 16<br>MHz                     |        | 1.8   | 2.1    | mA    | 3.0V            |         |  |  |  |  |  |

| D105                                                    | I <sub>DD<sub>DOZE</sub><sup>(3)</sup></sub> | DOZE mode,<br>HFINTOSC = 16<br>MHz, Doze Ratio =<br>16 |        | 1.6   |        | mA    | 3.0V            |         |  |  |  |  |  |

† - Data in "Typ." column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

#### Note:

The test conditions for all I<sub>DD</sub> measurements in active operation mode are: OSC1 = external square wave, from

rail-to-rail; all I/O pins are outputs driven low;  $\overline{MCLR} = V_{DD}$ ; WDT disabled.

- The supply current is mainly a function of the operating voltage and frequency. Other factors, such as I/O pin loading and switching rate, oscillator type, internal code execution pattern and temperature, also have an impact on the current consumption.

- 3.  $I_{DD_{DOZE}} = [I_{DD_{IDLE}}^{*}(N-1)/N] + I_{DD_{HFO}} 16/N$  where N = DOZE Ratio (see *CPUDOZE* register).

- 4. PMD bits are all in the default state, no modules are disabled.

#### **Related Links**

CPUDOZE

#### 42.3.3 Power-Down Current (I<sub>PD</sub>)<sup>(1,2)</sup>

Table 42-3.

| PIC16LF                                                 | PIC16LF18426/46 only |                                             |      |       |               |                |       |                 |      |

|---------------------------------------------------------|----------------------|---------------------------------------------|------|-------|---------------|----------------|-------|-----------------|------|

| Standard Operating Conditions (unless otherwise stated) |                      |                                             |      |       |               |                |       |                 |      |

| Param.<br>No.                                           | Sym.                 | Device<br>Characteristics                   | Min. | Тур.† | Max.<br>+85°C | Max.<br>+125°C | Units | Conditions      |      |

|                                                         |                      |                                             |      |       |               |                |       | V <sub>DD</sub> | Note |

| D200                                                    | I <sub>PD</sub>      | I <sub>PD</sub> Base                        | _    | 0.06  | 2             | 9              | μA    | 3.0V            |      |

| D201                                                    | I <sub>PD_WDT</sub>  | Low-Frequency<br>Internal<br>Oscillator/WDT |      | 0.8   | 4.0           | 11             | μA    | 3.0V            |      |

## **Electrical Specifications**

# 42.4.14 Capture/Compare/PWM Requirements (CCP) Table 42-20.

| Operating Temperature: -40°C≤T <sub>A</sub> ≤+125°C |                           |                         |                   |                             |        |        |       |                       |  |

|-----------------------------------------------------|---------------------------|-------------------------|-------------------|-----------------------------|--------|--------|-------|-----------------------|--|

| Param<br>No.                                        | Sym.<br>T <sub>CC</sub> L | Characteristic          |                   | Min.                        | Тур. † | Max.   | Units | Conditions            |  |

| CC01*                                               |                           | CCPx                    | No Prescaler      | 0.5T <sub>CY</sub> +20      | _      | _      | ns    |                       |  |

|                                                     |                           | Input Low<br>Time       | With<br>Prescaler | 20                          | _      |        | ns    |                       |  |

| CC02*                                               | T <sub>CC</sub> H         | CCPx                    | No Prescaler      | 0.5T <sub>CY</sub> +20      |        |        | ns    |                       |  |

|                                                     |                           | Input High<br>Time      | With<br>Prescaler | 20                          | —      | — — ns | ns    |                       |  |

| CC03*                                               | T <sub>CC</sub> P         | CCPx<br>Input<br>Period |                   | (3T <sub>CY</sub><br>+40)/N | _      |        | ns    | N = Prescale<br>value |  |

\* - These parameters are characterized but not tested.

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

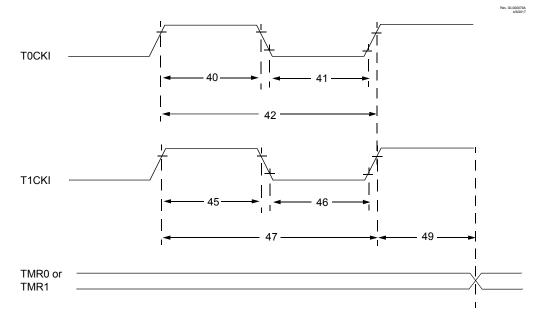

14-Lead Plastic Small Outline (SL) - Narrow, 3.90 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

#### RECOMMENDED LAND PATTERN

|                       | Units    | S    |          |      |

|-----------------------|----------|------|----------|------|

| Dimensio              | n Limits | MIN  | NOM      | MAX  |

| Contact Pitch         | E        |      | 1.27 BSC |      |

| Contact Pad Spacing   | С        |      | 5.40     |      |

| Contact Pad Width     | X        |      |          | 0.60 |

| Contact Pad Length    | Y        |      |          | 1.50 |

| Distance Between Pads | Gx       | 0.67 |          |      |

| Distance Between Pads | G        | 3.90 |          |      |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2065A