Welcome to **E-XFL.COM**

#### **Understanding Embedded - Microprocessors**

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

### **Applications of Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

| Details                         |                                                                    |

|---------------------------------|--------------------------------------------------------------------|

| Product Status                  | Obsolete                                                           |

| Core Processor                  | ARM926EJ-S                                                         |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                                     |

| Speed                           | 333MHz                                                             |

| Co-Processors/DSP               | Security; C3                                                       |

| RAM Controllers                 | LPDDR, DDR2                                                        |

| Graphics Acceleration           | No                                                                 |

| Display & Interface Controllers | LCD, Touchscreen                                                   |

| Ethernet                        | 10/100Mbps (3)                                                     |

| SATA                            | -                                                                  |

| USB                             | USB 2.0 + PHY (3)                                                  |

| Voltage - I/O                   | 3.3V                                                               |

| Operating Temperature           | -40°C ~ 85°C (TC)                                                  |

| Security Features               | Cryptography                                                       |

| Package / Case                  | 289-LFBGA                                                          |

| Supplier Device Package         | 289-LFBGA                                                          |

| Purchase URL                    | https://www.e-xfl.com/product-detail/stmicroelectronics/spear320-2 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

SPEAr320 List of tables

# List of tables

| Table 1.  | Device summary                                                                      | . 1 |

|-----------|-------------------------------------------------------------------------------------|-----|

| Table 2.  | Ethernet port multiplexing                                                          | 15  |

| Table 3.  | Master clock, RTC, Reset and 3.3 V comparator pin descriptions                      | 26  |

| Table 4.  | Power supply pin description                                                        |     |

| Table 5.  | Debug pin description                                                               |     |

| Table 6.  | SMI pin description                                                                 |     |

| Table 7.  | USB pin description                                                                 |     |

| Table 8.  | ADC pin description                                                                 |     |

| Table 9.  | DDR pin description                                                                 |     |

| Table 10. | PL_GPIO pin description                                                             |     |

| Table 11. | PL_GPIO multiplexing scheme                                                         |     |

| Table 12. | Table shading                                                                       |     |

| Table 13. | Ball sharing during debug                                                           |     |

| Table 14. | SPEAr320 main memory map                                                            |     |

| Table 15. | Reconfigurable array subsystem memory map                                           |     |

| Table 16. | Absolute maximum ratings                                                            |     |

| Table 10. | Maximum power consumption                                                           |     |

| Table 17. | Recommended operating conditions                                                    |     |

| Table 10. | Overshoot and undershoot specifications                                             |     |

| Table 19. | Low voltage TTL DC input specification (3 V< V <sub>DD</sub> <3.6 V)                |     |

| Table 20. | Low voltage TTL DC input specification (3 V< $V_{DD}$ <3.6 V)                       |     |

| Table 21. | Pull-up and pull-down characteristics                                               |     |

| Table 22. | DC characteristics                                                                  |     |

|           | Driver characteristics                                                              |     |

| Table 24. |                                                                                     |     |

| Table 25. | On die termination                                                                  |     |

| Table 26. | Reference voltage                                                                   |     |

| Table 27. | PL_GPIO external interrupt input timing                                             |     |

| Table 28. | Cold (power-on) reset                                                               |     |

| Table 29. | DDR2 read cycle timings                                                             |     |

| Table 30. | DDR2 write cycle timings                                                            |     |

| Table 31. | DDR2 command timings                                                                |     |

| Table 32. | CLCD timings                                                                        |     |

| Table 33. | Timing characteristics for I <sup>2</sup> C in high-speed mode                      |     |

| Table 34. | Timing characteristics for I <sup>2</sup> C in fast speed mode                      |     |

| Table 35. | Timing characteristics for I <sup>2</sup> C in standard speed mode                  |     |

| Table 36. | Timing characteristics for NAND Flash                                               |     |

| Table 37. | EMI timings for read cycle with acknowledgement on WAIT#                            |     |

| Table 38. | EMI timings for write cycle with acknowledgement on WAIT#                           |     |

| Table 39. | SDIO timings                                                                        |     |

| Table 40. | MII TX timings                                                                      |     |

| Table 41. | MII RX timings                                                                      |     |

| Table 42. | MDC timings                                                                         |     |

| Table 43. | SMII timings                                                                        |     |

| Table 44. | SMI timings                                                                         |     |

| Table 45. | Timing requirements for SSP (all modes)                                             |     |

| Table 46. | Timing requirements for SPI master mode (clock phase = 0)                           | 64  |

| Table 47. | Switching characteristics over recommended operating conditions for SPI master mode |     |

|           | (clock phase =0 )                                                                   | 64  |

#### Main features:

- Supports SPI-compatible Flash and EEPROM devices

- Acts always as a SPI master and up to 2 SPI slave memory devices are supported (with separate chip select signals), with up to 16 MB address space each

- SMI clock signal (SMICLK) is generated by SMI (and input to all slaves) using a clock provided by the AHB bus

- SMICLK can be up to 50 MHz in fast read mode (or 20 MHz in normal mode). It can be controlled by a programmable 7-bit prescaler allowing up to 127 different clock frequencies.

## 3.5 External memory interface (EMI)

The EMI Controller provides a simple external memory interface that can be used for example to connect to NOR Flash memory or FPGA devices.

#### Main features:

- EMI bus master

- 16 and 8-bit transfers

- Can access 4 different peripherals using CS#, one at a time.

- Supports single asynchronous transfers.

- Supports peripherals which use Byte Lane procedure

## 3.6 SDIO controller/MMC card interface

The SDIO host controller conforms to the SD host Controller Standard Specification Version 2.0. It handles SDIO/SD Protocol at transmission level, packing data, adding cyclic redundancy check (CRC), start/end bit and checking for transaction format correctness. The host controller provides programmed I/O and DMA data transfer method.

#### Main features:

- Meets the following specifications:

- SD Host Controller Standard Specification Version 2.0

- SDIO card specification version 2.0

- SD Memory Card Specification Draft version 2.0

- SD Memory Card Security Specification version 1.01

- MMC Specification version 3.31 and 4.2

- Supports both DMA and Non-DMA mode of operation

- Supports MMC Plus and MMC Mobile

- Card Detection (Insertion / Removal)

- Card password protection

- Host clock rate variable between 0 and 48 MHz

- Supports 1 bit, 4 bit and 8 bit SD modes and SPI mode

- Supports Multi Media Card Interrupt mode

- Allows card to interrupt host in 1 bit, 4 bit, 8 bit SD modes and SPI mode.

- Up to 100 Mbits per second data rate using 4 parallel data lines (SD4 bit mode)

Architecture overview SPEAr320

- Up to 416 Mbits per second data rate using 8 bit parallel data lines (SD8 bit mode)

- Cyclic Redundancy Check CRC7 for command and CRC16 for data integrity

- Designed to work with I/O cards, Read-only cards and Read/Write cards

- Error Correction Code (ECC) support for MMC4.2 cards

- Supports Read wait Control, Suspend/Resume operation

- Supports FIFO Overrun and Underrun condition by stopping SD clock

## 3.7 Flexible static memory controller (FSMC)

SPEAr320 provides a Flexible Static Memory Controller (FSMC) which interfaces to external parallel NAND Flash memories.

#### Main features:

- 8/16-bit wide data path

- FSMC performs only one access at a time and only one external device is accessed

- Supports little-endian and big-endian memory architectures

- AHB burst transfer handling to reduce access time to external devices

- Supplies an independent configuration for each memory bank

- Programmable timings to support a wide range of devices

- Programmable wait states (up to 31)

- Programmable bus turnaround cycles (up to 15)

- Programmable output enable and write enable delays (up to 15)

- Independent chip select control for each memory bank

- Shares the address bus and the data bus with all the external peripherals

- Only chips selects are unique for each peripheral

- External asynchronous wait control

- Boot memory bank configurable at reset using external control pins

### 3.8 Multichannel DMA controller

Within its basic subsystem, SPEAr320 provides a DMA controller (DMAC) able to service up to 8 independent DMA channels for serial data transfers between single source and destination (i.e., memory-to-memory, memory-to-peripheral, peripheral to- memory, and peripheral-to-peripheral).

Each DMA channel can support a unidirectional transfer, with internal four-word FIFO per channel.

14/73 Doc ID 16755 Rev 5

Architecture overview SPEAr320

### 3.10 CAN controller

SPEAr320 has two CAN controllers for interfacing CAN 2.0 networks.

#### Main features:

- Supports CAN protocol version 2.0 part A and B

- Bit rates up to 1 MBit/s

- 16 message objects(136 X 16 message RAM)

- Each message object has its own identifier mask

- Maskable interrupt

- Programmable loop-back mode for self-test operation

- Disabled automatic retransmission mode for time triggered CAN applications

### 3.11 USB2 Host controller

SPEAr320 has two fully independent USB 2.0 Hosts. Each consists of 5 major blocks:

- EHCI capable of managing high-speed transfers (HS mode, 480 Mbps)

- OHCI that manages the full and the low speed transfers (12 and 1.5 Mbps)

- Local 2-Kbyte FIFO

- Local DMA

- Integrated USB2 transceiver (PHY)

Both Hosts can manage an external power switch, providing a control line to enable or disable the power, and an input line to sense any over-current condition detected by the external switch.

One Host controller at time can perform high speed transfer.

### 3.12 USB2 Device controller

#### Main features:

- Supports the 480 Mbps high-speed mode (HS) for USB 2.0, as well as the 12 Mbps full-speed (FS) and the low-speed (LS modes) for USB 1.1

- Supports 16 physical endpoints, configurable as different logical endpoints

- Integrated USB transceiver (PHY)

- Local 4 Kbyte FIFO shared among all the endpoints

- DMA mode and slave-only mode are supported

- In DMA mode, the UDC supports descriptor-based memory structures in application memory

- In both modes, an AHB slave is provided by UDC-AHB, acting as programming interface to access to memory-mapped control and status registers (CSRs)

- An AHB master for data transfer to system memory is provided, supporting 8, 16, and 32-bit wide data transactions on the AHB bus

- A USB plug (UPD) detects the connection of a cable.

18/73 Doc ID 16755 Rev 5

### 3.13 CLCD controller

SPEAr320 has a color liquid crystal display controller (CLCDC) that provides all the necessary control signals to interface directly to a variety of color and monochrome LCD panels.

#### Main features:

- Resolution programmable up to 1024 x 768

- 16-bpp true-color non-palletized, for color STN and TFT

- 24-bpp true-color non-palletized, for color TFT

- Supports single and dual panel mono super twisted nematic (STN) displays with 4 or 8bit interfaces

- Supports single and dual-panel color and monochrome STN displays

- Supports thin film transistor (TFT) color displays

- 15 gray-level mono, 3375 color STN, and 32 K color TFT support

- 1, 2, or 4 bits per pixel (bpp) palletized displays for mono STN

- 1, 2, 4 or 8-bpp palletized color displays for color STN and TFT

- Programmable timing for different display panels

- 256 entry, 16-bit palette RAM, arranged as a 128 x 32-bit RAM physically frame, line and pixel clock signals

- AC bias signal for STN and data enable signal for TFT panels patented gray scale algorithm

- Supports little and big-endian

### 3.14 **GPIOs**

A maximum of 102 GPIOs (PL\_GPIOs) are available when part of the embedded IPs are not needed (see *Section 4.3: Shared I/O pins (PL\_GPIOs)*).

Within its basic subsystem, SPEAr320 provides a base General Purpose Input/Output (GPIO) block (basGPIO). The base GPIO block provides 6 programmable inputs or outputs. Each input/output can be controlled in two distinct modes:

- Software mode, through an APB interface.

- Hardware mode, through a hardware control interface.

Main features of the base GPIO block are:

- Six individually programmable input/output pins (default to input at reset)

- An APB slave acting as control interface in "software mode"

- Programmable interrupt generation capability on any number of pins.

- Hardware control capability of GPIO lines for different system configurations.

- Bit masking in both read and write operation through address lines.

Other GPIO blocks are present in the reconfigurable array subsystem.

### 3.21 8-channel ADC

#### Main features:

- Successive approximation conversion method

- 10-bit resolution @1 Msps

- Hardware supporting up to 13.5 bits resolution at 8 ksps by oversampling and accumulation

- Eight analog input (AIN) channels, ranging from 0 to 2.5 V

- INL ± 1 LSB, DNL ± 1 LSB

- Programmable conversion speed, (min. conversion time is 1 μs)

- Programmable averaging of results from 1 (No averaging) up to 128

- Programmable auto scan for all the eight channels.

## 3.22 System controller

The System Controller provides an interface for controlling the operation of the overall system.

#### Main features:

- Power saving system mode control

- Crystal oscillator and PLL control

- Configuration of system response to interrupts

- Reset status capture and soft reset generation

- Watchdog and timer module clock enable

## 3.22.1 Power saving system mode control

Using three mode control bits, the system controller switch the SPEAr320 to any one of four different modes: DOZE, SLEEP, SLOW and NORMAL.

- SLEEP mode: In this mode the system clocks, HCLK and CLK, are disabled and the System Controller clock SCLK is driven by a low speed oscillator (nominally 32768 Hz). When either a FIQ or an IRQ interrupt is generated (through the VIC) the system enters DOZE mode. Additionally, the operating mode setting in the system control register automatically changes from SLEEP to DOZE.

- DOZE mode: In this mode the system clocks, HCLK and CLK, and the System

Controller clock SCLK are driven by a low speed oscillator. The System Controller

moves into SLEEP mode from DOZE mode only when none of the mode control bits

are set and the processor is in Wait-for-interrupt state. If SLOW mode or NORMAL

mode is required the system moves into the XTAL control transition state to initialize the

crystal oscillator.

- SLOW mode: During this mode, both the system clocks and the System Controller

clock are driven by the crystal oscillator. If NORMAL mode is selected, the system goes

into the "PLL control" transition state. If neither the SLOW nor the NORMAL mode

control bits are set, the system goes into the "Switch from XTAL" transition state.

- NORMAL mode: In NORMAL mode, both the system clocks and the System Controller clock are driven by the PLL output. If the NORMAL mode control bit is not set, then the system goes into the "Switch from PLL" transition state.

Two different modes of operation are available:

Auto-reload mode, an interrupt source is activated, the counter is automatically cleared and then it restarts incrementing.

Single-shot mode, an interrupt source is activated, the counter is stopped and the GPT is disabled.

### 3.25 PWM timers

SPEAr320 provides 4 PWM timers.

#### Main features:

- Prescaler to define the input clock frequency to each timer

- Programmable duty cycle from 0% to 100%

- Programmable pulse length

- APB slave interface for register programming

## 3.26 Watchdog timer

The ARM watchdog module consists of a 32-bit down counter with a programmable timeout interval that has the capability to generate an interrupt and a reset signal on timing out. The watchdog module is intended to be used to apply a reset to a system in the event of a software failure.

### 3.27 RTC oscillator

The RTC provides a 1-second resolution clock. This keeps time when the system is inactive and can be used to wake the system up when a programmed alarm time is reached. It has a clock trimming feature to compensate for the accuracy of the 32.768 kHz crystal and a secured time update.

### Main features:

- Time-of-day clock in 24 hour mode

- Calendar

- Alarm capability

- Isolation mode, allowing RTC to work even if power is not supplied to the rest of the device.

SPEAr320 Pin description

Table 4. Power supply pin description (continued)

| USB_DEVICE_VSSA   N2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 0 V            |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| USB_HOST1_VSSA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 0 V            |

| ANALOG GROUND  USB_COMMON_VSSAC  USB_DEVICE_VSSA  N2  DITH_VSS2V5  N4  MCLK_GND  P3  MCLK_GNDSUB  R3  ADC_AGND  N12  I/O  DIGITAL_VDDE3V3  F8 F9 G12 H5 H12 J5 L11  ANALOG  USB_HOSTO_VSSA  L1  N2  N2  N4  N5  N6  N7  N6  N7  N7  N7  N7  N7  N7  N8  N8  N9  N9  N9  N9  N9  N9  N9  N9                                                                                                                                                                                                                                                                                                                                                            | 0 V            |

| ANALOG GROUND  USB_COMMON_VSSAC  USB_DEVICE_VSSA  N2  DITH_VSS2V5  N4  MCLK_GND  P3  MCLK_GNDSUB  R3  ADC_AGND  N12  I/O  DIGITAL_VDDE3V3  F5 F6 F7 F10 F11 F12 G5 J12 K12 L12 M12  10  CORE                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 0 V            |

| ANALOG GROUND  ANALOG GROUND  ANALOG USB_COMMON_VSSAC  USB_DEVICE_VSSA  DITH_VSS2V5  N4  MCLK_GND  MCLK_GND  ADC_AGND  N12  I/O  DIGITAL_VDDE3V3  F8 F9 G12 H5 H12 J5 L11  M6 M7 M11  USB HOST0 PHY  USB_HOST0_VDD2V5  L2  USB_HOST1_VDD2V5  K3  USB_HOST1_VDD2V5  N1  USB_HOST1_VDD3V3  J1  USB_DEVICE_VDD2V5  N1  USB_DEVICE_VDD3V3  N3  USB_DEVICE_VDD3V3  N3  USB_DEVICE_DVDD1V2  M3 | 0 V            |

| USB_DEVICE_VSSA   N2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | O V            |

| MCLK_GND   P3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                |

| MCLK_GNDSUB R3  ADC_AGND N12  I/O DIGITAL_VDDE3V3 F5 F6 F7 F10 F11 F12 G5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                |

| ADC_AGND N12  I/O DIGITAL_VDDE3V3 F5 F6 F7 F10 F11 F12 G5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                |

| I/O DIGITAL_VDDE3V3 F5 F6 F7 F10 F11 F12 G5 J12 K12 L12 M12  CORE VDD F8 F9 G12 H5 H12 J5 L11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                |

| J12 K12 L12 M12  OORE  VDD  F8 F9 G12 H5 H12 J5 L11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                |

| I CORE I VIII I I I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 3.3 V          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 1.2 V          |

| USB USB_HOST0_VDD2V5 L2 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 2.5 V          |

| HOST0 PHY USB_HOST0_VDD3V3 K4 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 3.3 V          |

| 000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 2.5 V          |

| HOST1 PHY USB_HOST1_VDD3V3 J1 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 3.3 V          |

| USB_DEVICE_VDD2V5 N1 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 2.5 V          |

| DEVICE USB_DEVICE_VDD3V3 N3 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 3.3 V          |

| USB_HOST1_HOST0_DEVICE_DVDD1V2 M3 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 1.2 V          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 1.2 V          |

| (master clock) MCLK_VDD2V5 R2 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 2.5 V          |

| PLL1 DITH_PLL_VDD_ANA G2 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 2.5 V          |

| PLL2 DITH_VDD_2V5 M4 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 2.5 V          |

| DDR I/O DDR_VDDE1V8 M5 N5 N6 N7 N8 N9 N10 N11 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                |

| ADC ADC_AVDD N13 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 1.8 V          |

| OSCI RTC RTC_VDD1V5 F1 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1.8 V<br>2.5 V |

Note: All the VDD 2V5 power supplies are analog VDD.

SPEAr320 Pin description

Table 7. USB pin description (continued)

| Group | Signal name           | Ball       | Direction        | Function                              | Pin type                               |

|-------|-----------------------|------------|------------------|---------------------------------------|----------------------------------------|

|       | USB_HOST1_DP          | H1         | 1/0              | USB HOST1 D+                          | Bidirectional                          |

|       | USB_HOST1_DM          | H2         | I/O              | USB HOST1 D-                          | analog buffer 5 V<br>tolerant          |

|       | USB_HOST1_VBUS H3 Out |            | USBHOST1<br>VBUS | TTL output buffer 3.3 V capable, 4 mA |                                        |

| USB   | USB_HOST1_OVERCUR     | J4         | ln               | USB Host1<br>Over-Current             | TTL input buffer 3.3 V tolerant, PD    |

| Host  | USB_HOST0_DP          | K1         | 1/0              | USB HOST0 D+                          | Bidirectional                          |

|       | USB_HOST0_DM          | K2         | I/O              | USB HOST0 D-                          | analog buffer 5 V<br>tolerant          |

|       | USB_HOST0_VBUS        | J3         | Out              | USB HOST0<br>VBUS                     | TTL output buffer 3.3 V capable, 4 mA  |

|       | USB_HOST0_OVERCUR     | H4         | ln               | USB Host0<br>Over-current             | TTL Input Buffer<br>3.3 V tolerant, PD |

| USB   | USB_TXRTUNE           | <b>K</b> 5 | Out              | Reference resistor                    | Analog                                 |

| OOD   | USB_ANALOG_TEST       | L4         | Out              | Analog Test<br>Output                 | Analog                                 |

Table 8. ADC pin description

| Signal name | Ball | Direction        | Function                       | Pin type |

|-------------|------|------------------|--------------------------------|----------|

| AIN_0       | N16  |                  |                                |          |

| AIN_1       | N15  |                  |                                |          |

| AIN_2       | P17  | ADC analog input | ADC analog input channel       |          |

| AIN_3       | P16  |                  |                                |          |

| AIN_4       | P15  |                  |                                |          |

| AIN_5       | R17  | In In            | Analog buffer 2.5 V tolerant   |          |

| AIN_6       | R16  |                  | tolerani                       |          |

| AIN_7       | R15  |                  |                                |          |

| ADC_VREFN   | N14  |                  | ADC negative voltage reference |          |

| ADC_VREFP   | P14  |                  | ADC positive voltage reference |          |

Pin description SPEAr320

## 4.3 Shared I/O pins (PL\_GPIOs)

The 98 PL\_GPIO and 4 PL\_CLK pins have the following characteristics:

- Output buffer: TTL 3.3 V capable up to 10 mA

- Input buffer: TTL, 3.3 V tolerant, selectable internal pull up/pull down (PU/PD)

The PL\_GPIOs can be configured in different modes. This allows SPEAr320 to be tailored for use in various applications like:

- Metering concentrators

- Large power supply controllers

- Small printers

## 4.3.1 PL\_GPIO pin description

Table 10. PL\_GPIO pin description

| Group    | Signal name             | Ball      | Direction | Function                                                                | Pin type                                 |

|----------|-------------------------|-----------|-----------|-------------------------------------------------------------------------|------------------------------------------|

| PL_GPIOs | PL_GPIO_97<br>PL_GPIO_0 | (see the  | I/O       | General<br>purpose I/O or<br>multiplexed pins<br>(see <i>Table 11</i> ) | (see the introduction of the Section 4.3 |

|          | PL_CLK1<br>PL_CLK4      | Table 11) |           | programmable<br>logic external<br>clocks                                | here above)                              |

## 4.3.2 Configuration modes

This section describes the main operating modes created by using a selection of the embedded IPs.

The following modes can be selected by programming some control registers present in the reconfigurable array subsystem.

- Mode 1: SMII automation networking mode

- Mode 2: MII automation networking mode

- Mode 3: Expanded automation mode

- Mode 4: Printer mode

Table 11: PL\_GPIO multiplexing scheme shows all the I/O functions available in each mode.

Mode 1 is the default mode for SPEAr320.

Pin description SPEAr320

### **Printer mode**

The "printer" operating mode mainly provides:

- NAND Flash interface (8 bits, 4 chip selects)

- Up to 4 PWM outputs

- 2 SMII interfaces

- 3 UARTs

- 1 with hardware flow control (up to 3 Mbps)

- 1 with hardware flow control (baud rate up to 7 Mbps)

- 1 with software flow control (baud rate up to 7 Mbps)

- SDIO interface supporting SPI, SD1, SD4 and SD8 mode

- Standard Parallel Port (SPP device implementation)

- 2 independent SSP Synchronous Serial Ports (SPI, Microwire or TI protocol)

- GPIOs with interrupt capabilities

•

### 4.3.3 Alternate functions

Other peripheral functions are listed in the Alternate Functions column of *Table 11: PL\_GPIO multiplexing scheme* and can be individually enabled/disabled configuring the bits of a dedicated control register.

### 4.3.4 Boot pins

The status of the boot pins is read at startup by the BootROM.

### 4.3.5 **GPIOs**

The PL\_GPIO pins can be used as software controlled general purpose I/Os (GPIOs) if they are not used by the I/O functions of the SPEAr320 IPs.

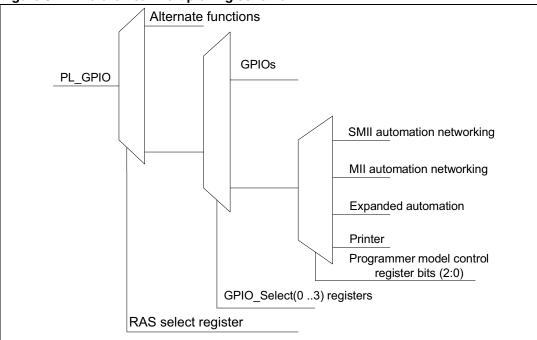

To configure any PL\_GPIO pin as GPIO, set the corresponding bit in the GPIO\_Select(0 ..3) registers that are 102 bits write registers that select GPIO versus some IPs.

SPEAr320 Pin description

## 4.3.6 Multiplexing scheme

To provide the best I/O multiplexing flexibility and the higher number of GPIOs for ARM controlled input-output function, the following hierarchical multiplexing scheme has been implemented.

Figure 3. Hierarchical multiplexing scheme

Table 11. PL\_GPIO multiplexing scheme

| PL_GPIO_# /    | Configurat | tion mode (enabled by Programmer model control register bits (2:0)) |         | nmer model | Alternate function   | pins | Function in GPIO    |

|----------------|------------|---------------------------------------------------------------------|---------|------------|----------------------|------|---------------------|

| number         | 1          | 2                                                                   | 3       | 4          | RAS select register) | Boot | alternative<br>mode |

| PL_GPIO_97/H16 | CLD0       | MII1_TXCLK                                                          | EMI_A0  | 0          |                      |      | GPIO_97             |

| PL_GPIO_96/H15 | CLD1       | MII1_TXD0                                                           | EMI_A1  | 0          |                      |      | GPIO_96             |

| PL_GPIO_95/H14 | CLD2       | MII1_TXD1                                                           | EMI_A2  | 0          |                      |      | GPIO_95             |

| PL_GPIO_94/H13 | CLD3       | MII1_TXD2                                                           | EMI_A3  | 0          |                      |      | GPIO_94             |

| PL_GPIO_93/G17 | CLD4       | MII1_TXD3                                                           | EMI_A4  | 0          |                      |      | GPIO_93             |

| PL_GPIO_92/G16 | CLD5       | MII1_TXEN                                                           | EMI_A5  | 0          |                      |      | GPIO_92             |

| PL_GPIO_91/G15 | CLD6       | MII1_TXER                                                           | EMI_A6  | 0          |                      |      | GPIO_91             |

| PL_GPIO_90/G14 | CLD7       | MII1_RXCLK                                                          | EMI_A7  | 0          |                      |      | GPIO_90             |

| PL_GPIO_89/F17 | CLD8       | MII1_RXDV                                                           | EMI_A8  | 0          |                      |      | GPIO_89             |

| PL_GPIO_88/F16 | CLD9       | MII1_RXER                                                           | EMI_A9  | 0          |                      |      | GPIO_88             |

| PL_GPIO_87/G13 | CLD10      | MII1_RXD0                                                           | EMI_A10 | 0          |                      |      | GPIO_87             |

## 6.5 3.3V I/O characteristics

The 3.3 V I/Os are compliant with JEDEC standard JESD8b.

Table 20. Low voltage TTL DC input specification (3 V<  $V_{DD}$  <3.6 V)

|                   |                            |     | -   |      |

|-------------------|----------------------------|-----|-----|------|

| Symbol            | Parameter                  | Min | Max | Unit |

| V <sub>IL</sub>   | Low level input voltage    |     | 0.8 | V    |

| V <sub>IH</sub>   | High level input voltage   | 2   |     | V    |

| V <sub>hyst</sub> | Schmitt trigger hysteresis | 300 | 800 | mV   |

Table 21. Low voltage TTL DC output specification (3 V<  $V_{DD}$  <3.6 V)

| Symbol          | Parameter                 | Test condition                         | Min                   | Max | Unit |

|-----------------|---------------------------|----------------------------------------|-----------------------|-----|------|

| V <sub>OL</sub> | Low level output voltage  | I <sub>OL</sub> = X mA <sup>(1)</sup>  |                       | 0.3 | V    |

| V <sub>OH</sub> | High level output voltage | I <sub>OH</sub> = -X mA <sup>(1)</sup> | V <sub>DD</sub> - 0.3 |     | V    |

Maximum current load (IOL) = 10 mA for PL\_GPIO and PL\_CLK pins. For the IOL max value of dedicated pins, refer to Chapter 4: Pin description.

Table 22. Pull-up and pull-down characteristics

| Symbol          | Parameter                       | Test condition       | Min | Max | Unit |

|-----------------|---------------------------------|----------------------|-----|-----|------|

| R <sub>PU</sub> | Equivalent pull-up resistance   | V <sub>I</sub> = 0 V | 29  | 67  | kΩ   |

| R <sub>PD</sub> | Equivalent pull-down resistance | $V_I = V_{DDE}3V3$   | 29  | 103 | kΩ   |

# 6.6 LPDDR and DDR2 pin characteristics

Table 23. DC characteristics

| Symbol            | Parameter                | Test condition | Min                     | Max                      | Unit |

|-------------------|--------------------------|----------------|-------------------------|--------------------------|------|

| $V_{IL}$          | Low level input voltage  | SSTL18         | -0.3                    | V <sub>REF</sub> -0.125  | V    |

| $V_{IH}$          | High level input voltage | SSTL18         | V <sub>REF</sub> +0.125 | V <sub>DDE</sub> 1V8+0.3 | V    |

| V <sub>hyst</sub> | Input voltage hysteresis |                | 200                     |                          | mV   |

Table 24. Driver characteristics

| Symbol         | Parameter        | Min | Тур | Max | Unit |

|----------------|------------------|-----|-----|-----|------|

| R <sub>O</sub> | Output impedance |     | 45  |     | Ω    |

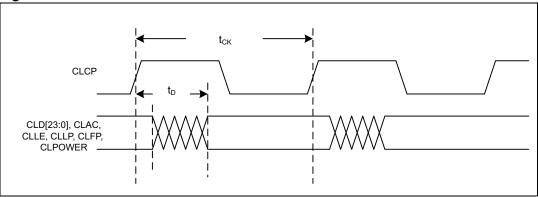

# 7.4 CLCD timing characteristics

The characterization timing is done considering an output load of 10 pF on all the outputs.

The CLCD has a wide variety of configurations and setting and the parameters change accordingly. *Figure 9* and *Table 32* specify the clock to output delay.

Figure 9. CLCD waveform

Table 32. CLCD timings

| Symbol          | Description                    | Min   | Max   | Unit |

|-----------------|--------------------------------|-------|-------|------|

| t <sub>CK</sub> | CLCP clock period              | 20.83 | 41.66 | ns   |

| t <sub>D</sub>  | CLCP to CLCD output data delay | 0.97  | 3.74  | ns   |

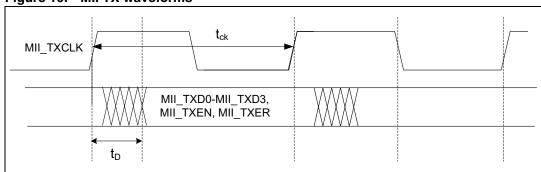

## 7.9 MII Ethernet MAC 10/100 Mbps timing characteristics

The characterization timing is given for an output load of 5 pF on the MII TX clock and 10 pF on the other pads.

## 7.9.1 MII transmit timing specifications

Figure 19. MII TX waveforms

Table 40. MII TX timings

| Symbol          | Description                        | Min | Max | Unit |

|-----------------|------------------------------------|-----|-----|------|

| t <sub>CK</sub> | MII_TXCLK clock period             | 40  | 40  | ns   |

| t <sub>D</sub>  | MII_TXCLK to MII output data delay | -1  | 8.9 | 115  |

To calculate the t<sub>SETUP</sub> value for the PHY you have to consider the next t<sub>CLK</sub> rising edge, so

you have to apply the following formula:  $t_{SETUP} = t_{CLK} - t_{max}$

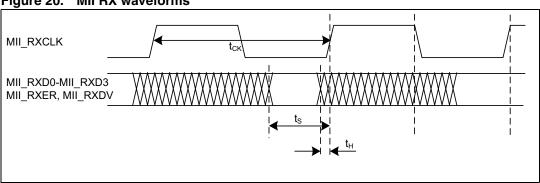

## 7.9.2 MII receive timing specifications

Note:

Figure 20. MII RX waveforms

Table 41. MII RX timings

| Symbol          | Description                                 | Min | Max | Unit |

|-----------------|---------------------------------------------|-----|-----|------|

| t <sub>CK</sub> | MII_TXCLK clock period                      | 40  | 40  |      |

| t <sub>S</sub>  | Setup time requirement for MII receive data | 1.6 |     | ns   |

| t <sub>H</sub>  | Hold time requirement for MII receive data  | 0.7 |     |      |

## 7.12 SSP timing characteristics

This module provides a programmable length shift register which allows serial communication with other SSP devices through a 3 or 4 wire interface (SSP\_CLK, SSP\_MISO, SSP\_MOSI and SSP\_CSn). The SSP supports the following features:

- Master/Slave mode operations

- Chip-selects for interfacing to multiple slave SPI devices.

- 3 or 4 wire interface (SSP\_SCK, SSP\_MISO, SSP\_MOSI and SSP\_CSn)

- Single interrupt

- Separate DMA events for SPI Receive and Transmit

- 16-bit shift register

- Receive buffer register

- Programmable character length (2 to 16 bits)

- Programmable SSP clock frequency range

- 8-bit clock pre-scaler

- Programmable clock phase (delay or no delay)

- Programmable clock polarity

Note:

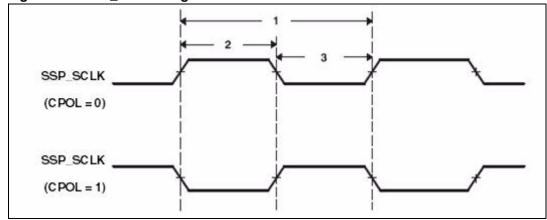

The following tables and figures show the characterization of the SSP using the SPI protocol.

Table 45. Timing requirements for SSP (all modes)

| No. |                      | parameters                   | Min     | Max     | Unit |

|-----|----------------------|------------------------------|---------|---------|------|

| 1   | T <sub>c(CLK)</sub>  | Cycle time, SSP_CLK          | 24      | _       | ns   |

| 2   | T <sub>w(CLKH)</sub> | Pulse duration, SSP_CLK high | 0.49*To | 0.51*To | ns   |

| 3   | T <sub>w(CLKL)</sub> | Pulse duration, SSP_CLK low  | 0.49*To | 0.51*To | ns   |

T = Tc(CLK) = SSP\_CLK period is equal to the SSP module master clock divided by a configurable divider.

Figure 24. SSP\_CLK timings

Timing requirements SPEAr320

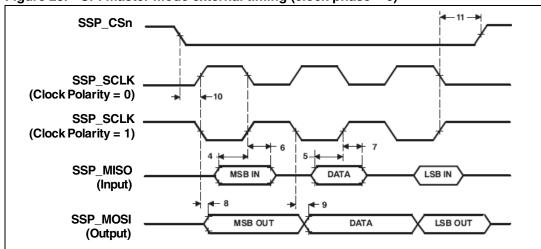

## 7.12.1 SPI master mode timings (clock phase = 0)

Table 46. Timing requirements for SPI master mode (clock phase = 0)

| No. |                           | Parameters                                                          |                       |      | Max  | Unit |

|-----|---------------------------|---------------------------------------------------------------------|-----------------------|------|------|------|

| 4   | t <sub>su(DIV-CLKL)</sub> | Setup time, MISO (input) valid before SSP_CLK (output) falling edge | Clock<br>polarity = 0 | -0.4 | -0.3 | ns   |

| 5   | t <sub>su(DIV-CLKH)</sub> | Setup time, MISO (input) valid before SSP_CLK (output) rising edge  | Clock<br>polarity = 1 | -0.4 | -0.3 | ns   |

| 6   | t <sub>h(CLKL-DIV)</sub>  | Hold time, MISO (input) valid after SSP_CLK (output) falling edge   | Clock<br>polarity = 0 | 0.9  | 1.7  | ns   |

| 7   | t <sub>h(CLKH-DIV)</sub>  | Hold time, MISO (input) valid after SSP_CLK (output) rising edge    | Clock<br>polarity = 1 | 0.9  | 1.7  | ns   |

Table 47. Switching characteristics over recommended operating conditions for SPI master mode (clock phase =0)

| No. |                            | Parameters                                                                                 |                       |      | Max | Unit |

|-----|----------------------------|--------------------------------------------------------------------------------------------|-----------------------|------|-----|------|

| 8   | t <sub>d(CLKH-DOV)</sub>   | Delay time, SSP_CLK (output) rising edge to MOSI (output) transition                       | Clock<br>Polarity = 0 | -3.1 | 2.2 | ns   |

| 9   | t <sub>d(CLKL-DOV)</sub>   | Delay time, SSP_CLK (output) falling edge to MOSI (output) transition                      | Clock<br>Polarity = 1 | -3.1 | 2.2 | ns   |

| 10  | t <sub>d(ENL-CLKH/L)</sub> | Delay time, SSP_CSn (output) falling edge to first SSP_CLK (output) rising or falling edge |                       |      | Γ   | ns   |

| 11  | td <sub>(CLKH/L-ENH)</sub> | Delay time, SSP_CLK (output) rising or falling edge to SSP_CSn (output) rising edge        |                       |      | /2  | ns   |

Figure 25. SPI master mode external timing (clock phase = 0)

64/73 Doc ID 16755 Rev 5

Timing requirements SPEAr320

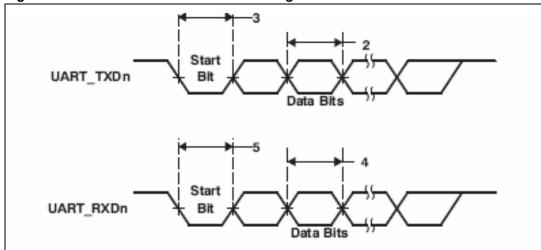

# 7.13 UART timing characteristics

Figure 27. UART transmit and receive timings

Table 50. UART transmit timing characteristics

| S.No. | Parameters                              | Min                  | Max              | Unit |  |

|-------|-----------------------------------------|----------------------|------------------|------|--|

| 1     | UART0 Maximum Baud Rate                 |                      | 3                | Mhne |  |

| ı     | UART1/UART2 Maximum Baud Rate           |                      | 7                | Mbps |  |

| 2     | UART Pulse Duration Transmit Data (TxD) | 0.99B <sub>(1)</sub> | B <sub>(1)</sub> | ns   |  |

| 3     | UART Transmit Start Bit                 | 0.99B <sub>(1)</sub> | B <sub>(1)</sub> | ns   |  |

Table 51. UART receive timing characteristics

| S.No. | Parameters                             | Min                  | Max                  | Units |

|-------|----------------------------------------|----------------------|----------------------|-------|

| 4     | UART Pulse Duration Receive Data (RxD) | 0.97B <sub>(1)</sub> | 1.06B <sub>(1)</sub> | ns    |

| 5     | UART Receive Start Bit                 | 0.97B <sub>(1)</sub> | 1.06B <sub>(1)</sub> | ns    |

where (1) B = UART baud rate

66/73 Doc ID 16755 Rev 5

**SEATING** PLANE C ppp 44 A2 Ā D  $_{\Omega}$ D1 00000000000000 R 0000000000000000 Ρ Ν 0000000000000000 0000000000000000 0000000000000000 0000000000000000  $\Box$ 0000000000000000 000000000000000 G 0000000000000000 0000000000000000 Ε 0000000000000000 D 0000000000000000 000000000000000000 000000000000000000 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 A1 CORNER INDEX AREA øb (289 BALLS) øeee (M) С Α В ø fff (M)

Figure 28. LFBGA289 package dimensions

Table 54. Thermal resistance characteristics

| package  | Θ <sub>JC</sub> (°C/W) | Θ <sub>JB</sub> (°C/W) | $\Theta_{JA}(^{\circ}C/W)^{(1)}$ |

|----------|------------------------|------------------------|----------------------------------|

| LFBGA289 | 18.5                   | 24.5                   | 33                               |

BOTTOM VIEW

$\triangleright \oplus$

<sup>1.</sup> Measured on JESD51 2s2p test board.

#### Please Read Carefully:

Information in this document is provided solely in connection with ST products. STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, modifications or improvements, to this document, and the products and services described herein at any time, without notice.

All ST products are sold pursuant to ST's terms and conditions of sale.

Purchasers are solely responsible for the choice, selection and use of the ST products and services described herein, and ST assumes no liability whatsoever relating to the choice, selection or use of the ST products and services described herein.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted under this document. If any part of this document refers to any third party products or services it shall not be deemed a license grant by ST for the use of such third party products or services, or any intellectual property contained therein or considered as a warranty covering the use in any manner whatsoever of such third party products or services or any intellectual property contained therein.

UNLESS OTHERWISE SET FORTH IN ST'S TERMS AND CONDITIONS OF SALE ST DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY WITH RESPECT TO THE USE AND/OR SALE OF ST PRODUCTS INCLUDING WITHOUT LIMITATION IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION), OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

UNLESS EXPRESSLY APPROVED IN WRITING BY AN AUTHORIZED ST REPRESENTATIVE, ST PRODUCTS ARE NOT RECOMMENDED, AUTHORIZED OR WARRANTED FOR USE IN MILITARY, AIR CRAFT, SPACE, LIFE SAVING, OR LIFE SUSTAINING APPLICATIONS, NOR IN PRODUCTS OR SYSTEMS WHERE FAILURE OR MALFUNCTION MAY RESULT IN PERSONAL INJURY, DEATH, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE. ST PRODUCTS WHICH ARE NOT SPECIFIED AS "AUTOMOTIVE GRADE" MAY ONLY BE USED IN AUTOMOTIVE APPLICATIONS AT USER'S OWN RISK.

Resale of ST products with provisions different from the statements and/or technical features set forth in this document shall immediately void any warranty granted by ST for the ST product or service described herein and shall not create or extend in any manner whatsoever, any liability of ST.

ST and the ST logo are trademarks or registered trademarks of ST in various countries.

Information in this document supersedes and replaces all information previously supplied.

The ST logo is a registered trademark of STMicroelectronics. All other names are the property of their respective owners.

© 2011 STMicroelectronics - All rights reserved

STMicroelectronics group of companies

Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan - Malaysia - Malta - Morocco - Philippines - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America

www.st.com