Welcome to E-XFL.COM

#### Embedded - FPGAs (Field Programmable Gate Array) with Microcontrollers: Enhancing Flexibility and Performance

#### Embedded - FPGAs (Field Programmable Gate

**Arrays) with Microcontrollers** represent a cutting-edge category of electronic components that combine the flexibility of FPGA technology with the processing power of integrated microcontrollers. This hybrid approach offers a versatile solution for designing and implementing complex digital systems that require both programmable logic and embedded processing capabilities.

#### What Are Embedded - FPGAs with Microcontrollers?

At their care EDCAR are comicanductor douices that can

#### Details

| Details                 |                                                                           |

|-------------------------|---------------------------------------------------------------------------|

| Product Status          | Obsolete                                                                  |

| Core Type               | 8-Bit AVR                                                                 |

| Speed                   | 25 MHz                                                                    |

| Interface               | I <sup>2</sup> C, UART                                                    |

| Program SRAM Bytes      | 4K-16K                                                                    |

| FPGA SRAM               | 2kb                                                                       |

| EEPROM Size             | -                                                                         |

| Data SRAM Bytes         | 4K ~ 16K                                                                  |

| FPGA Core Cells         | 256                                                                       |

| FPGA Gates              | 5К                                                                        |

| FPGA Registers          | 436                                                                       |

| Voltage - Supply        | 3V ~ 3.6V                                                                 |

| Mounting Type           | Surface Mount                                                             |

| Operating Temperature   | -40°C ~ 85°C                                                              |

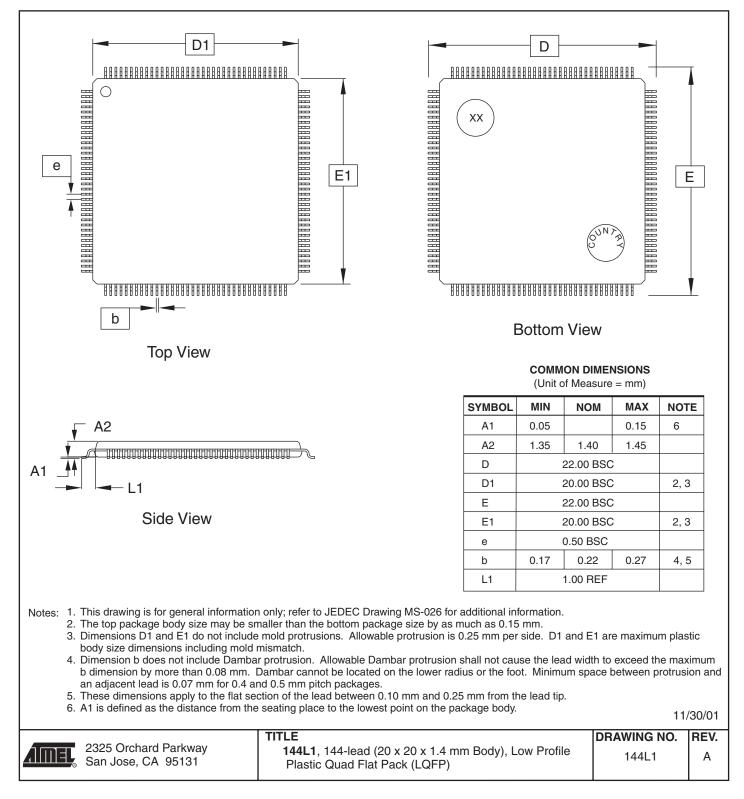

| Package / Case          | 144-LQFP                                                                  |

| Supplier Device Package | 144-LQFP (20x20)                                                          |

| Purchase URL            | https://www.e-xfl.com/product-detail/microchip-technology/at94k05al-25bqi |

|                         |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Bit           | Description                                                                                                                                                                                                                                                                                                                          |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SCR56         | 0 = Disable XTAL Pin (R <sub>feedback</sub> )<br>1 = Enable XTAL Pin (R <sub>feedback</sub> )                                                                                                                                                                                                                                        |

| SCR57         | 0 = Disable TOSC2 Pin (R <sub>feedback</sub> )<br>1 = Enable TOSC2 Pin (R <sub>feedback</sub> )                                                                                                                                                                                                                                      |

| SCR58 - SCR59 | Reserved                                                                                                                                                                                                                                                                                                                             |

| SCR60 - SCR61 | SCR61 = 0, SCR60 = 0 "1"<br>SCR61 = 0, SCR60 = 1 AVR System Clock<br>SCR61 = 1, SCR60 = 0 Timer Oscillator Clock (TOSC1) <sup>(1)</sup><br>SCR61 = 1, SCR60 = 1 Watchdog Clock<br>Global Clock 6 mux select (set by using the AT94K Device Options in System<br>Designer).<br>Note: 1. The AS2 bit must be set in the ASSR register. |

| SCR62         | 0 = Disable CacheLogic Writes to FPGA by AVR<br>1 = Enable CacheLogic Writes to FPGA by AVR                                                                                                                                                                                                                                          |

| SCR63         | 0 = Disable Access (Read and Write) to SRAM by FPGA<br>1 = Enable Access (Read and Write) to SRAM by FPGA                                                                                                                                                                                                                            |

Table 11. FPSLIC System Control Register

| Mnemonics | Operands | Description                              | Operation                                             | Flags       | #Clock |

|-----------|----------|------------------------------------------|-------------------------------------------------------|-------------|--------|

| CBR       | Rd, K    | Clear Bit(s) in Register                 | $Rd \leftarrow Rd \bullet (\$FFh - K)$                | Z,N,V,S     | 1      |

| INC       | Rd       | Increment                                | $Rd \leftarrow Rd + 1$                                | Z,N,V,S     | 1      |

| DEC       | Rd       | Decrement                                | $Rd \leftarrow Rd - 1$                                | Z,N,V,S     | 1      |

| TST       | Rd       | Test for Zero or Minus                   | $Rd \leftarrow Rd \bullet Rd$                         | Z,N,V,S     | 1      |

| CLR       | Rd       | Clear Register                           | $Rd \leftarrow Rd \oplus Rd$                          | Z,N,V,S     | 1      |

| SER       | Rd       | Set Register                             | $Rd \leftarrow \$FF$                                  | None        | 1      |

| MUL       | Rd, Rr   | Multiply Unsigned                        | $R1:R0 \leftarrow Rd \times Rr$ (UU)                  | Z,C         | 2      |

| MULS      | Rd, Rr   | Multiply Signed                          | $R1:R0 \leftarrow Rd \times Rr$ (SS)                  | Z,C         | 2      |

| MULSU     | Rd, Rr   | Multiply Signed with Unsigned            | $R1:R0 \leftarrow Rd \times Rr$ (SU)                  | Z,C         | 2      |

| FMUL      | Rd, Rr   | Fractional Multiply Unsigned             | $R1:R0 \leftarrow (Rd \times Rr) <<1 (UU)$            | Z,C         | 2      |

| FMULS     | Rd, Rr   | Fractional Multiply Signed               | $R1:R0 \leftarrow (Rd \times Rr) <<1 (SS)$            | Z,C         | 2      |

| FMULSU    | Rd, Rr   | Fractional Multiply Signed with Unsigned | $R1:R0 \leftarrow (Rd \times Rr) <<1 \text{ (SU)}$    | Z,C         | 2      |

|           |          | Branch In                                | structions                                            |             | 1      |

| RJMP      | k        | Relative Jump                            | $PC \leftarrow PC + k + 1$                            | None        | 2      |

| IJMP      |          | Indirect Jump to (Z)                     | PC(15:0) ← Z                                          | None        | 2      |

| JMP       | k        | Jump                                     | PC ← k                                                | None        | 3      |

| RCALL     | k        | Relative Call Subroutine                 | $PC \leftarrow PC + k + 1$                            | None        | 3      |

| ICALL     |          | Indirect Call to (Z)                     | PC(15:0) ← Z                                          | None        | 3      |

| CALL      | k        | Call Subroutine                          | PC ← k                                                | None        | 4      |

| RET       |          | Subroutine Return                        | $PC \leftarrow STACK$                                 | None        | 4      |

| RETI      |          | Interrupt Return                         | $PC \leftarrow STACK$                                 | I           | 4      |

| CPSE      | Rd, Rr   | Compare, Skip if Equal                   | if (Rd = Rr) PC $\leftarrow$ PC + 2 or 3              | None        | 1/2/3  |

| СР        | Rd, Rr   | Compare                                  | Rd - Rr                                               | Z,C,N,V,S,H | 1      |

| CPC       | Rd, Rr   | Compare with Carry                       | Rd - Rr - C                                           | Z,C,N,V,S,H | 1      |

| CPI       | Rd, K    | Compare with Immediate                   | Rd - K                                                | Z,C,N,V,S,H | 1      |

| SBRC      | Rr, b    | Skip if Bit in Register Cleared          | if (Rr(b) = 0) PC $\leftarrow$ PC + 2 or 3            | None        | 1/2/3  |

| SBRS      | Rr, b    | Skip if Bit in Register Set              | if (Rr(b) = 1) PC $\leftarrow$ PC + 2 or 3            | None        | 1/2/3  |

| SBIC      | A, b     | Skip if Bit in I/O Register Cleared      | $if(I/O(A,b) = 0) PC \leftarrow PC + 2 \text{ or } 3$ | None        | 1/2/3  |

| SBIS      | A, b     | Skip if Bit in I/O Register Set          | $If(I/O(A,b) = 1) PC \leftarrow PC + 2 \text{ or } 3$ | None        | 1/2/3  |

| BRBS      | s, k     | Branch if Status Flag Set                | if (SREG(s) = 1) then PC $\leftarrow$ PC+k+1          | None        | 1/2    |

| BRBC      | s, k     | Branch if Status Flag Cleared            | if (SREG(s) = 0) then PC $\leftarrow$ PC+k+1          | None        | 1/2    |

| BREQ      | k        | Branch if Equal                          | if (Z = 1) then PC $\leftarrow$ PC + k + 1            | None        | 1/2    |

| BRNE      | k        | Branch if Not Equal                      | if (Z = 0) then PC $\leftarrow$ PC + k + 1            | None        | 1/2    |

| BRCS      | k        | Branch if Carry Set                      | if (C = 1) then PC $\leftarrow$ PC + k + 1            | None        | 1/2    |

| BRCC      | k        | Branch if Carry Cleared                  | if (C = 0) then PC $\leftarrow$ PC + k + 1            | None        | 1/2    |

# Instruction Set Summary (Continued)

| Mnemonics | Operands | Description                                | Operation                                                          | Flags     | #Clock |

|-----------|----------|--------------------------------------------|--------------------------------------------------------------------|-----------|--------|

| ST        | -Y, Rr   | Store Indirect and Pre-Decrement           | $Y \leftarrow Y - 1, (Y) \leftarrow Rr$                            | None      | 2      |

| STD       | Y+q, Rr  | Store Indirect with Displacement           | $(Y + q) \leftarrow Rr$                                            | None      | 2      |

| ST        | Z, Rr    | Store Indirect                             | $(Z) \leftarrow Rr$                                                | None      | 2      |

| ST        | Z+, Rr   | Store Indirect and Post-Increment          | $(Z) \leftarrow Rr, Z \leftarrow Z + 1$                            | None      | 2      |

| ST        | -Z, Rr   | Store Indirect and Pre-Decrement           | $Z \leftarrow Z - 1$ , (Z) $\leftarrow Rr$                         | None      | 2      |

| STD       | Z+q, Rr  | Store Indirect with Displacement           | $(Z + q) \leftarrow Rr$                                            | None      | 2      |

| LPM       |          | Load Program Memory                        | $R0 \leftarrow (Z)$                                                | None      | 3      |

| LPM       | Rd, Z    | Load Program Memory                        | $Rd \leftarrow (Z)$                                                | None      | 3      |

| LPM       | Rd, Z+   | Load Program Memory and Post-<br>Increment | $Rd \leftarrow (Z), Z \leftarrow Z + 1$                            | None      | 3      |

| IN        | Rd, A    | In From I/O Location                       | $Rd \leftarrow I/O(A)$                                             | None      | 1      |

| OUT       | A, Rr    | Out To I/O Location                        | $I/O(A) \leftarrow Rr$                                             | None      | 1      |

| PUSH      | Rr       | Push Register on Stack                     | $STACK \leftarrow Rr$                                              | None      | 2      |

| POP       | Rd       | Pop Register from Stack                    | $Rd \gets STACK$                                                   | None      | 2      |

|           |          | Bit and Bit-tes                            | st Instructions                                                    |           |        |

| LSL       | Rd       | Logical Shift Left                         | $Rd(n+1)\leftarrow Rd(n), Rd(0)\leftarrow 0, C\leftarrow Rd(7)$    | Z,C,N,V,H | 1      |

| LSR       | Rd       | Logical Shift Right                        | $Rd(n) \leftarrow Rd(n+1), Rd(7) \leftarrow 0, C \leftarrow Rd(0)$ | Z,C,N,V   | 1      |

| ROL       | Rd       | Rotate Left Through Carry                  | $Rd(0)\leftarrow C,Rd(n+1)\leftarrow Rd(n),C\leftarrow Rd(7)$      | Z,C,N,V,H | 1      |

| ROR       | Rd       | Rotate Right Through Carry                 | $Rd(7)\leftarrow C,Rd(n)\leftarrow Rd(n+1),C\leftarrow Rd(0)$      | Z,C,N,V   | 1      |

| ASR       | Rd       | Arithmetic Shift Right                     | $Rd(n) \leftarrow Rd(n+1), n=06$                                   | Z,C,N,V   | 1      |

| SWAP      | Rd       | Swap Nibbles                               | $Rd(30) \leftrightarrow Rd(74)$                                    | None      | 1      |

| BSET      | S        | Flag Set                                   | $SREG(s) \leftarrow 1$                                             | SREG(s)   | 1      |

| BCLR      | s        | Flag Clear                                 | $SREG(s) \leftarrow 0$                                             | SREG(s)   | 1      |

| SBI       | A, b     | Set Bit in I/O Register                    | I/O(A, b) ← 1                                                      | None      | 2      |

| CBI       | A, b     | Clear Bit in I/O Register                  | $I/O(A, b) \leftarrow 0$                                           | None      | 2      |

| BST       | Rr, b    | Bit Store from Register to T               | $T \leftarrow Rr(b)$                                               | Т         | 1      |

| BLD       | Rd, b    | Bit load from T to Register                | $Rd(b) \leftarrow T$                                               | None      | 1      |

| SEC       |          | Set Carry                                  | C ← 1                                                              | С         | 1      |

| CLC       |          | Clear Carry                                | $C \leftarrow 0$                                                   | С         | 1      |

| SEN       |          | Set Negative Flag                          | N ← 1                                                              | N         | 1      |

| CLN       |          | Clear Negative Flag                        | N ← 0                                                              | N         | 1      |

| SEZ       |          | Set Zero Flag                              | Z ← 1                                                              | Z         | 1      |

| CLZ       |          | Clear Zero Flag                            | Z ← 0                                                              | Z         | 1      |

| SEI       |          | Global Interrupt Enable                    | ← 1                                                                | 1         | 1      |

| CLI       |          | Global Interrupt Disable                   | l ← 0                                                              | 1         | 1      |

| SES       |          | Set Signed Test Flag                       | S ← 1                                                              | S         | 1      |

# Instruction Set Summary (Continued)

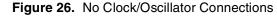

No Clock/Oscillator Source When not in use, for low static IDD, add a pull-down resistor to XTAL1.

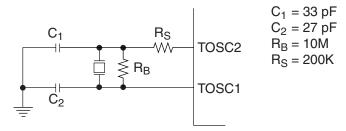

**Timer Oscillator** For the timer oscillator pins, TOSC1 and TOSC2, the crystal is connected directly between the pins. The oscillator is optimized for use with a 32.768 kHz watch crystal. An external clock signal applied to this pin goes through the same amplifier having a bandwidth of 1 MHz. The external clock signal should therefore be in the range 0 Hz – 1 MHz.

Figure 27. Time Oscillator Connections

# Architectural Overview

The AVR uses a Harvard architecture concept – with separate memories and buses for program and data. The program memory is accessed with a single level pipeline. While one instruction is being executed, the next instruction is pre-fetched from the program memory. This concept enables instructions to be executed in every clock-cycle. The program memory is in-system programmable SRAM memory. With a few exceptions, AVR instructions have a single 16-bit word format, meaning that every program memory address contains a single 16-bit instruction.

During interrupts and subroutine calls, the return address program counter (PC) is stored on the stack. The stack is effectively allocated in the general data SRAM, as a consequence, the stack size is only limited by the total SRAM size and the usage of the SRAM. All user programs must initialize the Stack Pointer (SP) in the reset routine (before subroutines or interrupts are executed). The 16-bit stack pointer is read/write accessible in the I/O space.

The data SRAM can be easily accessed through the five different addressing modes supported in the AVR architecture.

A flexible interrupt module has its control registers in the I/O space with an additional global interrupt enable bit in the status register. All the different interrupts have a separate interrupt vector in the interrupt vector table at the beginning of the program memory. The different interrupts have priority in accordance with their interrupt vector position. The lower the interrupt vector address, the higher the priority.

The memory spaces in the AVR architecture are all linear and regular memory maps.

| X-register,<br>Y-register and<br>Z-register | Registers R26R31 have some added functions to their general-purpose usage. These registers are address pointers for indirect addressing of the SRAM. The three indirect address registers X, Y and Z have functions as fixed displacement, automatic increment and decrement (see the descriptions for the different instructions). |  |  |  |  |

|---------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| ALU – Arithmetic<br>Logic Unit              | The high-performance AVR ALU operates in direct connection with all the 32 general-purpose working registers. Within a single clock cycle, ALU operations between registers in the register file are executed. The ALU operations are divided into three main categories – arithmetic, log-ical and bit-functions.                  |  |  |  |  |

| Multiplier Unit                             | The high-performance AVR Multiplier operates in direct connection with all the 32 general-pur-<br>pose working registers. This unit performs 8 x 8 multipliers every two clock cycles. See<br>multiplier details on page 106.                                                                                                       |  |  |  |  |

| SRAM Data                                   | External data SRAM (or program) cannot be used with the FPSLIC AT94K family.                                                                                                                                                                                                                                                        |  |  |  |  |

| Memory                                      | The five different addressing modes for the data memory cover: Direct, Indirect with Displace-<br>ment, Indirect, Indirect with Pre-decrement and Indirect with Post-increment. In the register<br>file, registers R26 to R31 feature the indirect addressing pointer registers.                                                    |  |  |  |  |

|                                             | The Indirect with Displacement mode features a 63 address locations reach from the base address given by the Y- or Z-register.                                                                                                                                                                                                      |  |  |  |  |

|                                             | When using register indirect addressing modes with automatic Pre-decrement and Post-increment, the address registers X, Y and Z are decremented and incremented.                                                                                                                                                                    |  |  |  |  |

|                                             | The entire data address space including the 32 general-purpose working registers and the 64 I/O registers are all accessible through all these addressing modes. See the next section for a detailed description of the different addressing modes.                                                                                 |  |  |  |  |

| Program and Data<br>Addressing Modes        | The embedded AVR core supports powerful and efficient addressing modes for access to the program memory (SRAM) and data memory (SRAM, Register File and I/O Memory). This section describes the different addressing modes supported by the AVR architecture.                                                                       |  |  |  |  |

|                                             | Register Direct, Single-register Rd                                                                                                                                                                                                                                                                                                 |  |  |  |  |

|                                             | The operand is contained in register d (Rd).                                                                                                                                                                                                                                                                                        |  |  |  |  |

|                                             | Register Direct, Two Registers Rd and Rr                                                                                                                                                                                                                                                                                            |  |  |  |  |

|                                             | Operands are contained in register r (Rr) and d (Rd). The result is stored in register d (Rd).                                                                                                                                                                                                                                      |  |  |  |  |

|                                             | I/O Direct                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

|                                             | Operand address is contained in 6 bits of the instruction word. $n$ is the destination or source register address.                                                                                                                                                                                                                  |  |  |  |  |

|                                             | Data Direct                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

|                                             | A 16-bit data address is contained in the 16 LSBs of a two-word instruction. Rd/Rr specify the destination or source register.                                                                                                                                                                                                      |  |  |  |  |

|                                             | Data Indirect with Displacement                                                                                                                                                                                                                                                                                                     |  |  |  |  |

|                                             | Operand address is the result of the Y- or Z-register contents added to the address contained in 6 bits of the instruction word.                                                                                                                                                                                                    |  |  |  |  |

# AT94KAL Series FPSLIC

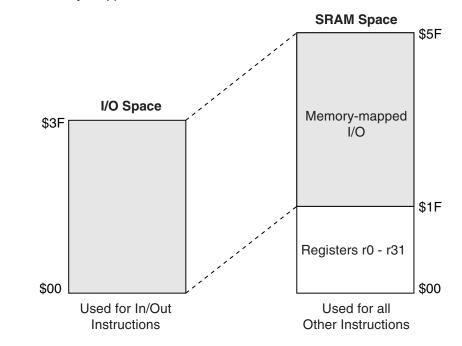

Figure 32. Memory-mapped I/O

For single-cycle access (In/Out Commands) to I/O, the instruction has to be less than 16 bits:

| opcode | register                 | address                  |

|--------|--------------------------|--------------------------|

| 5 bits | r0 - 31 (\$1F)<br>5 bits | r0 - 63 (\$3F)<br>6 bits |

In the data SRAM, the registers are located at memory addresses \$00 - \$1F and the I/O space is located at memory addresses \$20 - \$5F.

As there are only 6 bits available to refer to the I/O space, the address is shifted down 2 bits. This means the In/Out commands access \$00 to \$3F which goes directly to the I/O and maps to \$20 to \$5F in SRAM. All other instructions access the I/O space through the \$20 - \$5F addressing.

For compatibility with future devices, reserved bits should be written zero if accessed. Reserved I/O memory addresses should never be written.

The status flags are cleared by writing a logic 1 to them. Note that the CBI and SBI instructions will operate on all bits in the I/O register, writing a one back into any flag read as set, thus clearing the flag. The CBI and SBI instructions work with registers \$00 to \$1F only.

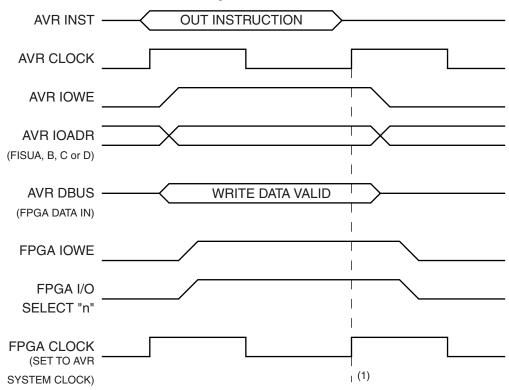

Figure 33. Out Instruction - AVR Writing to the FPGA

Note: 1. AVR expects Write to be captured by the FPGA upon posedge of the AVR clock.

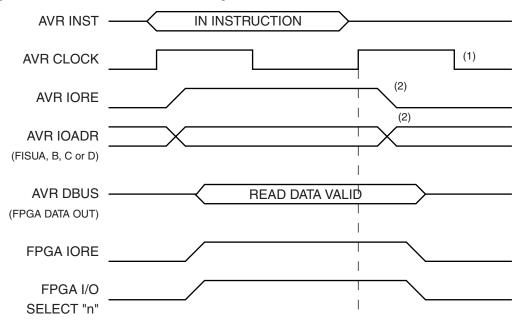

Figure 34. In Instruction – AVR Reading FPGA

- Notes: 1. AVR captures read data upon posedge of the AVR clock.

- At the end of an FPGA read cycle, there is a chance for the AVR data bus contention between the FPGA and another peripheral to start to drive (active IORE at new address versus FPGAIORE + Select "n"), but since the AVR clock would have already captured the data from AVR DBUS (= FPGA Data Out), this is a "don't care" situation.

External Interrupt Mask/Flag Register – EIMF

| Bit           | 7     | 6     | 5     | 4     | 3    | 2    | 1    | 0    | _    |

|---------------|-------|-------|-------|-------|------|------|------|------|------|

| \$3B (\$5B)   | INTF3 | INTF2 | INTF1 | INTF0 | INT3 | INT2 | INT1 | INT0 | EIMF |

| Read/Write    | R/W   | R/W   | R/W   | R/W   | R/W  | R/W  | R/W  | R/W  |      |

| Initial Value | 0     | 0     | 0     | 0     | 0    | 0    | 0    | 0    |      |

## • Bits 3..0 - INT3, 2, 1, 0: External Interrupt Request 3, 2, 1, 0 Enable

When an INT3 - INT0 bit is set (one) and the I-bit in the Status Register (SREG) is set (one), the corresponding external pin interrupt is enabled. The external interrupts are always negative edge triggered interrupts, see "Sleep Modes" on page 66.

## • Bits 7..4 - INTF3, 2, 1, 0: External Interrupt 3, 2, 1, 0 Flags

When a falling edge is detected on the INT3, 2, 1, 0 pins, an interrupt request is triggered. The corresponding interrupt flag, INTF3, 2, 1, 0 becomes set (one). If the I-bit in SREG and the corresponding interrupt enable bit, INT3, 2, 1, 0 in EIMF, are set (one), the MCU will jump to the interrupt vector. The flag is cleared when the interrupt routine is executed. Alternatively, the flag is cleared by writing a logic 1 to it.

## Timer/Counter Interrupt Mask Register – TIMSK

| Bit           | 7     | 6      | 5      | 4     | 3      | 2     | 1     | 0     | _     |

|---------------|-------|--------|--------|-------|--------|-------|-------|-------|-------|

| \$39 (\$39)   | TOIE1 | OCIE1A | OCIE1B | TOIE2 | TICIE1 | OCIE2 | TOIE0 | OCIE0 | TIMSK |

| Read/Write    | R/W   | R/W    | R/W    | R/W   | R/W    | R/W   | R/W   | R/W   | _     |

| Initial Value | 0     | 0      | 0      | 0     | 0      | 0     | 0     | 0     |       |

# • Bit 7 - TOIE1: Timer/Counter1 Overflow Interrupt Enable

When the TOIE1 bit is set (one) and the I-bit in the Status Register is set (one), the Timer/Counter1 Overflow interrupt is enabled. The corresponding interrupt is executed if an overflow in Timer/Counter1 occurs, i.e., when the TOV1 bit is set in the Timer/Counter Interrupt Flag Register – TIFR.

# • Bit 6 - OCIE1A: Timer/Counter1 Output CompareA Match Interrupt Enable

When the OCIE1A bit is set (one) and the I-bit in the Status Register is set (one), the Timer/Counter1 CompareA Match interrupt is enabled. The corresponding interrupt is executed if a CompareA match in Timer/Counter1 occurs, i.e., when the OCF1A bit is set in the Timer/Counter Interrupt Flag Register – TIFR.

# • Bit 5 - OCIE1B: Timer/Counter1 Output CompareB Match Interrupt Enable

When the OCIE1B bit is set (one) and the I-bit in the Status Register is set (one), the Timer/Counter1 CompareB Match interrupt is enabled. The corresponding interrupt is executed if a CompareB match in Timer/Counter1 occurs, i.e., when the OCF1B bit is set in the Timer/Counter Interrupt Flag Register – TIFR.

# • Bit 4 - TOIE2: Timer/Counter2 Overflow Interrupt Enable

When the TOIE2 bit is set (one) and the I-bit in the Status Register is set (one), the Timer/Counter2 overflow interrupt is enabled. The corresponding interrupt is executed if an overflow in Timer/Counter2 occurs, i.e., when the TOV2 bit is set in the Timer/Counter interrupt flag register – TIFR.

#### • Bit 3 - TICIE1: Timer/Counter1 Input Capture Interrupt Enable

When the TICIE1 bit is set (one) and the I-bit in the Status Register is set (one), the Timer/Counter1 input capture event interrupt is enabled. The corresponding interrupt is executed if a capture-triggering event occurs on pin 29, (IC1), i.e., when the ICF1 bit is set in the Timer/Counter interrupt flag register – TIFR.

Assuming Run-Test/Idle is the present state, a typical scenario for using the JTAG interface is

|                                   | <ul> <li>Assuming Run-Test/Idle is the present state, a typical scenario for using the JTAG interface is</li> <li>At the TMS input, apply the sequence 1, 1, 0, 0 at the rising edges of TCK to enter the Shift Instruction Register - Shift-IR state. While TMS is Low, shift the 4 bit JTAG instructions into the JTAG instruction register from the TDI input at the rising edge of TCK, while the captured IR-state 0x01 is shifts out on the TDO pin. The JTAG Instruction selects a particular Data Register as path between TDI and TDO and controls the circuitry surrounding the selected Data Register.</li> </ul>                                             |

|-----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                   | <ul> <li>Apply the TMS sequence 1, 1, 0 to re-enter the Run-Test/Idle state. The instruction is latched onto the parallel output from the shift register path in the Update-IR state. The Exit-IR, Pause-IR, and Exit2-IR states are only used for navigating the state machine.</li> <li>At the TMS input, apply the sequence 1, 0, 0 at the rising edges of TCK to enter the Shift Data Register - Shift-DR state. While TMS is Low, upload the selected Data Register (selected by the present JTAG instruction in the JTAG Instruction Register) from the TDI input at the rising edge of TCK. At the same time, the parallel inputs to the Data Register</li> </ul> |

|                                   | <ul> <li>captured in the Capture-DR state shifts out on the TDO pin.</li> <li>Apply the TMS sequence 1, 1, 0 to re-enter the Run-Test/Idle state. If the selected Data Register has a latched parallel-output, the latching takes place in the Update-DR state. The Exit-DR, Pause-DR, and Exit2-DR states are only used for navigating the state machine.</li> </ul>                                                                                                                                                                                                                                                                                                    |

|                                   | <ul> <li>As shown in Figure 40 on page 70, the Run-Test/Idle<sup>(1)</sup> state need not be entered between selecting JTAG instruction and using Data Registers, and some JTAG instructions may select certain functions to be performed in the Run-Test/Idle, making it unsuitable as an Idle state.</li> <li>Note: 1. Independent of the initial state of the TAP Controller, the Test-Logic-Reset state can always be entered by holding TMS High for 5 TCK clock periods.</li> </ul>                                                                                                                                                                                |

| Using the<br>Boundary-scan Chain  | A complete description of the Boundary-Scan capabilities are given in the section "IEEE 1149.1 (JTAG) Boundary-scan" on page 73.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Using the On-chip<br>Debug System | <ul> <li>As shown in Figure 39, the hardware support for On-Chip Debugging consists mainly of</li> <li>A scan chain on the interface between the internal AVR CPU and the internal peripheral units</li> <li>A breakpoint unit</li> <li>A communication interface between the CPU and JTAG system</li> <li>A scan chain on the interface between the internal AVR CPU and the FPGA</li> <li>A scan chain on the interface between the internal Program/Data SRAM and the FPGA</li> </ul>                                                                                                                                                                                 |

|                                   | All read or modify/write operations needed for implementing the Debugger are done by apply-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

All read or modify/write operations needed for implementing the Debugger are done by applying AVR instructions via the internal AVR CPU Scan Chain. The CPU sends the result to an I/O memory mapped location which is part of the communication interface between the CPU and the JTAG system.

|                            |                                                                                                                                                                                                                                                                                                                          | i                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | <u>AIMEL</u> -             |                                                                                                |             |               |  |  |

|----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|------------------------------------------------------------------------------------------------|-------------|---------------|--|--|

|                            | issued to mak<br>the reset state                                                                                                                                                                                                                                                                                         | e the shortes<br>either by pul                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | st possible scan <u>ch</u> | de. If needed, the BYF<br>ain through the device<br>/R RESET pin Low, or i<br>t Data Register. | . The AVR o | can be set in |  |  |

|                            | The data from<br>tion is loaded<br>used for settir<br>EXTEST instru                                                                                                                                                                                                                                                      | The EXTEST instruction is used for sampling external pins and loading output pins with data. The data from the output latch will be driven out on the pins as soon as the EXTEST instruction is loaded into the JTAG IR-register. Therefore, the SAMPLE/PRELOAD should also be used for setting initial values to the scan ring, to avoid damaging the board when issuing the EXTEST instruction for the first time. SAMPLE/PRELOAD can also be used for taking a snapshot of the AVR's external pins during normal operation of the part. |                            |                                                                                                |             |               |  |  |

|                            | The JTAG Enable bit must be programmed and the JTD bit in the I/O register MCUR must be<br>cleared to enable the JTAG Test Access Port.                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                            |                                                                                                |             |               |  |  |

|                            | When using the JTAG interface for Boundary-Scan, using a JTAG TCK clock frequency higher than the internal chip frequency is possible. The chip clock is not required to run.                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                            |                                                                                                |             |               |  |  |

| Data Registers             | The Data Registers are selected by the JTAG instruction registers described in section<br>"Boundary-scan Specific JTAG Instructions" on page 75. The data registers relevant for<br>Boundary-Scan operations are:                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                            |                                                                                                |             |               |  |  |

|                            | <ul> <li>Bypass Re</li> </ul>                                                                                                                                                                                                                                                                                            | egister                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                            |                                                                                                |             |               |  |  |

|                            | Device Ide                                                                                                                                                                                                                                                                                                               | entification Re                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | egister                    |                                                                                                |             |               |  |  |

|                            | <ul> <li>AVR Rese</li> </ul>                                                                                                                                                                                                                                                                                             | et Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                            |                                                                                                |             |               |  |  |

|                            | AVR Bour                                                                                                                                                                                                                                                                                                                 | ndary-Scan Cl                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | hain                       |                                                                                                |             |               |  |  |

| Bypass Register            | The Bypass register consists of a single shift-register stage. When the Bypass register is selected as path between TDI and TDO, the register is reset to 0 when leaving the Capture-DR controller state. The Bypass register can be used to shorten the scan chain on a system when the other devices are to be tested. |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                            |                                                                                                |             |               |  |  |

| Device                     | Figure 41 sho                                                                                                                                                                                                                                                                                                            | ws the structu                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ire of the Device Id       | entification register.                                                                         |             |               |  |  |

| Identification<br>Register | -                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ne Device Identifica       | -                                                                                              |             |               |  |  |

|                            |                                                                                                                                                                                                                                                                                                                          | MSB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                            |                                                                                                |             | LSB           |  |  |

|                            | Bit                                                                                                                                                                                                                                                                                                                      | 31 28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 27 12                      | 11                                                                                             | 1           | 0             |  |  |

|                            | Device ID                                                                                                                                                                                                                                                                                                                | Version                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Part Number                | Manufacturer ID                                                                                |             | 1             |  |  |

|                            |                                                                                                                                                                                                                                                                                                                          | 4 bits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 16 bits                    | 11 bits                                                                                        |             | 1 bit         |  |  |

## Version

Version is a 4-bit number identifying the revision of the component. The relevant version numbers are shown in Table 18.

#### Table 18. JTAG Part Version

| Device  | Version (Binary Digits) |

|---------|-------------------------|

| AT94K05 | _                       |

| AT94K10 | 0010                    |

| AT94K40 | _                       |

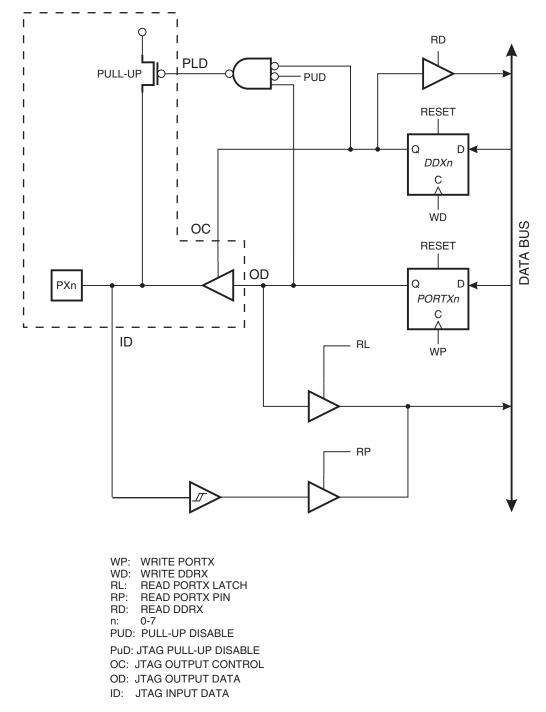

Figure 44 shows a simple digital Port Pin as described in the section "I/O Ports" on page 147. The Boundary-Scan details from Figure 43 replaces the dashed box in Figure 44.

Figure 44. General Port Pin Schematic Diagram

The 16-bit Timer/Counter1 can select the clock source from CK, prescaled CK, or an external pin. In addition it can be stopped as described in section "Timer/Counter1 Control Register B – TCCR1B" on page 98. The different status flags (overflow, compare match and capture event) are found in the Timer/Counter Interrupt Flag Register – TIFR. Control signals are found in the Timer/Counter1 Control Registers – TCCR1A and TCCR1B. The interrupt enable/disable settings for Timer/Counter1 are found in the Timer/Counter Interrupt Mask Register – TIMSK.

When Timer/Counter1 is externally clocked, the external signal is synchronized with the oscillator frequency of the CPU. To assure proper sampling of the external clock, the minimum time between two external clock transitions must be at least one internal CPU clock period. The external clock signal is sampled on the rising edge of the internal CPU clock.

The 16-bit Timer/Counter1 features both a high-resolution and a high-accuracy usage with the lower prescaling opportunities. Similarly, the high-prescaling opportunities makes the Timer/Counter1 useful for lower speed functions or exact-timing functions with infrequent actions.

The Timer/Counter1 supports two Output Compare functions using the Output Compare Register 1 A and B – OCR1A and OCR1B as the data sources to be compared to the Timer/Counter1 contents. The Output Compare functions include optional clearing of the counter on compareA match, and actions on the Output Compare pins on both compare matches.

Timer/Counter1 can also be used as a 8-, 9- or 10-bit Pulse Width Modulator. In this mode, the counter and the OCR1A/OCR1B registers serve as a dual-glitch-free stand-alone PWM with centered pulses. Alternatively, the Timer/Counter1 can be configured to operate at twice the speed in PWM mode, but without centered pulses. Refer to page 101 for a detailed description on this function.

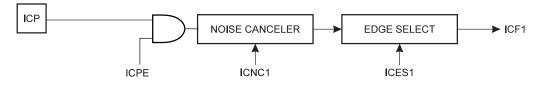

The Input Capture function of Timer/Counter1 provides a capture of the Timer/Counter1 contents to the Input Capture Register – ICR1, triggered by an external event on the Input Capture Pin – PE7(ICP). The actual capture event settings are defined by the Timer/Counter1 Control Register – TCCR1B.

Figure 55. ICP Pin Schematic Diagram

ICPE: Input Capture Pin Enable

If the noise canceler function is enabled, the actual trigger condition for the capture event is monitored over four samples, and all four must be equal to activate the capture flag.

# TCNT1 Timer/Counter1 Read

When the CPU reads the low byte TCNT1L, the data of the low byte TCNT1L is sent to the CPU and the data of the high byte TCNT1H is placed in the TEMP register. When the CPU reads the data in the high byte TCNT1H, the CPU receives the data in the TEMP register. Consequently, the low byte TCNT1L must be accessed first for a full 16-bit register read operation.

The Timer/Counter1 is realized as an up or up/down (in PWM mode) counter with read and write access. If Timer/Counter1 is written to and a clock source is selected, the Timer/Counter1 continues counting in the timer clock-cycle after it is preset with the written value.

| Bit           | 15  | 14  | 13  | 12  | 11  | 10  | 9   | 8   |        |

|---------------|-----|-----|-----|-----|-----|-----|-----|-----|--------|

| \$2B (\$4B)   | MSB |     |     |     |     |     |     |     | OCR1AH |

| \$2A (\$4A)   |     |     |     |     |     |     |     | LSB | OCR1AL |

|               | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |        |

| Read/Write    | R/W |        |

|               | R/W |        |

| Initial Value | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |        |

|               | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |        |

## Timer/Counter1 Output Compare Register – OCR1AH AND OCR1AL

Timer/Counter1 Output Compare Register – OCR1BH AND OCR1BL

| Bit           | 15  | 14  | 13  | 12  | 11  | 10  | 9   | 8   |        |

|---------------|-----|-----|-----|-----|-----|-----|-----|-----|--------|

| \$29 (\$49)   | MSB |     |     |     |     |     |     |     | OCR1BH |

| \$28 (\$48)   |     |     |     |     |     |     |     | LSB | OCR1BL |

|               | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |        |

| Read/Write    | R/W |        |

|               | R/W |        |

| Initial Value | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |        |

|               | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |        |

The output compare registers are 16-bit read/write registers.

The Timer/Counter1 Output Compare Registers contain the data to be continuously compared with Timer/Counter1. Actions on compare matches are specified in the Timer/Counter1 Control and Status register. A compare match does only occur if Timer/Counter1 counts to the OCR value. A software write that sets TCNT1 and OCR1A or OCR1B to the same value does not generate a compare match.

A compare match will set the compare interrupt flag in the CPU clock cycle following the compare event.

Since the Output Compare Registers – OCR1A and OCR1B – are 16-bit registers, a temporary register TEMP is used when OCR1A/B are written to ensure that both bytes are updated simultaneously. When the CPU writes the high byte, OCR1AH or OCR1BH, the data is temporarily stored in the TEMP register. When the CPU writes the low byte, OCR1AL or OCR1BL, the TEMP register is simultaneously written to OCR1AH or OCR1BH. Consequently, the high byte OCR1AH or OCR1BH must be written first for a full 16-bit register write operation.

The TEMP register is also used when accessing TCNT1, and ICR1. If the main program and also interrupt routines perform access to registers using TEMP, interrupts must be disabled during access from the main program and interrupt routines.

Example 3 – Multiplyaccumulate Operation The final example of 8-bit multiplication shows a multiply-accumulate operation. The general formula can be written as:

```

c(n) = a(n) × b + c(n-1)

; r17:r16 = r18 * r19 + r17:r16

in r18,PINB ; Get the current pin value on port B

ldi r19,b ; Load constant b into r19

muls r19,r18 ; r1:r0 = variable A * variable B

add r16,r0 ; r17:r16 += r1:r0

adc r17,r1

```

Typical applications for the multiply-accumulate operation are FIR (Finite Impulse Response) and IIR (Infinite Impulse Response) filters, PID regulators and FFT (Fast Fourier Transform). For these applications the FMULS instruction is particularly useful. The main advantage of using the FMULS instruction instead of the MULS instruction is that the 16-bit result of the FMULS operation always may be approximated to a (well-defined) 8-bit format, see "Using Fractional Numbers" on page 111.

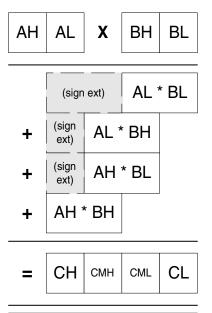

**16-bit Multiplication** The new multiply instructions are specifically designed to improve 16-bit multiplication. This section presents solutions for using the hardware multiplier to do multiplication with 16-bit operands.

Figure 60 schematically illustrates the general algorithm for multiplying two 16-bit numbers with a 32-bit result ( $C = A \cdot B$ ). AH denotes the high byte and AL the low byte of the A operand. CMH denotes the middle high byte and CML the middle low byte of the result C. Equal notations are used for the remaining bytes.

The algorithm is basic for all multiplication. All of the partial 16-bit results are shifted and added together. The sign extension is necessary for signed numbers only, but note that the carry propagation must still be done for unsigned numbers.

Figure 60. 16-bit Multiplication, General Algorithm

# UART0 Control and Status Registers – UCSR0A

| Bit           | 7    | 6    | 5     | 4   | 3   | 2 | 1    | 0     |        |

|---------------|------|------|-------|-----|-----|---|------|-------|--------|

| \$0B (\$2B)   | RXC0 | TXC0 | UDRE0 | FE0 | OR0 | - | U2X0 | MPCM0 | UCSR0A |

| Read/Write    | R    | R/W  | R     | R   | R   | R | R/W  | R/W   | -      |

| Initial Value | 0    | 0    | 1     | 0   | 0   | 0 | 0    | 0     |        |

## UART1 Control and Status Registers – UCSR1A

| Bit           | 7    | 6    | 5     | 4   | 3   | 2 | 1    | 0     |        |

|---------------|------|------|-------|-----|-----|---|------|-------|--------|

| \$02 (\$22)   | RXC1 | TXC1 | UDRE1 | FE1 | OR1 | - | U2X1 | MPCM1 | UCSR1A |

| Read/Write    | R    | R/W  | R     | R   | R   | R | R/W  | R/W   | -      |

| Initial Value | 0    | 0    | 1     | 0   | 0   | 0 | 0    | 0     |        |

## • Bit 7 - RXC0/RXC1: UART Receive Complete

This bit is set (one) when a received character is transferred from the Receiver Shift register to UDRn. The bit is set regardless of any detected framing errors. When the RXCIEn bit in UCS-RnB is set, the UART Receive Complete interrupt will be executed when RXCn is set (one). RXCn is cleared by reading UDRn. When interrupt-driven data reception is used, the UART Receive Complete Interrupt routine must read UDRn in order to clear RXCn, otherwise a new interrupt will occur once the interrupt routine terminates.

#### • Bit 6 - TXC0/TXC1: UART Transmit Complete

This bit is set (one) when the entire character (including the stop bit) in the Transmit Shift register has been shifted out and no new data has been written to UDRn. This flag is especially useful in half-duplex communications interfaces, where a transmitting application must enter receive mode and free the communications bus immediately after completing the transmission.

When the TXCIEn bit in UCSRnB is set, setting of TXCn causes the UART Transmit Complete interrupt to be executed. TXCn is cleared by the hardware when executing the corresponding interrupt handling vector. Alternatively, the TXCn bit is cleared (zero) by writing a logic 1 to the bit.

#### • Bit 5 - UDRE0/UDRE1: UART Data Register Empty

This bit is set (one) when a character written to UDRn is transferred to the Transmit shift register. Setting of this bit indicates that the transmitter is ready to receive a new character for transmission.

When the UDRIEn bit in UCSRnB is set, the UART Transmit Complete interrupt will be executed as long as UDREn is set and the global interrupt enable bit in SREG is set. UDREn is cleared by writing UDRn. When interrupt-driven data transmittal is used, the UART Data Register Empty Interrupt routine must write UDRn in order to clear UDREn, otherwise a new interrupt will occur once the interrupt routine terminates.

UDREn is set (one) during reset to indicate that the transmitter is ready.

#### • Bit 4 - FE0/FE1: Framing Error

This bit is set if a Framing Error condition is detected, i.e., when the stop bit of an incoming character is zero.

The FEn bit is cleared when the stop bit of received data is one.

# 2-wire Serial Interface (Byte Oriented)

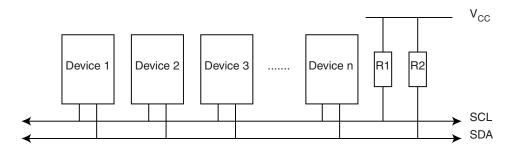

The 2-wire Serial Bus is a bi-directional two-wire serial communication standard. It is designed primarily for simple but efficient integrated circuit (IC) control. The system is comprised of two lines, SCL (Serial Clock) and SDA (Serial Data) that carry information between the ICs connected to them. Various communication configurations can be designed using this bus. Figure 68 shows a typical 2-wire Serial Bus configuration. Any device connected to the bus can be Master or Slave.

Figure 68. 2-wire Serial Bus Configuration

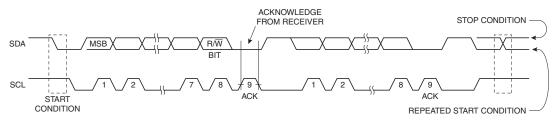

The 2-wire Serial Interface provides a serial interface that meets the 2-wire Serial Bus specification and supports Master/Slave and Transmitter/Receiver operation at up to 400 kHz bus clock rate. The 2-wire Serial Interface has hardware support for the 7-bit addressing, but is easily extended to 10-bit addressing format in software. When operating in 2-wire Serial mode, i.e., when TWEN is set, a glitch filter is enabled for the input signals from the pins SCL and SDA, and the output from these pins are slew-rate controlled. The 2-wire Serial Interface is byte oriented. The operation of the serial 2-wire Serial Bus is shown as a pulse diagram in Figure 69, including the START and STOP conditions and generation of ACK signal by the bus receiver.

Figure 69. 2-wire Serial Bus Timing Diagram

The block diagram of the 2-wire Serial Bus interface is shown in Figure 70.

# DC Characteristics – 3.3V Operation – Commercial/Industrial (Preliminary)

$T_{A}$  = -40°C to 85°C,  $V_{CC}$  = 2.7V to 3.6V (unless otherwise noted^{(1)})

| Symbol                                   | Parameter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Conditions                                                     | Minimum <sup>(3)</sup>              | Typical           | Maximum <sup>(2)</sup> | Units  |

|------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|-------------------------------------|-------------------|------------------------|--------|

| V <sub>IH</sub>                          | High-level Input Voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | CMOS                                                           | 0.7 V <sub>CC</sub>                 | _                 | 5.5                    | V      |

| V <sub>IH1</sub>                         | Input High-voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | XTAL                                                           | 0.7 V <sub>CC</sub> <sup>(3)</sup>  | _                 | V <sub>CC</sub> + 0.5  | V      |

| V <sub>IH2</sub>                         | Input High-voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | RESET                                                          | 0.85 V <sub>CC</sub> <sup>(3)</sup> | -                 | V <sub>CC</sub> + 0.5  | V      |

| V <sub>IL</sub>                          | Low-level Input Voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | CMOS                                                           | -0.3                                | -                 | 30% V <sub>CC</sub>    | V      |

| V <sub>IL1</sub>                         | Input Low-voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | XTAL                                                           | -0.5                                | -                 | 0.1 <sup>(2)</sup>     | V      |

|                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | $I_{OH} = 4 \text{ mA}$<br>$V_{CC} = V_{CC}$ Minimum           | 2.1                                 | -                 | -                      | V      |

| V <sub>OH</sub> High-level Outpu         | High-level Output Voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | $I_{OH} = 12 \text{ mA}$<br>$V_{CC} = 3.0 \text{V}$            | 2.1                                 | -                 | _                      | V      |

|                                          | High-level Input VoltageInput High-voltageInput High-voltageLow-level Input VoltageInput Low-voltageHigh-level Output VoltageHigh-level Output VoltageLow-level Output VoltageLow-level Output VoltageInput Low-voltageInput Low-voltageHigh-level Output VoltageInput Low-level Output VoltageInput Low-level Output VoltageInput Low-level Output VoltageInput Low-level Input CurrentInput Low-level Input CurrentInput Low-level Input CurrentInput Leakage CurrentInput Leakage CurrentPower Supply CurrentPower Supply Current | $I_{OH} = 16 \text{ mA}$<br>$V_{CC} = 3.0 \text{V}$            | 2.1                                 | -                 | -                      | V      |

|                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | $I_{OL} = -4 \text{ mA}$<br>$V_{CC} = 3.0 \text{V}$            | -                                   | -                 | 0.4                    | V      |