# E·XFL

#### Atmel - AT94K10AL-25DQU Datasheet

Welcome to E-XFL.COM

#### Embedded - FPGAs (Field Programmable Gate Array) with Microcontrollers: Enhancing Flexibility and Performance

#### Embedded - FPGAs (Field Programmable Gate

**Arrays) with Microcontrollers** represent a cutting-edge category of electronic components that combine the flexibility of FPGA technology with the processing power of integrated microcontrollers. This hybrid approach offers a versatile solution for designing and implementing complex digital systems that require both programmable logic and embedded processing capabilities.

#### What Are Embedded - FPGAs with Microcontrollers?

At their care EDCAR are comicanductor devices that can

#### Details

| Details                 |                                                            |

|-------------------------|------------------------------------------------------------|

| Product Status          | Active                                                     |

| Core Type               | 8-Bit AVR                                                  |

| Speed                   | 25 MHz                                                     |

| Interface               | I <sup>2</sup> C, UART                                     |

| Program SRAM Bytes      | 20K-32K                                                    |

| FPGA SRAM               | 4kb                                                        |

| EEPROM Size             | -                                                          |

| Data SRAM Bytes         | 4K ~ 16K                                                   |

| FPGA Core Cells         | 576                                                        |

| FPGA Gates              | 10К                                                        |

| FPGA Registers          | 846                                                        |

| Voltage - Supply        | 3V ~ 3.6V                                                  |

| Mounting Type           | Surface Mount                                              |

| Operating Temperature   | -40°C ~ 85°C                                               |

| Package / Case          | 208-BFQFP                                                  |

| Supplier Device Package | 208-PQFP (28x28)                                           |

| Purchase URL            | https://www.e-xfl.com/product-detail/atmel/at94k10al-25dqu |

|                         |                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### Clocking and Set/Reset

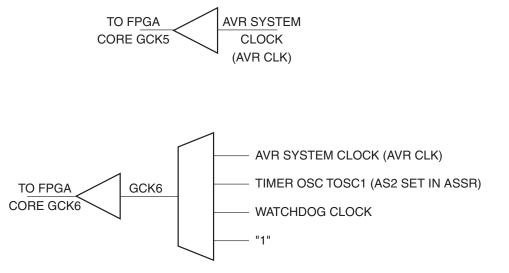

Six of the eight dedicated Global Clock buses (1, 2, 3, 4, 7 and 8) are connected to a dual-use Global Clock pin. In addition, two Global Clock buses (5 and 6) are driven from clock signals generated within the AVR microcontroller core, see Figure 11.

An FPGA core internal signal can be placed on any Global Clock bus by routing that signal to a Global Clock access point in the corners of the embedded core. Each column of the array has a Column Clock selected from one of the eight Global Clock buses. The left edge Column Clock mux has two additional inputs from dual-use pins FCK1, see Figure 8, and FCK2 to provide fast clocking to left-side I/O. Each sector column of four cells can be clocked from a (Plane 4) express bus or from the Column Clock. Clocking to the 4 cells of a sector can be disabled. The Plane 4 express bus used for clocking is half length at the array edge. The clock provided to each sector column of four cells can be either inverted or not inverted. The register in each cell is triggered on a rising clock edge. On power-up, constant "0" is provided to each register's clock pins. A dedicated Global Set/Reset bus, see Figure 9, can be driven by any USER I/O pad, except those used for clocking, Global or Fast. An internal signal can be placed on the Global Set/Reset bus by routing that signal to the pad programmed as the Global Set/Reset input. Global Set/Reset is distributed to each column of the array. Each sector column of four cells can be Set/Reset by a (Plane 5) express bus or by the Global Set/Reset. The Plane 5 express bus used for Set/Reset is half length at array edge. The Set/Reset provided to each sector column of four cells can be either inverted or not inverted. The function of the Set/Reset input of a register (either Set or Reset) is determined by a configuration bit for each cell. The Set/Reset input of a register is Active Low (logic 0). Setting or resetting of a register is asynchronous. On power-up, a logic 1 (High) is provided by each register, i.e., all registers are set at power-up.

| Address Range                      | SRAM     | Comments                                   |  |  |

|------------------------------------|----------|--------------------------------------------|--|--|

| \$07FF – \$0000<br>\$0FFF – \$0800 | 00<br>01 | AVR Data Read/Write<br>AVR Data Read/Write |  |  |

| \$17FF – \$1000<br>\$1FFF – \$1800 | 02<br>03 | CR41:40 = 11,10,01                         |  |  |

| \$27FF – \$2000<br>\$2FFF – \$2800 | 04<br>05 | CR41:40 = 11,10                            |  |  |

| \$37FF – \$3000<br>\$3FFF – \$3800 | 06<br>07 | CR41:40 = 11                               |  |  |

#### Table 6. AVR Data Decode for SRAM 0:17 (16K8)

B Side

The B side is not partitioned; the FPGA (and AVR debug mode) views the memory space as 36 x 8 Kbytes.

- The B side is accessed by the FPGA/Configuration Logic.

- The B side is accessed by the AVR with ST and LD instructions in DBG mode for code self-modify.

To activate the debug mode and allow the AVR to access the program code space (with ST - see Figure 21 – and LD – see Figure 22 – instructions), the DBG bit (bit 1) of the SFTCR \$3A (\$5A) register has to be set. When this bit is set, SCR36 and SCR37 are ignored – you can overwrite anything in the AVR program memory.

The FPGA memory access interface should be disabled while in debug mode. This is to ensure that there is no contention between the FPGA address and data signals and the AVR-generated address and data signals. To ensure the AVR has control over the "B side" memory interface, the FMXOR bit (bit 3) of the SFTCR \$3A (\$5A) register should be used in conjunction with the SCR63 system control register bit.

The FMXOR bit is XORed with the System Control Register's Enable FPGA SRAM Interface bit (SCR63). The behavior when this bit is set to 1 is dependent on how the SCR was initialized. If the Enable FPGA SRAM Interface bit (SCR63) in the SCR is 0, the FMXOR bit enables the FPGA SRAM Interface when set to 1. If the Enable FPGA SRAM Interface bit in the SCR is 1, the FMXOR bit disables the FPGA SRAM Interface when set to 1. During AVR reset, the FMXOR bit is cleared by the hardware.

Even though the FPGA (and AVR debug mode) views the memory space as 36 x 8 Kbytes, an awareness of the 2K x 8 partitions (or SRAM labels) is required if Frame (and AVR debug mode) read/writes are to be meaningful to the AVR.

- AVR data to FPGA addressing is 1:1 mapping.

- AVR program to FPGA addressing requires 16-bit to 8-bit mapping and an understanding of the partitions in Table 7.

| SRAM              | FPGA and AVR DBG<br>Address Range | AVR Data<br>Address Range | AVR PC Address Range      |

|-------------------|-----------------------------------|---------------------------|---------------------------|

| 00                | \$0000 - \$07FF                   | \$0000 - \$07FF           |                           |

| 01                | \$0800 - \$0FFF                   | \$0800 - \$0FFF           |                           |

| 02 <sup>(1)</sup> | \$1000 - \$17FF                   | \$1000 - \$17FF           | \$3800 - \$3FFF (LS Byte) |

| 03 <sup>(1)</sup> | \$1800 - \$1FFF                   | \$1800 - \$1FFF           | \$3800 - \$3FFF (MS Byte) |

| 04 <sup>(1)</sup> | \$2000 - \$27FF                   | \$2000 - \$27FF           | \$3000 - \$37FF (LS Byte) |

#### Table 7. Summary Table for AVR and FPGA SRAM Addressing

| Bit           | Description                                                                                                                                                                                                                                                                                                                          |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SCR56         | 0 = Disable XTAL Pin (R <sub>feedback</sub> )<br>1 = Enable XTAL Pin (R <sub>feedback</sub> )                                                                                                                                                                                                                                        |

| SCR57         | 0 = Disable TOSC2 Pin (R <sub>feedback</sub> )<br>1 = Enable TOSC2 Pin (R <sub>feedback</sub> )                                                                                                                                                                                                                                      |

| SCR58 - SCR59 | Reserved                                                                                                                                                                                                                                                                                                                             |

| SCR60 - SCR61 | SCR61 = 0, SCR60 = 0 "1"<br>SCR61 = 0, SCR60 = 1 AVR System Clock<br>SCR61 = 1, SCR60 = 0 Timer Oscillator Clock (TOSC1) <sup>(1)</sup><br>SCR61 = 1, SCR60 = 1 Watchdog Clock<br>Global Clock 6 mux select (set by using the AT94K Device Options in System<br>Designer).<br>Note: 1. The AS2 bit must be set in the ASSR register. |

| SCR62         | 0 = Disable CacheLogic Writes to FPGA by AVR<br>1 = Enable CacheLogic Writes to FPGA by AVR                                                                                                                                                                                                                                          |

| SCR63         | 0 = Disable Access (Read and Write) to SRAM by FPGA<br>1 = Enable Access (Read and Write) to SRAM by FPGA                                                                                                                                                                                                                            |

Table 11. FPSLIC System Control Register

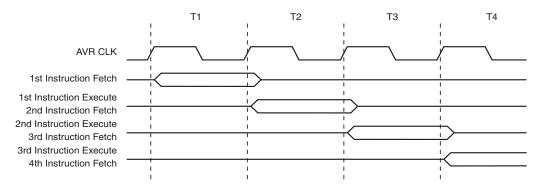

Figure 29. The Parallel Instruction Fetches and Instruction Executions

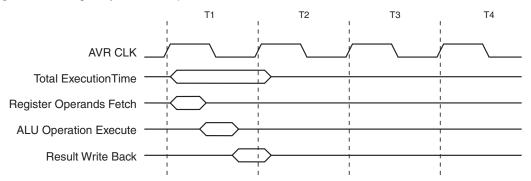

Figure 30 shows the internal timing concept for the register file. In a single clock cycle an ALU operation using two register operands is executed, and the result is stored back to the destination register.

Figure 30. Single Cycle ALU Operation

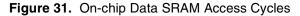

The internal data SRAM access is performed in two system clock cycles as described in Figure 31.

External Interrupt Mask/Flag Register – EIMF

| Bit           | 7     | 6     | 5     | 4     | 3    | 2    | 1    | 0    | _    |

|---------------|-------|-------|-------|-------|------|------|------|------|------|

| \$3B (\$5B)   | INTF3 | INTF2 | INTF1 | INTF0 | INT3 | INT2 | INT1 | INT0 | EIMF |

| Read/Write    | R/W   | R/W   | R/W   | R/W   | R/W  | R/W  | R/W  | R/W  |      |

| Initial Value | 0     | 0     | 0     | 0     | 0    | 0    | 0    | 0    |      |

#### • Bits 3..0 - INT3, 2, 1, 0: External Interrupt Request 3, 2, 1, 0 Enable

When an INT3 - INT0 bit is set (one) and the I-bit in the Status Register (SREG) is set (one), the corresponding external pin interrupt is enabled. The external interrupts are always negative edge triggered interrupts, see "Sleep Modes" on page 66.

#### • Bits 7..4 - INTF3, 2, 1, 0: External Interrupt 3, 2, 1, 0 Flags

When a falling edge is detected on the INT3, 2, 1, 0 pins, an interrupt request is triggered. The corresponding interrupt flag, INTF3, 2, 1, 0 becomes set (one). If the I-bit in SREG and the corresponding interrupt enable bit, INT3, 2, 1, 0 in EIMF, are set (one), the MCU will jump to the interrupt vector. The flag is cleared when the interrupt routine is executed. Alternatively, the flag is cleared by writing a logic 1 to it.

#### Timer/Counter Interrupt Mask Register – TIMSK

| Bit           | 7     | 6      | 5      | 4     | 3      | 2     | 1     | 0     | _     |

|---------------|-------|--------|--------|-------|--------|-------|-------|-------|-------|

| \$39 (\$39)   | TOIE1 | OCIE1A | OCIE1B | TOIE2 | TICIE1 | OCIE2 | TOIE0 | OCIE0 | TIMSK |

| Read/Write    | R/W   | R/W    | R/W    | R/W   | R/W    | R/W   | R/W   | R/W   | _     |

| Initial Value | 0     | 0      | 0      | 0     | 0      | 0     | 0     | 0     |       |

#### • Bit 7 - TOIE1: Timer/Counter1 Overflow Interrupt Enable

When the TOIE1 bit is set (one) and the I-bit in the Status Register is set (one), the Timer/Counter1 Overflow interrupt is enabled. The corresponding interrupt is executed if an overflow in Timer/Counter1 occurs, i.e., when the TOV1 bit is set in the Timer/Counter Interrupt Flag Register – TIFR.

#### • Bit 6 - OCIE1A: Timer/Counter1 Output CompareA Match Interrupt Enable

When the OCIE1A bit is set (one) and the I-bit in the Status Register is set (one), the Timer/Counter1 CompareA Match interrupt is enabled. The corresponding interrupt is executed if a CompareA match in Timer/Counter1 occurs, i.e., when the OCF1A bit is set in the Timer/Counter Interrupt Flag Register – TIFR.

#### • Bit 5 - OCIE1B: Timer/Counter1 Output CompareB Match Interrupt Enable

When the OCIE1B bit is set (one) and the I-bit in the Status Register is set (one), the Timer/Counter1 CompareB Match interrupt is enabled. The corresponding interrupt is executed if a CompareB match in Timer/Counter1 occurs, i.e., when the OCF1B bit is set in the Timer/Counter Interrupt Flag Register – TIFR.

#### • Bit 4 - TOIE2: Timer/Counter2 Overflow Interrupt Enable

When the TOIE2 bit is set (one) and the I-bit in the Status Register is set (one), the Timer/Counter2 overflow interrupt is enabled. The corresponding interrupt is executed if an overflow in Timer/Counter2 occurs, i.e., when the TOV2 bit is set in the Timer/Counter interrupt flag register – TIFR.

#### • Bit 3 - TICIE1: Timer/Counter1 Input Capture Interrupt Enable

When the TICIE1 bit is set (one) and the I-bit in the Status Register is set (one), the Timer/Counter1 input capture event interrupt is enabled. The corresponding interrupt is executed if a capture-triggering event occurs on pin 29, (IC1), i.e., when the ICF1 bit is set in the Timer/Counter interrupt flag register – TIFR.

#### Timer/Counter1 Control Register A – TCCR1A

| Bit           | 7      | 6      | 5      | 4      | 3     | 2     | 1     | 0     |        |

|---------------|--------|--------|--------|--------|-------|-------|-------|-------|--------|

| \$2F (\$4F)   | COM1A1 | COM1A0 | COM1B1 | COM1B0 | FOC1A | FOC1B | PWM11 | PWM10 | TCCR1A |

| Read/Write    | R/W    | R/W    | R/W    | R/W    | R/w   | R/W   | R/W   | R/W   | -      |

| Initial Value | 0      | 0      | 0      | 0      | 0     | 0     | 0     | 0     |        |

#### • Bits 7,6 - COM1A1, COM1A0: Compare Output Mode1A, Bits 1 and 0

The COM1A1 and COM1A0 control bits determine any output pin action following a compare match in Timer/Counter1. Any output pin actions affect pin OC1A – Output CompareA pin PE6. This is an alternative function to an I/O port, and the corresponding direction control bit must be set (one) to control an output pin. The control configuration is shown in Table 27.

#### • Bits 5,4 - COM1B1, COM1B0: Compare Output Mode1B, Bits 1 and 0

The COM1B1 and COM1B0 control bits determine any output pin action following a compare match in Timer/Counter1. Any output pin actions affect pin OC1B – Output CompareB pin PE5. This is an alternative function to an I/O port, and the corresponding direction control bit must be set (one) to control an output pin. The following control configuration is given:

| Table 27. | Cor | npare | 1 Mode | Select <sup>(1)</sup> |

|-----------|-----|-------|--------|-----------------------|

|           |     |       |        |                       |

| COM1X1 <sup>(2)</sup> | COM1X0 <sup>(2)</sup> | Description                                      |

|-----------------------|-----------------------|--------------------------------------------------|

| 0                     | 0                     | Timer/Counter1 disconnected from output pin OC1X |

| 0                     | 1                     | Toggles the OC1X output line                     |

| 1                     | 0                     | Clears the OC1X output line (to zero)            |

| 1                     | 1                     | Sets the OC1X output line (to one)               |

Notes: 1. In PWM mode, these bits have a different function. Refer to Table 31 for a detailed description.

#### • Bit 3 - FOC1A: Force Output Compare1A

Writing a logic 1 to this bit forces a change in the compare match output pin PE6 according to the values already set in COM1A1 and COM1A0. If the COM1A1 and COM1A0 bits are written in the same cycle as FOC1A, the new settings will not take effect until next compare match or forced compare match occurs. The Force Output Compare bit can be used to change the output pin without waiting for a compare match in the timer. The automatic action programmed in COM1A1 and COM1A0 happens as if a Compare Match had occurred, but no interrupt is generated and it will not clear the timer even if CTC1 in TCCR1B is set. The FOC1A bit will always be read as zero. The setting of the FOC1A bit has no effect in PWM mode.

#### • Bit 2 - FOC1B: Force Output Compare1B

Writing a logic 1 to this bit forces a change in the compare match output pin PE5 according to the values already set in COM1B1 and COM1B0. If the COM1B1 and COM1B0 bits are written in the same cycle as FOC1B, the new settings will not take effect until next compare match or forced compare match occurs. The Force Output Compare bit can be used to change the output pin without waiting for a compare match in the timer. The automatic action programmed in COM1B1 and COM1B0 happens as if a Compare Match had occurred, but no interrupt is generated. The FOC1B bit will always be read as zero. The setting of the FOC1B bit has no effect in PWM mode.

<sup>2.</sup> X = A or B

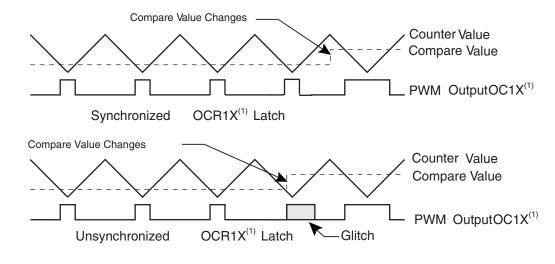

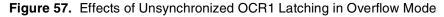

Figure 56. Effects on Unsynchronized OCR1 Latching

Note: 1. X = A or B

Note: 1. X = A or B

During the time between the write and the latch operation, a read from OCR1A or OCR1B will read the contents of the temporary location. This means that the most recently written value always will read out of OCR1A/B.

When the OCR1X contains \$0000 or TOP, and the up/down PWM mode is selected, the output OC1A/OC1B is updated to Low or High on the next compare match according to the settings of COM1A1/COM1A0 or COM1B1/COM1B0. This is shown in Table 32. In overflow PWM mode, the output OC1A/OC1B is held Low or High only when the Output Compare Register contains TOP.

#### Implementations

mul16x16\_16

#### Description

Multiply of two 16-bit numbers with a 16-bit result.

#### Usage

R17:R16 = R23:R22 • R21:R20

#### Statistics

Cycles: 9 + ret

```

Words: 6 + ret

```

Register usage: R0, R1 and R16 to R23 (8 registers)<sup>(1)</sup>

Note: 1. Full orthogonality, i.e., any register pair can be used as long as the result and the two operands do not share register pairs. The routine is non-destructive to the operands.

mull6x16\_16:

```

mul r22, r20 ; al * bl

movw r17:r16, r1:r0

mul r23, r20 ; ah * bl

add r17, r0

mul r21, r22 ; bh * al

add r17, r0

ret

```

mul16x16\_32

#### Description

Unsigned multiply of two 16-bit numbers with a 32-bit result.

#### Usage

R19:R18:R17:R16 = R23:R22 • R21:R20

#### Statistics

Cycles: 17 + ret

```

Words: 13 + ret

```

Register usage: R0 to R2 and R16 to R23 (11 registers)<sup>(1)</sup>

Note: 1. Full orthogonality, i.e., any register pair can be used as long as the result and the two operands do not share register pairs. The routine is non-destructive to the operands.

```

mul16x16_32:

```

```

clr r2

mul r23, r21

; ah * bh

movw r19:r18, r1:r0

r22, r20

; al * bl

mul

movw r17:r16, r1:r0

r23, r20

; ah * bl

mul

add r17, r0

adc

r18, r1

r19, r2

adc

m11]

r21, r22

; bh * al

r17, r0

add

adc

r18, r1

r19, r2

adc

ret

```

# **AT94KAL Series FPSLIC**

Table 37. UBR Settings at Various Crystal Frequencies in Double UART Speed Mode

| Actual<br>UBR Freq<br>95 2400<br>47 4800<br>23 9600<br>15 14400<br>11 19200<br>7 28800<br>5 38400<br>3 57600<br>2 76800<br>1 115200<br>1 115200<br>UBR Freq<br>959 2400<br>479 4800 | Freq. E<br>2400 (<br>4800 (<br>9600 (<br>14400 (<br>19200 (<br>28880 (<br>38400 (<br>57600 (<br>76800 (<br>0 115200 (                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 47 4800<br>23 9600<br>15 14400<br>11 19200<br>7 28800<br>5 38400<br>3 57600<br>2 76800<br>1 115200<br>UBR Freq<br>959 2400                                                          | 4800 (<br>9600 (<br>14400 (<br>28880 (<br>38400 (<br>57600 (<br>76800 (<br>115200 (<br>Freq. E                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 23 9600<br>15 14400<br>11 19200<br>7 28800<br>5 38400<br>3 57600<br>2 76800<br>1 115200<br>Actual<br>UBR Freq<br>959 2400                                                           | 9600 (<br>14400 (<br>19200 (<br>28880 (<br>38400 (<br>57600 (<br>76800 (<br>115200 (<br>Freq. E                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 15 14400<br>11 19200<br>7 28800<br>5 38400<br>3 57600<br>2 76800<br>1 115200<br>Actual<br>UBR Freq<br>959 2400                                                                      | ) 14400 (<br>) 19200 (<br>) 28880 (<br>) 38400 (<br>) 57600 (<br>) 76800 (<br>) 76800 (<br>) 115200 (<br>Freq. E                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 11 19200<br>7 28800<br>5 38400<br>3 57600<br>2 76800<br>1 115200<br>UBR Freq<br>959 2400                                                                                            | ) 19200 (<br>) 28880 (<br>) 38400 (<br>) 57600 (<br>) 76800 (<br>) 115200 (<br>) LDesired<br>Freq. E                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 7 28800<br>5 38400<br>3 57600<br>2 76800<br>1 115200<br>UBR Freq<br>959 2400                                                                                                        | 28880 (<br>38400 (<br>57600 (<br>76800 (<br>0 115200 (<br>Freq. E                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 5 38400<br>3 57600<br>2 76800<br>1 115200<br>UBR Freq<br>959 2400                                                                                                                   | 38400 (<br>57600 (<br>76800 (<br>0 115200 (<br>H Desired<br>Freq. E                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 3 57600<br>2 76800<br>1 115200<br>Actual<br>UBR Freq<br>959 2400                                                                                                                    | 57600 (<br>76800 (<br>0 115200 (<br>Desired<br>Freq. E                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 2 76800<br>1 11520<br>Actual<br>UBR Freq<br>959 2400                                                                                                                                | 76800 (<br>0 115200 (<br>Desired<br>Freq. E                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 1 115200<br>Actual<br>UBR Freq<br>959 2400                                                                                                                                          | D 115200 (<br>Desired<br>Freq. E                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| UBR Freq<br>959 2400                                                                                                                                                                | Freq. E                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| UBR Freq<br>959 2400                                                                                                                                                                | Freq. E                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 959 2400                                                                                                                                                                            | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 479 4800                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                                                                                                                                                                     | 4800 (                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 239 9600                                                                                                                                                                            | 9600 (                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 159 14400                                                                                                                                                                           | 14400 (                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 119 19200                                                                                                                                                                           | 19200 (                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 79 28800                                                                                                                                                                            | 28880 (                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 59 38400                                                                                                                                                                            | 38400 (                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 2 76800                                                                                                                                                                             | <b>0</b> 912600 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Actua                                                                                                                                                                               | Desired                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| UBR Freq                                                                                                                                                                            | Freq. E                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 2082 2400                                                                                                                                                                           | 2400 (                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 1041 4798                                                                                                                                                                           | 4800 (                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 520 9597                                                                                                                                                                            | 9600 (                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 346 14409                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                                                                                                                                                                     | 5 460800 <sup>-</sup><br>0 912600 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                                                                                                                                                                     | 119         19200           79         28800           59         38400           39         57600           29         76800           19         115200           9         230400           4         460800           2         768000           2         768000           2         768000           2         768000           2         768000           2         768000           2         768000           2         768000           2         768000           2         768000           2         768000           2         768000           2         768000           2         768000           2         768000           2         768000           2         9597           346         14409           259         19231           172         28902           129         38462           86         57471           64         76923           42         116275           21         227273 |

#### • Bits 7..0 - 2-wire Serial Bit-rate Register

TWBR selects the division factor for the bit-rate generator. The bit-rate generator is a frequency divider which generates the SCL clock frequency in the Master modes according to the following equation:

Bit-rate =

$$\frac{f_{CK}}{16 + 2(TWBR)}$$

- Bit-rate = SCL frequency

- f<sub>CK</sub> = CPU Clock frequency

- TWBR = Contents of the 2-wire Serial Bit Rate Register

Both the receiver and the transmitter can stretch the Low period of the SCL line when waiting for user response, thereby reducing the average bit rate.

#### The 2-wire Serial Control Register – TWCR

| Bit           | 7     | 6    | 5     | 4     | 3    | 2    | 1 | 0    |      |

|---------------|-------|------|-------|-------|------|------|---|------|------|

| \$36 (\$56)   | TWINT | TWEA | TWSTA | TWSTO | TWWC | TWEN | - | TWIE | TWCR |

| Read/Write    | R/W   | R/W  | R/W   | R/W   | R    | R/W  | R | R/W  | -    |

| Initial Value | 0     | 0    | 0     | 0     | 0    | 0    | 0 | 0    |      |

• Bit 7 - TWINT: 2-wire Serial Interrupt Flag

This bit is set by the hardware when the 2-wire Serial Interface has finished its current job and expects application software response. If the I-bit in the SREG and TWIE in the TWCR register are set (one), the MCU will jump to the interrupt vector at address \$0046. While the TWINT flag is set, the bus SCL clock line Low period is stretched. The TWINT flag must be cleared by software by writing a logic 1 to it. Note that this flag is not automatically cleared by the hardware when executing the interrupt routine. Also note that clearing this flag starts the operation of the 2-wire Serial Interface, so all accesses to the 2-wire Serial Address Register – TWAR, 2-wire Serial Status Register – TWSR, and 2-wire Serial Data Register – TWDR must be complete before clearing this flag.

#### • Bit 6 - TWEA: 2-wire Serial Enable Acknowledge Flag

TWEA flag controls the generation of the acknowledge pulse. If the TWEA bit is set, the ACK pulse is generated on the 2-wire Serial Bus if the following conditions are met:

- The device's own Slave address has been detected

- A general call has been received, while the TWGCE bit in the TWAR is set

- A data byte has been received in Master Receiver or Slave Receiver mode

By setting the TWEA bit Low the device can be virtually disconnected from the 2-wire Serial Bus temporarily. Address recognition can then be resumed by setting the TWEA bit again.

#### • Bit 5 - TWSTA: 2-wire Serial Bus START Condition Flag

The TWSTA flag is set by the CPU when it desires to become a Master on the 2-wire Serial Bus. The 2-wire serial hardware checks if the bus is available, and generates a Start condition on the bus if the bus is free. However, if the bus is not free, the 2-wire Serial Interface waits until a STOP condition is detected, and then generates a new Start condition to claim the bus Master status.

#### 2-wire Serial Modes

The 2-wire Serial Interface can operate in four different modes:

- Master Transmitter

- Master Receiver

- Slave Receiver

- Slave Transmitter

Data transfer in each mode of operation is shown in Figure 71 to Figure 74. These figures contain the following abbreviations:

S: START condition

R: Read bit (High level at SDA)

W: Write bit (Low level at SDA)

A: Acknowledge bit (Low level at SDA)

A: Not acknowledge bit (High level at SDA)

Data: 8-bit data byte

P: STOP condition

In Figure 71 to Figure 74, circles are used to indicate that the 2-wire Serial Interrupt flag is set. The numbers in the circles show the status code held in TWSR. At these points, an interrupt routine must be executed to continue or complete the 2-wire Serial Transfer. The 2-wire Serial Transfer is suspended until the 2-wire Serial Interrupt flag is cleared by software.

The 2-wire Serial Interrupt flag is not automatically cleared by the hardware when executing the interrupt routine. Also note that the 2-wire Serial Interface starts execution as soon as this bit is cleared, so that all access to TWAR, TWDR and TWSR must have been completed before clearing this flag.

When the 2-wire Serial Interrupt flag is set, the status code in TWSR is used to determine the appropriate software action. For each status code, the required software action and details of the following serial transfer are given in Table 41 to Table 45.

In the Master Transmitter mode, a number of data bytes are transmitter to a Slave Receiver, see Figure 71. Before the Master Transmitter mode can be entered, the TWCR must be initialized as shown in Table 38.

Table 38. TWCR: Master Transmitter Mode Initialization

| TWCR  | TWINT | TWEA | TWSTA | TWSTO | TWWC | TWEN | - | TWIE |

|-------|-------|------|-------|-------|------|------|---|------|

| value | 0     | Х    | 0     | 0     | 0    | 1    | 0 | Х    |

TWEN must be set to enable the 2-wire Serial Interface, TWSTA and TWSTO must be cleared.

The Master Transmitter mode may now be entered by setting the TWSTA bit. The 2-wire Serial Logic will now test the 2-wire Serial Bus and generate a START condition as soon as the bus becomes free. When a START condition is transmitted, the 2-wire Serial Interrupt flag (TWINT) is set by the hardware, and the status code in TWSR will be \$08. TWDR must then be loaded with the Slave address and the data direction bit (SLA+W). The TWINT flag must then be cleared by software before the 2-wire Serial Transfer can continue. The TWINT flag is cleared by writing a logic 1 to the flag.

When the Slave address and the direction bit have been transmitted and an acknowledgment bit has been received, TWINT is set again and a number of status codes in TWSR are possible. Status codes \$18, \$20, or \$38 apply to Master mode, and status codes \$68, \$78, or \$B0 apply to Slave mode. The appropriate action to be taken for each of these status codes is

Master

Transmitter Mode

| Δ | <u>mel</u> |

|---|------------|

#### Table 42. Status Codes for Master Receiver Mode

|                |                                               | Application Software Response |                              |    |          |   |                                                                                                     |

|----------------|-----------------------------------------------|-------------------------------|------------------------------|----|----------|---|-----------------------------------------------------------------------------------------------------|

| Status<br>Code | Status of the 2-wire<br>Serial Bus and 2-wire |                               |                              | То | TWCR     |   | Next Action Taken by 2-wire Serial                                                                  |

| (TWSR)         | Serial Hardware                               | To/From TWDR                  | From TWDR STA STO TWINT TWEA |    | Hardware |   |                                                                                                     |

| \$08           | A START condition has been transmitted        | Load SLA+R                    | х                            | 0  | 1        | Х | SLA+R will be transmitted<br>ACK or NOT ACK will be received                                        |

| \$10           | A repeated START condition has been           | Load SLA+R or                 | х                            | 0  | 1        | X | SLA+R will be transmitted<br>ACK or NOT ACK will be received                                        |

|                | transmitted                                   | Load SLA+W                    | x                            | 0  | 1        | x | SLA+W will be transmitted<br>Logic will switch to Master Transmitter mode                           |

| \$38           | Arbitration lost in<br>SLA+R or NOT ACK bit   | No TWDR action or             | 0                            | 0  | 1        | X | 2-wire serial bus will be released and not<br>addressed Slave mode will be entered                  |

|                |                                               | No TWDR action                | 1                            | 0  | 1        | x | A START condition will be transmitted when the bus becomes free                                     |

| \$40           | SLA+R has been<br>transmitted;                | No TWDR action or             | 0                            | 0  | 1        | 0 | Data byte will be received and NOT ACK will<br>be returned                                          |

|                | ACK has been received                         | No TWDR action                | 0                            | 0  | 1        | 1 | Data byte will be received and ACK will be returned                                                 |

| \$48           | SLA+R has been                                | No TWDR action or             | 1                            | 0  | 1        | x | Repeated START will be transmitted                                                                  |

|                | transmitted;<br>NOT ACK has been              | No TWDR action or             | 0                            | 1  | 1        | X | STOP condition will be transmitted and<br>TWSTO flag will be reset                                  |

|                | received                                      | No TWDR action                | 1                            | 1  | 1        | X | STOP condition followed by a START<br>condition will be transmitted and TWSTO flag<br>will be reset |

| \$50           | Data byte has been received;                  | Read data byte or             | 0                            | 0  | 1        | 0 | Data byte will be received and NOT ACK will be returned                                             |

|                | ACK has been returned                         | Read data byte                | 0                            | 0  | 1        | 1 | Data byte will be received and ACK will be returned                                                 |

| \$58           | Data byte has been                            | Read data byte or             | 1                            | 0  | 1        | x | Repeated START will be transmitted                                                                  |

|                | received;<br>NOT ACK has been                 | Read data byte or             | 0                            | 1  | 1        | x | STOP condition will be transmitted and<br>TWSTO flag will be reset                                  |

|                | returned                                      | Read data byte                | 1                            | 1  | 1        | X | STOP condition followed by a START<br>condition will be transmitted and TWSTO flag<br>will be reset |

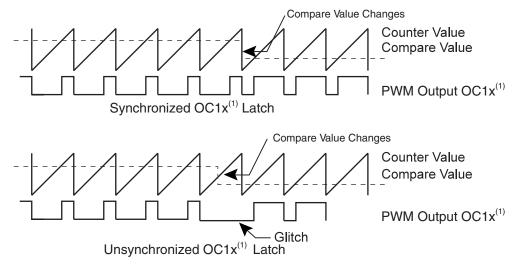

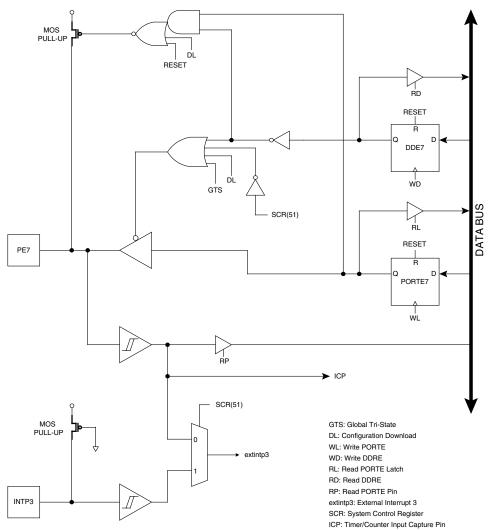

Figure 77. PortE Schematic Diagram (Pin PE1)

Figure 82. PortE Schematic Diagram (Pin PE7)

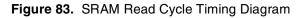

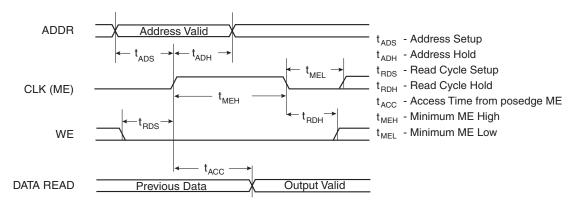

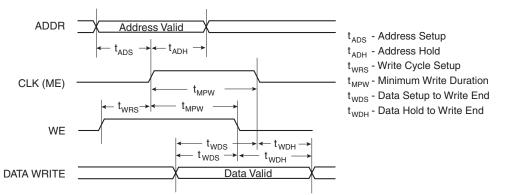

### FPSLIC Dual-port SRAM Characteristics

The Dual-port SRAM operates in single-edge clock controlled mode during read operations, and a double-edge controlled mode during write operations. Addresses are clocked internally on the rising edge of the clock signal (ME). Any change of address without a rising edge of ME is not considered.

In read mode, the rising clock edge triggers data read without any significant constraint on the length of the clock pulse. The WE signal must be changed and held Low before the rising edge of ME to signify a read cycle. The WE signal should then remain Low until the falling edge of the clock.

In write mode, data applied to the inputs is latched on either the falling edge of WE or the falling edge of the clock, whichever comes earlier, and written to memory. Also, WE must be High before the rising edge of ME to signify a write cycle. If data inputs change during a write cycle, only the value present at the write end is considered and written to the address clocked at the ME rise. A write cycle ending on WE fall does not turn into a read cycle – the next cycle will be a read cycle if WE remains Low during rising edge of ME.

#### **Frame Interface**