Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                 |

| Core Processor             | HC08                                                                     |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 8MHz                                                                     |

| Connectivity               | CANbus, SCI, SPI                                                         |

| Peripherals                | LVD, POR, PWM                                                            |

| Number of I/O              | 37                                                                       |

| Program Memory Size        | 60KB (60K x 8)                                                           |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 2K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                |

| Data Converters            | A/D 24x10b                                                               |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 48-LQFP                                                                  |

| Supplier Device Package    | 48-LQFP (7x7)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc68hc908gz60cfa |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **List of Chapters**

| Chapter 1 General Description                                     | 23  |

|-------------------------------------------------------------------|-----|

| Chapter 2 Memory                                                  | 33  |

| Chapter 3 Analog-to-Digital Converter (ADC)                       | 61  |

| Chapter 4 Clock Generator Module (CGM)                            |     |

| Chapter 5 Configuration Register (CONFIG)                         | 91  |

| Chapter 6 Computer Operating Properly (COP) Module                | 95  |

| Chapter 7 Central Processor Unit (CPU)                            |     |

| Chapter 8 External Interrupt (IRQ)                                | 111 |

| Chapter 9 Keyboard Interrupt Module (KBI)                         | 115 |

| Chapter 10 Low-Power Modes                                        | 123 |

| Chapter 11 Low-Voltage Inhibit (LVI)                              | 131 |

| Chapter 12 MSCAN08 Controller (MSCAN08)                           | 135 |

| Chapter 13 Input/Output (I/O) Ports                               | 169 |

| Chapter 14 Enhanced Serial Communications Interface (ESCI) Module | 189 |

| Chapter 15 System Integration Module (SIM)                        | 221 |

| Chapter 16 Serial Peripheral Interface (SPI) Module               | 239 |

| Chapter 17 Timebase Module (TBM)                                  | 259 |

| Chapter 18 Timer Interface Module (TIM1)                          | 263 |

| Chapter 19 Timer Interface Module (TIM2)                          | 279 |

| Chapter 20 Development Support                                    | 299 |

| Chapter 21 Electrical Specifications                              | 315 |

| Chapter 22 Ordering Information and Mechanical Specifications     |     |

| Appendix A MC68HC908GZ48                                          | 343 |

| Appendix B MC68HC908GZ32                                          | 347 |

MC68HC908GZ60 • MC68HC908GZ48 • MC68HC908GZ32 Data Sheet, Rev. 6

# **Table of Contents**

# Chapter 1 General Description

| 1.1              | Introduction                                                                                                     | 23  |

|------------------|------------------------------------------------------------------------------------------------------------------|-----|

| 1.2              | Features                                                                                                         | 23  |

| 1.2.1            | Standard Features                                                                                                | 23  |

| 1.2.2            | Features of the CPU08                                                                                            | 25  |

| 1.3              | MCU Block Diagram                                                                                                | 25  |

| 1.4              | Pin Assignments                                                                                                  | 25  |

| 1.5              | Pin Functions                                                                                                    | 28  |

| 1.5.1            | Power Supply Pins (V <sub>DD</sub> and V <sub>SS</sub> )                                                         | 28  |

| 1.5.2            | Oscillator Pins (OSC1 and OSC2)                                                                                  |     |

| 1.5.3            | External Reset Pin (RST).                                                                                        |     |

| 1.5.4            | External Interrupt Pin (IRQ)                                                                                     |     |

| 1.5.5            | CGM Power Supply Pins (V <sub>DDA</sub> and V <sub>SSA</sub> )                                                   |     |

| 1.5.6            | External Filter Capacitor Pin (CGMXFC)                                                                           |     |

| 1.5.7            | ADC Power Supply/Reference Pins (V <sub>DDAD</sub> /V <sub>REFH</sub> and V <sub>SSAD</sub> /V <sub>REFL</sub> ) |     |

| 1.5.8            | Port A Input/Output (I/O) Pins (PTA7/KBD7/AD15–PTA0/KBD0/AD8)                                                    |     |

| 1.5.9            | Port B I/O Pins (PTB7/AD7–PTB0/AD0)                                                                              |     |

| 1.5.10           | Port C I/O Pins (PTC6–PTC0/CANTX)                                                                                |     |

| 1.5.11           | Port D I/O Pins (PTD7/T2CH1–PTD0/ <del>SS</del> )                                                                |     |

| 1.5.12           | Port E I/O Pins (PTE5-PTE2, PTE1/RxD, and PTE0/TxD)                                                              |     |

| 1.5.13           | Port F I/O Pins (PTF7/T2CH5–PTF0)                                                                                |     |

| 1.5.14<br>1.5.15 | Port G I/O Pins (PTG7/AD23–PTBG0/AD16)                                                                           |     |

| 1.5.15           | Unused Pin Termination                                                                                           | J I |

|                  | Chapter 2                                                                                                        |     |

|                  | Memory                                                                                                           |     |

| 2.1              | Introduction                                                                                                     | 33  |

| 2.2              | Unimplemented Memory Locations                                                                                   | 33  |

| 2.3              | Reserved Memory Locations                                                                                        | 33  |

| 2.4              | Input/Output (I/O) Section                                                                                       | 33  |

| 2.5              | Random-Access Memory (RAM)                                                                                       | 45  |

| 2.6              | FLASH-1 Memory (FLASH-1)                                                                                         | 45  |

| 2.6.1            | Functional Description                                                                                           |     |

| 2.6.2            | FLASH-1 Control and Block Protect Registers                                                                      | 46  |

| 2.6.2.1          |                                                                                                                  |     |

| 2.6.2.2          | FLASH-1 Block Protect Register                                                                                   | 47  |

| 2.6.3            | FLASH-1 Block Protection                                                                                         |     |

| 2.6.4            | FLASH-1 Mass Erase Operation                                                                                     |     |

| 2.6.5            | FLASH-1 Page Erase Operation                                                                                     | 49  |

|                  |                                                                                                                  |     |

MC68HC908GZ60 • MC68HC908GZ48 • MC68HC908GZ32 Data Sheet, Rev. 6

| Addr.  | Register Name                                        |                 | Bit 7 | 6          | 5     | 4           | 3          | 2            | 1        | Bit 0 |

|--------|------------------------------------------------------|-----------------|-------|------------|-------|-------------|------------|--------------|----------|-------|

| \$0000 | Port A Data Register<br>(PTA)                        | Read:<br>Write: | PTA7  | PTA6       | PTA5  | PTA4        | PTA3       | PTA2         | PTA1     | PTA0  |

|        | See page 173.                                        | Reset:          |       |            |       | Unaffecte   | d by reset |              |          |       |

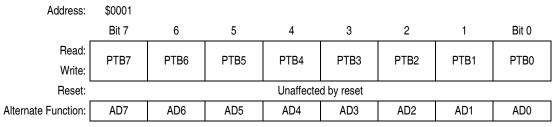

| \$0001 | Port B Data Register<br>(PTB)                        | Read:<br>Write: | PTB7  | PTB6       | PTB5  | PTB4        | PTB3       | PTB2         | PTB1     | PTB0  |

| 4000   | See page 176.                                        | Reset:          |       |            |       | Unaffecte   | d by reset |              |          |       |

|        | Port C Data Register                                 | Read:           | 1     | PTC6       | PTC5  | PTC4        | PTC3       | PTC2         | PTC1     | PTC0  |

| \$0002 | (PTC)<br>See page 178.                               | Write:          |       | 1100       | 1100  |             |            | 1102         | 1101     | 1100  |

|        | ooo page 17 o.                                       | Reset:          |       | 1          |       | Unaffecte   | d by reset |              | <u> </u> |       |

| \$0003 | Port D Data Register (PTD)                           | Read:<br>Write: | PTD7  | PTD6       | PTD5  | PTD4        | PTD3       | PTD2         | PTD1     | PTD0  |

|        | See page 180.                                        | Reset:          |       |            |       | Unaffecte   | d by reset |              |          |       |

| \$0004 | Data Direction Register A (DDRA)                     | Read:<br>Write: | DDRA7 | DDRA6      | DDRA5 | DDRA4       | DDRA3      | DDRA2        | DDRA1    | DDRA0 |

|        | See page 174.                                        | Reset:          | 0     | 0          | 0     | 0           | 0          | 0            | 0        | 0     |

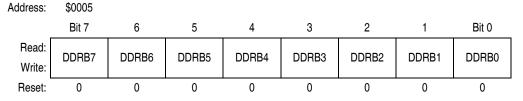

| \$0005 | Data Direction Register B<br>(DDRB)<br>See page 176. | Read:<br>Write: | DDRB7 | DDRB6      | DDRB5 | DDRB4       | DDRB3      | DDRB2        | DDRB1    | DDRB0 |

|        |                                                      | Reset:          | 0     | 0          | 0     | 0           | 0          | 0            | 0        | 0     |

| \$0006 | Data Direction Register C (DDRC)                     | Read:<br>Write: | 0     | DDRC6      | DDRC5 | DDRC4       | DDRC3      | DDRC2        | DDRC1    | DDRC0 |

| φοσσσ  | See page 178.                                        | Reset:          | 0     | 0          | 0     | 0           | 0          | 0            | 0        | 0     |

| \$0007 | Data Direction Register D (DDRD)                     | Read:<br>Write: | DDRD7 | DDRD6      | DDRD5 | DDRD4       | DDRD3      | DDRD2        | DDRD1    | DDRD0 |

|        | See page 181.                                        | Reset:          | 0     | 0          | 0     | 0           | 0          | 0            | 0        | 0     |

|        | Port E Data Register                                 | Read:           | 0     | 0          | PTE5  | PTE4        | PTE3       | PTE2         | PTE1     | PTE0  |

| \$0008 | (PTE)<br>See page 183.                               | Write:          |       |            | FIES  | FIE4        | FIES       | FILZ         | FIEI     | FILU  |

|        |                                                      | Reset:          |       |            |       | Unaffecte   | d by reset |              |          |       |

| \$0009 | ESCI Prescaler Register<br>(SCPSC)<br>See page 214.  | Read:<br>Write: | PDS2  | PDS1       | PDS0  | PSSB4       | PSSB3      | PSSB2        | PSSB1    | PSSB0 |

|        |                                                      | Reset:          | 0     | 0          | 0     | 0           | 0          | 0            | 0        | 0     |

|        | ESCI Arbiter Control                                 | Read:           | ΛΜ1   | ALOST      | AMO   | ACLK        | AFIN       | ARUN         | AROVFL   | ARD8  |

| \$000A | Register (SCIACTL)                                   | Write:          | AM1   |            | AM0   | ACLK        |            |              |          |       |

|        | See page 217.                                        | Reset:          | 0     | 0          | 0     | 0           | 0          | 0            | 0        | 0     |

|        | ESCI Arbiter Data                                    | Read:           | ARD7  | ARD6       | ARD5  | ARD4        | ARD3       | ARD2         | ARD1     | ARD0  |

| \$000B | Register (SCIADAT)                                   | Write:          |       |            |       |             |            |              |          |       |

|        | See page 218.                                        | Reset:          | 0     | 0          | 0     | 0           | 0          | 0            | 0        | 0     |

|        |                                                      |                 |       | = Unimplem | ented | R = Reserve | ed         | U = Unaffect | ted      |       |

Figure 2-2. Control, Status, and Data Registers (Sheet 1 of 9)

MC68HC908GZ60 • MC68HC908GZ48 • MC68HC908GZ32 Data Sheet, Rev. 6

# Memory

| Addr.  | Register Name                                                  |                 | Bit 7  | 6          | 5      | 4           | 3      | 2            | 1      | Bit 0  |

|--------|----------------------------------------------------------------|-----------------|--------|------------|--------|-------------|--------|--------------|--------|--------|

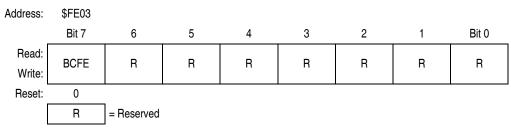

| \$FE03 | Break Flag Control Register<br>(BFCR)                          | Read:<br>Write: | BCFE   | R          | R      | R           | R      | R            | R      | R      |

|        | See page 238.                                                  | Reset:          | 0      | 0          | 0      | 0           | 0      | 0            | 0      | 0      |

|        | Interrupt Status Register 1                                    | Read:           | IF6    | IF5        | IF4    | IF3         | IF2    | IF1          | 0      | 0      |

| \$FE04 | (INT1)                                                         | Write:          | R      | R          | R      | R           | R      | R            | R      | R      |

|        | See page 231.                                                  | Reset:          | 0      | 0          | 0      | 0           | 0      | 0            | 0      | 0      |

|        | Interrupt Status Register 2                                    | Read:           | IF14   | IF13       | IF12   | IF11        | IF10   | IF9          | IF8    | IF7    |

| \$FE05 | (INT2)                                                         | Write:          | R      | R          | R      | R           | R      | R            | R      | R      |

|        | See page 233.                                                  | Reset:          | 0      | 0          | 0      | 0           | 0      | 0            | 0      | 0      |

|        | Interrupt Status Register 3                                    | Read:           | IF22   | IF21       | IF20   | IF19        | IF18   | IF17         | IF16   | IF15   |

| \$FE06 | (INT3)                                                         | Write:          | R      | R          | R      | R           | R      | R            | R      | R      |

|        | See page 233.                                                  | Reset:          | 0      | 0          | 0      | 0           | 0      | 0            | 0      | 0      |

|        | Interrupt Status Register 4                                    | Read:           | 0      | 0          | 0      | 0           | 0      | 0            | IF24   | IF23   |

| \$FE07 | (INT4)                                                         | Write:          | R      | R          | R      | R           | R      | R            | R      | R      |

|        | See page 233.                                                  | Reset:          | 0      | 0          | 0      | 0           | 0      | 0            | 0      | 0      |

|        | FLASH-2 Control Register<br>(FL2CR)<br>See page 53.            | Read:           | 0      | 0          | 0      | 0           | HVEN   | MASS         | ERASE  | PGM    |

| \$FE08 |                                                                | Write:          |        |            |        |             | IIVEIV | WIAGO        | LITAGE | 1 GIVI |

|        |                                                                | Reset:          | 0      | 0          | 0      | 0           | 0      | 0            | 0      | 0      |

| \$FE09 | Break Address Register High<br>(BRKH)<br>See page 303.         | Read:<br>Write: | Bit 15 | 14         | 13     | 12          | 11     | 10           | 9      | Bit 8  |

|        |                                                                | Reset:          | 0      | 0          | 0      | 0           | 0      | 0            | 0      | 0      |

| \$FE0A | Break Address Register Low (BRKL)                              | Read:<br>Write: | Bit 7  | 6          | 5      | 4           | 3      | 2            | 1      | Bit 0  |

|        | See page 303.                                                  | Reset:          | 0      | 0          | 0      | 0           | 0      | 0            | 0      | 0      |

|        | Break Status and Control<br>Register (BRKSCR)<br>See page 303. | Read:           | BRKE   | BRKA       | 0      | 0           | 0      | 0            | 0      | 0      |

| \$FE0B |                                                                | Write:          | DNNE   | DHNA       |        |             |        |              |        |        |

|        |                                                                | Reset:          | 0      | 0          | 0      | 0           | 0      | 0            | 0      | 0      |

|        | LVI Status Register                                            | Read:           | LVIOUT | 0          | 0      | 0           | 0      | 0            | 0      | 0      |

| \$FE0C | (LVISR)                                                        | Write:          |        |            |        |             |        |              |        |        |

|        | See page 133.                                                  | Reset:          | 0      | 0          | 0      | 0           | 0      | 0            | 0      | 0      |

| \$FE0D | FLASH-2 Test Control<br>Register (FLTCR2)                      | Read:<br>Write: | R      | R          | R      | R           | R      | R            | R      | R      |

|        | negister (FLTOR2)                                              | Reset:          | 0      | 0          | 0      | 0           | 0      | 0            | 0      | 0      |

| \$FE0E | FLASH-1 Test Control<br>Register (FLTCR1)                      | Read:<br>Write: | R      | R          | R      | R           | R      | R            | R      | R      |

|        | riogister (i Eroiti)                                           | Reset:          | 0      | 0          | 0      | 0           | 0      | 0            | 0      | 0      |

|        |                                                                |                 |        | = Unimplem | nented | R = Reserve | d      | U = Unaffect | ted    |        |

Figure 2-2. Control, Status, and Data Registers (Sheet 8 of 9)

MC68HC908GZ60 • MC68HC908GZ48 • MC68HC908GZ32 Data Sheet, Rev. 6

#### Memory

- 8. Wait for a time,  $t_{NVHI}$  (minimum 100  $\mu$ s).

- 9. Clear the HVEN bit.

- 10. Wait for a time,  $t_{RCV}$ , (typically 1  $\mu$ s) after which the memory can be accessed in normal read mode.

#### NOTES

- **A.** Programming and erasing of FLASH locations can not be performed by code being executed from the same FLASH array.

- **B.** While these operations must be performed in the order shown, other unrelated operations may occur between the steps. However, care must be taken to ensure that these operations do not access any address within the FLASH array memory space such as the COP control register (COPCTL) at \$FFFF.

- C. It is highly recommended that interrupts be disabled during program/erase operations.

# 2.7.5 FLASH-2 Page Erase Operation

Use this step-by-step procedure to erase a page (128 bytes) of FLASH-2 memory:

- 1. Set the ERASE bit and clear the MASS bit in the FLASH-2 control register (FL2CR).

- 2. Read the FLASH-2 block protect register (FL2BPR).

- 3. Write any data to any FLASH-2 address within the address range of the page (128 byte block) to be erased.

- 4. Wait for time,  $t_{NVS}$  (minimum 10  $\mu$ s).

- 5. Set the HVEN bit.

- 6. Wait for time, t<sub>ERASE</sub> (minimum 1 ms or 4 ms).

- 7. Clear the ERASE bit.

- 8. Wait for time,  $t_{NVH}$  (minimum 5  $\mu$ s).

- 9. Clear the HVEN bit.

- 10. Wait for a time,  $t_{BCV}$ , (typically 1  $\mu$ s) after which the memory can be accessed in normal read mode.

#### **NOTES**

- **A.** Programming and erasing of FLASH locations can not be performed by code being executed from the same FLASH array.

- **B.** While these operations must be performed in the order shown, other unrelated operations may occur between the steps. However, care must be taken to ensure that these operations do not access any address within the FLASH array memory space such as the COP control register (COPCTL) at \$FFFF.

- C. It is highly recommended that interrupts be disabled during program/erase operations.

In applications that require more than 1000 program/erase cycles, use the 4 ms page erase specification to get improved long-term reliability. Any application can use this 4 ms page erase specification. However, in applications where a FLASH location will be erased and reprogrammed less than 1000 times, and speed is important, use the 1 ms page erase specification to get a shorter cycle time.

#### Analog-to-Digital Converter (ADC)

#### 3.3.3 Conversion Time

Conversion starts after a write to the ADC status and control register (ADSCR). One conversion will take between 16 and 17 ADC clock cycles. The ADIVx and ADICLK bits should be set to provide a 1-MHz ADC clock frequency.

Conversion time =

$$\frac{16 \text{ to } 17 \text{ ADC cycles}}{\text{ADC frequency}}$$

Number of bus cycles = conversion time  $\times$  bus frequency

#### 3.3.4 Conversion

In continuous conversion mode, the ADC data register will be filled with new data after each conversion. Data from the previous conversion will be overwritten whether that data has been read or not. Conversions will continue until the ADCO bit is cleared. The COCO bit is set after each conversion and will stay set until the next read of the ADC data register.

In single conversion mode, conversion begins with a write to the ADSCR. Only one conversion occurs between writes to the ADSCR.

When a conversion is in process and the ADSCR is written, the current conversion data should be discarded to prevent an incorrect reading.

# 3.3.5 Accuracy and Precision

The conversion process is monotonic and has no missing codes.

#### 3.3.6 Result Justification

The conversion result may be formatted in four different ways:

- 1. Left justified

- 2. Right justified

- 3. Left Justified sign data mode

- 8-bit truncation mode

All four of these modes are controlled using MODE0 and MODE1 bits located in the ADC clock register (ADCLK).

Left justification will place the eight most significant bits (MSB) in the corresponding ADC data register high, ADRH. This may be useful if the result is to be treated as an 8-bit result where the two least significant bits (LSB), located in the ADC data register low, ADRL, can be ignored. However, ADRL must be read after ADRH or else the interlocking will prevent all new conversions from being stored.

Right justification will place only the two MSBs in the corresponding ADC data register high, ADRH, and the eight LSBs in ADC data register low, ADRL. This mode of operation typically is used when a 10-bit unsigned result is desired.

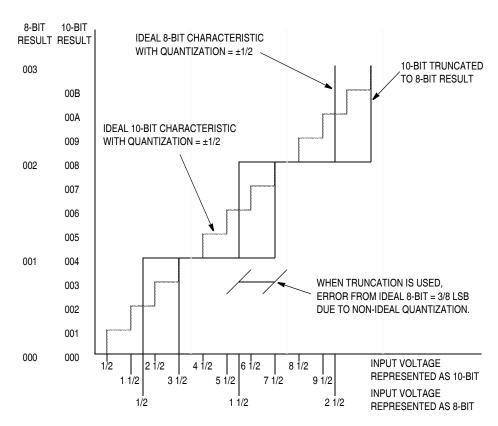

Left justified sign data mode is similar to left justified mode with one exception. The MSB of the 10-bit result, AD9 located in ADRH, is complemented. This mode of operation is useful when a result, represented as a signed magnitude from mid-scale, is needed. Finally, 8-bit truncation mode will place the eight MSBs in the ADC data register low, ADRL. The two LSBs are dropped. This mode of operation is used when compatibility with 8-bit ADC designs are required. No interlocking between ADRH and ADRL is present.

# **NOTE**Quantization error is affected when only the most significant eight bits are used as a result. See Figure 3-3.

Figure 3-3. Bit Truncation Mode Error

# 3.4 Monotonicity

The conversion process is monotonic and has no missing codes.

# 3.5 Interrupts

When the AIEN bit is set, the ADC module is capable of generating CPU interrupts after each ADC conversion. A CPU interrupt is generated if the COCO bit is a 0. The COCO bit is not used as a conversion complete flag when interrupts are enabled.

**Clock Generator Module (CGM)**

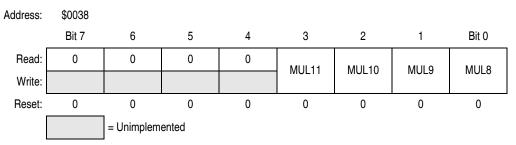

# 4.5.3 PLL Multiplier Select Register High

The PLL multiplier select register high (PMSH) contains the programming information for the high byte of the modulo feedback divider.

Figure 4-6. PLL Multiplier Select Register High (PMSH)

## **MUL11-MUL8** — Multiplier Select Bits

These read/write bits control the high byte of the modulo feedback divider that selects the VCO frequency multiplier N. (See 4.3.3 PLL Circuits and 4.3.6 Programming the PLL.) A value of \$0000 in the multiplier select registers configures the modulo feedback divider the same as a value of \$0001. Reset initializes the registers to \$0040 for a default multiply value of 64.

#### NOTE

The multiplier select bits have built-in protection such that they cannot be written when the PLL is on (PLLON = 1).

# PMSH[7:4] — Unimplemented Bits

These bits have no function and always read as 0s.

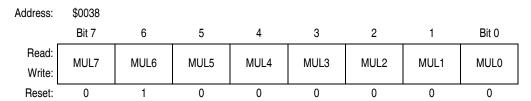

# 4.5.4 PLL Multiplier Select Register Low

The PLL multiplier select register low (PMSL) contains the programming information for the low byte of the modulo feedback divider.

Figure 4-7. PLL Multiplier Select Register Low (PMSL)

#### NOTE

For applications using 1–8 MHz reference frequencies this register must be reprogrammed before enabling the PLL. The reset value of this register will cause applications using 1–8 MHz reference frequencies to become unstable if the PLL is enabled without programming an appropriate value. The programmed value must not allow the VCO clock to exceed 32 MHz. See 4.3.6 Programming the PLL for detailed instructions on choosing the proper value for PMSL.

MC68HC908GZ60 • MC68HC908GZ48 • MC68HC908GZ32 Data Sheet, Rev. 6

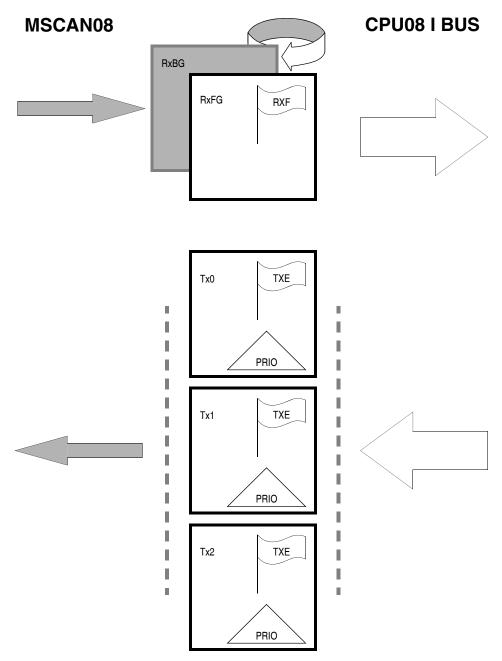

Figure 12-3. User Model for Message Buffer Organization

### 12.4.3 Transmit Structures

The MSCAN08 has a triple transmit buffer scheme to allow multiple messages to be set up in advance and to achieve an optimized real-time performance. The three buffers are arranged as shown in Figure 12-3.

All three buffers have a 13-byte data structure similar to the outline of the receive buffers (see 12.12 Programmer's Model of Message Storage). An additional transmit buffer priority register (TBPR) contains an 8-bit "local priority" field (PRIO) (see 12.12.5 Transmit Buffer Priority Registers).

MC68HC908GZ60 • MC68HC908GZ48 • MC68HC908GZ32 Data Sheet, Rev. 6

#### SFTRES — Soft Reset

When this bit is set by the CPU, the MSCAN08 immediately enters the soft reset state. Any ongoing transmission or reception is aborted and synchronization to the bus is lost.

The following registers enter and stay in their hard reset state:

CMCR0, CRFLG, CRIER, CTFLG, and CTCR.

The registers CMCR1, CBTR0, CBTR1, CIDAC, CIDAR0–CIDAR3, and CIDMR0–CIDMR3 can only be written by the CPU when the MSCAN08 is in soft reset state. The values of the error counters are not affected by soft reset.

When this bit is cleared by the CPU, the MSCAN08 tries to synchronize to the CAN bus. If the MSCAN08 is not in bus-off state, it will be synchronized after 11 recessive bits on the bus; if the MSCAN08 is in bus-off state, it continues to wait for 128 occurrences of 11 recessive bits.

Clearing SFTRES and writing to other bits in CMCR0 must be in separate instructions.

- 1 = MSCAN08 in soft reset state

- 0 = Normal operation

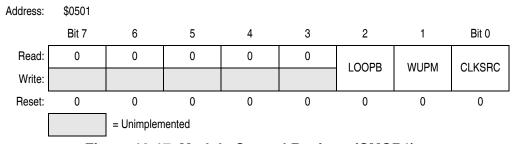

# 12.13.2 MSCAN08 Module Control Register 1

Figure 12-17. Module Control Register (CMCR1)

#### **LOOPB** — Loop Back Self-Test Mode

When this bit is set, the MSCAN08 performs an internal loop back which can be used for self-test operation: the bit stream output of the transmitter is fed back to the receiver internally. The CAN<sub>RX</sub> input pin is ignored and the CAN<sub>TX</sub> output goes to the recessive state (1). The MSCAN08 behaves as it does normally when transmitting and treats its own transmitted message as a message received from a remote node. In this state the MSCAN08 ignores the bit sent during the ACK slot of the CAN frame Acknowledge field to insure proper reception of its own message. Both transmit and receive interrupts are generated.

- 1 = Activate loop back self-test mode

- 0 = Normal operation

# WUPM — Wakeup Mode

This flag defines whether the integrated low-pass filter is applied to protect the MSCAN08 from spurious wakeups (see 12.8.5 Programmable Wakeup Function).

- 1 = MSCAN08 will wakeup the CPU only in cases of a dominant pulse on the bus which has a length of at least  $t_{wup}$ .

- 0 = MSCAN08 will wakeup the CPU after any recessive-to-dominant edge on the CAN bus.

**MSCAN08 Controller (MSCAN08)**

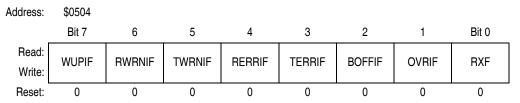

# 12.13.5 MSCAN08 Receiver Flag Register (CRFLG)

All bits of this register are read and clear only. A flag can be cleared by writing a 1 to the corresponding bit position. A flag can be cleared only when the condition which caused the setting is valid no more. Writing a 0 has no effect on the flag setting. Every flag has an associated interrupt enable flag in the CRIER register. A hard or soft reset will clear the register.

Figure 12-20. Receiver Flag Register (CRFLG)

### **WUPIF** — Wakeup Interrupt Flag

If the MSCAN08 detects bus activity while in sleep mode, it sets the WUPIF flag. If not masked, a wakeup interrupt is pending while this flag is set.

- 1 = MSCAN08 has detected activity on the bus and requested wakeup.

- 0 = No wakeup interrupt has occurred.

# RWRNIF — Receiver Warning Interrupt Flag

This flag is set when the MSCAN08 goes into warning status due to the receive error counter (REC) exceeding 96 and neither one of the error interrupt flags or the bus-off interrupt flag is set<sup>(1)</sup>. If not masked, an error interrupt is pending while this flag is set.

- 1 = MSCAN08 has gone into receiver warning status.

- 0 = No receiver warning status has been reached.

# TWRNIF — Transmitter Warning Interrupt Flag

This flag is set when the MSCAN08 goes into warning status due to the transmit error counter (TEC) exceeding 96 and neither one of the error interrupt flags or the bus-off interrupt flag is set<sup>(2)</sup>. If not masked, an error interrupt is pending while this flag is set.

- 1 = MSCAN08 has gone into transmitter warning status.

- 0 = No transmitter warning status has been reached.

#### RERRIF — Receiver Error Passive Interrupt Flag

This flag is set when the MSCAN08 goes into error passive status due to the receive error counter exceeding 127 and the bus-off interrupt flag is not set<sup>(3)</sup>. If not masked, an error interrupt is pending while this flag is set.

- 1 = MSCAN08 has gone into receiver error passive status.

- 0 = No receiver error passive status has been reached.

<sup>1.</sup> Condition to set the flag: RWRNIF = (96  $\rightarrow$  REC) & RERIF & TERRIF & BOFFIF

<sup>2.</sup> Condition to set the flag: TWRNIF = (96  $\rightarrow$  TEC) & RERRIF & TERRIF & BOFFIF

<sup>3.</sup> Condition to set the flag: RERRIF = (127  $\rightarrow$  REC  $\rightarrow$  255) & BOFFIF

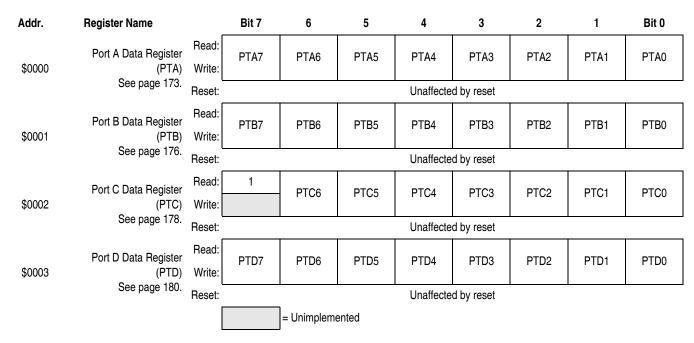

# Chapter 13 Input/Output (I/O) Ports

# 13.1 Introduction

Bidirectional input-output (I/O) pins form seven parallel ports. All I/O pins are programmable as inputs or outputs. All individual bits within port A, port C, port D and port F are software configurable with pullup devices if configured as input port bits. The pullup devices are automatically and dynamically disabled when a port bit is switched to output mode.

# 13.2 Unused Pin Termination

Input pins and I/O port pins that are not used in the application must be terminated. This prevents excess current caused by floating inputs, and enhances immunity during noise or transient events. Termination methods include:

- 1. Configuring unused pins as outputs and driving high or low;

- 2. Configuring unused pins as inputs and enabling internal pull-ups;

- 3. Configuring unused pins as inputs and using external pull-up or pull-down resistors.

Never connect unused pins directly to V<sub>DD</sub> or V<sub>SS</sub>.

Since some general-purpose I/O pins are not available on all packages, these pins must be terminated as well. Either method 1 or 2 above are appropriate.

Figure 13-1. I/O Port Register Summary (Sheet 1 of 3)

MC68HC908GZ60 • MC68HC908GZ48 • MC68HC908GZ32 Data Sheet, Rev. 6

Input/Output (I/O) Ports

# 13.4 Port B

Port B is an 8-bit special-function port that shares all eight of its pins with the analog-to-digital converter (ADC) module.

# 13.4.1 Port B Data Register

The port B data register (PTB) contains a data latch for each of the eight port pins.

Figure 13-6. Port B Data Register (PTB)

#### PTB7-PTB0 — Port B Data Bits

These read/write bits are software-programmable. Data direction of each port B pin is under the control of the corresponding bit in data direction register B. Reset has no effect on port B data.

### AD7-AD0 — Analog-to-Digital Input Bits

AD7-AD0 are pins used for the input channels to the analog-to-digital converter module. The channel select bits in the ADC status and control register define which port B pin will be used as an ADC input and overrides any control from the port I/O logic by forcing that pin as the input to the analog circuitry.

#### NOTE

Care must be taken when reading port B while applying analog voltages to AD7–AD0 pins. If the appropriate ADC channel is not enabled, excessive current drain may occur if analog voltages are applied to the PTBx/ADx pin, while PTB is read as a digital input during the CPU read cycle. Those ports not selected as analog input channels are considered digital I/O ports.

#### 13.4.2 Data Direction Register B

Data direction register B (DDRB) determines whether each port B pin is an input or an output. Writing a 1 to a DDRB bit enables the output buffer for the corresponding port B pin; a 0 disables the output buffer.

Figure 13-7. Data Direction Register B (DDRB)

#### **Enhanced Serial Communications Interface (ESCI) Module**

### 14.4.3.2 Character Reception

During an ESCI reception, the receive shift register shifts characters in from the RxD pin. The ESCI data register (SCDR) is the read-only buffer between the internal data bus and the receive shift register.

After a complete character shifts into the receive shift register, the data portion of the character transfers to the SCDR. The ESCI receiver full bit, SCRF, in ESCI status register 1 (SCS1) becomes set, indicating that the received byte can be read. If the ESCI receive interrupt enable bit, SCRIE, in SCC2 is also set, the SCRF bit generates a receiver CPU interrupt request.

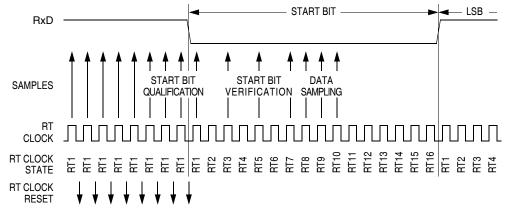

#### 14.4.3.3 Data Sampling

The receiver samples the RxD pin at the RT clock rate. The RT clock is an internal signal with a frequency 16 times the baud rate. To adjust for baud rate mismatch, the RT clock is resynchronized at these times (see Figure 14-7):

- · After every start bit

- After the receiver detects a data bit change from 1 to 0 (after the majority of data bit samples at RT8, RT9, and RT10 returns a valid 1 and the majority of the next RT8, RT9, and RT10 samples returns a valid 0)

To locate the start bit, data recovery logic does an asynchronous search for a 0 preceded by three 1s. When the falling edge of a possible start bit occurs, the RT clock begins to count to 16.

Figure 14-7. Receiver Data Sampling

To verify the start bit and to detect noise, data recovery logic takes samples at RT3, RT5, and RT7. Table 14-2 summarizes the results of the start bit verification samples.

Table 14-2. Start Bit Verification

| RT3, RT5, and RT7 Samples | Start Bit Verification | Noise Flag |

|---------------------------|------------------------|------------|

| 000                       | Yes                    | 0          |

| 001                       | Yes                    | 1          |

| 010                       | Yes                    | 1          |

| 011                       | No                     | 0          |

| 100                       | Yes                    | 1          |

| 101                       | No                     | 0          |

| 110                       | No                     | 0          |

| 111                       | No                     | 0          |

MC68HC908GZ60 • MC68HC908GZ48 • MC68HC908GZ32 Data Sheet, Rev. 6

# **Chapter 15 System Integration Module (SIM)**

# 15.1 Introduction

This section describes the system integration module (SIM). Together with the central processor unit (CPU), the SIM controls all microcontroller unit (MCU) activities. A block diagram of the SIM is shown in Figure 15-1. Table 15-1 is a summary of the SIM input/output (I/O) registers. The SIM is a system state controller that coordinates CPU and exception timing.

The SIM is responsible for:

- Bus clock generation and control for CPU and peripherals:

- Stop/wait/reset/break entry and recovery

- Internal clock control

- Master reset control, including power-on reset (POR) and computer operating properly (COP) timeout

- Interrupt arbitration

Table 15-1 shows the internal signal names used in this section.

**Table 15-1. Signal Name Conventions**

| Signal Name | Description                                                                              |

|-------------|------------------------------------------------------------------------------------------|

| CGMXCLK     | Buffered version of OSC1 from clock generator module (CGM)                               |

| CGMVCLK     | PLL output                                                                               |

| CGMOUT      | PLL-based or OSC1-based clock output from CGM module (Bus clock = CGMOUT divided by two) |

| IAB         | Internal address bus                                                                     |

| IDB         | Internal data bus                                                                        |

| PORRST      | Signal from the power-on reset module to the SIM                                         |

| IRST        | Internal reset signal                                                                    |

| R/W         | Read/write signal                                                                        |

# 15.3 Reset and System Initialization

The MCU has these reset sources:

- Power-on reset module (POR)

- External reset pin (RST)

- Computer operating properly module (COP)

- Low-voltage inhibit module (LVI)

- Illegal opcode

- Illegal address

- Forced monitor mode entry reset (MODRST)

All of these resets produce the vector \$FFFE:\$FFFF (\$FEFE:\$FEFF in monitor mode) and assert the internal reset signal (IRST). IRST causes all registers to be returned to their default values and all modules to be returned to their reset states.

An internal reset clears the SIM counter (see 15.4 SIM Counter), but an external reset does not. Each of the resets sets a corresponding bit in the SIM reset status register (SRSR). See 15.7 SIM Registers.

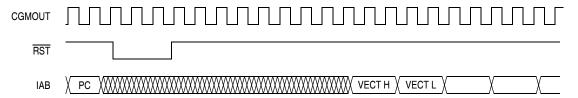

A reset immediately stops the operation of the instruction being executed. Reset initializes certain control and status bits. Reset selects CGMXCLK divided by four as the bus clock.

#### 15.3.1 External Pin Reset

The  $\overline{RST}$  pin circuit includes an internal pullup device. Pulling the asynchronous  $\overline{RST}$  pin low halts all processing. The PIN bit of the SIM reset status register (SRSR) is set as long as  $\overline{RST}$  is held low for at least the minimum  $t_{RI}$  time and no other reset sources are present. Figure 15-4 shows the relative timing.

Figure 15-4. External Reset Timing

#### 15.3.2 Active Resets from Internal Sources

All internal reset sources actively pull the RST pin low for 32 CGMXCLK cycles to allow resetting of external peripherals. The internal reset continues to be asserted for an additional 32 cycles at which point the reset vector will be fetched. See Figure 15-5. An internal reset can be caused by an illegal address, illegal opcode, COP timeout, LVI, or POR. See Figure 15-6.

#### NOTE

For LVI or POR resets, the SIM cycles through 4096 CGMXCLK cycles during which the SIM forces the RST pin low. The internal reset signal then follows the sequence from the falling edge of RST shown in Figure 15-5.

The COP reset is asynchronous to the bus clock.

The active reset feature allows the part to issue a reset to peripherals and other chips within a system built around the MCU.

MC68HC908GZ60 • MC68HC908GZ48 • MC68HC908GZ32 Data Sheet, Rev. 6

#### **System Integration Module (SIM)**

#### ILOP — Illegal Opcode Reset Bit

- 1 = Last reset caused by an illegal opcode

- 0 = POR or read of SRSR

## ILAD — Illegal Address Reset Bit (opcode fetches only)

- 1 = Last reset caused by an opcode fetch from an illegal address

- 0 = POR or read of SRSR

#### **MODRST** — Monitor Mode Entry Module Reset Bit

- 1 = Last reset caused by monitor mode entry when vector locations \$FFFE and \$FFFF are \$FF after POR while  $\overline{IRQ} = V_{DD}$

- 0 = POR or read of SRSR

### LVI — Low-Voltage Inhibit Reset Bit

- 1 = Last reset caused by the LVI circuit

- 0 = POR or read of SRSR

# 15.7.3 Break Flag Control Register

The break flag control register contains a bit that enables software to clear status bits while the MCU is in a break state.

Figure 15-23. Break Flag Control Register (BFCR)

# **BCFE** — Break Clear Flag Enable Bit

This read/write bit enables software to clear status bits by accessing status registers while the MCU is in a break state. To clear status bits during the break state, the BCFE bit must be set.

- 1 = Status bits clearable during break

- 0 = Status bits not clearable during break

#### Serial Peripheral Interface (SPI) Module

In a master SPI with the mode fault enable bit (MODFEN) set, the mode fault flag (MODF) is set if SS goes low. A mode fault in a master SPI causes the following events to occur:

- If ERRIE = 1, the SPI generates an SPI receiver/error CPU interrupt request.

- The SPE bit is cleared.

- · The SPTE bit is set.

- The SPI state counter is cleared.

- The data direction register of the shared I/O port regains control of port drivers.

#### NOTE

To prevent bus contention with another master SPI after a mode fault error, clear all SPI bits of the data direction register of the shared I/O port before enabling the SPI.

When configured as a slave (SPMSTR = 0), the MODF flag is set if  $\overline{SS}$  goes high during a transmission. When CPHA = 0, a transmission begins when  $\overline{SS}$  goes low and ends once the incoming SPSCK goes back to its idle level following the shift of the eighth data bit. When CPHA = 1, the transmission begins when the SPSCK leaves its idle level and  $\overline{SS}$  is already low. The transmission continues until the SPSCK returns to its idle level following the shift of the last data bit. See 16.4 Transmission Formats.

#### NOTE

Setting the MODF flag does not clear the SPMSTR bit. SPMSTR has no function when SPE = 0. Reading SPMSTR when MODF = 1 shows the difference between a MODF occurring when the SPI is a master and when it is a slave.

When CPHA = 0, a MODF occurs if a slave is selected ( $\overline{SS}$  is low) and later unselected ( $\overline{SS}$  is high) even if no SPSCK is sent to that slave. This happens because  $\overline{SS}$  low indicates the start of the transmission (MISO driven out with the value of MSB) for CPHA = 0. When CPHA = 1, a slave can be selected and then later unselected with no transmission occurring. Therefore, MODF does not occur since a transmission was never begun.

In a slave SPI (MSTR = 0), MODF generates an SPI receiver/error CPU interrupt request if the ERRIE bit is set. The MODF bit does not clear the SPE bit or reset the SPI in any way. Software can abort the SPI transmission by clearing the SPE bit of the slave.

#### NOTE

A high on the  $\overline{SS}$  pin of a slave SPI puts the MISO pin in a high impedance state. Also, the slave SPI ignores all incoming SPSCK clocks, even if it was already in the middle of a transmission.

To clear the MODF flag, read the SPSCR with the MODF bit set and then write to the SPCR register. This entire clearing mechanism must occur with no MODF condition existing or else the flag is not cleared.

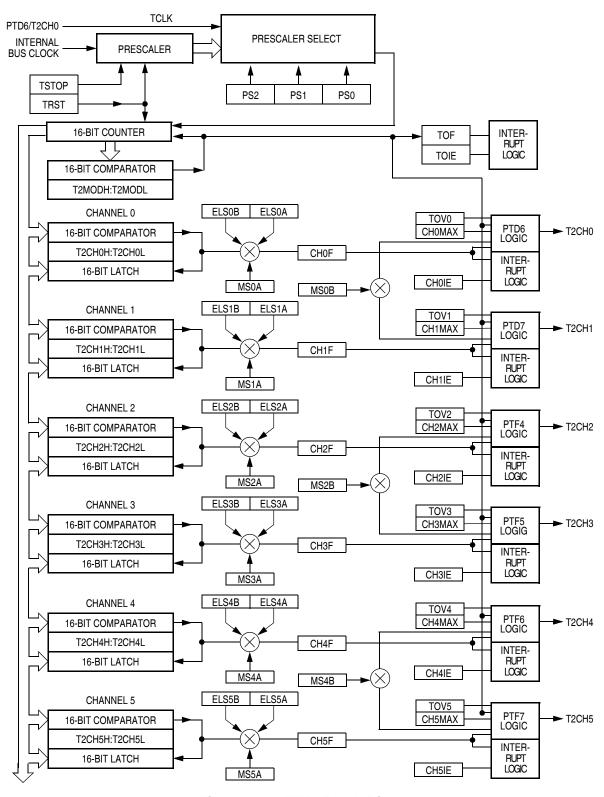

Figure 19-2. TIM2 Block Diagram

MC68HC908GZ60 • MC68HC908GZ48 • MC68HC908GZ32 Data Sheet, Rev. 6

# **Timer Interface Module (TIM2)**

| Addr.         | Register Name                                                          |                                 | Bit 7                     | 6                         | 5      | 4             | 3             | 2     | 1     | Bit 0      |         |      |        |

|---------------|------------------------------------------------------------------------|---------------------------------|---------------------------|---------------------------|--------|---------------|---------------|-------|-------|------------|---------|------|--------|

| TII<br>\$002B | TIM2 Status and Control                                                | Read: TOF                       | TOF                       | TOIE                      | TSTOP  | 0             | 0             | PS2   | PS1   | PS0        |         |      |        |

|               | Register (T2SC)                                                        | Write:                          | 0                         | TOIL                      |        | TRST          |               | 1 02  | P31   | F 30       |         |      |        |

|               | See page 291.                                                          | Reset:                          | 0                         | 0                         | 1      | 0             | 0             | 0     | 0     | 0          |         |      |        |

|               | TIM2 Counter Register High                                             | Read:                           | Bit 15                    | 14                        | 13     | 12            | 11            | 10    | 9     | Bit 8      |         |      |        |

| \$002C        | (T2CNTH)                                                               | Write:                          |                           |                           |        |               |               |       |       |            |         |      |        |

|               | See page 292.                                                          | Reset:                          | 0                         | 0                         | 0      | 0             | 0             | 0     | 0     | 0          |         |      |        |

|               | TIM2 Counter Register Low                                              | Read:                           | Bit 7                     | 6                         | 5      | 4             | 3             | 2     | 1     | Bit 0      |         |      |        |

| \$002D        | (T2CNTL)                                                               | Write:                          |                           |                           |        |               |               |       |       |            |         |      |        |

|               | See page 292.                                                          | Reset:                          | 0                         | 0                         | 0      | 0             | 0             | 0     | 0     | 0          |         |      |        |

| \$002E        | TIM2 Modulo Register High<br>(T2MODH)                                  | Read:<br>Write:                 | Bit 15                    | 14                        | 13     | 12            | 11            | 10    | 9     | Bit 8      |         |      |        |

|               | See page 293.                                                          | Reset:                          | 1                         | 1                         | 1      | 1             | 1             | 1     | 1     | 1          |         |      |        |

| \$002F        | TIM2 Modulo Register Low (T2MODL)                                      | Read:<br>Write:                 | Bit 7                     | 6                         | 5      | 4             | 3             | 2     | 1     | Bit 0      |         |      |        |

|               | See page 293.                                                          | Reset:                          | 1                         | 1                         | 1      | 1             | 1             | 1     | 1     | 1          |         |      |        |

| \$0030        | TIM2 Channel 0 Status and<br>Control Register (T2SC0)<br>See page 293. | TIM2 Channel 0 Status and       | TIM2 Channel 0 Status and | TIM2 Channel 0 Status and | Read:  | CH0F          | CH0IE         | MS0B  | MS0A  | ELS0B      | ELS0A   | TOV0 | CH0MAX |

|               |                                                                        | Write:                          | 0                         | OFIOIL                    | IVIOUD | IVIOUA        | LLSUB         | LLOUA | 1000  | CHUIVIAX   |         |      |        |

|               |                                                                        | Reset:                          | 0                         | 0                         | 0      | 0             | 0             | 0     | 0     | 0          |         |      |        |

| \$0031        | TIM2 Channel 0 Register High (T2CH0H)                                  | Read:<br>Write:                 | Bit 15                    | 14                        | 13     | 12            | 11            | 10    | 9     | Bit 8      |         |      |        |

|               | See page 297.                                                          | Reset:                          |                           | •                         |        | Indeterminate | e after reset |       |       | <u> </u>   |         |      |        |

| \$0032        | TIM2 Channel 0 Register Low<br>(T2CH0L)                                | Read:<br>Write:                 | Bit 7                     | 6                         | 5      | 4             | 3             | 2     | 1     | Bit 0      |         |      |        |

|               | See page 297.                                                          | Reset:                          |                           |                           |        | Indeterminate | e after reset |       |       |            |         |      |        |

|               | Control Register (T2SC1) Wi                                            | Read:                           | CH1F                      | CH1IE                     | 0      | MS1A          | ELS1B         | ELS1A | TOV1  | CH1MAX     |         |      |        |

| \$0033        |                                                                        |                                 | Write:                    | 0                         | OITTIL |               | MOTA          | LLOID | LLOTA | 10         | OTTIWAX |      |        |

|               |                                                                        | Reset:                          | 0                         | 0                         | 0      | 0             | 0             | 0     | 0     | 0          |         |      |        |

| \$0034        | TIM2 Channel 1 Register High (T2CH1H)                                  | Read:<br>Write:                 | Bit 15                    | 14                        | 13     | 12            | 11            | 10    | 9     | Bit 8      |         |      |        |

|               | See page 297.                                                          | Reset:                          |                           | •                         |        | Indeterminate | e after reset |       |       | <u> </u>   |         |      |        |

| \$0035        | TIM2 Channel 1 Register Low<br>(T2CH1L)                                | Read:<br>Write:                 | Bit 7                     | 6                         | 5      | 4             | 3             | 2     | 1     | Bit 0      |         |      |        |

|               | See page 297.                                                          | Reset:                          |                           |                           |        | Indeterminate | e after reset |       |       |            |         |      |        |

|               | TIM2 Channel 2 Status and                                              | TIM2 Channel 2 Status and Read: | CH2F                      | CH2IE                     | MS2B   | MS2A          | ELS2B         | ELS2A | TOV2  | CH2MAX     |         |      |        |

| \$0456        | Control Register (T2SC2)                                               | Write:                          | 0                         | OI IZIE                   | IVIOZD | IVIOZA        | LLOZD         | LLUZA | 1012  | OI IZIVIAA |         |      |        |

|               | See page 293.                                                          | Reset:                          | 0                         | 0                         | 0      | 0             | 0             | 0     | 0     | 0          |         |      |        |

|               |                                                                        |                                 |                           | = Unimplen                | nented |               |               |       |       |            |         |      |        |

Figure 19-3. TIM2 I/O Register Summary (Sheet 1 of 2)

MC68HC908GZ60 • MC68HC908GZ48 • MC68HC908GZ32 Data Sheet, Rev. 6